I

Изобретение относится к электротехнике и может быть использовано в импульсных интегральных схемах на НЛП-транзисторах, и в особенности, в интегральных схемах на МДПтранзисторах с обедненными нагрузками.

Известен форь гирователь имупльсов на НЦП-транзисторах, содержащий повторитель и инверторы Ij,

Недостатком зтого устройства является низкая помехоустойчивость.

Наиболее близким к предлагаемому является формирователь импульсов, содержащий двухтактный каскад на МДП-транзисторах, первый сложный инвертор с шиной питания и общей шиной, инвертор с нагрузочным МДПтранзистором, первый и опорой дополнительные МДП-транзисторы, конденсатор, вход первого сложного инвертора и инвертирующий вход двухтактного каскада объединены и подключены к выходной шине, шина питания первпгосложного инвертора подключена к истоку 1(;рвого дoпoл штeльнo МГЩ-транзисюра, сток которого подключен к шине питания, а затвор - к выходу инвертора, выход первого сложного инвертора подключен к неинвертирующему входу двухтактного каскада и к входу инвертора, исток и затвор второго дополнительного МДП-транзистора подклю чены к выходу двухтактного каскада, , выходной шине и через конденсатор к шике питания первого сложного инвертора, а его сток подключен к шине питания t 2.

Недостаток известного устройства15низкая помехоустойчивость.

Цель изобретения - повьпвение помехохоустойчивости.

Поставленная цель достигается тем, что в формирователь импульсов,

0 содержащий двухтактньп каскад на ВДИтранзисторах обогащенного типа, первый сложньш инвертор с шнной питания и общей агичой, инвертор с нагруэоч -гьт ШП-TDaнзиcтopoм обепненного типа, первый и второй дополнительные НДЛ- ранзнсторы обедненного типа, шину питания, входную, выходную и общую шины, конденсатор, вход, первого сложного инвертора и инвертирующий вход двухтактного каскада объединены и подключены к входной щине, шина питания первого сложного инвертора подключена к истоку первого дополнительного МДП-транзистора обедненного типа,сток .которого подключен к шине питания, а затвор - к выходу и нвертора, выход первого сложного инвертора подключен к неинвертирующему входу двухтактного каскада и к входу инвертора, нсток и затвор второго дополнительного МДП-транзистора обедненного типа подключен к выходу двухтактного каскада, выходной шине и через конденсатор - к шине питания первого сложного инвертора, а его сток подключен к шине питания, вве дан второй слож1а1Й инвертор, вход которого подключен к входной шине , а выход к общей шине первого слоясного инвертора,

Каждый из сложных инверторов содержит инвертор с нагрузочным ВДП-транзистором обедненного.типа и двухтактный каскад на МДП транзисторах обедненного типа и обогащенного типа, . причем вход инвертора объединен с инвертирунзЕИМ входом двухтактного каскада, а выход инвертора подключен к неинвертир тощему входу двухтактного каскада,

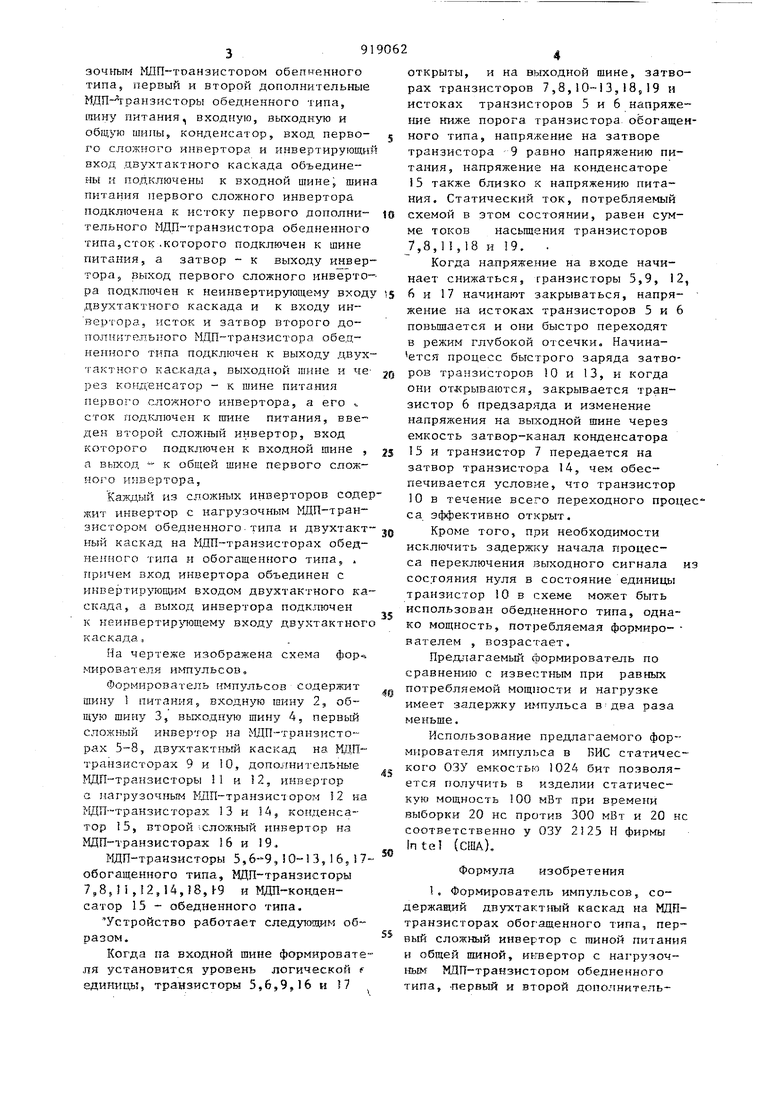

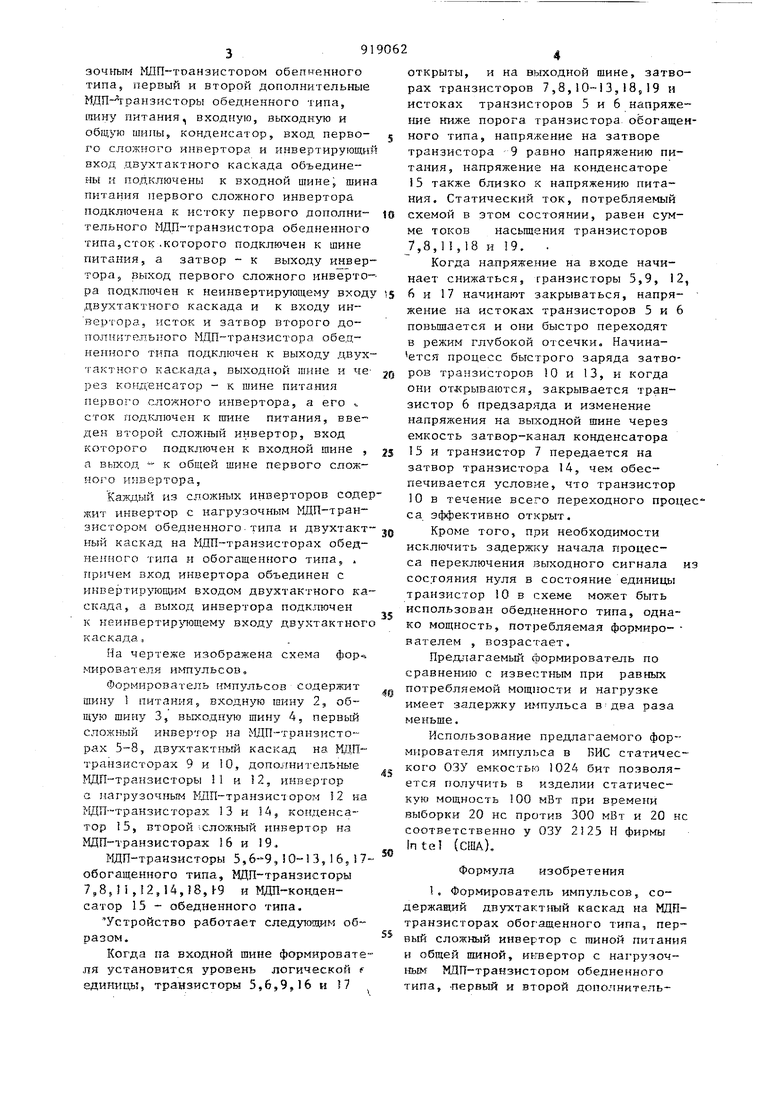

На чертеже изображена схема фор мирователя импульсов.

Формирователь импульсов содержит шину 1 питания, входную шкну 2, общую шину 3, выходаую шину 4, первый сложьъ1й инвертор на МДП--транзисторах 5-8, двухтактный каскад на ВДПтранзисторах 9 и iO, дополнительные МДП-траизисторы 1 и 12, инвертор а нагрузочным ЩП транзистором 12 на ЩП-транзисторах 13 и 1, конденсатор 15, второйiсложный инвертор на МДП-транзисторах 16 и 19,.

ВДП-транзисторы 5,6-9,,16,17обогащенного типа, МДП-транзисторы 7,85 ,12,14, 8, 1-9 и ЩП кон;ценсатор 15 - обедненного типа.

Устройство работает следующим образом.

Когда па входной шине формярователя установится уровень логической г едиииць, транзисторы 5,6,9,16 и 7

открыты, и на выходной шине, затворах транзисторов 7,8,10-i3,8,19 и

истоках транзисторов 5 и 6 напряже- roie ниже порога транзистора обогащенного типа, напряжение на затворе транзистора 9 равно напряжению питания, напряжение на конденсаторе 15 также близко к напряжению питания. Статический ток, потребляемый схемой в этом состоянии, равен сумме токов насыщения транзисторов 7,8, П , 1 8 и I 9.

Когда напряжение на входе начинает снижаться, граизисторы 5,9, 12 6 и 17 начинают закрываться, напряжение на истоках транзисторов 5 и 6 повьшается и они быстро переходят в режим глубокой отсечки. Начина ется процесс быстрого заряда затворов транзисторов 10 и 13, и когда они открываются, закрывается транзистор 6 предзаряда и изменение напряжения на выходной шине через емкость затвор-канал конденсатора I5 и транзистор 7 передается на затвор транзистора 14, чем обеспечивается условие, что транзистор 10 в течение всего переходного проц са эффективно открыт.

Кроме того, при необходимости исключить задержку начала процесса переключения выходного сигнала состояния нуля в состояние единицы транзистор 10 в схеме может быть использован обедненного типа, однако мощность, потребляемая формиро- вателем , возрастает.

Предлагаемый формирователь по сравнению с известным при равных потребляемой мощности и нагрузке имеет задержку импульса в-два раза меньще.

Использование предлагаемого формировате-ля импупьса в БИС статического ОЗУ емкостью 1024 бит позволяется получить в изделии статическую мощность 100 мВт при времени выборки 20 НС против 300 мВт и 20 н соответственно у ОЗУ 2125 Н фирмы

Intel (CIIIA),

Формула изобретения

1. Формирователь импульсов, содержащий двухтакт5{ый каскад на МДПтранзисторах обогащенного типа, первый сложный инвертор с гаиной питания и общей шиной, инвертор с нагрузочиым МДП-транзистором обедненного типа, -первый и второй допо.чнитель

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Формирователь импульсов | 1987 |

|

SU1431054A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Формирователь импульсов на МДП-транзисторах | 1982 |

|

SU1172003A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Ключевой элемент | 1984 |

|

SU1202048A1 |

Авторы

Даты

1982-04-07—Публикация

1980-09-29—Подача