Изобретение относится к электронике и может быть использовано в импульсных интегральных схемах на МДПтранзисторах.

Известен формирователь, состоящий из двух инверторов с общим входом, причем затвор нагрузочного транзистора выходного инвертора подключен к выходу первого 1.

Недостатком такого устройства является значительная мощность, потребляемая в статическом режиме при уровне входного напряжения, соответствующем логической единице.

Известен также формирователь импульсов, содержащий общую шину, шину питания, первую и вторую входную и выходную шины, инвертор на первом МДП-транзисторе обогащенного типа, в цепь стока которого включены последовательно второй МДП-транзистор обедненного типа и третий МДП-транзистор, затвор первого и второго МДП-транзисторов инвертора объединены и .подключены к первой входной шине, выходной каскад на первом и втором МДП-транзисторах обогащенного типа, первый из которых шуитирован третьим МДП-транзисторрм обедненного типа в диодном включении,

шток третьего МДП-транзистора инвертора подключен к затвору первого МДП-транзистора выходного каскада, а его сток через конденсатор подключен к выходной шине и выходу выходного каскада, затвор второго транзистора выходного каскада подключен ко входу инвертора и к первой входной шине 2J.

10

Недостатком такого формирователя является низкое быстродействие к большое потребление мощности.

Цель изобретения снижение потребляемой мощности и повышение быст15родействия формирователя импульсов.

Поставленная цель достигается тем, что в формирователь импульсов, содержащий общую шину, шину питания, первую и вторую входную и выходную

20 шины, инвертор на первом МДП-транзисторе обогащенного типа, в цепь стока которого включены последовательно второй МДП-транзистор обедненного типа и третий МДП-траизис25тор обогсцценного типа, затворы первого и второго МДП-транзисторов инвертора объединены и подключены к

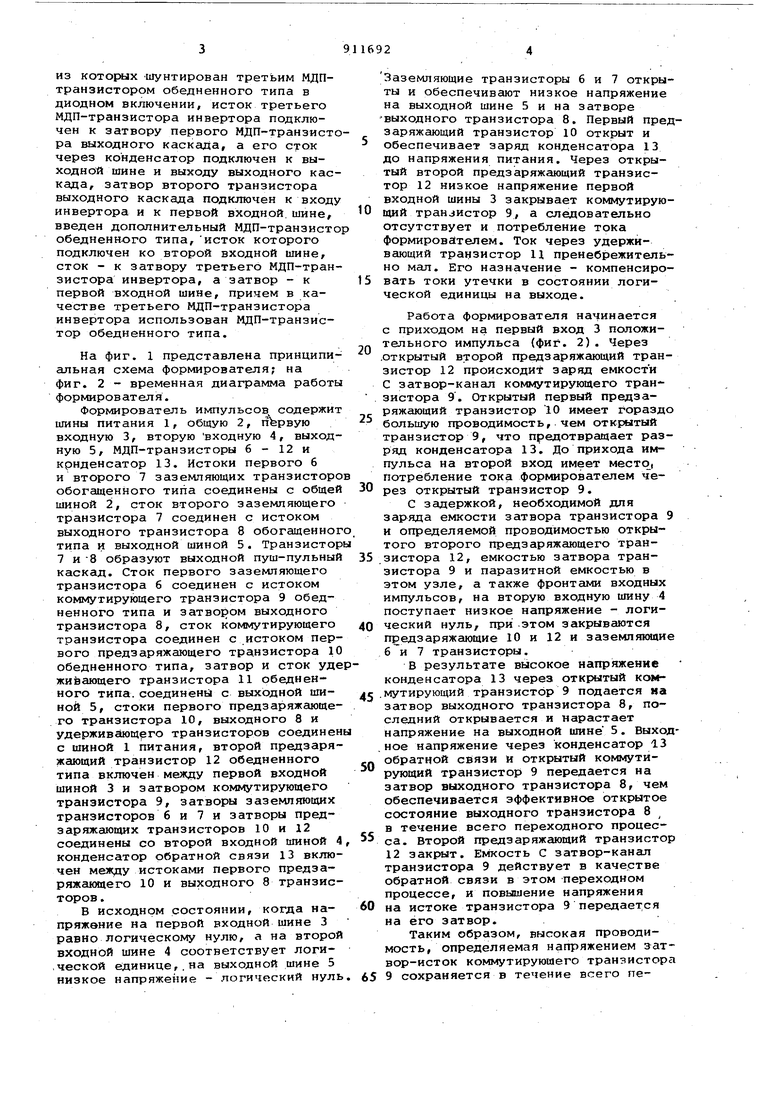

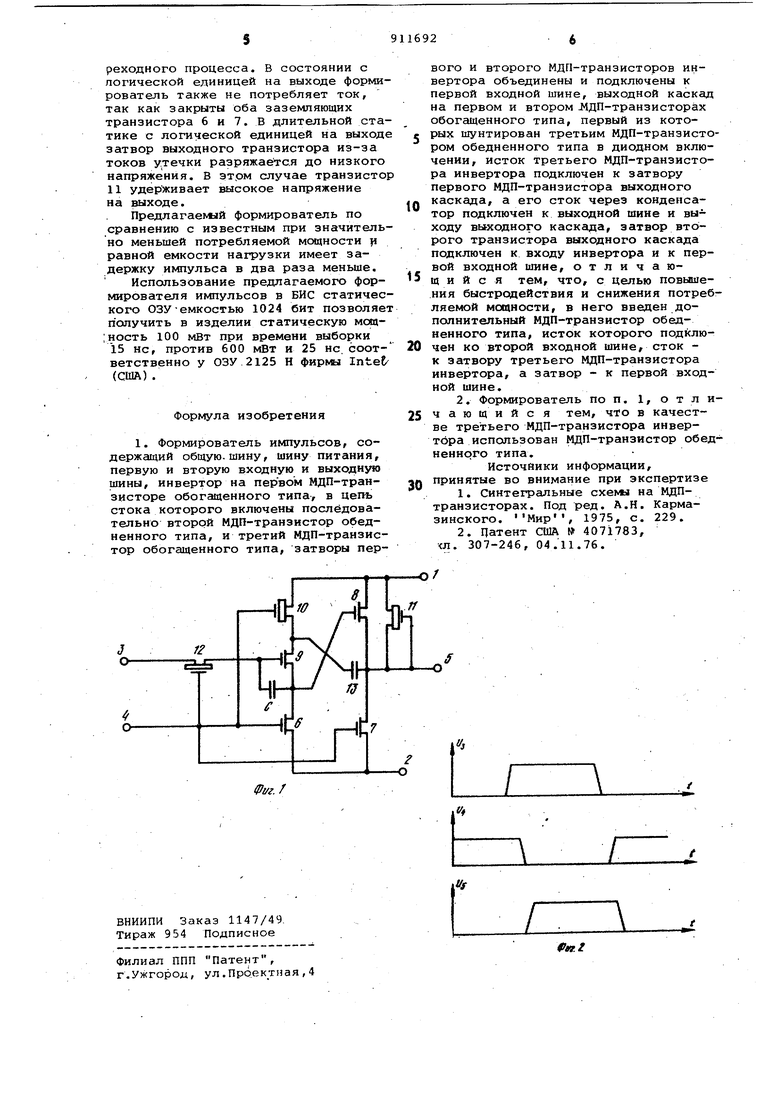

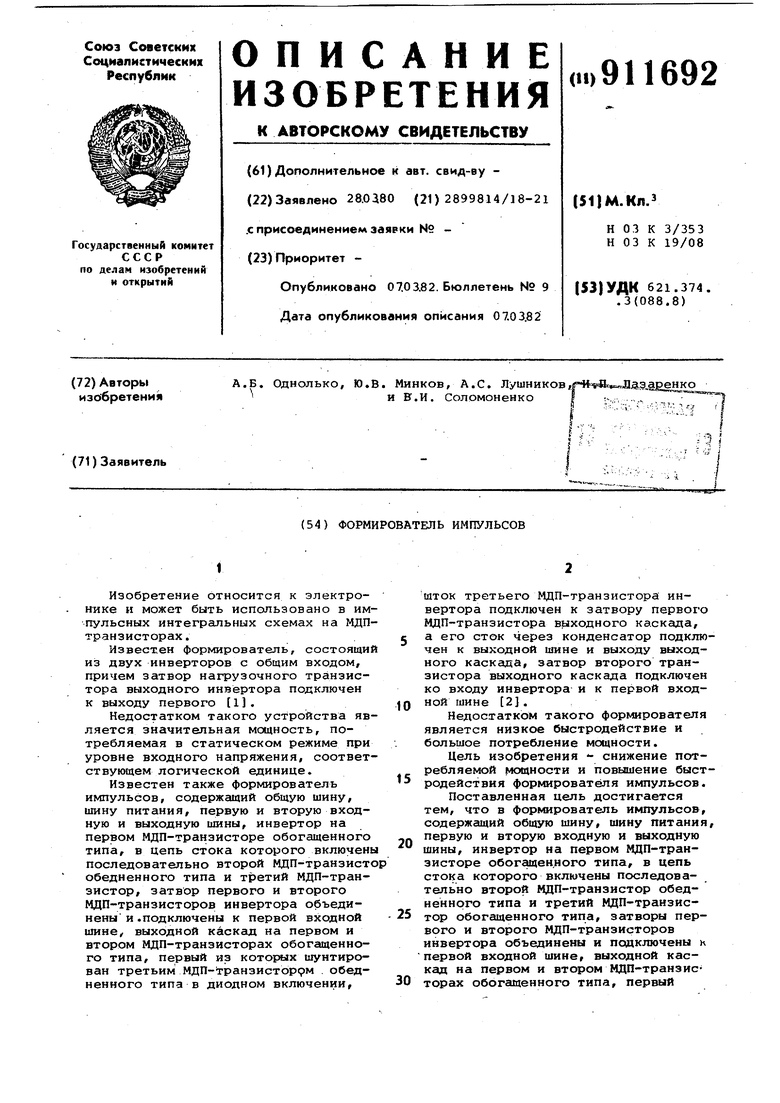

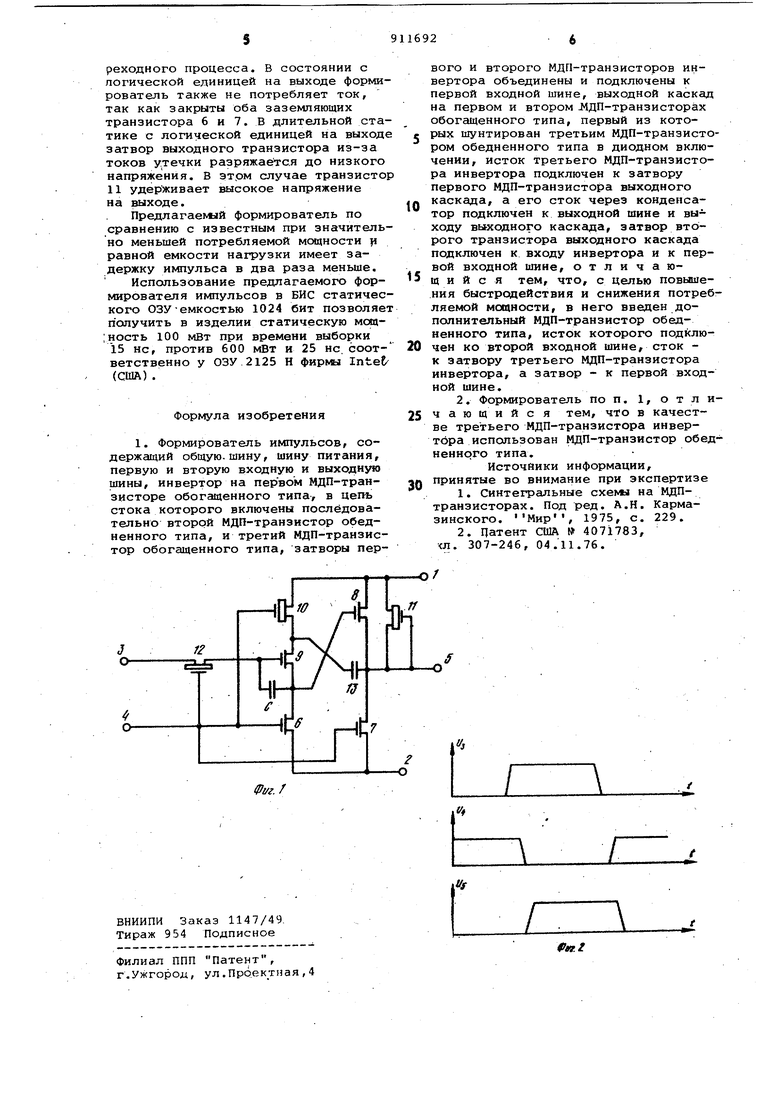

первой входной шине, выходной каскад на первом и втором МДП-транзис30торах обогащенного типа, первый из которых Шунтирован третьим МДПтранзистором обедненного типа в диодном включении, исток третьего МДП-транзистора инвертора подключен к затвору первого МДП-транзист ра выходного каскада, а его сток через конденсатор подключен к выходной шине и выходу выходного кас када, затвор второго транзистора выходного каскада подключен к входу инвертора и к первой входной шине, введен дополнительный МДП-транзисто обедненного типа,исток которого подключен ко второй входной шине, сток - к затвору третьего МДП-тран зистора инвертора, а затвор - к первой входной шине, причем в качестве третьего МДП-транзистора инвертора использован МДП-транзистор обедненного типа. На фиг. 1 представлена принципи альная схема формирователя; на фиг. 2 - временная диаграмма работы формирователя. Формирователь импульсов содержит шины питания 1, общую 2, первую входную 3, вторую входную 4, выход ную 5, МДП-транзисторы 6 - 12 и крнденсатор 13. Истоки первого 6 и второго 7 заземляющих транзистор обогащенного типа соединены с общей шиной 2, сток второго заземляющего транзистора 7 соединен с истоком выходного транзистора 8 обогащенно типа и выходной шиной 5. Транзистор 7 и -8 образуют выходной пуш-пульный каскад. Сток первого заземляющего транзистора 6 соединен с истоком коммутирующего транзистора 9 обедненного типа и затво15ом выходного транзистора 8, сток коммутирующего транзистора соединен с истоком первого предзаряжающего транзистора 10 обедненного типа, затвор и сток уде живающего транзистора 11 обедненного типа.соединены с выходной шиной 5, стоки первого предзаряжающего транзистора 10, выходного 8 и удерживающего транзисторов соединен с шиной 1 питания, второй предзаряжающий транзистор 12 обедненного типа включен между первой входной шиной 3 и затвором коммутирующего транзистора 9, затворы заземпяюгцих транзисторов 6 и 7 и затворы предзаряжающих транзисторов 10 и 12 соединены со второй входной шиной 4 конденсатор обратной связи 13 включен между истоками первого предзаряжающего 10 и выходного 8 транзисторов . В исходном состоянии, когда напряжение на первой входной шине 3 равно логическому нулю, а на второй входной шине 4 соответствует логи.ческой единице,.на выходной шине 5 низкое напряжение - логический нуль Заземляющие транзисторы 6 и 7 открыты и обеспечивают низкое напряжение на выходной шине 5 и на затворе ВЫХОДНОГО транзистора 8. Первый предзаряжающий транзистор 10 открыт и обеспечивает заряд конденсатора 13 до напряжения питания. Через открытый второй предзаряжающий транзистор 12 низкое напряжение первой входной шины 3 закрывает коммутирующий транзистор 9, а следовательно отсутствует и потребление тока формирователем. Ток через удерживающий транзистор 11 пренебрежительно мал. Его назначение - компенсировать токи утечки в состоянии логической единицы на выходе. Работа формирователя начинается с приходом на первый вход 3 положительного импульса (фиг. 2). Через .открытый второй предзаряжающий транзистор 12 происходит заряд емкости С затвор-канал коммутирующего транзистора 9. Открытый первый предзаряжающий транзистор 10 имеет гораздо большую проводимость, чем открытый транзистор 9, что предотвращает разряд конденсатора 13. До прихода импульса на второй вход имеет место, потребление тока формирователем через открытый транзистор 9. С задержкой, необходимой для заряда емкости затвора транзистора 9 и определяемой проводимостью открытого второго предзаряжающего транзистора 12, емкостью затвора транзистора 9 и паразитной емкостью в этом узле, а также фронтами входных импульсов, на вторую входную шину 4 поступает низкое напряжение - логический нуль, при .этом закрываются предзаряжающие 10 и 12 и заземляющие б и 7 транзисторы. В результате высокое напряжение конденсатора 13 через открытый коммутирующий транзистор 9 подается на затвор выходного транзистора 8, последний открывается и нарастает напряжение на выходной шине 5. Выходное напряжение через конденсатор 13 обратной св1язи и открытый коммутирующий транзистор 9 передается на затвор выходного транзистора 8, чем обеспечивается эффективное открытое состояние выходного транзистора 8 в течение всего переходного процесса. Второй предзаряжающий транзистор 12 закрыт. ЕМКОСТЬ С затвор-канал транзистора 9 действует в качестве обратной связи в этом переходном процессе, и повышение напряжения на истоке транзистора 9 передается на его затвор. Таким образом, высокая проводимость, определяемая напряжением затвор-исток коммутирующего транзистора 9 сохраняется в течение всего переходного процесса. В состоянии с логической единицей на выходе форми рователь также не потребляет ток, так как закрыты оба заземляющих транзистора 6 и 7. в длительной ст тике с логической единицей на выход затвор выходного транзистора из-за токов утечки разряжается до низкого напряжения. В этрм случае транзист 11 удерживает высокое напряжение на выходе. Предлагаемой формирователь по сравнению с известным при значитель но меньшей потребляемой мощности равной емкости нагрузки имеет задержку импульса в два раза меньше. Использование предлагаемого формирователя импульсов в БИС статичес кого ОЗУ-емкостью 1024 бит позволяе получить в изделии статическую моад;ность 100 мВт при времени выборки 15 НС, против 600 мВт и 25 не соответственно у ОЗУ 2125 Н фиркы Inte (США). Формула изобретения 1. Формирователь импульсов, содержащий общую, шину, шину питания, первую и вторую входную и выходную шины, инвертор на первом МДП-транзисторе обогащенного типа, в цепь стока которого включены последовательно второй МДП-транзистор обедненного типа, и третий МДП-транзистор обогащенного типа, затворы первого и второго МДП-транзисторов инвертора объединены и подключены к первой входной шине, выходной каскад на первом и втором ДП-транзисторах обогащенного типа, первый из которых шунтирован третьим МДП-транзистором обедненного типа в диодном включении, исток третьего МДП-транзистора инвертора подключен к затвору первого МДП-транзистора выходного каскада, а его сток через конденсатор подключен к выходной шине и выходу вы ходного каскада, затвор второго транзистора выходного каскада подключен к входу инвертора и к первой входной шине, отличающ и и с я тем, что, с целью повышения быстродействия и снижения потребляемой мсщности, в него введен дополнительный МДП-транзистор обедненного типа, исток которого подключен ко второй входной шине, сток к затвору третьего МДП-транзистора инвертора, а затвор - к первой входной шине. 2. Формирователь по п. 1, отличающийся тем, что в качестве третьего МДП-транзистора инвертбра использован МДП-транзистор обедненного типа. Источники информации, принятые во внимание при экспертизе 1.Синтегральные схемы на МДПтранзисторах. Под ред. А.Н. Кармазинского. Мир, 1975, с. 229. 2.Патент США № 4071783, л. 307-246, 04.11.76.

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Формирователь импульсов | 1980 |

|

SU919062A1 |

| Формирователь импульсов | 1987 |

|

SU1431054A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Формирователь импульсов | 1981 |

|

SU991507A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Формирователь импульсов на МДП-транзисторах | 1982 |

|

SU1172003A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

Авторы

Даты

1982-03-07—Публикация

1980-03-28—Подача