Изобретение относится к импульсой технике и может быть использовано в цифровых интегральных микрохемах на МДП-транзисторах,

Известен формирователь импуль-5

ов, состоящий из двух инверторов общим входом, причем затвор нагрузочного транзистора выходного нвертора соединен с выходом первого инвертора Л.О

Однако устройство характеризуется значительной мощностью, потребяемой в статическом режиме при уровне входного напряжения, соответствующем логической единице..15

Известен также формирователь, одержащий первый инвертор на трех ДП-транзисторах, затвор первого транзистора первого инвертора соеинен с входной щиной, в цепь стока 20 первого транзистора первого инвертора включены последовательно второй и третий МДП-транзисторы, сток второго транзистора первого инвертора через конденсатор соединен25 с.выходной шиной, второй инвертор на первом НЦП-транзисторах обогащенного типа, исток первого транзистора второго инвертора соединен с общей шИной, сток - с выходной шиной зо а затвор - с входной шиной, исток второго транзистора соединен с выходной шиной, а затвор соединен с затвором второго транзистора первого инвертора и через конденсатор ,г с его истоком, управляющий каскад, представляющий собой третий инвертор, вход которого соединен с затвором второго транзистора второго инвертора, заряжающий транзистор в до диодном режиме, -сток которого соединен с щиной питания Yj,

Однако этот формирователь также обладает большой потребляемой мощностью и сложным управлением (не- 45 обходимо три управляющих сигнала). . Наиболее близким к предлагаемо- му по -технической сущности и достигаемому результату является фор- , мирователь импульсов, содержащийJQ

общую шину, шину питания, первую и вторую входные шины, выходную шину, первый -инвертор на первом МДП-транзисторе обогащенного типа, в цепь стока которого включены последова- 55 тельно второй МДП-транзистор обогащенного типа и третий .МДП-транзистор обедненного типа, затворы первого и

третьего МДП-транзисторов первого ин вёртора объединены и подключены к первой входной шине, выходной каскад, представляющий второй инвертор на двух МДП-транзисторах обогащенного типа, первьй из которых шунтирован третьим МДП-транзистором обогащенного типав диодном включении, исток второго МДП-транзистора первого инвертора подключен к затвору первого МДП-транзистора выходного каскада, затвор второго транзистора выходного каскада подключен к выход первого инвертора и к входной шине, МДП-транзистор обедненного типа, исток которого подключен к второй входной шине, сток - к затвору второго МДП-транзистора первого инвертора, а затвор- - к первой входной шине.

Однако известный формирователь обладает низким .быстродействием и недостаточной нагрузочной способностью.

Цель изобретения - повьтение быстродействия формирователя импульсов при увеличении его нагрузочной способности,

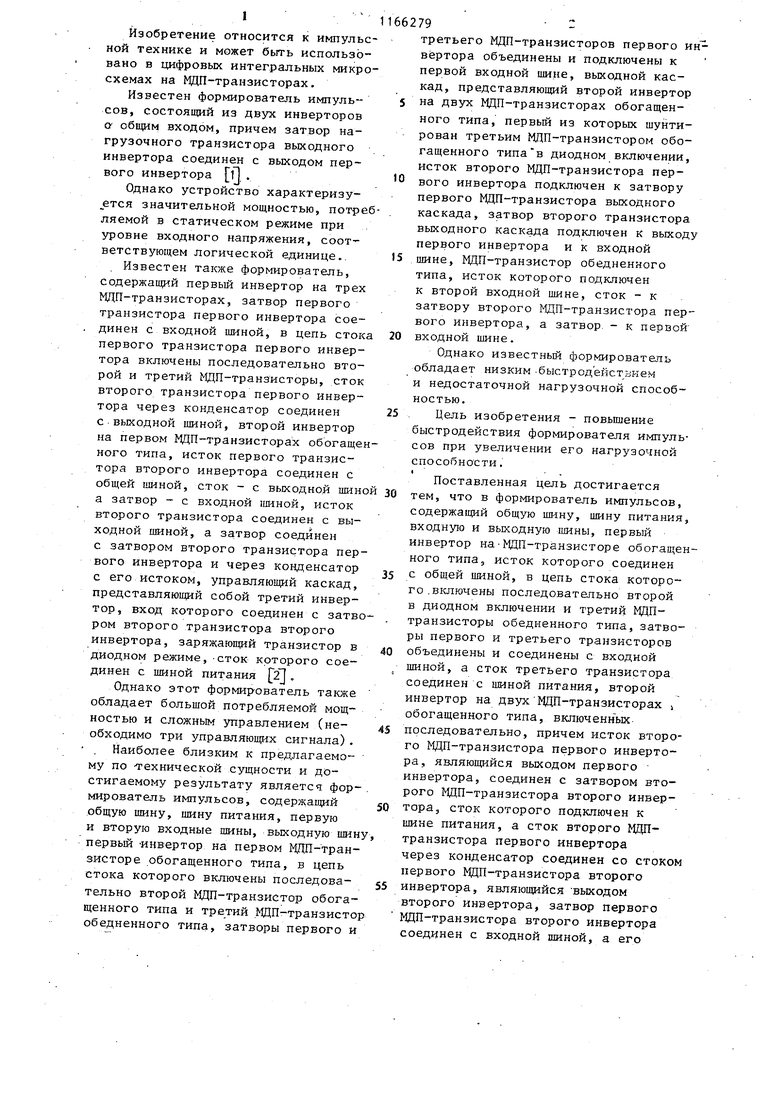

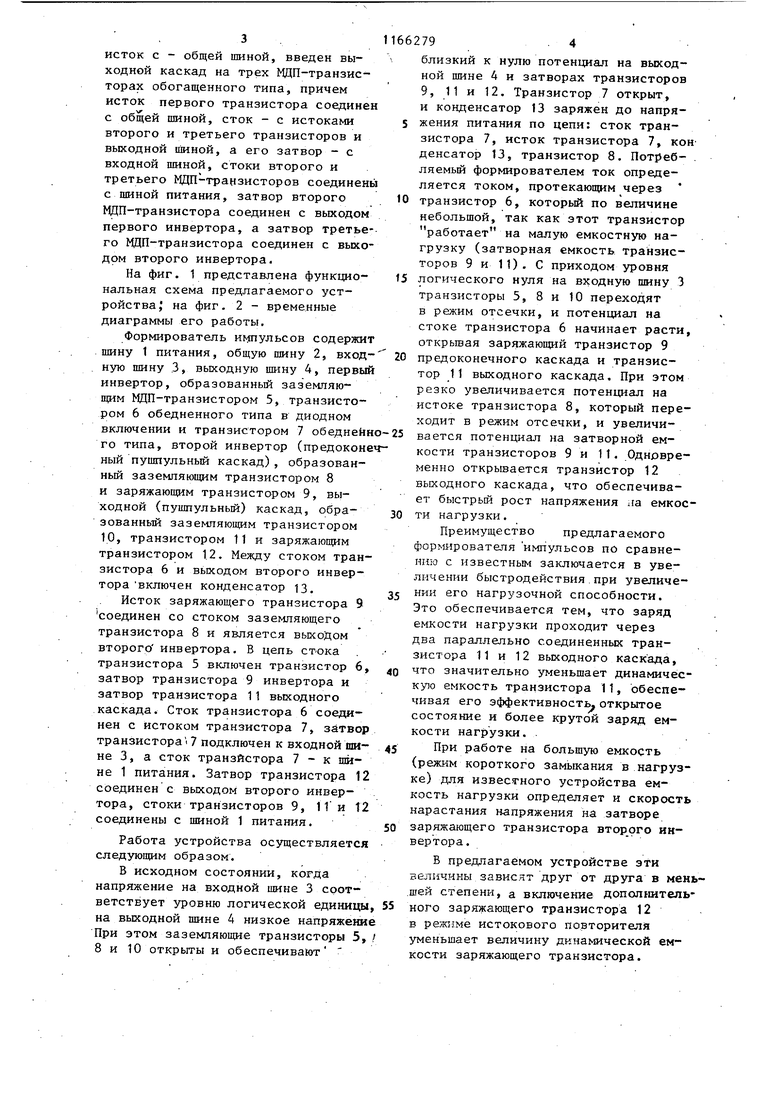

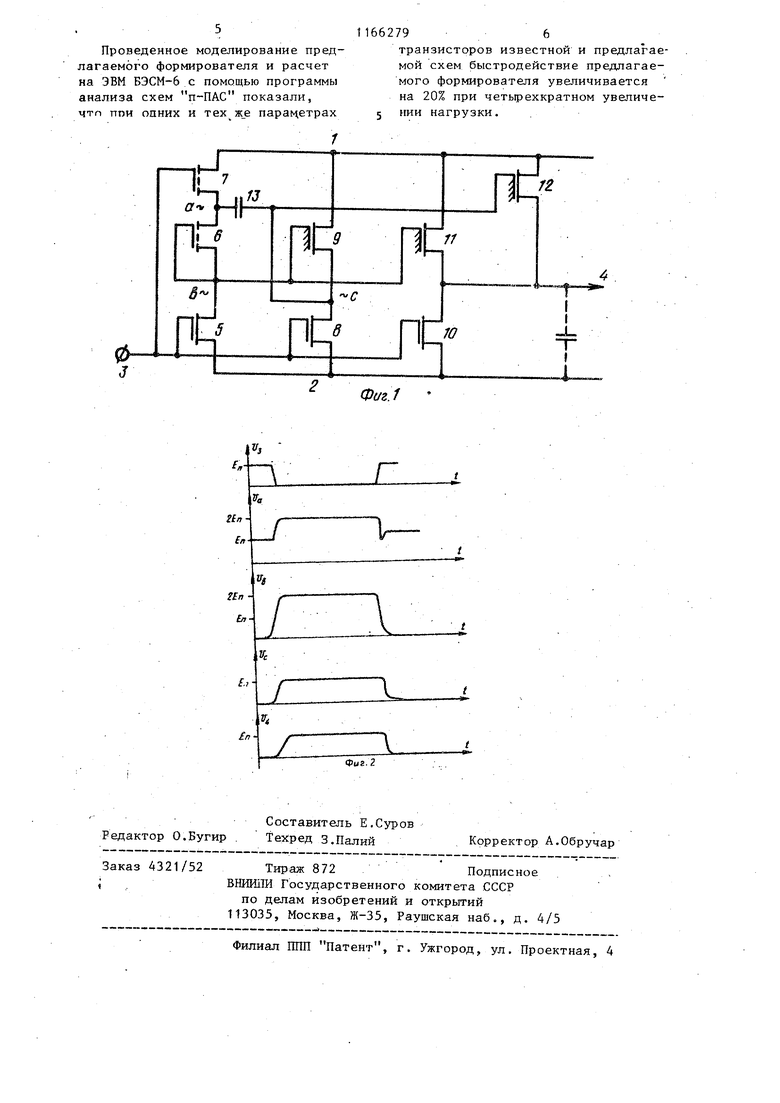

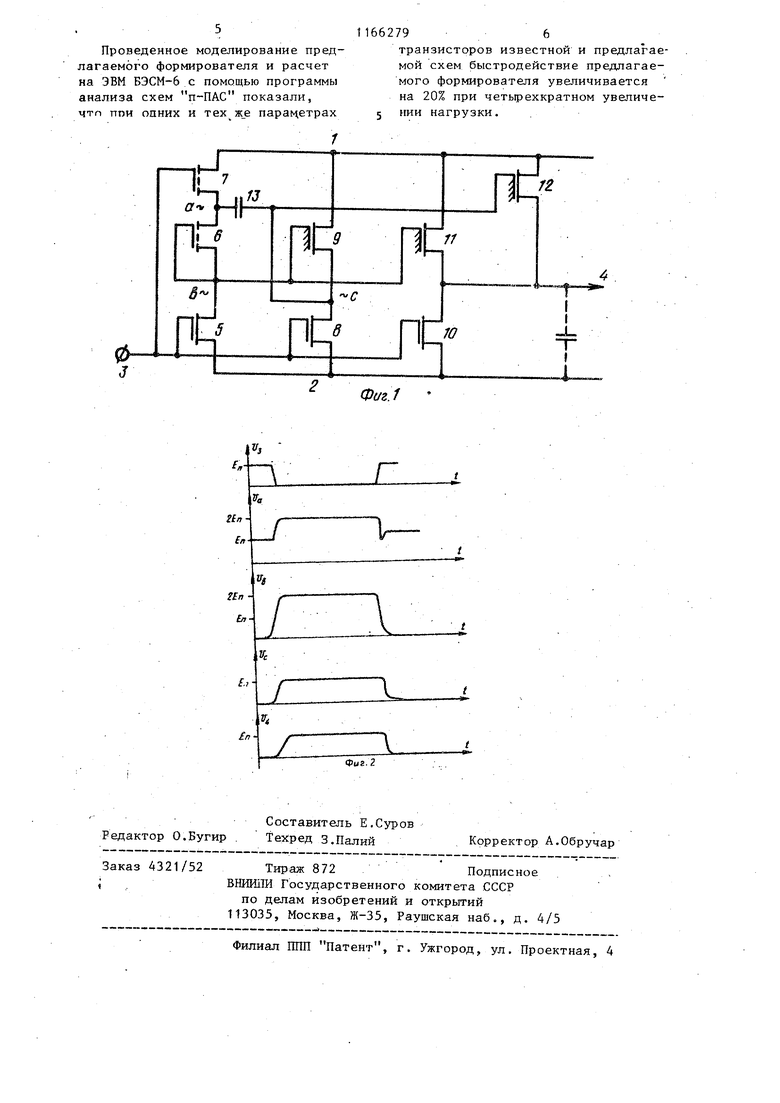

Поставленная цель достигается тем, что в формирователь импульсов, содержащий общую шину, шину питания входную и выходную шины, первый инвертор на-НЦП-транзисторе обогащеного типа, исток которого соединен с обш.ей шиной, в цепь стока которого .включены последовательно второй в диодном включении и третий МДПтранзисторы обедненного типа, затворы первого и третьего транзисторов объединены и соединены с входной пшной, а сток третьего транзистора соединен с шиной питания, второй инвертор на двухВДП-транзисторах i обогащенного типа, включеннЪкпоследовательно, причем исток второго МДП-транзистора первого инвертора, являющимися выходом первого инвертора, соединен с затвором второго МДП-транзистора второго инвертора, сток которого подключен к шине питания, а сток второго МДПтранзистора первого инвертора через конденсатор соединен со стоко первого МДП-транзистора второго инвертора, являющийся выходом второго инвертора, затвор первого ЩП-транзистора второго инвертора соединен с входной щиной, а его исток с - общей шиной, введен выходной каскад на трех ЩП-транзисторах обогащенного типа, причем исток первого транзистора соедине с общей шиной, сток - с истоками второго и третьего транзисторов и выходной шиной, а его затвор - с входной шиной, стоки второго и третьего МДП-транзисторов соединен с шиной питания, затвор второго НЦП-транзистора соединен с выходом первого инвертора, а затвор третье го МДП-транзистора соединен с выхо дом второго инвертора. На фиг. 1 представлена функциональная схема предлагаемого устройства J на фиг. 2 - временные диаграммы его работы. Формирователь иктульсов содержи шину 1 питания, общую шину 2, вход ную шину .3 выходную шину 4, первы инвертор, образованный заземляющим МДП-транзистором 5, транзистором 6 обедненного типа в диодном включении и транзистором 7 обедней го типа, второй инвертор (предокон ный пушпульный каскад), образованньй заземпяющим транзистором 8 и заряжающим транзистором 9, выходной (пушпульный) каскад, образованный заземляющим транзистором 10, транзистором 11 и заряжающим транзистором 12. Между стоком тран зистора 6 и выходом второго инвертора включен конденсатор 13. Исток заряжающего транзистора 9 соединен со стоком заземляющего транзистора 8 и является выхоДом второго инвертора. В цепь ст-ока транзистора 5 включен транзистор 6 затвор транзистора 9 инвертора и затвор транзистора 11 выходного каскада. Сток транзистора 6 соединен с истоком транзистора 7, зйтво транзистора7 подключен к входной ши не 3, а сток транзистора 7 - к шине 1 питания. Затвор транзистора 1 соединен с выходом второго инвертора, стоки транзисторов 9, 11 и 1 соединены с шиной 1 питания. Работа устройства осуществляетс следующим образом. В исходном состоянии, когда напряжение на входной шине 3 соответствует уровню логической единиц на выходной шине 4 низкое напряжен При этом заземляющие транзисторы 5 8 и 10 открыты и обеспечивают 79.4 близкий к нулю потенциал на выходной шине 4 и затворах транзисторов 9, 11 и 12. Транзистор 7 открыт, и конденсатор 13 заряжен до наиряжения питания по цепи: сток транзистора 7, исток транзистора 7, кон денсатор 13, транзистор 8. Потреб- . ляемьй формирователем ток определяется током, протекающим через транзистор 6, которьй по величине небольшой, так как этот транзистор работает на малую емкостную нагрузку (затворная емкость транзисторов 9 и 11). С приходом уровня логического нуля на входную шину 3 транзисторы 5, 8 и 10 переходят в режим отсечки, и потенциал на стоке транзистора 6 начинает расти, открьшая заряжающий транзистор 9 предоконечного каскада и транзистор 11 выходного каскада. При этом резко увеличивается потенциал на истоке транзистора 8, который переходит в режим отсечки, и увеличивается потенциал на затворной емкости транзисторов 9 и 11. Одновременно открьшается транзистор 12 выходного каскада, что обеспечивает быстрый рост напряжения иа емкости нагрузки. Преимущество предлагаемого формирователя импульсов по сравнению с известным заключается в увеличении быстродействия при увеличении его нагрузочной способности. Это обеспечивается тем, что заряд емкости нагрузки проходит через два параллельно соединенных транзистора 11 и 12 выходного каскада, что значительно уменьшает динамическую емкость транзистора 11, обеспечивая его эффективность открытое состояние и более крутой заряд емкости нагрузки. При работе на большую емкость (режим короткого замыкания в нагрузке) для известного устройства емкость нагрузки определяет и скорость нарастания напряжения на затворе заряжающего транзистора второго инвертора. В предлагаемом устройстве эти величины зависят друг от друга в меньшей степени, а включение дoпoл штeльного заряжающего транзистора 12 в истокового повторителя уменьшает величину динамической емкости заряжающего транзистора.

Проведенное моделирование предлагаемого формирователя и расчет на ЭВМ БЭСМ-6 с помощью программы анализа схем п-ПАС показали, чтп ппи опних и тех парацетрах

11662796

транзисторов известной и предлагаемой схем быстродействие предлагаемого формирователя увеличивается на 20% при четырехкратном увеличе5 НИИ нагрузки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Формирователь импульсов | 1980 |

|

SU919062A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Формирователь импульсов | 1987 |

|

SU1431054A1 |

| Формирователь импульсов | 1981 |

|

SU991507A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Адресный формирователь | 1981 |

|

SU1007133A1 |

| Многофункциональное логическое устройство | 1982 |

|

SU1089761A1 |

| Формирователь импульсов на МДП-транзисторах | 1982 |

|

SU1172003A1 |

ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ, содержащий-общую шину, шину питания, входную и выходную шины, первый ин.вертор на МДП-транзисторе обогащенного типа, исток которого соединен с общей шиной, в цепь стока которого включены последовательно второй в диодном включении и третий МДПтранзисторы обедненного типа, затворы первого и третьего транзисторов объединены и соединены с входной шиной, а сток третьего транзистора соединен с шиной питания, второй инвертор на двух МДП-транзисторах обогащенного типа, включенных последовательно, причем исток второго МДП-транзистора первого инвертора, являющийся выходом первого инвертора, соединен с затвором второго МДП-транзистора второго инвертора, ...сток которого подключен к шине питания, а сток второго МДП-транзистора первого инвертора через конденсатор соединен со стоком первого ОДП-транзистора второго инвертора, явлйющийся выходом второго инвертора, затвор первого МДП-транзистора второго инвертора соединен с входной шиной, а его исток - с общей шиной, отличающийся тем, что, с целью увеличения быстродействия формирователя при увеличении его нагрузочной способности, в него вве(Л ден выходной каскад на трех ЬЩПтранзисторах обогащенного типа, причем исток первого транзистора соединен с общей шиной, сток - с истоками второго и третьего транзисторов и выходной шиной, а его затвор с входной шиной, стоки второго Од и третьего МДП-транзисторов соедиа нены с шиной питания, затвор второto го МДП-транзистора соединен с выЧ ходом первого инвертора, а затвор СО третьего МДП-транзистора соединек с выходом второго инвертора.

Авторы

Даты

1985-07-07—Публикация

1983-12-30—Подача