Изобретение относится к электронике и может быть использовано в импульсных интегральных схемах на МДП-транзисторах.

Цель изобретения - повышение быстродействия усилителя считывания.

В усилителе считывания значительно повышено быстродействие при снижении мощности потребления, так как при достижении на выходе цепочки инверторов разности напряжений, равной порогу МДП- транзистора, сбрасывает импульсная схема усиления и на выходе усилителя устанавливается напряжение, равное напряжению питания. В данной схеме усилителя линейная часть усилителя на цепочке инверторов работает на малом выходном сигнале, т. е. в диапазоне рабочих выходных напряжений сохраняются высокие характеристики по быстродействию и коэффициенту усиления. Длина цепочки ограничена требыемым малым выходным напряжением, тем самым уменьшена потребляемая мош,- ность.

Значительный выигрыш в быстродействии реализуется за счет согласованности работы линейной и импульсной частей усилителя, позволившей получить устойчивость работы схемы в широком диапазоне питающих напряжений в разбросе параметров МДП- транзисторов.

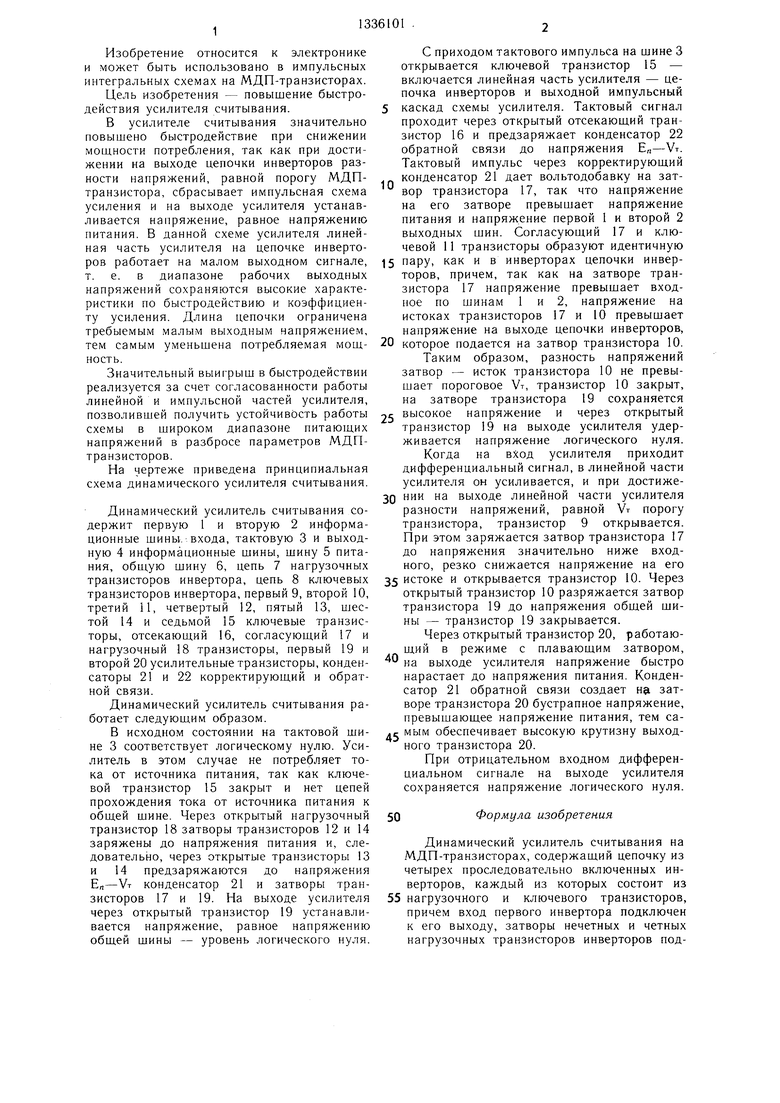

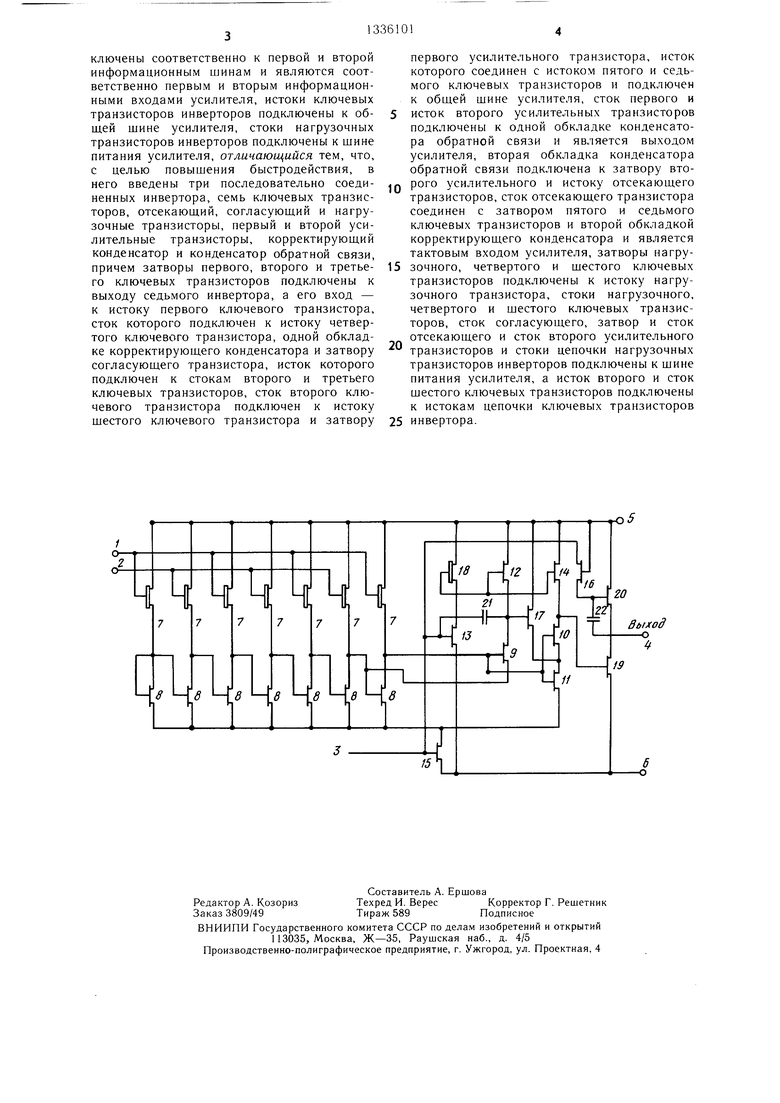

На чертеже приведена принципиальная схема динамического усилителя считывания.

Динамический усилитель считывания содержит первую 1 и вторую 2 информационные шины, .входа, тактовую 3 и выходную 4 информационные шины, шину 5 питания, общую шину 6, цепь 7 нагрузочных транзисторов инвертора, цепь 8 ключевых транзисторов инвертора, первый 9, второй 10, третий 11, четвертый 12, пятый 13, шестой 14 и седьмой 15 ключевые транзисторы, отсекающий 16, согласующий 17 и нагрузочный 18 транзисторы, первый 19 и второй 20 усилительные транзисторы, конденсаторы 21 и 22 корректирующий и обратной связи.

Динамический усилитель считывания работает следующим образом.

В исходном состоянии на тактовой шине 3 соответствует логическому нулю. Усилитель в этом случае не потребляет тока от источника питания, так как ключевой транзистор 15 закрыт и нет цепей прохождения тока от источника питания к общей шине. Через открытый нагрузочный транзистор 18 затворы транзисторов 12 и 14 заряжены до напряжения питания и, следовательно, через открытые транзисторы 13 и 14 предзаряжаются до напряжения Е„-VT конденсатор 21 и затворы транзисторов 17 и 19. На выходе усилителя через открытый транзистор 19 устанавливается напряжение, равное напряжению общей шины - уровень логического нуля.

С приходом тактового импульса на шине 3 открывается ключевой транзистор 15 - включается линейная часть усилителя - цепочка инверторов и выходной импульсный

каскад схемы усилителя. Тактовый сигнал проходит через открытый отсекающий транзистор 16 и предзаряжает конденсатор 22 обратной связи до напряжения Е„-VT. Тактовый импульс через корректирующий конденсатор 21 дает вольтодобавку на затвор транзистора 17, так что напряжение на его затворе превышает напряжение питания и напряжение первой 1 и второй 2 выходных шин. Согласующий 17 и ключевой 11 транзисторы образуют идентичную

5 пару, как и в инверторах цепочки инверторов, причем, так как на затворе транзистора 17 напряжение превышает входное по щинам 1 и 2, напряжение на истоках транзисторов 17 и 10 превышает напряжение на выходе цепочки инверторов,

0 которое подается на затвор транзистора 10. Таким образом, разность напряжений затвор - исток транзистора 10 не превышает пороговое VT, транзистор 10 закрыт, на затворе транзистора 19 сохраняется

5 высокое напряжение и через открытый транзистор 19 на выходе усилителя удерживается напряжение логического нуля. Когда на вход усилителя приходит дифференциальный сигнал, в линейной части усилителя он усиливается, и при достиже0 НИИ на выходе линейной части усилителя разности напряжений, равной VT порогу транзистора, транзистор 9 открывается. При этом заряжается затвор транзистора 17 до напряжения значительно ниже входного, резко снижается напряжение на его

5 истоке и открывается транзистор 10. Через открытый транзистор 10 разряжается затвор транзистора 19 до напряжения общей шины - транзистор 19 закрывается.

Через открытый транзистор 20, работаю- цдий в режиме с плавающим затвором.

0

на выходе усилителя напряжение быстро

нарастает до напряжения питания. Конденсатор 21 обратной связи создает на затворе транзистора 20 бустрапное напряжение, превышающее напряжение питания, тем са- с мым обеспечивает высокую крутизну выходного транзистора 20.

При отрицательном входном дифференциальном сигнале на выходе усилителя сохраняется напряжение логического нуля.

50

Формула изобретения

Динамический усилитель считывания на МДП-транзисторах, содержащий цепочку из четырех проследовательно включенных инверторов, каждый из которых состоит из 55 нагрузочного и ключевого транзисторов, причем вход первого инвертора подключен к его выходу, затворы нечетных и четных нагрузочных транзисторов инверторов подключены соответственно к первой и второй информационным шинам и являются соответственно первым и вторым информационными входами усилителя, истоки ключевых транзисторов инверторов подключены к общей шине усилителя, стоки нагрузочных транзисторов инверторов подключены к шине питания усилителя, отличающийся тем, что, с целью повышения быстродействия, в него введены три последовательно соединенных инвертора, семь ключевых транзисторов, отсекаюш,ий, согласующий и нагрузочные транзисторы, первый и второй усилительные транзисторы, корректирующий конденсатор и конденсатор обратной связи, причем затворы первого, второго и третьего ключевых транзисторов подключены к выходу седьмого инвертора, а его вход - к истоку первого ключевого транзистора, сток которого подключен к истоку четвертого ключевого транзистора, одной обкладке корректирующего конденсатора и затвору согласующего транзистора, исток которого подключен к стокам второго и третьего ключевых транзисторов, сток второго ключевого транзистора подключен к истоку щестого ключевого транзистора и затвору

первого усилительного транзистора, исток которого соединен с истоком пятого и седьмого ключевых транзисторов и подключен к общей шине усилителя, сток первого и

исток второго усилительных транзисторов подключены к одной обкладке конденсатора обратной связи и является выходом усилителя, вторая обкладка конденсатора обратной связи подключена к затвору второго усилительного и истоку отсекающего транзисторов, сток отсекающего транзистора соединен с затвором пятого и седьмого ключевых транзисторов и второй обкладкой корректирующего конденсатора и является тактовым входом усилителя, затворы нагрузочного, четвертого и щестого ключевых транзисторов подключены к истоку нагрузочного транзистора, стоки нагрузочного, четвертого и шестого ключевых транзисторов, сток согласующего, затвор и сток отсекающего и сток второго усилительного транзисторов и стоки цепочки нагрузочных транзисторов инверторов подключены к щине питания усилителя, а исток второго и сток шестого ключевых транзисторов подключены к истокам цепочки ключевых транзисторов

инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Дешифратор | 1989 |

|

SU1644222A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

Изобретение относится к области электроники и может быть использовано в импульсных интегральных схемах на МДП- транзисторах. Цель изобретения - повышение быстродействия при снижении потребляемой мощности. Быстродействие обеспечивается срабатыванием импульсной схемы усиления за счет разности напряжений на выходе цепочки инверторов, равной пороговому напряжению МДП-транзистора. На выходе усилителя устанавливается напряжение, равное напряжению питания. Значительный выигрыш в быстродействии реализуется за счет согласованности работы линейной и импульсной частей усилителя, позволившей получить устойчивость работы схемы в широком диапазоне питающих напряжений и разбросе параметров МДП-транзисторов. 1 ил. 00 со О5

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| СПОСОБ ПОЛУЧЕНИЯ СМЕШАННОГО КОАГУЛЯНТА ДИГИДРОКСОХЛОРИДА АЛЮМИНИЯ И ФЛОКУЛЯНТА КРЕМНИЕВОЙ КИСЛОТЫ | 2011 |

|

RU2458945C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-29—Подача