рассогласования предыдущей группы, выходы первых блоков фиксации временного рассогласования в К-группе с второй по (|1-2)-ю соединены с шестыми входами первых блоков фиксации временного рассогласования в группе fe + 1 , выход первого блока фиксации временного рассогласования первой группы соединен с пятыми входами всех блоков фиксации временного рассогласования второй группы, второй вход первого блока фиксации временного рассогласования первой группы соединен с выходом второго рециркулятора, а выход п-го рец1фкулятора соединен с вторым входом блока фиксации в1)еменного рассогласования (п-О-й группы,

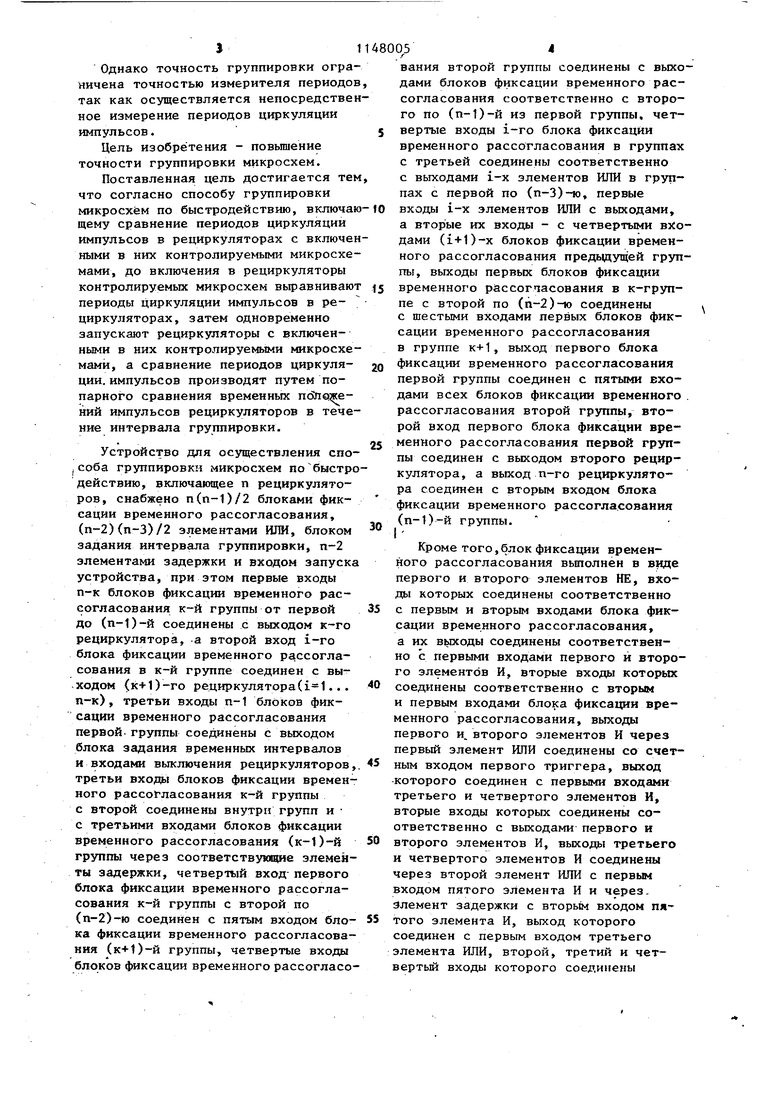

3. Устройство по п. 2, о т л ичающееся тем, что блок фиксации временного рассогласования выполнен в виде первого и второго эдементов НЕ, входы которых соединены соответственно с первым и вторым входами блока фиксации временного рассогласования, а их выходы соединены соответственно с входами первого и второго элементов И, вторые входы которых соединены соответственно с вторым и первым входами блока фиксации временного рассогласования, выходы первого и второго элементов И через первый элемент ИЛИ соединены .со счетным входом первого триггера, выход которого соединен с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с выходами первого и второго элементов И, выходы третьего и четвертого элементов И соединены через второй элемент ИЛИ -с первым входом пятого элемента И и через элемент -задержки с вторым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второйj третий и четвертый входы которого соединены соответственно с шестик, пятым и четвертым входами блока фиксации временного рассогласования, а выход третьего элемента ИЛИ соединен с входом сброса второго триггера, выход которого соединен с первым входом шестого элемента И, второй вход которого соединен с третьим входом блока фиксации временного рассогласования, а выход соединен с выходом блока фиксации временного рассогласования и входом третьего триггера, выход которого соединен с входом элемента индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

| Способ определения времени задержки распространения сигнала интегральными микросхемами и устройство для его осуществления | 1984 |

|

SU1177761A1 |

| Формирователь импульсов | 1985 |

|

SU1283952A1 |

| Устройство для моделирования систем массового обслуживания | 1990 |

|

SU1758651A1 |

| Устройство для ввода информации | 1988 |

|

SU1539763A1 |

| Устройство для вычисления нормированных статистических моментов случайных процессов | 1986 |

|

SU1385131A2 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Устройство для контроля цифровых систем | 1980 |

|

SU955073A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

1. Способ группировки микросхем по быстродействию, включающий сравнение периодов циркуляции импульсов в рециркуляторах с включенными в них контролируемыми микросхемами, о т л.и чающийся тем, что, с тделью повьшения точности, до включения в рециркуляторы контролируемых микросхем выравнивают периоды циркуляции импульсов в рециркуляторах, затем одновременно запускают рециркуляторы с включенными в них контролируемыми микросхемами, а сравнение периодов циркуляции импульсов производят путем попарного сравнения временных положений импульсов рециркуляторов в течение интервала группировки. 2. Устройство для группировки микросхем по бьютродействию, включающее И рециркуляторов, отличающееся тем, что оно снабжено П()/2 блоками фиксации временного рассогласования, (п-2)(п-3)/2 элементами ИЛИ, блоком задания интервала группировки, П-2 элементами задержки и входом запуска устройства, при этом первые входыh- к блоков фиксации временного рассогласования К-й группы от первой до (п-1)-й соединены с выходом к-го рециркулятора, а второй вход i-го блока фиксации временного рассогласования в К-й группе соединен с выходом (|с + 1) -го рециркулятора (i 1,... ,п-1с), третьи входы п-1 блоков фиксации временного рассогласования первой группы соединены с выходом блока задания временных интервалов и входами выключения рециркуляторов, третьи входы блоков фиксации временного рассогласования K-VL группы С второй соединены внутри групп и с третьими входами блоков фиксации временного рассогласования (К-1)-й грзтпы через соответствующие элементы задержки, четвертый вход первого блока фиксации :времеиного рассогласования -и группы с второй по (п-2)-ю соединен с пятым входом блока фиксации временного рассогласования ()-й группы, четвертые входы блоков фиксации временного; 00 рассогласования второй группы соедио о ел нены с выходами блоков фиксации временного рассогласования соответственно с второго по (п-1)-и из первой группы, четвертые входы -го блока фиксации временного рассогласования в группах с третьей соединены соответственно с выходами 1 -X элементов ИЛИ в группах с первой По (П-З)-ю, первые входы 1-х элементов ИЛИ соединены с выходами, а вто-рые их входы - с четвертыми входами (i+1)-x блоков фиксации временного

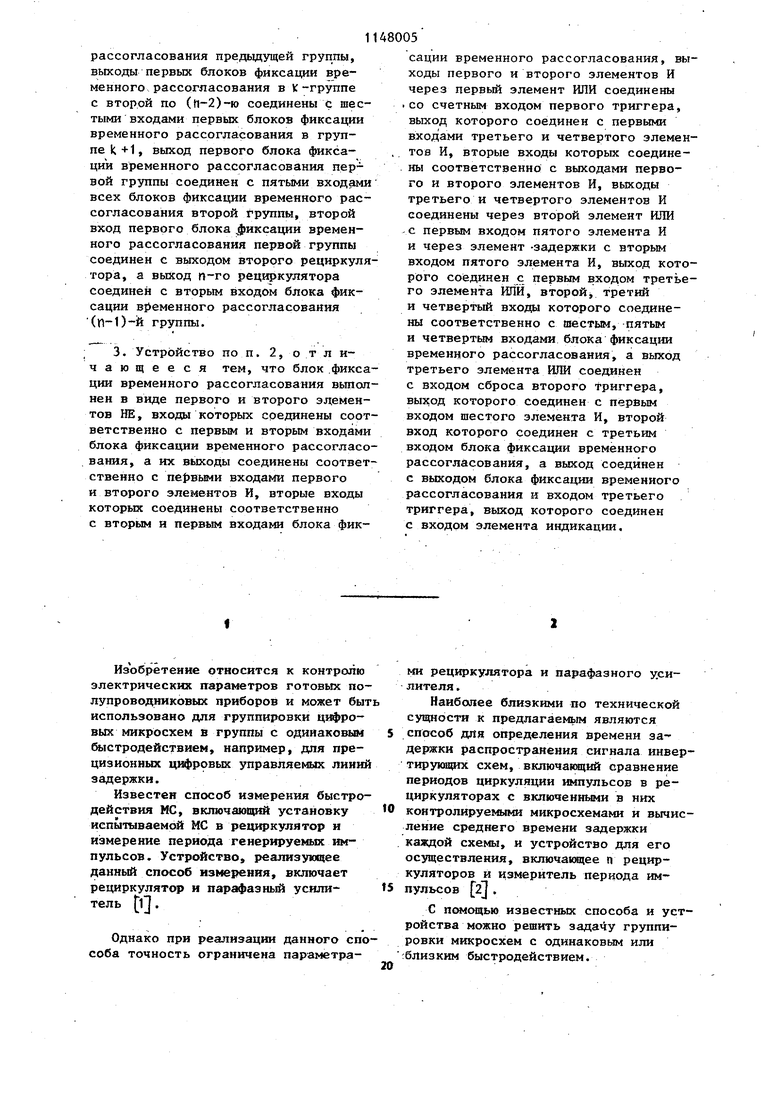

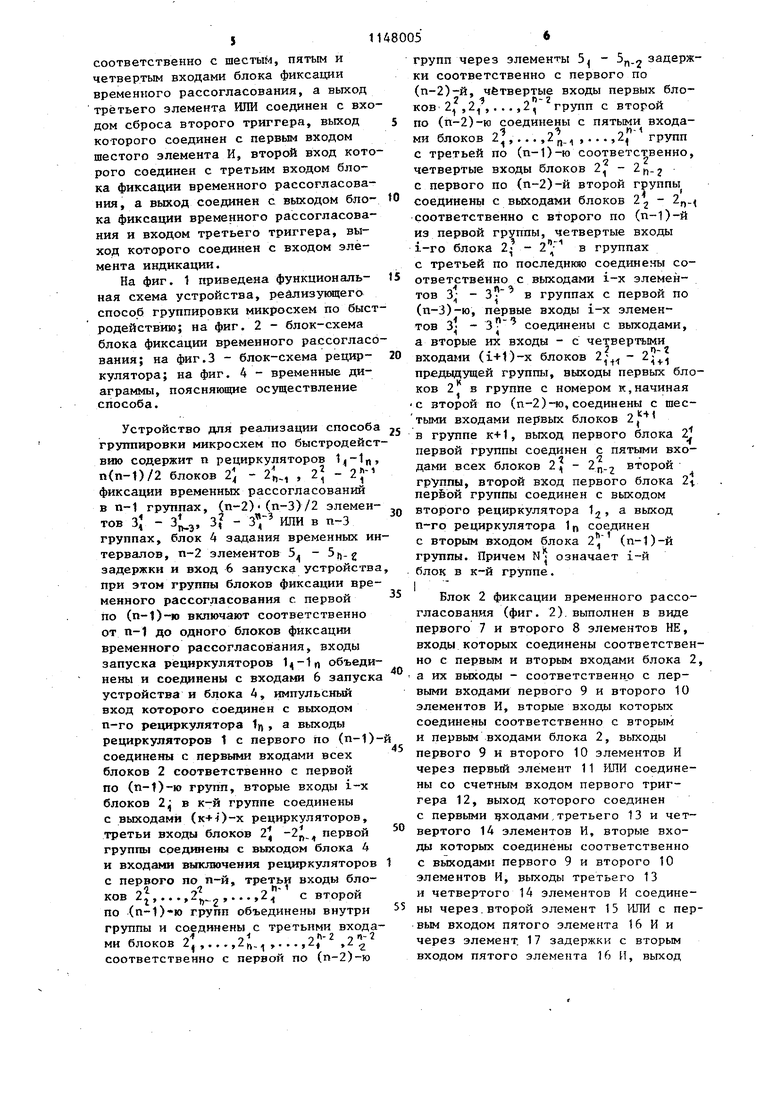

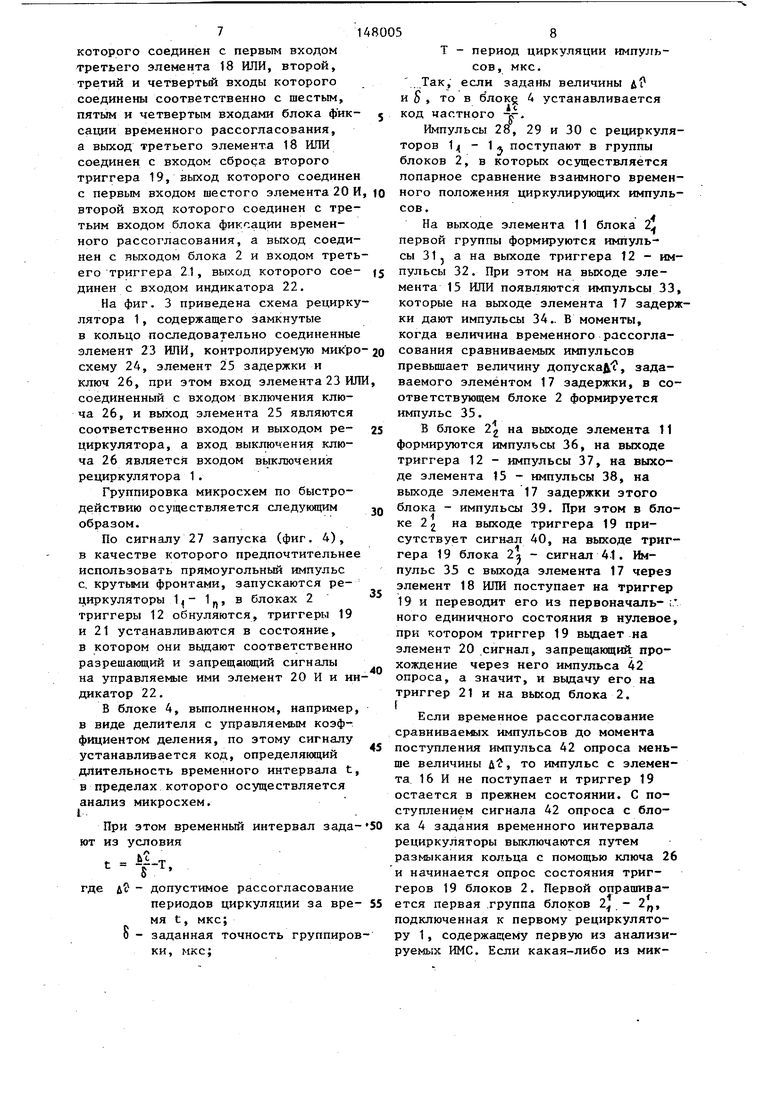

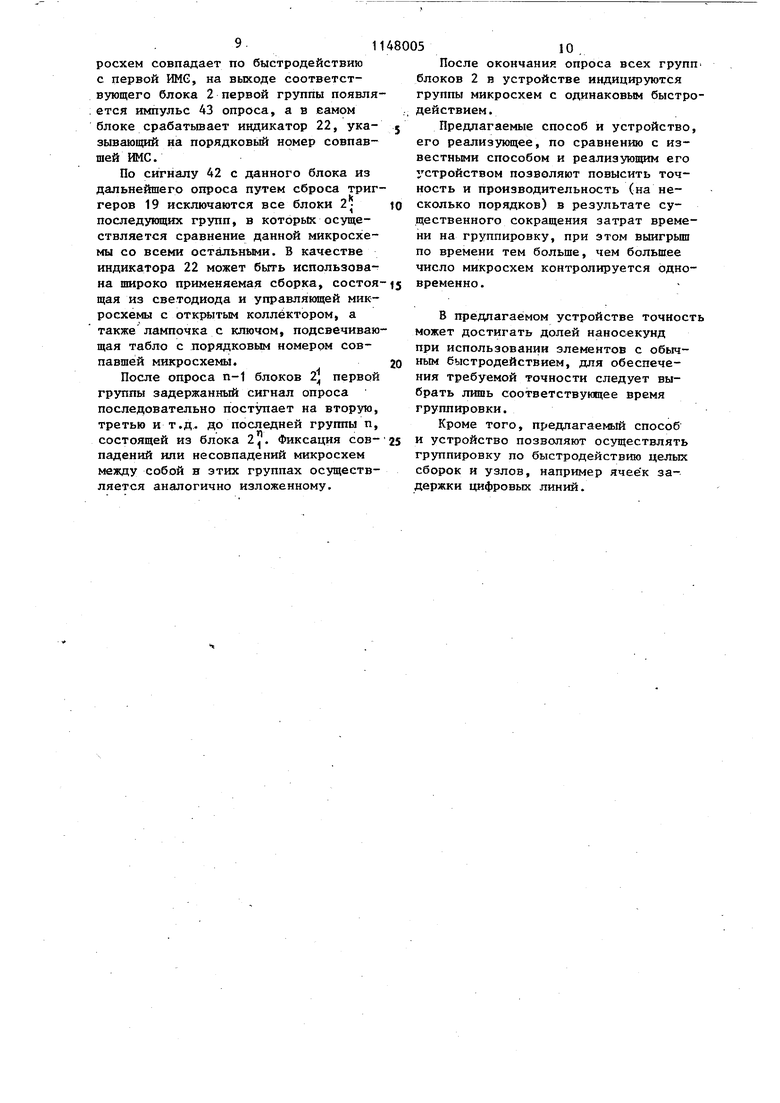

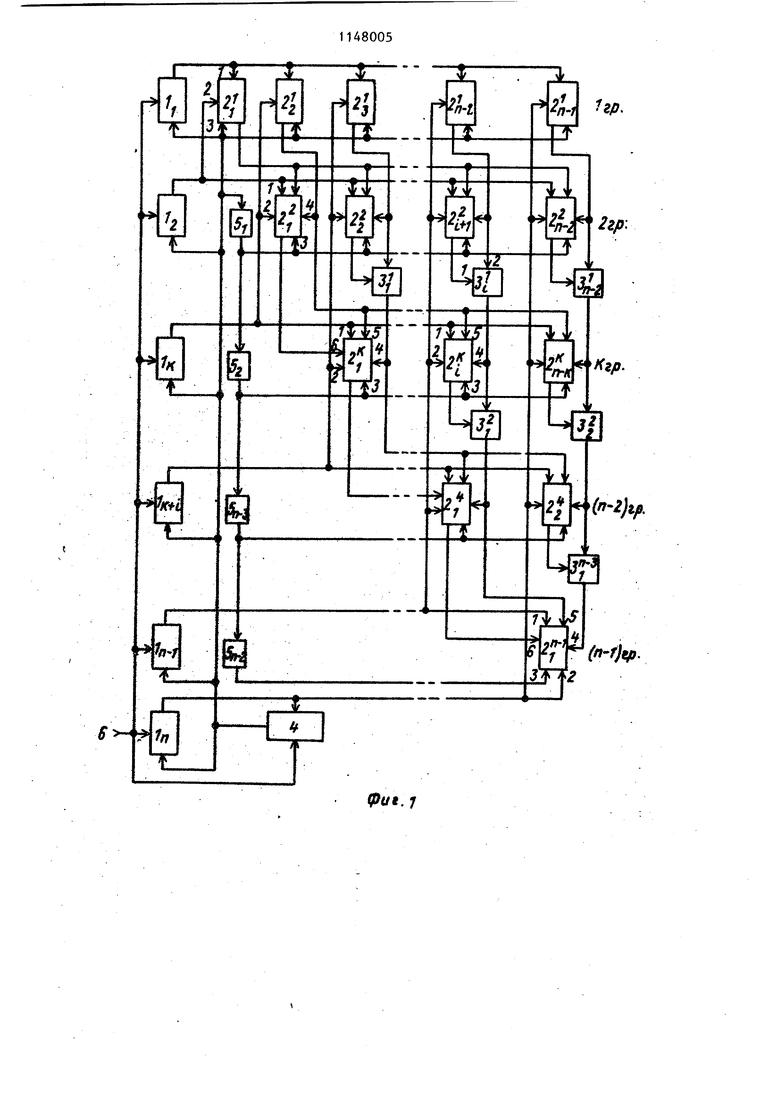

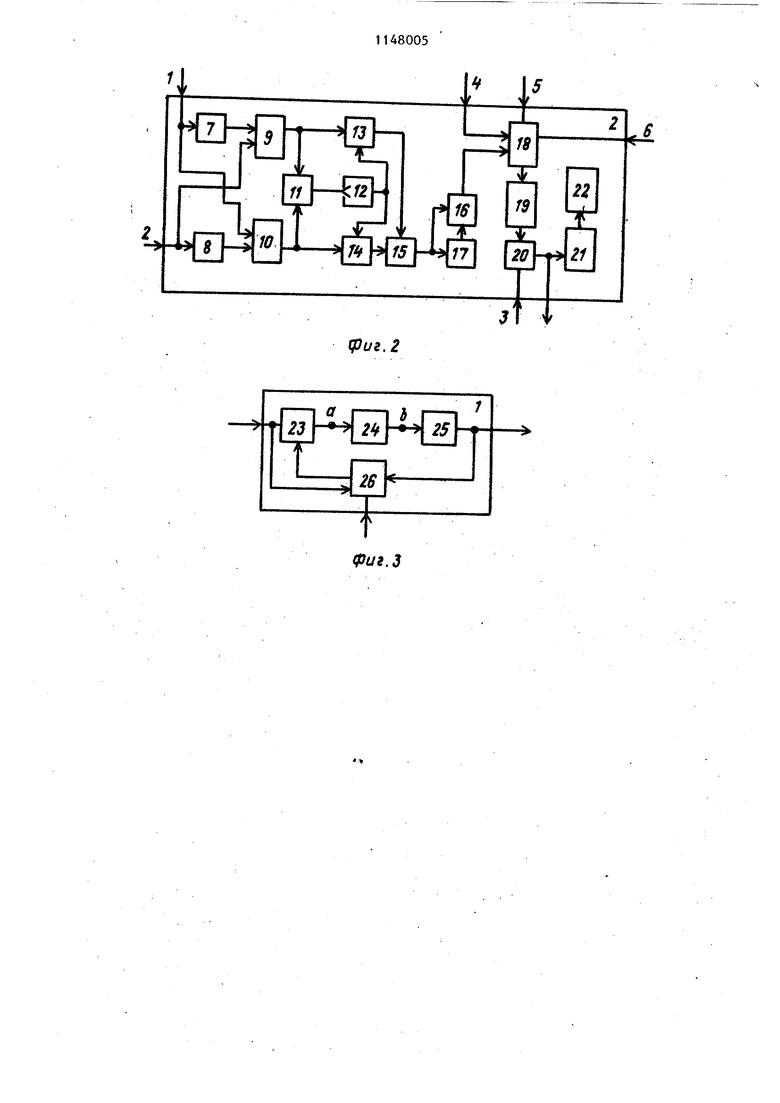

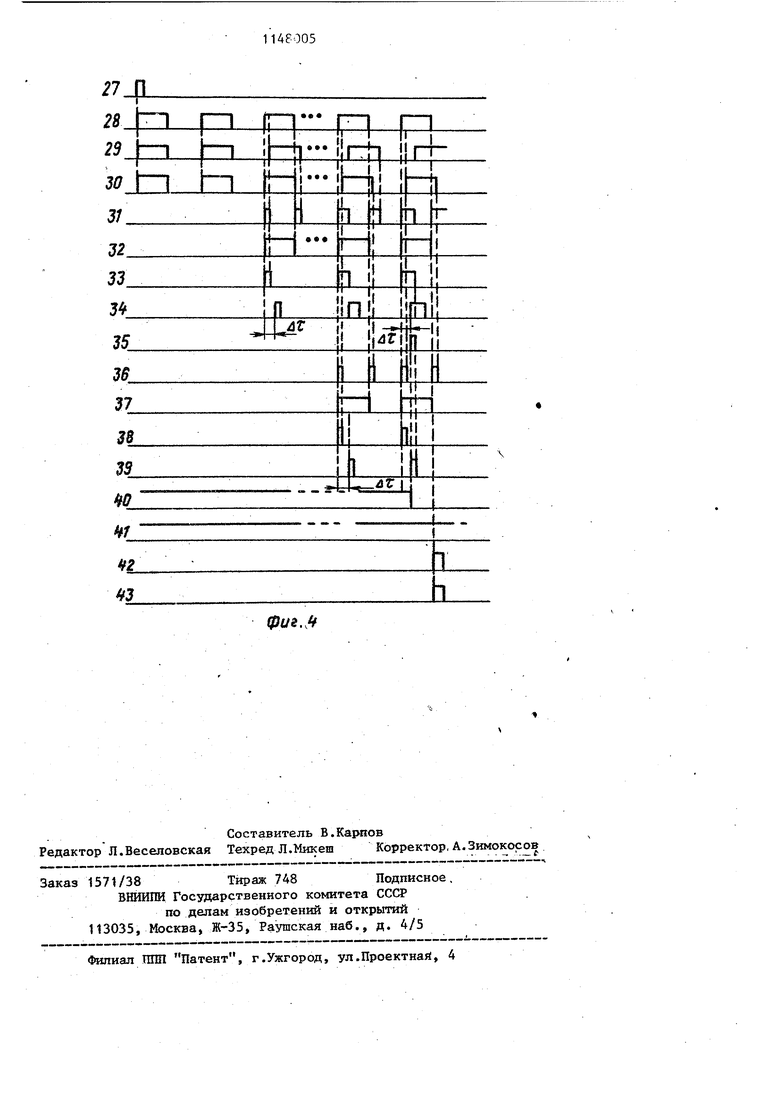

Изобретение относится к контролю электрических параметров готовых полупроводниковых приборов и может быт использовано для группировки цифровых микросхем в группы с одинаковым быстродействием, например, для прецизионных цифровых управляемых линий задержки. Известен способ измерения быстродействия МС, включающий установку испытываемой МС в рециркулятор и измерение периода генерируемых импульсов. Устройство, реализующее данный способ измерения, включает рециркулятор и парафазнь усилитель . Однако при реализации данного спо соба точность ограничена параметрами рециркулятора и парафазного усилителя . Наиболее близкими по технической сущности к предлагаемь1м являются способ для определения времени задержки распространения сигнала инвертирующих схем, включагаций сравнение периодов циркуляции импульсов в рециркуляторах с включенными в них контролируемыми микросхемами и вычисление среднего времени задержки каждой схемы, и устройство для его осуществления, включакяцее п рециркуляторов и измеритель периода импульсов . С помощью известных способа и устройства можно решить задачу группировки микросхем с одинаковым или близким быстродействием. Однако точность группировки огра иичена точностью измерителя периодо так как осуществляется непосредстве ное измерение периодов циркуляции импульсов. Цель изобретения - повьпиенне точности группировки микросхем. Поставленная цель достигается те что согласно способу группировки микросхем по быстродействию, включа щему сравнение периодов циркуляции импульсов в рециркуляторах с включе ными в них контролируемыми микросхе мами, до включения в рециркуляторы контролируемых микросхем вьфавниваю периоды циркуляции импульсов в рециркуляторах, затем одновременно запускают рециркуляторы с включенными в них контролируемыми микросхе мами, а сравнение периодов циркуляции, импульсов производят путем попарного сравнения временных ndJiQ eний импульсов рециркуляторов в тече ние интервала группировки. Устройство для осуществления спо jсоба группировки микросхем по быстр действию, включающее п рециркулято- ров, снабжено п(п-1)/2 блоками фиксации временного рассогласования, (п-2)(п-3)/2 элементами ИЛИ, блоком задания интервала группировки, п-2 элементами задержки и входом запуск устройства, при этом первые входы п-к блоков фиксации временного рассогласования к-й группы от первой до (п-1)-й соединены с выходом к-го рециркулятора, а второй вход i-ro блока фиксации временного рассогласования в к-й группе соединен с выходом (к+1)-го рециркулятора(... п-к), третьи входы п-1 блоков фиксации временного рассогласования первой- группы соединены с выходом блока задания временных интервалов и входами выключения рециркуляторов третьи входь блоков фиксации временного рассогласования к-й группы с второй соединены внутри групп и с третьими входами блоков фиксации временного рассогласования (к-1)-й группы через соответствующие элемейты задержки, четвертый вход первого блока фиксации временного рассогласования к-й группы с второй по (п-2)-ю соединен с пятым входом блока фиксации временного рассогласования (к+1)-й группы, четвертые входы блоков фиксации временного рассогласо0.54 вания второй группы соединены с выходами блоков фиксации временного рассогласования соответственно с второго по (п-1)-и из первой группы, четвертые входы i-ro блока фиксации временного рассогласования в группах с третьей соединены соответственно с выходами i-x элементов ИЛИ в группах с первой по {п-3)-ю, первые входы i-x элементов ИЛИ с выходами, а вторые их входы - с четвертыми входами (i+1)-x блоков фиксации временного рассогласования предьщущей группы, выходы первых блоков фиксации временного рассогласования в к-группе с второй по (п-2)-ю соединены с шестыми входами первых блоков фиксации временного рассогласования в группе к+1, выход первого блока фиксации временного рассогласования первой группы соединен с пятыми входами всех блоков фиксации временного , рассогласования второй грзпппы, второй вход первого блока фиксации временного рассогласования первой группы соединен с выходом второго рецир- кулятора, а выход п-го рециркулятора соединен с вторым входом блока фиксации временного рассогласования (п-1)-й группы. Кроме того,блок фиксации временного рассогласования выполнен в виде первого и второго элементов НЕ, входы которых соединены соответственно с первым и вторым входами блока фиксации временного рассогласования, а их выходы соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с вторым и первым входами блока фиксации вре менного рассогласования, выходы первого и. второго элементов И через первый элемент ИЛИ соединены со счетным входом первого триггера, выход которого соединен с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с выходами первого и второго элементов И, выходы третьего и четвертого элементов И соединены через второй элемент ИЛИ с первым входом пятого элемента И и через. элемент задержки с вторьм входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй, третий и четвертый входы которого соединены соответственно с шестым, пятым и четвертым входами блока фиксации временного рассогласования, а выход третьего элемента ИЛИ соединен с вхо дом сброса второго триггера, выход которого соединен с первым входом шестого элемента И, второй вход кото рого соединен с третьим входом блока фиксации временного рассогласования, а выход соединен с выходом блока фиксации временного рассогласова ния и входом третьего триггера, выход которого соединен с входом элемента индикации. На фиг. 1 приведена функциональная схема устройства, рейлизукщега способ группировки микр1осхем по быс родействию; на фиг. 2 - блок-схема блока фиксации временного рассоглас вания; на фиг.З - блок-схема рециркулятора; на фиг. 4 - временные диаграммы, поясняющие осуществление способа. Устройство для реализации способ группировки микросхем по быстродейс вию содержит п рециркуляторов п(п-1)/2 блоков 2 - 2, ,2 -2;фиксации временных рассогласований в п-1 группах, п-2)(п-3)/2 элемен - 3V или в п-3 3 - V - п-Э группах, блок 4 задания временных и блок 4 тервалов, п-2 элементов 5. - Зц. g задержки и вход 6 запуска устройств при этом группы блоков фиксации вре менного рассогласования с первой по (п-1)-ю включают соответственно от п-1 до одного блоков фиксации временного рассогласования, входы запуска рецнркуляторов объеди нены и соединены с входами 6 запуск устройства и блока А, импульсный вход которого соединен с вькодом п-го рециркулятора Ijj , а выходы рециркуляторов 1 с первого по (п-1) соединены с первыми входами всех блоков 2 соответственно с первой по (п-1)-ю групп, вторые входы i-x блоков 2 в к-й группе соединены с выходами (к+О-х рециркуляторов, третьи входы блоков 2 первой группы соединены с выходом блока А и входами выключения рециркуляторов с первого по п-й, третьи входы блоков 2 ,... ,2 ,... ,2 с второй по (п-1)-ю групп объединены внутри группы и соединены с третьими входа ми блоков 2.,..., 2 ц, ,. .., , 2 соответственно с первой по (п-2)-ю групп через элементы 5 - З. задержки соответственно с первого по (п-2)-й, четвертые входы первых блоков 2 ,2,,. .,,2, групп с второй по (п-2)-ю соединены с пятыми входами блоков 2 , .,., 2 , , . .., 2 групп с третьей по (п-1)-ю соответственно, 0 9 четвертые входы блоков с первого по (п-2)-й второйгруппы соединены с выходами блоков2 - 2„. соответственно с второго по(п-1)-й из первой группы, четвертыевходы i-ro блока в группах с третьей по последнкло соединены соответственно с выходами i-x элементов - в группах с первой по (п-З)-ю, первые входы i-x элемен;1 - соединены с выходами. а вторые их входы - с че твертыми 2 „о-г - 2входами (i+1)-x блоков 2 предьщущей группы, выходы первых блоков 2 в группе с номером к,начиная С второй по (п-2)-та,соединены с шестыми входами первых блоков в группе к+1, выход первого блока 2 первой группы соединен с пятыми вхол л fiat-iK всех блоков 2, - 2f,.2 второй группы, второй вход первого блока 2. пербой группы соединен с выходом второго рециркулятора а выход 2 1п соединен п-го рециркулятора с вторым входом блока (п-1)-и группы. Причем означает i-й блок в к-й группе. Блок 2 фиксации временного рассогласования (фиг. 2). выполнен в виде первого 7 и второго 8 элементов НЕ, входы которых соединены соответственно с первым и вторым входами блока 2, а их выходы - соответственн о с первыми входами первого 9 и второго 10 элементов И, вторые входы которых соединены соответственно с вторым и первым входами блока 2, выходы первого 9 и второго 10 элементов И через первый элемент 11 ИЛИ соединены со счетным входом первого триггера 12, выход которого соединен с первыми уходами,третьего 13 и четвертого 14 элементов И, вторые входы которых соединены соответственно с выходами первого 9 и второго 10 элементов И, выходы третьего 13 и четвертого 14 элементов И соединены через.второй элемент 15 ИЛИ с первым входом пятого элемента 16 И и через элемент. 17 задержки с вторым входом пятого элемента 16 И, выход которого соединен с первым входом третьего элемента 18 ИЛИ, второй, третий и четвертый входы которого соединены соответственно с шестым, пятым и четвертым входами блока фик сации временного рассогласования, а выход третьего элемента 18 ИЛИ соединен с входом сброса второго триггера 19, выход которого соедине с первым входом шестого элемента 20 второй вход которого соединен с тре тьим входом блока фиксации временного рассогласования, а выход соеди нен с выходом блока 2 и входом трет его триггера 21, выход которого сое динен с входом индикатора 22. На фиг. 3 приведена схема рецирк лятора 1, содержащего замкнутые в кольцо последовательно соединенны элемент 23 ИЛИ, контролируемую микр схему 24, элемент 25 задержки и ключ 26, при этом вход элемента 23 И соединенный с входом включения ключа 26, и выход элемента 25 являются соответственно входом и выходом рециркулятора, а вход выключения ключа 26 является входом выключения рецкркулятора 1. Группировка микросхем по быстродействию осуществляется следующим образом. По сигналу 27 запуска (фиг. 4), в качестве которого предпочтительне использовать прямоугольный импульс с. крутьми фронтами, запускаются ре1 , в блоках 2 циркуляторы триггеры 12 обнуляются, триггеры 19 и 21 устанавливаются в состояние, в котором они вьщают соответственно разрешающий и запрещающий сигналы на управляемые ими элемент 20 И и и дикатор 22. В блоке 4, выполненном, например в виде делителя с управляемым коэффициентом деления, по этому сигналу устанавливается код, определяющий длительность временного интервала t в пределах которого осуществляется анализ микросхем. При этом временный интервал зада ют из условия t S - где ut допустимое рассогласование периодов циркуляции за вре мя t, мкс; о - заданная точность группиро ки, мкс; Т - период циркуляции импульсов, мкс. . Так, если заданы величины Дс и S , то в блок 4 устанавливается код частного 4 Импульсы 28, 29 и 30 с рециркуляторов 1 5 поступают в группы блоков 2, в которых осуществляется попарное сравнение взаимного временного положения циркулирующих импульсов. На выходе элемента 11 блока 2 первой группы формируются импульсы 31J а на выходе триггера 12 - импульсы 32. При этом на выходе элемента 15 ИЛИ появляются импульсы 33, которые на вьпсоде элемента 17 задержки дают импульсы 34.. В моменты, когда величина временного рассогласования сравниваемых импульсов превьш1ает величину допускаД, задаваемого элементом 17 задержки, в соответствзпощем блоке 2 формируется импульс 35. В блоке 22 на выходе элемента 11 формируются импульсы 36, на выходе триггера 12 - импульсы 37, на выходе элемента 15 - импульсы 38, на выходе элемента 17 задержки этого блока - импульсы 39. При этом в блоке 2 на выходе триггера 19 при40, на выходе тригсутствует сигнал гера 19 блока 2 - сигнал 41. № пульс 35 с выхода элемента 17 через элемент 18 ИЛИ поступает на триггер 19 и переводит его из первоначаль- ; ного единичного состояния в нулевое, при котором триггер 19 вьщает на элемент 20 сигнал, запрещакмций прохождение через него импульса 42 опроса, а значит, и выдачу его на триггер 21 и на выход блока 2. Если временное рассогласование сравниваемых импульсов до момента поступления импульса 42 опроса меньше величины U, то импульс с элемента. 16 И не поступает и триггер 19 остается в прежнем состоянии. С поступлением сигнала 42 опроса с блока 4 задания временного интервала рециркуляторы выключаются путем размыкания кольца с помощью ключа 26 и начинается опрос состояния триггеров 19 блоков 2. Первой опрашивается первая группа блоков 2 - 2, подключенная к первому рециркулятору 1, содержащему первую из анализируемых ИМС. Если какая-либо из микросхем совпадает по быстродействию с первой ИМС, на выходе соответствующего блока 2 первой группы появля ется импульс 43 опроса, а в еамом блоке срабатьшает индикатор 22, указывающий на порядковый номер совпавшей ШС. По сигналу 42 с данного блока из дальнейшего опроса путем сброса триг геров 19 исключаются все блоки 2 последующих групп, в которь1х осуществляется сравнение данной микросхемы со всеми остальными. В качестве индикатора 22 может быть использована широко применяемая сборка, состоя щая из светодиода и управляющей микросхемы с открытым коллектором, а также лампочка с ключом, подсвечиваю щая табло с порядковым номером совпавшей микросхемы. После опроса п-1 блоков 2 первой группы задержанный сигнал опроса последовательно поступает на вторую третью и т.д. до последней группы п состоящей из блока 2. Фиксация совпадений или несовпадений микросхем между собой н этих группах осуществляется аналогично изложенному. После окончания опроса всех групп блоков 2 в устройстве индицируются группы микросхем с одинаковым быстродействием. Предлагаемые способ и устройство, его реализующее, по сравнению с известными способом и реализующим его устройством позволяют повысить точность и производительность (на несколько порядков) в результате существенного сокращения затрат времени на группировку, при этом выигрьш по времени тем больше, чем большее число микросхем контролируется одновременно. В предлагаемом устройстве точность может достигать долей наносекунд при использовании элементов с обычным быстродействием, для обеспечения требуемой точности следует выбрать лишь соответствующее время группировки. Кроме того, предлагаемый способ и устройство позволяют осуществлять группировку по быстродействию целых сборок и узлов, например ячеек задержки цифровых линий.

Фu.

(риг. 2

фиг.З

U.tf

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| , 2 | |||

| Способ определения времени задержки распространения сигнала инвертитующих схем | 1973 |

|

SU473959A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| « | |||

Авторы

Даты

1985-03-30—Публикация

1983-04-12—Подача