го ел

|й

Изобретение относится к вычислительной технике и может быть использовано в системах передачи данных с избыточным кодированием.

Цель изобретения - расширение функциональных возможностей путем автоматизации формирования квазициклических кодов заданных длины и веса

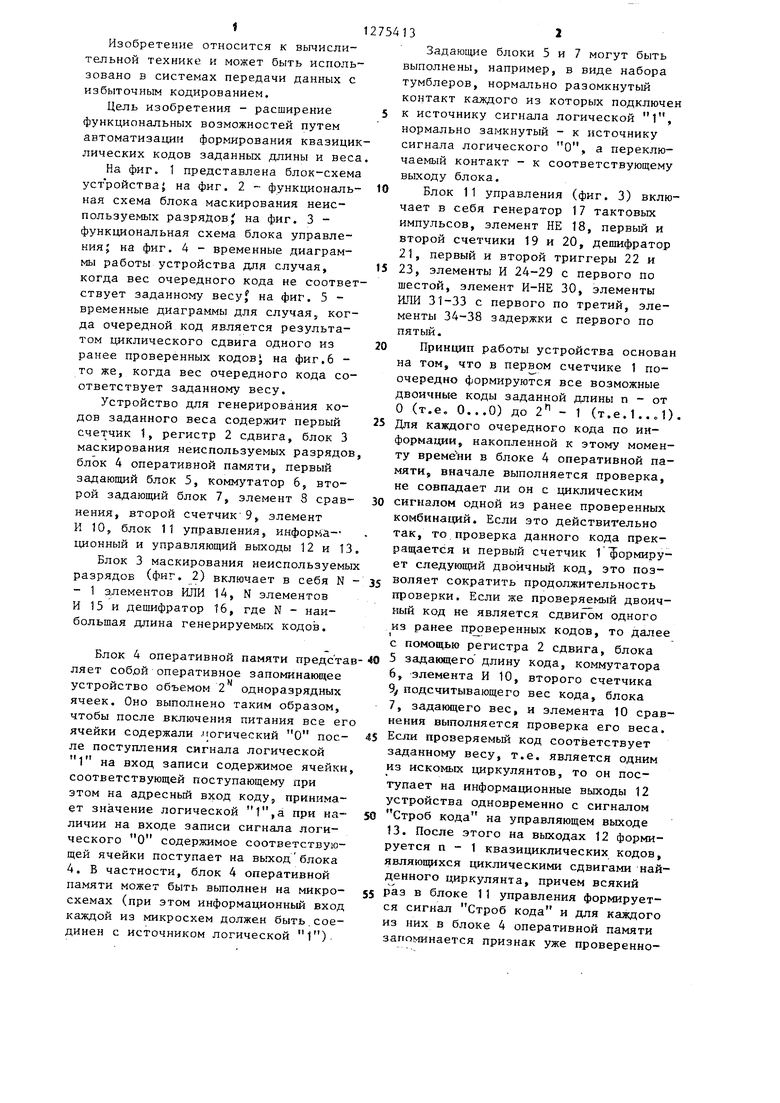

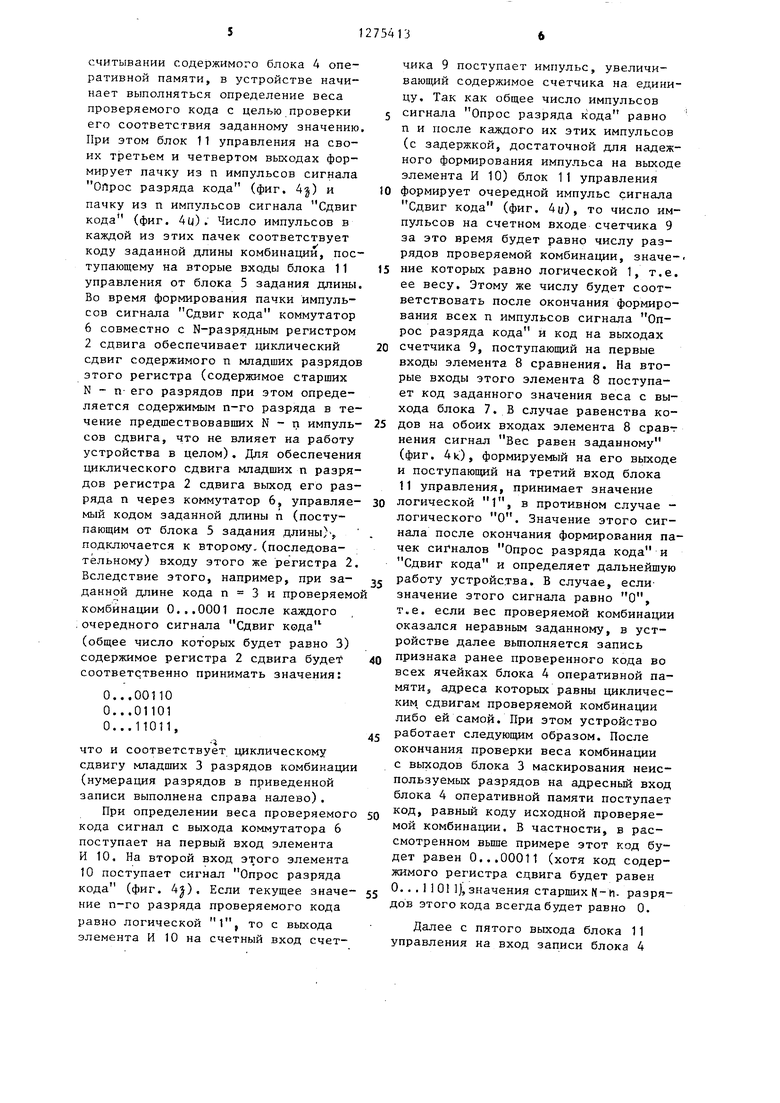

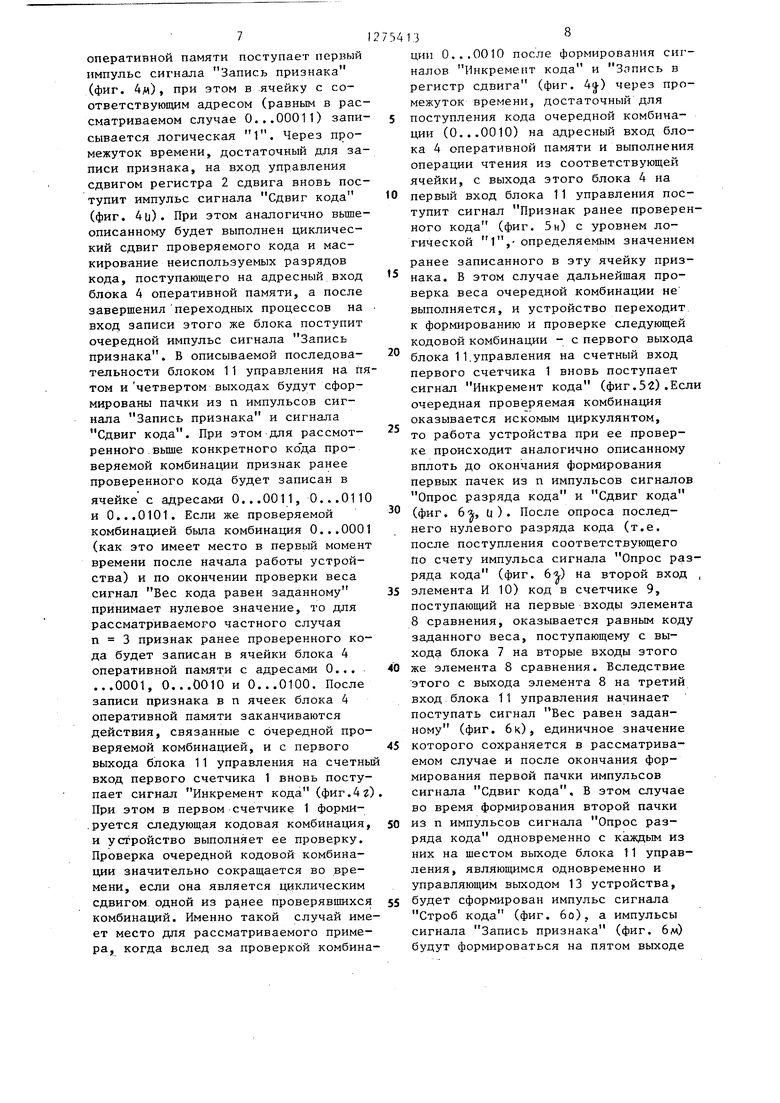

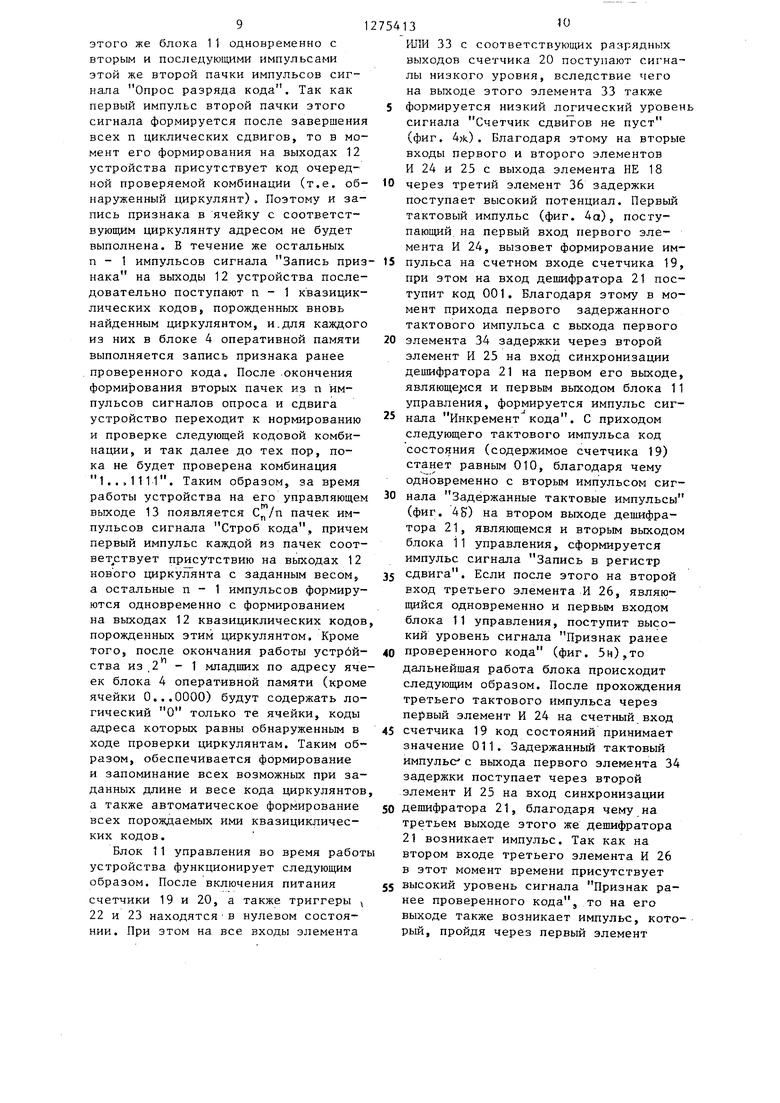

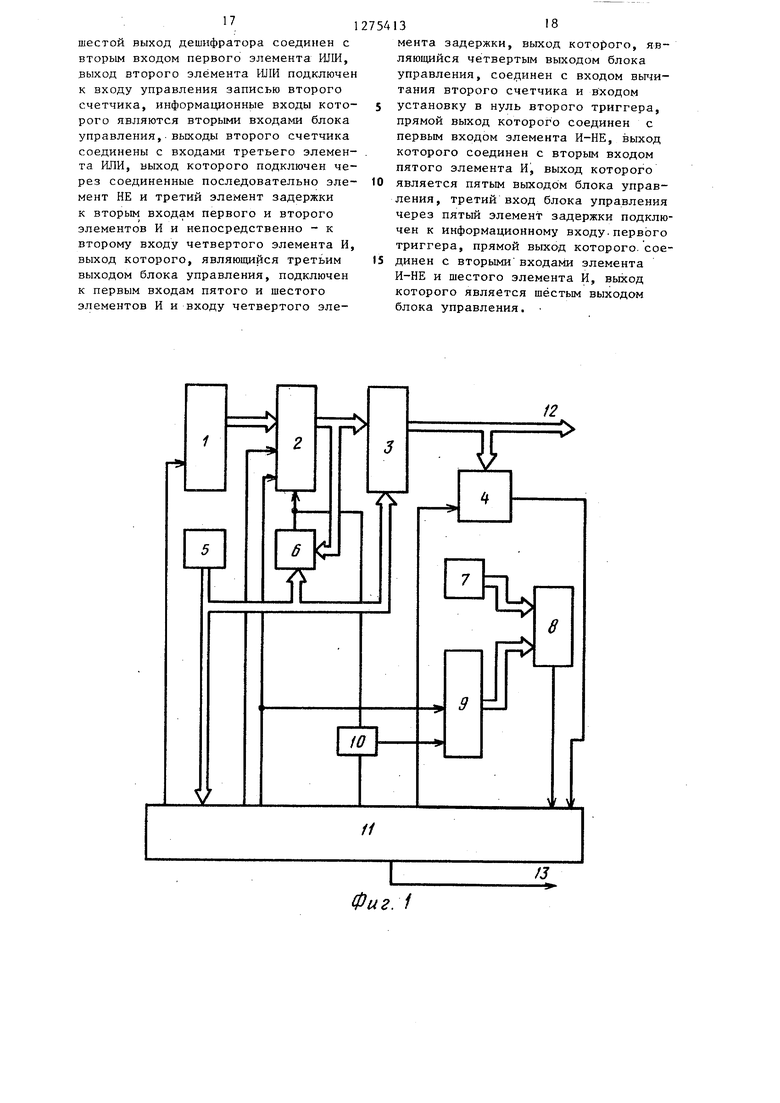

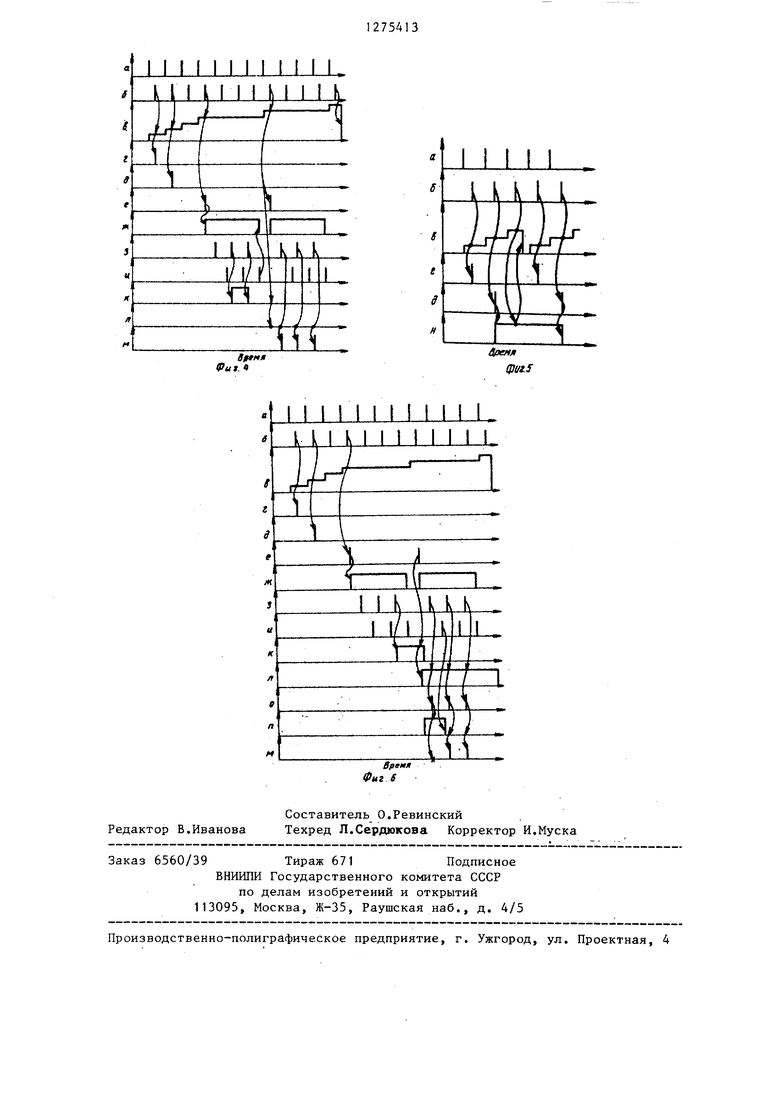

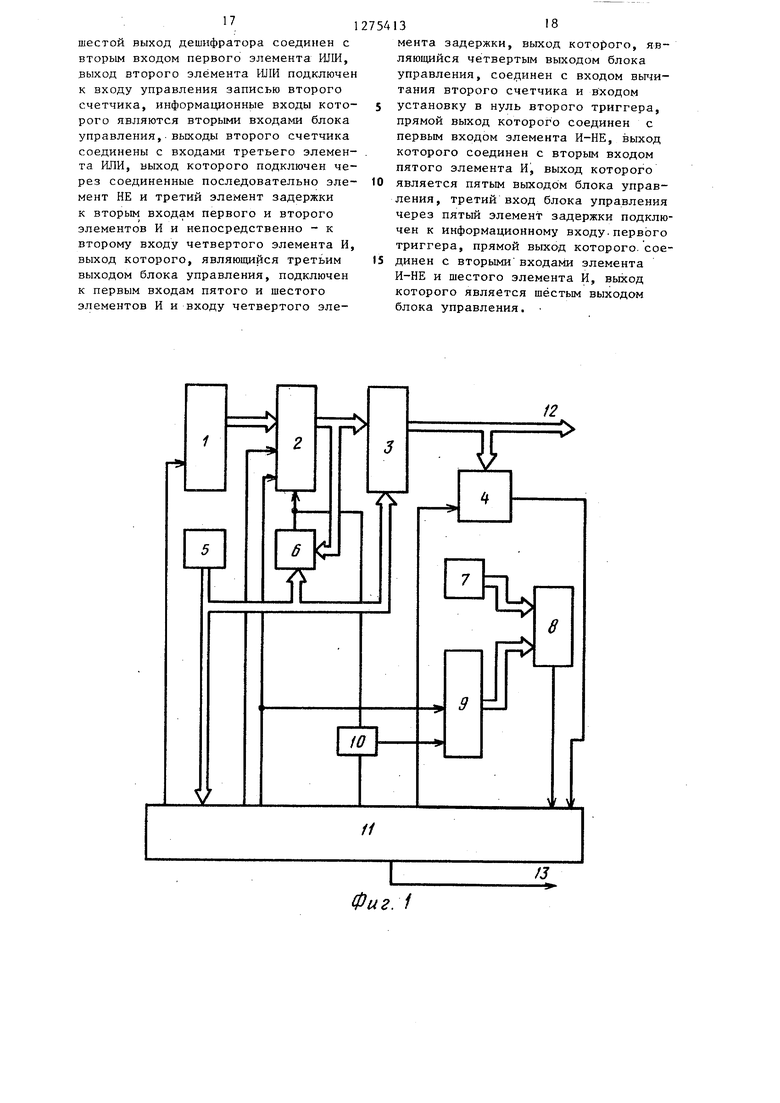

На фиг. 1 представлена блок-схема устройстваJ на фиг. 2 функциональнал схема блока маскирования неиспользуемых разрядов на фиг. 3 функциональная схема блока управления; на фиг, 4 - временные диаграммы работы устройства для случая, когда вес очередного кода не соответствует заданному BecyJ на фиг. 5 временные диаграммы для случая, когда очередной код является результатом циклического сдвига одного из ранее проверенных кодовJ на фиг,6 то же, когда вес очередного кода соответствует заданному весу.

Устройство для генерирования кодов заданного веса содержит первый счетчик 1, регистр 2 сдвига, блок 3 маскирования неиспользуемых разрядов блок 4 оперативной памяти, первый задающий блок 5, коммутатор 6, второй задающий блок 7, элемент 3 сравнения, второй счетчик9, элемент И 10, блок 11 управления, инфop 4a- ционный и управляющий выходы 12 и 13

Блок 3 маскирования неиспользуемы разрядов (фиг. 2) включает в себя N - 1 элементов ИЛИ 14, N элементов И 15 и дешифратор 16, где N - наибольшая длина генерируемых кодов.

Блок 4 оперативной памяти предста ляет собой оперативное запоминающее устройство объемом 2 одноразрядных ячеек. Оно выполнено таким образом, чтобы после включения питания все ег ячейки содержали ,югический О после поступления сигнала логической Г на вход записи содержимое ячейки соответствующей поступающему при этом на адресный вход коду, принимает значение логической 1,а при наличин на входе записи сигнала логического О содержимое соответствующей ячейки поступает на выходблока 4. В частности, блок 4 оперативной памяти может быть выполнен на микросхемах (при этом информационный вход каждой из микросхем должен быть,соединен с источником логической 1).

132

Задающие блоки 5 и 7 могут быть выполнены, например, в виде набора тумблеров, нормально разомкнутый контакт каждого из которьпс подключен к источнику сигнала логической 1, нормально замкнутый - к источнику сигнала логического О, а переключаемый контакт - к соответствующему выходу блока.

Блок 11 управления (фиг, 3) включает в себя генератор 17 тактовых импульсов, элемент НЕ 18, первый и второй счетчики 19 и 20, дешифратор 21, первый и второй триггеры 22 и 23, элементы И 24-29 с первого по шестой, элемент И-НЕ 30, элементы ИЛИ 31-33 с первого по третий, элементы 34-38 задержки с первого по пятый.

Принцип работы устройства основан на том, что в первом счетчике 1 поочередно формируются все возможные двоичные коды заданной длины п - от О (т.е. 0...0) до 2 - 1 (т.е.1...1) Для каждого очередного кода по информации, накопленной к этому моменту време ни в блоке 4 оперативной памяти, вначале выполняется проверка, не совпадает ли он с циклическим сигналом одной из ранее проверенных комбинаций. Если это действительно так, то проверка данного кода прекращается и первый счетчик 1 формирует следующий двоичный код, это позволяет сократить продолжительность проверки. Если же проверяемый двоичный код не является сдвигом одного КЗ ранее проверенных кодов, то далее с помощью регистра 2 сдвига, блока 5 задающего длину кода, коммутатора

6,элемента И 10, второго счетчика 9у подсчитывающего вес кода, блока

7,задающего вес, и элемента 10 сравнения выполняется проверка его веса. Если проверяемый код соответствует заданному весу, т.е. является одним из искомых циркулянтов, то он поступает на информационные выходы 12 устройства одновременно с сигналом Строб кода на управляющем выходе 13. После этого на выходах 12 формируется п - 1 квазициклических кодов, являющихся циклическими сдвигами найденного циркулянта, причем всякий раз в блоке 11 управления формируется сигнал Строб кода и для каждого из них в блоке 4 оперативной памяти запоминается признак уже проверенно3го кода. После этого в устройстве формируется и проверяется следующий двоичный код. Если же в результате проверки веса очередного двоичного кода будет выявлено несоответствие заданному весу, то для него самого и дпя п - 1 кодов, являющихся его циклическими сдвигами, в блоке 4 оперативной памяти запоминается при наки ранее проверенных кодов. Таким образом к концу проверки всех кодо заданной длины в блоке 4 оперативной памяти не будут запомнены признаки ранее проверенных кодов. Таким образом, к концу проверки всех кодо заданной длины в блоке 4 оперативно памяти не будут заполнены признаки ранее проверенных кодов только для тех кодов, которые являются циркуля тами квазициклических кодов заданно го веса, а все квазициклические код заданного веса поступят на выходы 12 устройства в сопровождении сигнала Строб кода с выхода 13. На фиг. 4-6, иллюстрирующих работу устройства, обозначено: q - тактовые импульсы на выходе генератора 17 &-те же импульсы на выходе элемента 34 задержки Е - код состояния на выходах первого счетчика 19j t - сигнал Инкремент кода с пер вого выхода дешифратора 21 - сигнал записи в регистр 2 . сдвига с второго выхода дешифратора 21- е - сигнал записи в счетчик 20 с выхода элемента ИЛИ 32 ж - сигнал с выхода элемента ИЛИ 33 о том, что счетчик 20 не пуст ч, - сигйал Спроса разряда кода с выхода элемента И 27 j U - сигнал сдвига кода в регистре 2 с выхода элемента 37 задержки, k - сигнал с выхода элемента 8 сравнения о том, что вес кода равен заданному Л - сигнал с выхода первого триг гера 22, М- сигнал записи признака в бло . 4 оперативной памяти с выхода элемента И 28, Н- сигнал Признак ранее проверенного кода с выхода блока 4 oneративной памяти; о - строб кода на управляющем вы ходе 13 J 134 h - сигнал с выхода второго триггера 23. Устройство работает следующим образом. В исходном состоянии (после включения питания) первый счетчик 1, блок 4 оперативной памяти, а в блоке 11 управления - счетчик 19 и триггеры 22 и 23 очищены (содержат нули во всех разрядах и ячейках памяти). С выхода блока 5 на вторые входы блока 11 управления и на управляющие входы блока 3 маскирования неиспользуемых разрядов и коммутатора 6 поступают параллельный код заданной длины кодовых комбинаций. С Выхода блока 7 на вторые входы элемента 8 сравнения поступает параллельный код заданного веса кодовых комбинаций. С первого выхода блока 11 управления на счетньш вход первого счетчика 1 поступает сигнал Инкремент кода (фиг. 4г), при этом код содержимого счетчика 1, являющийся очередной проверяемой комбинацией, увеличивается на 1 (в частности, в начале работы устройства код 00...00 сменяется кодом 00...01). С некоторой задержкой относительно этого сигнала, необходимой для окончания переходных процессов в первом счетчике 1, на втором выходе блока 11 управления формируется сигнал Запись в регистр сдвига, поступающий на вхрд обнуления второго счетчика 9 и на вход записи регистра 2 сдвига. При этом код очередной проверяемой комбинации, поступающий на первые информационные входы регистра 2 сдвига, записывается в этот регистр 2 и с его выходов через блок 3 поступает на адресные входы блока 4 оперативной памяти. В начале работы устройства при проверке кодовой комбинации 00...01 блок 4 оперативной памяти содержит во всех ячейкахпамяти нули, поэтому его сигнал Признак ранее проверенного кода, поступающий на первый вход блока 11 управления, будет иметь уровень логического О (значение этого сигнала соответствует содержимому той ячейки блока 4 оперативной памяти, адрес которой равен коду на адресном входе этого же блока). Вследствие этого с некоторой задержкой, достаточной для окончания переходных процессов при записи параллельного кода в регистр 2 сдвига и

считывании содержимого блока 4 оперативной памяти, в устройстве начинает выполняться определение веса проверяемого кода с целью проверки его соответствия заданному значению. При этом блок 11 управления на своих третьем и четвертом выходах формирует пачку из п импульсов сигнала Ойрос разряда кода (фиг. 4) и пачку из п импульсов сигнала Сдвиг кода (фиг. 4и). Число импульсов в каждой из этих пачек соответствует коду заданной длины комбинации, поступающему на вторые входы блока 11 управления от блока 5 задания длины. Во время формирования пачки импульсов сигнала Сдвиг кода коммутатор 6 совместно с N-разрядным регистром 2 сдвига обеспечивает тдиклический сдвиг содержимого п младших разрядов этого регистра (содержимое старших N - п его разрядов при этом определяется содержимым п-го разряда в течение предшествовавших N - п импульсов сдвига, что не влияет на работу устройства в целом). Для обеспечения циклического сдвига младших п разрядов регистра 2 сдвига выход его разряда п через коммутатор 6, управлявмый кодом заданной длины п (поступающим от блока 5 задания длины)-, подключается к второму,(последовательному) входу этого же регистра 2. Вследствие этого, например, при заданной длине кода п 3 и проверяемо комбинации 0...0001 после каждого , : очередного сигнала Сдвиг кода (общее число которых будет равно 3) содержимое регистра 2 сдвига будет соответственно принимать значения:

0...00110 0...01101 0...11011,

.4

что и соответствует циклическому

сдвигу младших 3 разрядов комбинации (нумерация разрядов в приведенной записи выполнена справа налево).

При определении веса проверяемого кода сигнал с выхода коммутатора 6 поступает на первый вход элемента И 10, На второй вход этого элемента 10 поступает сигнал Опрос разряда кода (фиг. 4j). Если текущее значекие п-го разряда проверяемого кода равно логической 1, то с выхода элемента И 10 на счетный вход счетчика 9 поступает импульс, увеличивающий содержимое счетчика на единицу. Так как общее число импульсов сигнала Опрос разряда кода равно п и после каждого их этих импульсов (с задержкой, достаточной для надежного формирования импульса на выходе элемента И 10) блок 11 управления формирует очередной импульс сигнала Сдвиг кода (фиг. 4о), то число импульсов на счетном входе счетчика 9 за это время будет равно числу разрядов проверяемой комбинации, значение которых равно логической 1, т.е. ее весу. Этому же числу будет соответствовать после окончания формирования всех п импульсов сигнала Опрос разряда кода и код на выходах счетчика 9, поступающий на первые входы элемента 8 сравнения. На вторые входы этого элемента 8 поступает код заданного значения веса с выхода блока 7. В случае равенства кодов на обоих входах элемента 8 сравт нения сигнал Вес равен заданному (фиг. 4k), формируемый на его выходе и поступающий на третий вход блока 11 управления, принимает значение логической 1, в противном случае логического О. Значение зтого сигнала после окончания формирования пачек сигналов Опрос разряда кода и Сдвиг кода и определяет дальнейшую работу устройства. В случае, еслизначение зтого сигнала равно О, т.е. если вес проверяемой комбинации оказался неравным заданному, в устройстве далее выполняется запись признака ранее проверенного кода во всех ячейках блока 4 оперативной памяти, адреса которых равны циклическим, сдвигам проверяемой комбинации либо ей самой. При этом устройство работает следующим образом. После окончания проверки веса комбинации с выходов блока 3 маскирования неиспользуемьк разрядов на адресньй вход блока 4 оперативной памяти поступает код, равный коду исходной проверяемой комбинации. В частности, в рассмотренном выше примере этот код будет равен 0...00011 (хотя код содержимого регистра сдвига будет равен 0.. . 1 1 О 1), значения старших N- и- разрядов этого кода всегда будет равно 0.

Далее с пятого выхода блока 11 управления на вход записи блока 4 оперативной памяти поступает первый импульс сигнала Запись признака (фиг. 4м) при этом в ячейку с соответствующим адресом (равным в рас сматриваемом случае 0...00011) запи сывается логическая 1. Через промежуток времени, достаточный для за писи признака, на вход управления сдвигом регистра 2 сдвига вновь пос тупит импульс сигнала Сдвиг кода (фиг. 4и). При этом аналогично вьше описанному будет выполнен циклический сдвиг проверяемого кода и маскирование неиспользуемых разрядов кода, поступающего на адресный вход блока 4 оперативной памяти, а после завершенияпереходных процессов на вход записи этого же блока поступит очередной импульс сигнала Запись признака. В описываемой последовательности блоком 11 управления на П том ичетвертом выходах будут сформированы пачки из п импульсов сигнала Запись признака и сигнала Сдвиг кода. При этом для рассмотренного выше конкретного кода проверяемой комбинации признак ранее проверенного кода будет записан в ячейке с адресами 0...0011, 0...011 и 0...0101. Если же проверяемой комбинацией была комбинация 0...000 (как это имеет место в первый момен времени после начала работы устройства) и по окончении проверки веса сигнал Вес кода равен заданному принимает нулевое значение, то для рассматриваемого частного случая п 3 признак ранее проверенного ко да будет записан в ячейки блока 4 оперативной памяти с адресами 0... ...0001, 0...0010 и 0...0100. После записи признака в п ячеек блока 4 оперативной памяти заканчиваются действия, связанные с очередной проверяемой комбинацией, и с первого выхода блока 11 управления на счетны вход первого счетчика 1 вновь поступает сигнал Инкремент кода (фиг.4г При этом в первом счетчике 1 форми.руется следующая кодовая комбинация и устройство выполняет ее проверку. Проверка очередной кодовой комбинации значительно сокращается во времени, если она является циклическим сдвигом одной из ра.нее проверявшихся комбинаций. Именно такой случай име ет место для рассматриваемого примера, когда вслед за проверкой комбина 13 дни O...OOtO после формирования сигналов Инкремент кода и Злпись в регистр сдвига (фиг. 4) через промежуток времени, достаточный для поступления кода очередной комбинации (0...0010) на адресный вход блока 4 оперативной памяти и выполнения операции чтения из соответствующей ячейки, с выхода этого блока 4 на первый вход блока 11 управления поступит сигнал Признак ранее проверенного кода (фиг. 5н) с уровнем логической 1,- определяемым значением ранее записанного в эту ячейку признака. В этом случае дальнейшая проверка веса очередной комбинации не выполняется, и устройство переходит к формированию и проверке следующей кодовой комбинации - с первого выхода блока 11.управления на счетный вход первого счетчика 1 вновь поступает сигнал Инкремент кода (фиг.52).Если очередная проверяемая комбинация оказывается искомым циркулянтом, то работа устройства при ее проверке происходит аналогично описанному вплоть до окончания формирования первых пачек из п импульсов сигналов Опрос разряда кода и Сдвиг кода (фиг. б, и). После опроса последнего нулевого разряда кода (т.е. после поступления соответствующего По счету импульса сигнала Опрос разряда кода (фиг. б) на второй вход , элемента И 10) код в счетчике 9, поступающий на первые входы элемента 8 сравнения, оказывается равным коду заданного веса, поступающему с выходу блока 7 на вторые входы этого же элемента 8 сравнения. Вследствие этого с выхода элемента 8 на третий вход блока 11 управления начинает поступать сигнал Вес равен заданному (фиг. 6к), единичное значение которого сохраняется в рассматриваемом случае и после окончания формирования первой пачки импульсов сигнала Сдвиг кода. В этом случае во время формирования второй пачки из п импульсов сигнала Опрос разряда кода одновременно с каждым из них на шестом выходе блока 11 управления, являющимся одновременно и управляющим выходом 13 устройства, будет сформирован импульс сигнала Строб кода (фиг. 6о), а импульсы сигнала Запись признака (фиг. 6м) будут формироваться на пятом выходе

91

этого же блока 11 одновременно с вторым и последующими импульсами этой же второй пачки импульсов сигнала Опрос разряда кода. Так как первый импульс второй пачки этого сигнала формируется после завершения всех п циклических сдвигов, то в момент его формирования на выходах 12 устройства присутствует код очередной проверяемой комбинации (т.е. обнарушенный циркулянт), Поэтому и запись признака в ячейку с соответствующим циркулянту адресом не будет выполнена. В течение же остальных п - 1 импульсов сигнала Запись приз нака на выходы 12 устройства последовательно поступают п - 1 квазициклических кодов, порожденных вновь найденным циркулянтом, и.для каждого из них в блоке 4 оперативной памяти выполняется запись признака ранее проверенного кода. После окончения формирования вторых пачек из п импульсов сигналов опроса и сдвига устройство переходит к нормированию и проверке следующей кодовой комбинации, и так далее до тех пор, пока не будет проверена комбинация 1...1111. Таким образом, за время работы устройства на его управляющем выходе 13 появляется пачек импульсов сигнала Строб кода, причем первый импульс каждой из пачек соответ ствует при сутствию на выходах 12 нового циркулянта с заданным весом, а остальные п - 1 импульсов формируются одновременно с формированием на выходах 12 квазициклических кодов порожденных этим циркулянтом. Кроме того, после окончания работы устрбйства из .2 - 1 младших по адресу ячеек блока 4 оперативной памяти (кроме ячейки 0...0000) будут содержать логический О только те ячейки, коды адреса которых равны обнаруженным в ходе проверки циркулянтам. Таким образом, обеспечивается формирование и запоминание всех возможных при заданных длине и весе кода циркулянтов а также автоматическое формирование всех порождаемых ими квазициклических кодов.

Блок 11 управления во время работ устройства функционирует следующим образом. После включения питания счетчики 19 и 20, а также триггеры 22 и 23 находятсяв нулевом состоянии. При этом на все входы элемента

10

13

ИЛИ 33 с соответствующих разрядных выходов счетчика 20 поступают сигналы низкого уровня, вследствие чего на выходе этого элемента 33 также формируется низкий логический уровен сигнала Счетчик сдвигов не пуст (фиг. 4ж) . Благодаря этому на вторые входы первого и второго элементов И 24 и 25 с выхода элемента НЕ 18 через третий элемент 36 задержки поступает высокий потенциал. Первый тактовый импульс (фиг. 4а), поступающий на первый вход первого элемента И 24, вызовет формирование импульса на счетном входе счетчика 19, при этом на вход дешифратора 21 поступит код 001. Благодаря этому в момент прихода первого задержанного тактового импульса с выхода первого элемента 34 задержки через второй элемент И 25 на вход синхронизации дешифратора 21 на первом его выходе, являюще 1ся и первым выходом блока 11 управления, формируется импульс сигнала Инкремент кода. С приходом следующего тактового импульса код состояния (содержимое счетчика 19) станет равным 010, благодаря чему одновременно с вторым импульсом сигнала Задержанные тактовые импульсы (фиг. 4S) на втором выходе дешифратора 21, являющемся и вторым выходом блока 11 управления, сформируется импульс сигнала Запись в регистр сдвига. Если после этого на второй вход третьего элемента И 26, являющийся одновременно и первым входом блока 11 управления, поступит высокий уровень сигнала Признак ранее проверенного кода (фиг. 5и),то дальнейшая работа блока происходит следующим образом. После прохождения третьего тактового импульса через первый элемент И 24 на счетный вход счетчика 19 код состояний принимает значение 011. Задержанный тактовый импульс с выхода первого элемента 34 задержки поступает через второй элемент И 25 на вход синхронизации дешифратора 21, благодаря чему на третьем выходе этого же дешифратора 21 возникает импульс. Так как на втором входе третьего элемента И 26 в этот момент времени присутствует высокий уровень сигнала Признак ранее проверенного кода, то на его выходе также возникает импульс, который, пройд;я через первый элемент n ИЛИ 31 и второй элемент 35 задержки поступит на вход сброса счетчика 19 и установит его в исходное состояни Благодаря этому работа блока 11 управления возобновится в дальнейшем, начиная с формирования сигнала Инк ремент кода. В том случае работы устройства, когда после формировани сигнала Запись в регистр сдвига на второй вход третьего элемента И 26 не поступает высокий уровень сигнала Признак ранее проверенного кода не будет сформирован и импульс на выходе этого же элемента 2 во время третьего состояния счетчик 19состояний.Поэтому счетчик 19 в моме прихода четвертого тактового импульс перейдет в четвертое состояние 100, и после формирования очередного задержанного тактового импульса на четвертом выходе дешифратора 21 воз никает импульс,)который, пройдя через второй элемент ИЛИ 32, поступит на вход управления записью счетчика 20в качестве сигнала Запись в сче чик сдвигов (фиг. 4е). При- этом ко заданной длины комбинаций, поступающий на параллельный информационный вход счетчика 20, будет записан в этот счетчик. При этом ненулевые разряды записанного в счетчик 20 ко да поступят с его разрядных выходов .на соответствующие входы третьего элемента ИЛИ 33 и на выходе последнего возникнет высокий уровень сигнала Счетчик сдвигов не пуст (фиг. 4ж) . Благодаря этому на втором входе четвертого элемента И 27 появится разрешающий, а на вторых входах первого и второго элементов . И 24, 25 - запрещающие (низкие) уровни сигнала. В связи с этим в течение следующих периодов тактовых импульсов новые сигналы на входы счетчика 10 и дешифратора 21 поступать не; будут. В течение этого промея утка времени в моменты появления тактовых импульсов на первом входе четвертого элемента. И 27 на .выходе этого же элемента, являющемся одновременно и третьим выходом блока 11 управления, будет сформирована пачка из n импульсов сигнала Опрос разряда кода. Поскольку к выходу четвертого элемента И 27 подключен вход четвертого элемента 37 задержки, то на выходе последнего являющемся одновременно и четвертым 1312 в1,1Х(.)дом блока 11 управления, будет сформирована пачка из импульсов сигнала Сдвиг кода. Поскольку триггеры 22 и 23 в течение этого промежутка времени находятся в исходных состояниях (которым соответствуют низкие уровни сигналов с их выходов), сигналы Строб кода и Запись признака с выходов элементов И 28 и 29 при этом не будут формироваться. Каждый из импульсов сигнала Сдвиг кода, поступая с выхода четвертого элемента 37 задержки на вход вычитания счетчика 20, уменьшает содержимое последнего на единицу. Через n таких импульсов в счетчике 20 окажется код 0...0 и сигнал на выходе третьего элемента ИЛИ 33 вновь принимает значение логического О. Благодаря этому на втором входе четвертого элемента И 27 возникает запрещаюпщй уровень сигнала (что приводит к прекращению формирования пйчек импульсов), и через некоторый промежуток времени на вторых входах первого и второго элементов И 24 и 25 возникает разрешаюищй уровень сигнала. Таким образом, при формировании очередного тактового импульса счетчик (9 перейдет в следующее - пятое состояние (101) . При формировании очередного задержанного тактового импульса на пятом выходе дешифратора 21 возникает импульс, который, пройдя через второй элемент ИЛИ 32, вызывает повторное формирование сигнала Запись в.счетчик сдвигов. Кроме того, этот же импульс поступает на вход установки триггера 23 и на вход синхронизации триггера 22. Дальнейшая работа блока 11 управления определяется уровнем сигнала Вес равен заданному, поступающего в этот момент времени на вход пятого элемента 38 задержки, являющийся одновременно и третьим входом этого блока. Если после окончания первой пачки из n импульсов-сигнала 0);рсс разряда кода сигнал Вес равен заданному имеет уровень логического О (фиг. 4к), то и сигнал на выходе триггера 22 также будет иметь этот же уровень и после прихода на его вход синхронизации импульса с пятого выхода дешифратора 21. В связи с этим на втором входе шестого элемента И 29 будет иметь место запрещаюощй, а на втором входе пятого элемента И 28.- разрешаюи й уровень сигнала. Благодаря этому одновременно с п импульсами второй пачки сигнала Опрос разряда кода, формируемый аналогично описанному, на выходе пятого элемента И 28, являющемся и пятым выходом блока 11 управления, сформируется п импульсов сигнала За пись признака. Если же после окончания первой пачки из п импульсов сигнала Опрос разряда кода сигнал Вес равен заданному будет иметь уровень логической 1 (фиг. бк), то с этого момента блок М управления будет функционировать следующим образом. В момент формирования импульс на пятом выходе дешифратора 21 триггеры 22 и 23 установятся в единичное состояние (соответствующее высоким уровнем сигналов на их выходах). Вследствие этого на выходе элемента И-НЕ 30 будет иметь место уровень логического О. Поэтому одновременн с первым импульсом второй пачки сигнала Опрос разряда кода импульс сигнала Запись признака не будет сформирован. Далее первый же импульс второй пачки сигнала Сдвиг кода, поступив на вход обнуления триггера 23, установит его в исходное сосстоя ние (фиг. 6п)и на втором входе пят го элемента И 28 появится разрешающий уровень сигнала. Поэтому одновpeJxieHHO со следующими п - . 1 импульса ми второй пачки сигнала Опрос разря да кода будут сформированы п - 1 импульсов сигнала Запись признака А благодаря наличию уровня логическ 1 сигнал на втором .входе шестого элемента И 29 од1 овременно с каждым из импульсов второй пачки сигнала Опрос разряда кода на выходе шестого элемента И 29, являющимся шесты выходом блока 11 управления, будет сформирован и импульс сигнала Стро кода (фиг. 6о). После окончания формирования вторых пачек импульсов сигналов опроса и сдвига в счетчике 20 сформируется код 0...0, на вторых входах первого и второго элементов И 24 и 25 появится разрешающий потенциал, счетчик ,19 перейдет в шестое состояние 110 и на шестом выходе дешифратора 21 сформи руется импульс, который, пройдя через первый элемент Ш1И 31 и второй элемент 35 задержки, поступает на 1 1314 входы обнуления счетчика 19 триггера 22, устанавливая их в исходное состояние. После этого работа блока 11 управления возобновляется, начиная с первого состояния счетчика 19у и проходит в одном из трех вьшюописанных режимов. Блок 3 маскирования неиспользуемых разрядов работает следующим образом. На входы дешифратора 16, являющиеся управляющими входами блока, поступает код заданной длины п. При этом на том из N выходов дешифратора 16, номер которого соответствует п, появится уровень Логической 1. Вследствие этого на первый вход соответствующего элемента И 15 также поступает уровень логической 1. Одновременно этот же сигнал с уровнем логической 1 поступит и на второй вход того элемента ИЛИ 14, номер которого на единицу меньше. При этом сигнал с уровнем логической 1 с выхода этого элемента поступит .на f второй вход элемента ИЛИ 14 и первый вход элемента И 15, номер которых соответственно на 1 и на 1 меньше. С выхода этого элементаИЛИ 14 уровень логической 1 поступит на второй вход предыдущего и так далее вплоть до первого элемента ИЛИ 14. Таким образом, на первых входах тех элементов И 15, вторые входы которьсх соединены с информационными входами блока 3 с первого по п-й, будет постоянно присутствовать разрешающий уровень потенциала, а на первых входах остальных элементов И 15 будет уровень логического нуля. Вследствие этого на выходах блока 3 с первого по п-й будут передаваться значения одноименных разрядов информационного входа блока 3, а на неиспользуемые старшие разряды - логические нули. Именно это и позволяет обеспечить запись (и последующее считывание) признаков ранее проверенного кода только в те ячейки блока 4 оперативной памяти устройства, адреса которых попадают в интервал от О до 2 - 1, независимо от содержимого неиспользуемых старших N - п разрядов регистра 2 сдвига. Таким образом, устройство позволяет автоматически генерировать все возможные циркулянты, обладающие заданньми параметрами. 15 Формула изобретени 1.Устройство для генерирования кодов заданного веса, содержащее первый и второй счетчики, регистр сдвига и блок управления, о т-л и чающееся тем, что, с целью расширения функциональных возможнос тей путем автоматизации формирования квазициклическим кодов заданных длины и веса, в него введены первый и второй задающие блоки, коммутатор элемент И, элемент сравнения, блок маскирования неиспользуемых разрядов и блок оперативной памяти, выхо которого соединен с первым входом блока управления, первый выход кото рого подключенк счетному входу пер вого счетчика, выходы разрядов кото рого соединены с соответствующими первыми информационными входами регистра сдвига, вход управления записью которого объединен с входом обнуления второго счетчика и подклю чен к второму выходу блока управления, вторые входы которого объедине ны с соответствующими управляющими входами блока маскирования неисполь зуемых разрядов и коммутатора и под ключены к соответствующим выходам первого задающего блока, выходы раз рядов регистра сдвига подключены к соответствующим информационным входам блока маскирования неиспользуемых разрядов и коммутатора, выход которого соединен с вторым информационным входом регистра сдвига и первым входом элемента И, выход которого подключен к счетному входу второго счетчика, а второй вход соединен с третьим выходом блока управления, четвертый выход которого подключен к входу управления сдвигом регистра сдвига, выходы блока маскирования неиспользуемых разрядов, являющиеся информационными выходами устройства, подключены к соответствующим адресным входам блока оперативной памяти, вход записи которого соединен с пятым выходом блока управ ления, выходы вторых счетчика и зада ющего блока подключены соответственно к первым и вторым входам элемента сравнения, выход которого соединен с третьим входом блока управления, шестой выход которого является управ ляющим выходом устройства. 2.Устройство по п. 1, отличающееся тем, что блок мас13кирования неиспользуемых разрядов выполнен на N - 1 элементах ИЛИ, N элементах И и дешифраторе, входы которого являются управляюи(ими входами блока маскирования неиспользуемых разрядов, а выходы, кроме N-ro, подключены к входам соответствующих элементов ИЛИ, выход первого из которых подключен к первому входу первого элемента И, выход каждого из остальных элементов ИЛИ соединен с первым входом соответствующего элемента И и вторым входом предыдущего элемента ИЛИ, N-й выход дешифратора подключен к второму входу (N - 1)-го элемента ИЛИ и первому входу N-ro элемента И, вторые входы и выходы всех элементов И являются соответствующими информационными входами и выходами блока маскирования неиспользуемых разрядов, причем N - наибольшая длина генерируемых кодов. 3. Устройство по п. 1, отличающееся тем, что блок управления выполнен на первом и втором счетчиках, дешифраторе, первом и втором триггерах, элементах И с первого по шестой, первом, втором и третьем элементах 1ШИ, элементе НЕ, элементе И-НЕ, элементах задержки с первого по пятый и генераторе тактовых импульсов, выход которого соединен с первыми входами первого и четвертого элементов И и через первый элемент задержки - с первым входом второго элемента И, выход которого подключен к входу синхронизации дешифратора, первый и второй выходы которого являются соответствуюищми выходами блока управления, третий выход дешифрат-ора соединен с первым входом третьего элемента И, второй вход которого является первым входом блока управления, а выход подключен к первому входу первого элемента ИЛИ, выход которого через второй элемент задержки подключен к входам обнуления первого триггера и первого счетчика, счетный вхой которого соединен с выходом первого элемента И, а выходы подключены к информационным входам дешифратора, четвертый выход которого подключен к первому входу второго элемента ИЛИ, пятый выход дешифратора соединен с вторым входом второго элемента ИЛИ, входам синхронизации первого триггера и входом установки в единицу второго триггера.

шестой выход дешифратора соединен с вторым входом первого элемента ШШ, выход второго элемента ИЛИ подключен к входу управления записью второго счетчика, информационные входы которого являются вторыми входами блока управления,. выходы второго счетчика соединены с входами третьего элемента ИЛИ, выход которого подключен через соединенные последовательно элемент НЕ и третий элемент задержки к вторым входам первого и второго элементов И и непосредственно - к второму входу четвертого элемента И, выход которого, являющийся третьим выходом блока управления, подключен к первым входам пятого и шестого элементов И и входу четвертого элемента эадержки, выход которого, являющийся четвертым выходом блока управления, соединен с входом вьп итания второго счетчика и входом установку в нуль второго триггера, прямой выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с вторым входом пятого элемента И, выход которого является пятым выходом блока управления, третий вход блока управления через пятый элемент задержки подключен к информационному входу.первого триггера, прямой выход которого, соединен с вторымивходами элемента И-НЕ и шестого элемента И, выход которого является шестым выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1594554A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Способ декодирования данных на основе LDPC кода | 2020 |

|

RU2747050C1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1056269A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

Изобретение относится к вычислительной технике. Использование в : системах передачи данных с избыточ,ным кодированием позволяет расширить функциональные возможности устройства путем автоматизации формирования квазициклических кодов заданных длины и массы. Оно содержит два счетчика, регистр сдвига и блок управления . Благодаря введению двух задающих блоков, коммутатора, злемента И, злемента сравнения, маскирования неиспользуемых разрядов и блока оперативной памяти в нем обеспечивается автоматическое формирование всех циркулянтов с заданными параметрами. 2 з.п. ф-лы, 6 ил.

Kj

rvl

12

:

NLJ

Фиг. 1

| 1970 |

|

SU419883A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-07—Публикация

1985-05-14—Подача