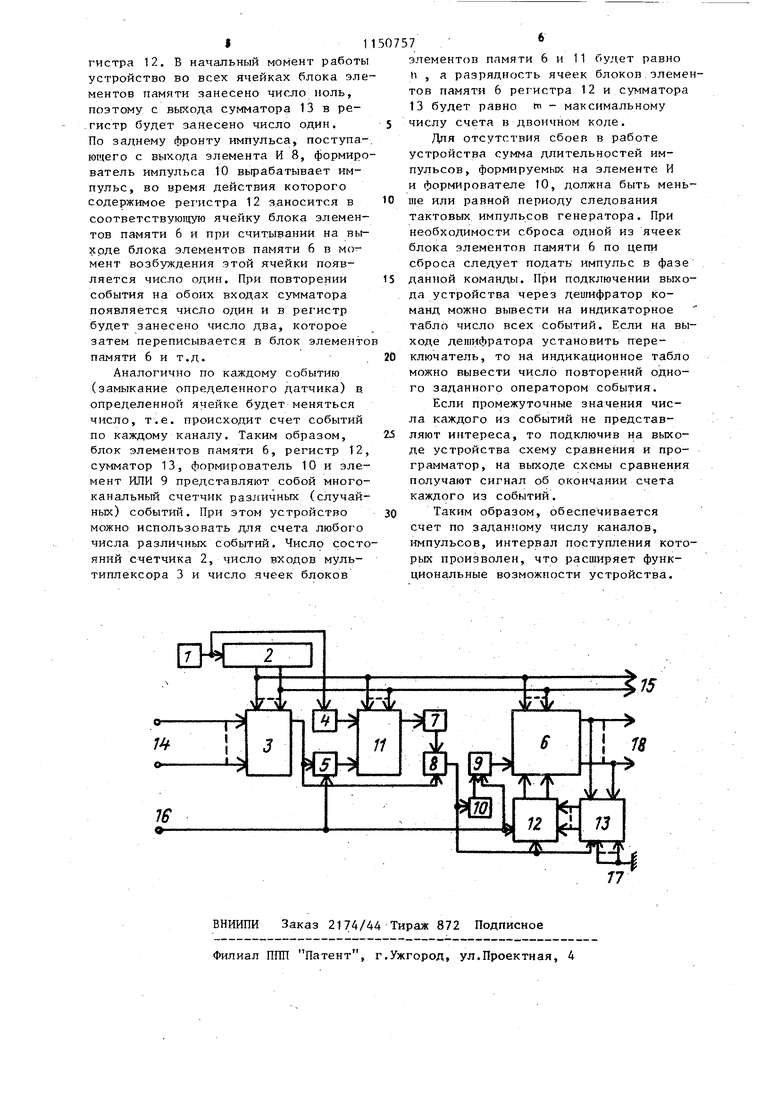

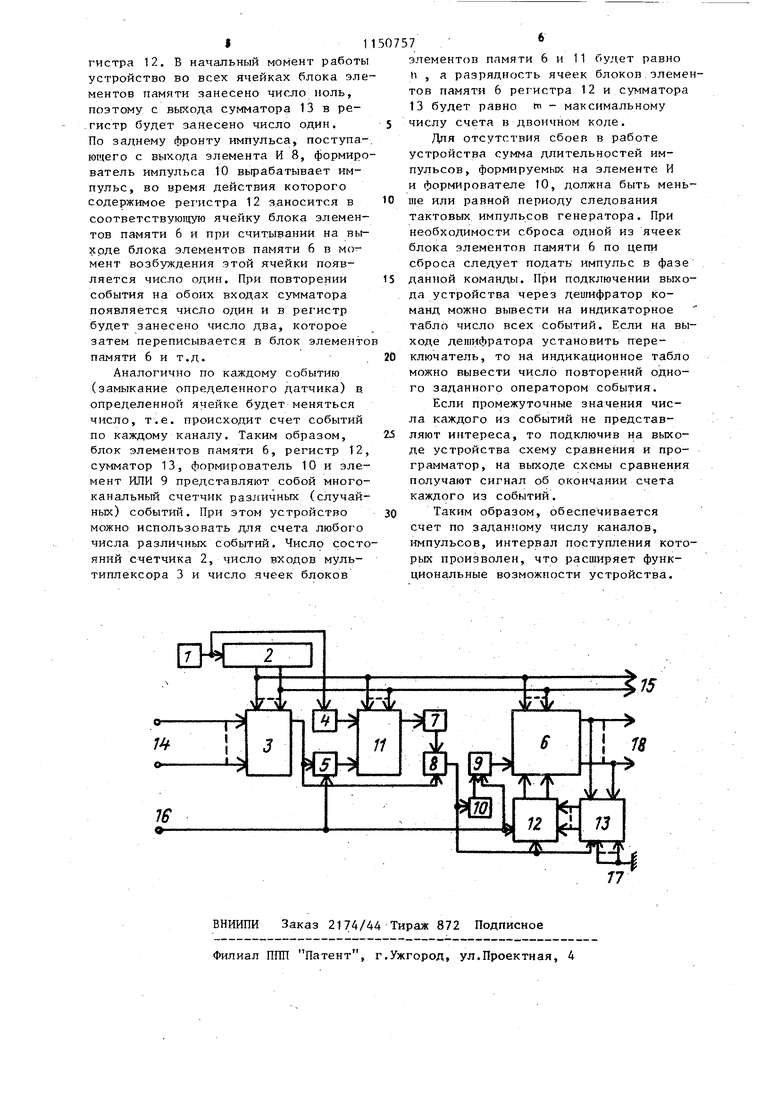

Изобретение относится к автоматике и вычислительной технике, в частности к многоканальным устройствам счета импульсных сигналов, и может быть использовано для пересчета импульсов случайным образом распределенных во времени. Известно многоканальное пересчетное устройство, содержащее последова тельно соединенные генератор тактов, счетчик команд, мультиплексор, информационные входы которого соединены с первыми входами устройства, регистр, сумматор 1 . Недостатком этого устройства янляется ограниченность функгщональных возможностей, так как оно может считать только импульсы, длительност которых меньше скважности тактов опроса, что снижает их функциональные возможности, не позволяет исполь зовать их в системах контроля и упра ления для счета случайных событий большой длительности и большим диапазоном разброса длительности по Ka дому каналу (например, для подсчета предаварийньк и аварийных ситуаций, подсчета числа выполненных операций и т.д.) . Наиболее близким к предлагаемому является многоканальное пересчетноё устройство, содержащее источник тактовых импульсов, счетчик, мультиплек сор, блок элементов памяти, элемент И, регистр, и сумматор, выход источника тактовых импульсов соединен с входом счетчика, выходы которого сое динены с входами управления мультиплексора, информационные входы которого соединены с входами устройства C2j. Недостатком этого устройства является ограниченность функциональньк возможностей, поскольку оно не обеспечивает возможности счета случайных событий с большим разбросом интервалов поступления. Целью изобретения является расширение функциональных возможностей за счет обеспечения возможности счета случайных событий с большим разбросом интервалов поступления. Поставленная цель достигается тем, что в многоканальное пересчетное устройство, содержащее источник тактовых импульсов, счетчик, мультиплексрр, блок элементов памяти, элемент И, регистр и сумматор, при этом выход источника тактовых импульсов соединен с входом счетчика, выходы которого соединены с входами управления мультиплексора, информационные входы которого соединены с входами устройства, введены элемент задержки, первый и второй элементы ИЛИ, инвертор, формирователь и дополнительньй блок элементов памяти, адресные входы которого соединены с соответствующими адресными входами блока элементов памяти и выходами счетчика, которые являются первой группой выходов устройства, выход источника тактовых импульсов соединен с входом элемента задержки, выход которого соединен с входом разрешения дополнительного блока элементов памяти, информационный вход которого соединен с выходом первого элемента ИЛИ, nepBwi вход которого соединен с выходом мультиплексора, который соединен с первым входом элемента И, второй вход которого соединен с выходом инвертора, вход которого соединен с выходом дополнительного блока элементов памяти, выход элемента И соединен с входом формирователя, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с .вторьм входом первого элемента ИЛИ и входом управления устройства, который соединен с установочньтм входом регистра, вход разрешения которого соединен с выходом элемента И, который соединен с входом младшего разряда первой группы входов сумматора, остальные входы которой соединены с шиной нулевого логического сигнала, выходы регистра соединены с информационными входами блока элементов памяти, выходы которого являются второй группой выходов устройства и соединены с соответствующими входами второй группы входов сумматора, выходы которого соединены с информационными входами регистра. На чертеже показана структурная схема многоканального пересчетного устройства. Многоканальное пересчетное устройство содержит источник тактовых импульсов 1, счетчик 2, мультиплексор 3, элемент задержки 4, первый элемент ИЛИ 5, блок элементов памяти 6, инвертор 7, элемент И 8, второй элемент ИЛИ 9, формирователь 10, дополнительный блок элементов памяти 11, регистр 12 и сумматор 13. Выход источника тактовых импульсов соединен с входом счетчика 2, выходы которого соединены с входами управле ния мультиплексора 3, информационные входы которого соединены с входами 14 устройства. Адресные входы дополнительного блока элементов памяти соединены с соответствующими адресны ми входами блока элементов памяти 6 и вьпсодами счетчика 2, которые являются первой группой выходов 15 устройства, выход источника тактовых им пульсов 1 соединен с входом элемента задержки 4, выход которого соединен входом разрешения дополнительного блока элементов памяти 11, информационный вход которого соединен с выходом первого элемента ИЛИ 5, первый вход которого соединен с выходом мультиплексора 3, который соединен с первым входом элемента И 8, второй вход которого соединен с выходом инвертора 7, вход которого соединен с выходом дополнительного блока элемен тов памяти 11, выход элемента И 8 соединен с входом формирователя 10, выход которого соединен с первым входом второго элемента ИЛИ 9, второй вход которого соединен с вторым входом первого элемента ИЛИ 5 и входом 16 управления устройства, который соединен с установочным входом регистра 12, вход разрешения которого соединен с вькодом элемента И 8, который соединен с входом младшего разряда первой группы входов суммато ра 13, остальные входы которой соединены с шиной 17 нулевого логического сигнала, выходы регистра 12 соединены с ннформацконньв и входами блока элементов памяти 6, выходы которого являются второй группой выходов 18 устройства и соединены с соответствующими входами второй группы входов сумматора 13, выходы которого соединены с информационными входами регистра 12. Устройство работает следующим образом. С помощью мультиплексора 3, источника i и счетчика 2 последовательно опрашиваются датчики информации. При этом длительность сигнала по каждому датчику при несинхронной работе должна быть в 2ь раз больше .перибда следования импульсов с источника тактов во избежание потери 7574 измерения информации по какому-либо датчику (где п - число датчиков). Последовательный код состояния датчиков с выхода мультиплексора 3 поступает на многоканальный формирователь одиночного импульса, который состоит из блока элементов памяти 11, элемента ИВ, инвертора 7, элемента задержки 4, элемента ИЛИ 5 и работает следующим образом. При включении устройства сигналом Начальный сброс по входу 16, длительность которого должна быть больше суммы длительностей всех состояний счетчика, через элемент ИЛИ 5 обнуляется блок элементов памяти, одновременно обнуляется регистр 12 и через элемент ИЛИ 9 обнуляется блок элементов памяти 6. При появлении логической единицы на какомлибо из информационных датчиков за счет задержки записи на входе и выходе блока элементов памяти И появятся разные сигналы, так как на выходе блока элементов памяти 6 появится логический ноль,воспринимаемый через элемент НЕ элементом И . как логическая единица, а на выходе мультиплексора 3 в данный момент времени - логическая единица, поступающая на второй вход элемента И 8. На выходе элемента И 8 формируется одиночный импульс, длительность которого равна величине задержки элемента 4, так как по окончании задержки в блок элементов памяти будет записана логическая единица. Повторньй импульс по данному датчику может возникнуть только после повторения события, т.е. когда в ОЗУ будет вновь Записан в данную ячейку логический ноль (событие закончено), а затем вновь появится логическая единица. Таким образом на выходе многоканального формирователя одиночных импульсов (на выходе элемента И 8) будут формироваться одиночные импульсы при каждом повторении события по каждому датчику, т.е. его замыканию, ри этом фаза импульса будет совпадать с определенной фазой-счетчика характеризующей время подключения опредеенного датчика для опроса Импульс с-выхода элемента И 8 поступает на дин вход сумматора 13, на вторые входы которого поступает содержание озбужденной ячейки блока -элементов амяти 6, и на-разрешающ Л вход ре

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сложения (вычитания) N чисел с настраиваемым модулем | 2016 |

|

RU2637988C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Устройство для опроса информационных датчиков | 1983 |

|

SU1172085A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| Логический анализатор | 1986 |

|

SU1410033A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2477887C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2455682C1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 2009 |

|

RU2416157C1 |

МНОГОКАНАЛЬНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО, содержащее источник тактовых импульсов, счетчик, мультиплексор, блок элементов памяти, элемент И, регистр и сумматор, при этом выход- источника тактовых импуль сов соединен с входом счетчика, вцходы которого соединены с входами управления мультиплексора, информационные входы которого соединены с входами устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности счета случайных событий с большим разбросом интервалов поступления импульсов, в него введены элемент задержки, первый и второй элементы ИЛИ, инвертор, формирователь и дополнительный блок элементов памяти, адресные входы которрго соединены с соответствующими адресньаш входами блока элементов памяти и выходами счетчика, которые являются первой группой выходов устройства, выход источника тактовых импульсов соединен с входом элемента задержки, ,. выход которого соединен с входом разрешения дополнительного блока элементов памяти, информационный вход которого соединен с выходом первого элемента ИЛИ, первьй вход которого соединен с выходом мультиплексора, который соединен с первым входом элемента И, второй вход которого соединен с выходом инвертора, вход которого соединен с выходом дополнительного блока элементов памяти, выход элемента И соединен с входом формирователя, выход которого соединен с первым входом второго элемента ИПИ, второй вход которого (Л соединен с вторым входом первого элемента ИЛИ и входом управления устройства, который соединен с установочным входом регистра, вход разрешения которого соединен с выходом элемента И, который соединен С вхогдом младшего разряда первой группы D1 о :л входов сумматора, остальные входы которой соединены с шиной нулевого логического сигнала, выходы регистра соединены с информационными входами блока элементов памяти, выходы которого являются второй группой выходов устройства и соединены с соответствующими. входг:ми второй группы входов сумматора, выходы кото рого соединены с информационными входами регистра.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальный счетчик импульсов | 1974 |

|

SU508938A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Станок для изготовления замковых муфт | 1958 |

|

SU119508A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-04-15—Публикация

1983-10-10—Подача