о

со

ОЭ

114

I Изобретение относится к вычисли- |тельной технике и предназначено для комплексной отладки устройств, по- Ьтроенных на БИС и микропроцессорных ШС.

Цель изобретения - повышение достоверности контроля с

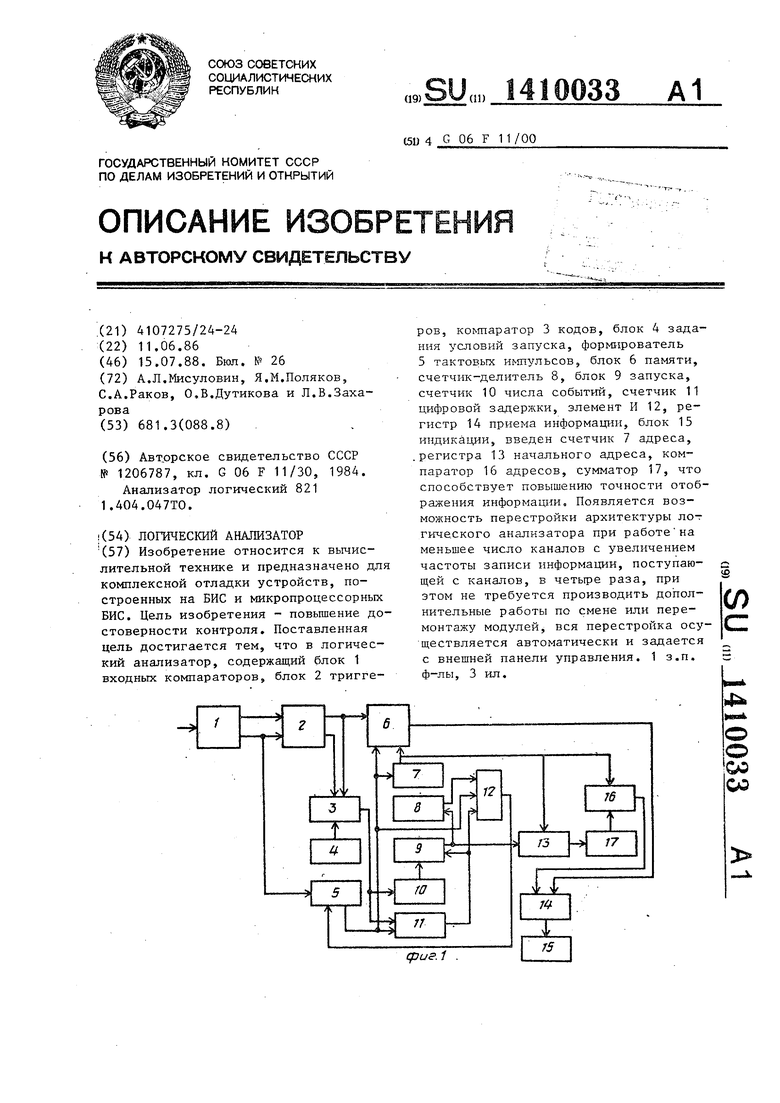

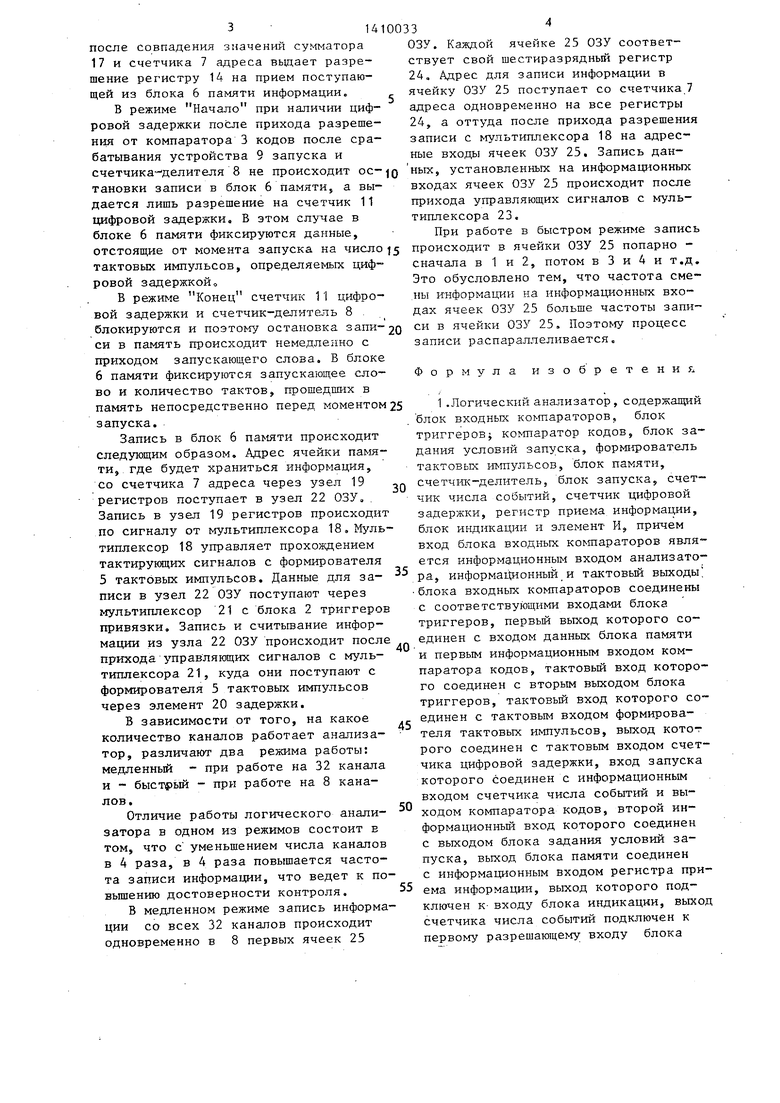

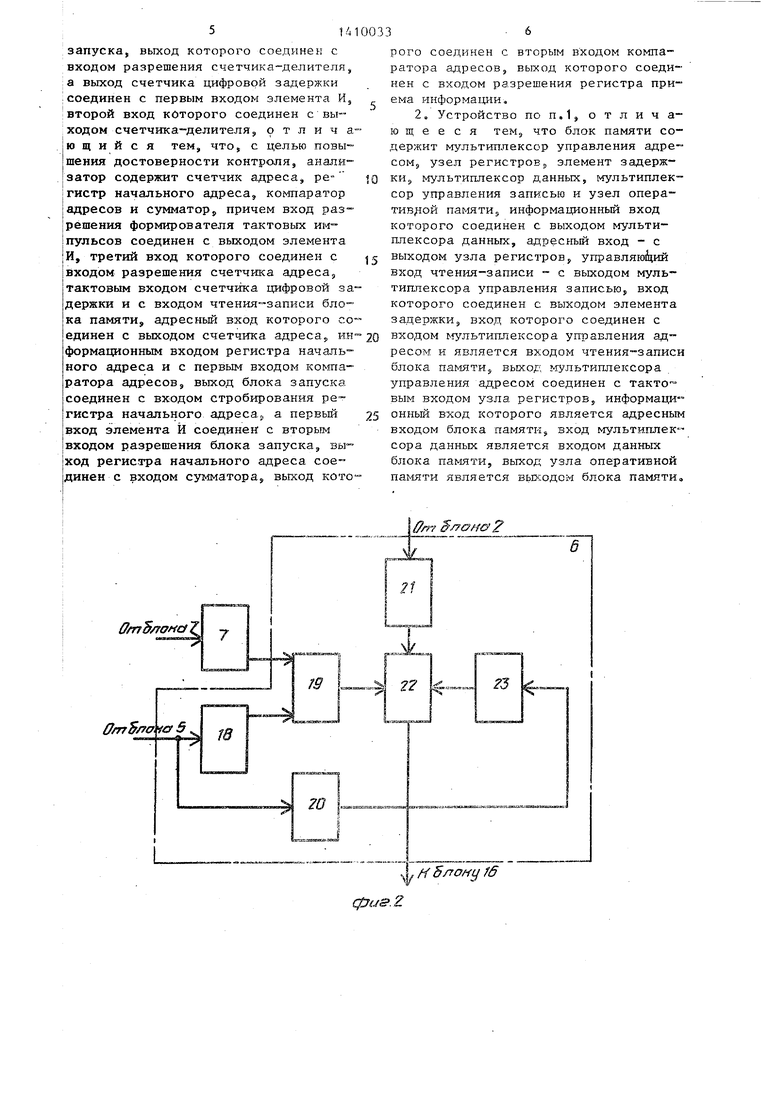

На фиг.1 приведена структурная . хема логического анализатораJ на фиг.2 - структурная схема блока памяти; на фиг.З - функциональная схема Злока памяти

Логический анализатор содержит элок 1 входных компараторов 5 блок 2 триггеров, компаратор 3 кодов, блок

задания условий запуска; формирова ель 5 тактовых импульсов,, блок 6 па , счетчик 7 адреса, счетчик-делитель 8, блок 9 запуска счетчик 10 числа событий, счетчик 11 цифрово

ки, элемент 12 Hj регистр 13 начального адреса, регистр 14 приема информации, блок 15 индикации,, компа )атор 16 адресов, сз мматор 17о

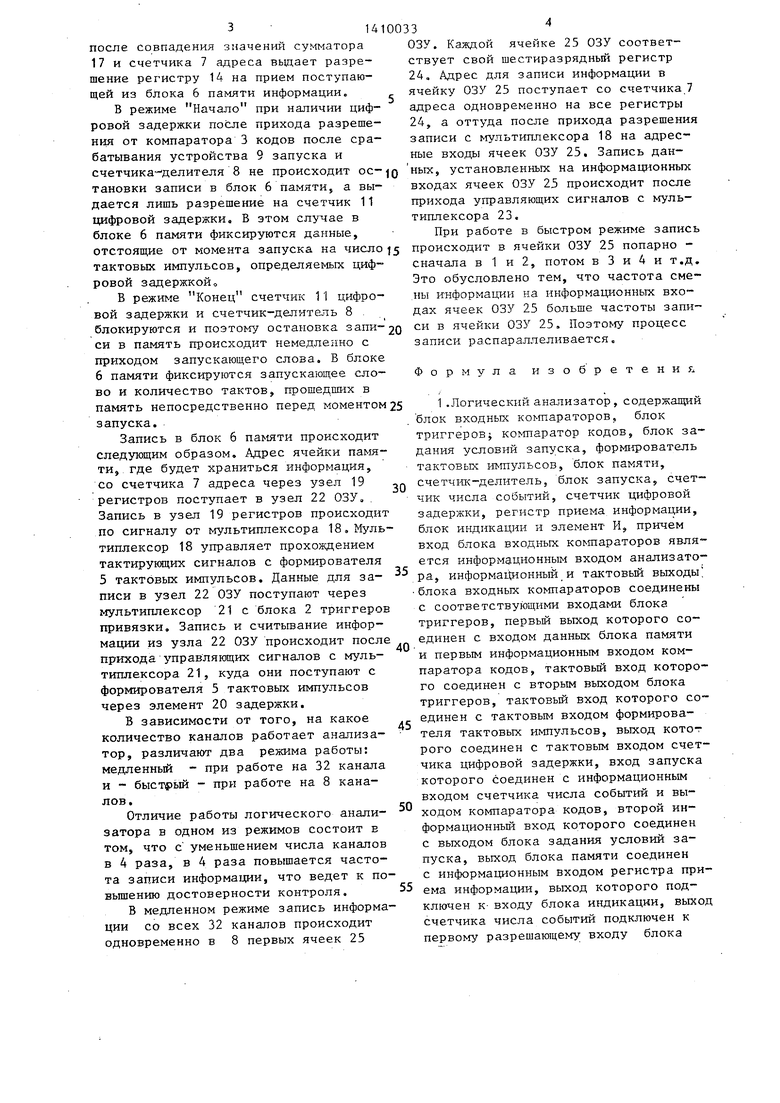

Блок 6 памяти (фиг,2) с;одер7кит |1ультипд ексор 18 управления адресом .МХУА)5 узел 19 регистров, элемент , задержки, мультиплексор 21 данньж МХД), узел 22 оперативной памяти блок ОЗУ), мультиплексор 23 управления записью (МХУЗ)«

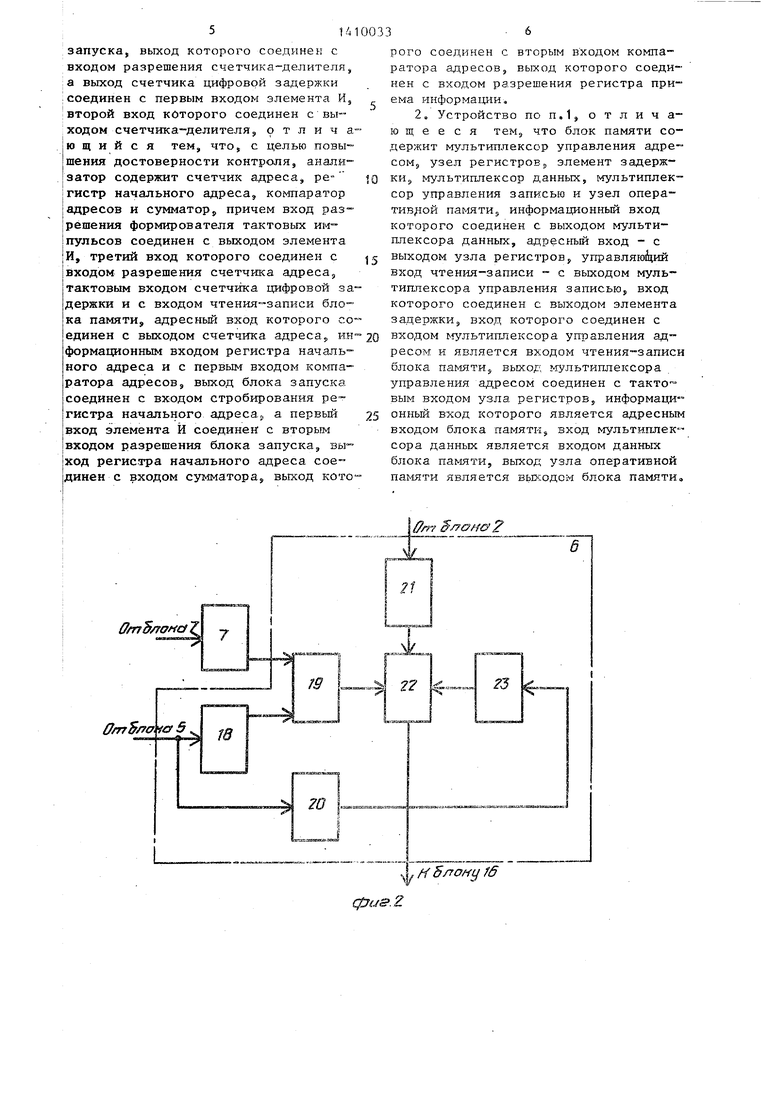

На функциональной схеме блока б памяти (фиг.З) показано соединение регистров (Рг) 24 блока 19 регистров

ячейками узла оперативной памяти ОЗУ) 25 блока 22 ОЗУ

Анализатор работает следующим об-- Глазом.

Информация на входе сравнивается блоке 1 входных компараторов и нор йируется по амйлитуде для ТТЛ (логи- -веский О менее 0,4 В, логическая

О менее 0,4 1 более 2,А В)„ С выхода блока 1 1|ходных компараторов информация пос™ 1 упает в блок 2 триггеров,, которые тактируются приходящими из блока 1 входных компараторов тактовыми им™ г|ульсами, что позволяет исключить разброс задержки информационных сиг- Налов. Из блока 2 триггеров информация поступает для записи в блок 6 па 1«(яти. Если код входной информации йе совпадает с кодом, введенным с передней панели логического анализато™ р|а через блок 4 задания условий за- njycKa, то запись в память происходит н|епрерывно. Старые данные вытесняютс HioBbWH, Этот процесс продолжается до

момента прихода запускающего слова. Запускающее слово - это совпадение комбинации нулей и единиц, приходящих одновременно по всем каналам, с комбинацией нулей и единиц, введенных в компаратор 3 кодов с передачей панели анализатора. При приходе запускающего слова дальнейшая работа возможна в одном из трех режимов:

-режим Начало без цифровой задержки,

-режим Начало с цифровой задержкой ,

Конец,

-режим

В режиме Начало без цифровой за держки работа происходит следующим образом. Компаратор 3 кодов выдает сигнал на блок 9 запуска через счет чик 10 числа событий. Если счетчик 10 числа событий установлен на нуль, то с гфиходом этого сигнала срабатывает блок 9 запуска, давая разрешение на счетчик-делитель 8 и на регистр 13- начального адреса, куда по данному сигналу записывается показание счетчика 7 адреса Счетчик 7 адреса определяет адрес в блоке 6 памяти запи- сьшаемой информации., Таким образом, регистр 13 начального 1дреса фиксирует начальный адрес поступающей информации В блоке 6 памяти хранится информация, включaюuj;aя запускающее слово и количество тактов, следующих за ним и определяемьк счетчиком-делителем 8, Остальная область памяти блока 6 хранит предысторию о

Если счетчик 10 чисхга событий установлен не на нуль,- то блок 9 запуска

сработает только после заполнения счетчика 10 числа событий После окончания цикла записи по сигналу от счетчика-делителя 8, прошедшему через элемент 12 И и поступившему на.формирователь 5 тактовых импульсов, последний формирует сигналы считывания из блока б памяти. Начальный адрес с регистра 14 начального адреса поступает в суг-тматор 17, где корректируется с учетом того, что с момента

прихода запускающего слова и до момента фртксации начального адреса, учитывая задержку на элементах, теряется несколько тактов считывания. Поэтому сумматор 17 компенсирует задержку, вычитая из начального адреса заданную величину. Далее скорректи- рованньтй ачальный адрес поступает на KOMisapaTOp 16 адресов, который

после совпадения значений сумматора 17 и счетчика 7 адреса выдает разрешение регистру 14 на прием поступающей из блока 6 памяти информации.

В режиме Начало при наличии цифровой задержки после прихода разрешения от компаратора 3 кодов после срабатывания устройства 9 запуска и счетчика- делителя 8 не происходит OCтановки записи в блок 6 памяти, а выдается лишь разрешение на счетчик 11 цифровой задержки. В этом случае в блоке 6 памяти фиксируются данные, отстоящие от момента запуска на число тактовых импульсов, определяемых цифровой задержкойо

В режиме Конец счетчик 11 цифровой задержки и счетчик-делитель 8 .

ОЗУ. Каждой ячейке 25 ОЗУ соответствует свой шестиразрядньм регистр 24, Адрес для записи информации в ячейку ОЗУ 25 поступает со счетчика,7 адреса одновременно на все регистры 24, а оттуда после прихода разрешения записи с мультиплексора 18 на адресные входы ячеек ОЗУ 25, Запись дан- ных, установленных на информационньге входах ячеек ОЗУ 25 происходит после прихода управляющих сигналов с мультиплексора 23.

При работе в быстром запись происходит в ячейки ОЗУ 25 попарно - сначала в 1 и 2, потом вЗи4ит.д. Это обусловлено тем, что частота сме- .ны информации на информационных входах ячеек ОЗУ 25 больше частоты запи

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

| Логический анализатор | 1981 |

|

SU1032457A1 |

Изобретение относится к вычислительной технике и предназначено для комплексной отладки устройств, построенных на БИС и микропроцессорных БИС. Цель изобретения - повышение достоверности контроля. Поставленная цель достигается тем, что в логический анализатор, содержащий блок 1 входных компараторов, блок 2 триггеров, компаратор 3 кодов, блок 4 задания условий запуска, формирователь 5 тактовых импульсов, блок 6 памяти, счетчик-делитель 8, блок 9 запуска, счетчик 10 числа событий, счетчик 11 цифровой задеряски, элемент И 12, регистр 14 приема информации, блок 15 индикации, введен счетчик 7 адреса, .регистра 13 начального адреса, компаратор 16 адресов, сумматор 17, что способствует повышению точности отображения информации. Появляется возможность перестройки архитектуры логического анализатора при работе на меньшее число каналов с увеличением частоты записи информации, поступающей с каналов, в четыре раза, при этом не требуется производить дополнительные работы по смене или перемонтажу модулей, вся перестройка осуществляется автоматически и задается с внешней панели управления. 1 з.п. ф-лы, 3 ил. S (Л

блокируются и поэтому остановка запи-20 си в ячейки ОЗУ 25. Поэтому процесс

.

си в память происходит немедленно с приходом запускающего слова. В блоке 6 памяти фиксируются запускающее слово и количество тактов, прошедших в память непосредственно перед моментом запуска.

Запись в блок 6 памяти происходит следующим образом. Адрес ячейки памяти, . где будет храниться информация, со счетчика 7 адреса через узел 19 регистров поступает в узел 22 ОЗУ, Запись в узел 19 регистров происходит по сигналу от мультиплексора 18, Мультиплексор 18 управляет прохождением тактирующих сигналов с формирователя 5 тактовых импульсов. Данные для записи в узел 22 ОЗУ поступают через мультиплексор 21 с блока 2 триггеров привязки. Запись и считывание информации из узла 22 ОЗУ происходит после прихода управляющих сигналов с мультиплексора 21, куда они поступают с формирователя 5 тактовых импульсов через элемент 20 задержки.

В зависимости от того, на какое количество каналов работает анализатор, различают два режима работы: медленньй - при работе на 32 канала и быстрьш - при работе на 8 каналов.

Отличие работы логического анализатора в одном из режимов состоит в том, что с уменьшением числа каналов в 4 раза, в 4 раза повышается частота записи информации, что ведет к по- вьш1ению достоверности контроля.

В медленном режиме запись информации со всех 32 каналов происходит одновременно в 8 первых ячеек 25

30

35

25

55

40

45

50

записи распараллеливается. Формула изобретения

5141

запуска, выход которого соединен с входом разрешения счетчика-делителя, а выход счетчика дифровой задержки ;соединен с первым входом элемента И, второй вход которого соединен с выходом счетчика делителя, о т л и ч а™ ю щ и и с я тем, что, с целью повышения достоверности контроля, анализатор содержит счетчик адреса, ре- |гистр начального адреса, кo mapaтop I адресов и сумматор причем вход раз- Iрешения формирователя тактовых им- I пульсов соединен с выходом элемента IИ, третий вход которого соединен с Входом разрешения счетчика адреса,, тактовым входом счетчика цифровой задержки и с входом чтения-записи блока памяти,, адресньй вход которого соединен с выходом счетчика адреса5, ин- формационным входом регистра начального адреска и с первым входом компаратора адресов5 выход блока запуска соединен с входом стробирования регистра начального адреса,„ а первьш вход элемента И соединен с вторым

входом разрешения блока запуска, вы- |ход регистра начального адреса соединен с входом сумматора, выход котоOfTT rfO

рого соединен с вторым входом компаратора адресов, выход которого соединен с входом разрешения регистра приема информации,

2„ Устройство поп,1,отлича- ю щ е е с я тем,, что блок памяти содержит мультиплексор управления адресом, узел регистров5 элемент задерж- ки мультиплексор данных, Ivfyльтиплeк- сор управления записью и узел опера- ТИВ/1ОЙ памяти информационный вход которого соединен с выходом мультиплексора данных, адресьгьй вход - с выходом узла регистров, управляю ций вход чтения-записи с выходом мультиплексора управлеьгия записью, вход которого соединен с выходом элемента задержки, вход которого соединен с входом мультиплексора управления адресом и является входом чтения-записи блока oaMHTHj выход мультиплексора управления адресом соединен с такто™ вым входом узла регистров, информаци онньй вход которого является адресньм входом блока памяти, вход мультиплексора данных является входом данных блока памяти, выход узла оперативной памяти является вьшодсм блока памяти.

ff/Tf /у ома 2

. Н 5л он у f6

фиг.З

| Авторское свидетельство СССР № 1206787, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ручной ткацкий станок | 1923 |

|

SU821A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-07-15—Публикация

1986-06-11—Подача