й

Од

)

ц

Изобретение относится к Вычислительной технике, предназначено для вьшода информации из ЭВМ и может использоваться в системах автоматизации проектирования и конструирования при автоматизации обработки данных в диа- логовьк системах.

Цель изобретения - повышение точII

ности отображения информации за счет реализации динамического знакогенери- рования.

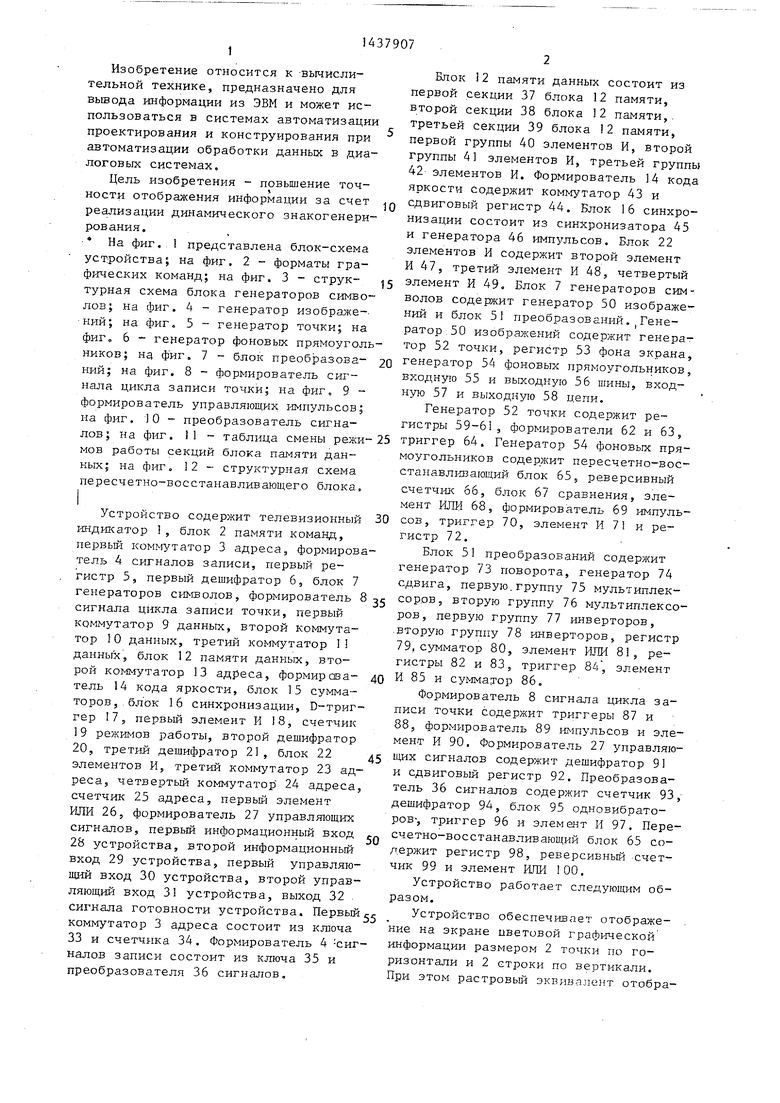

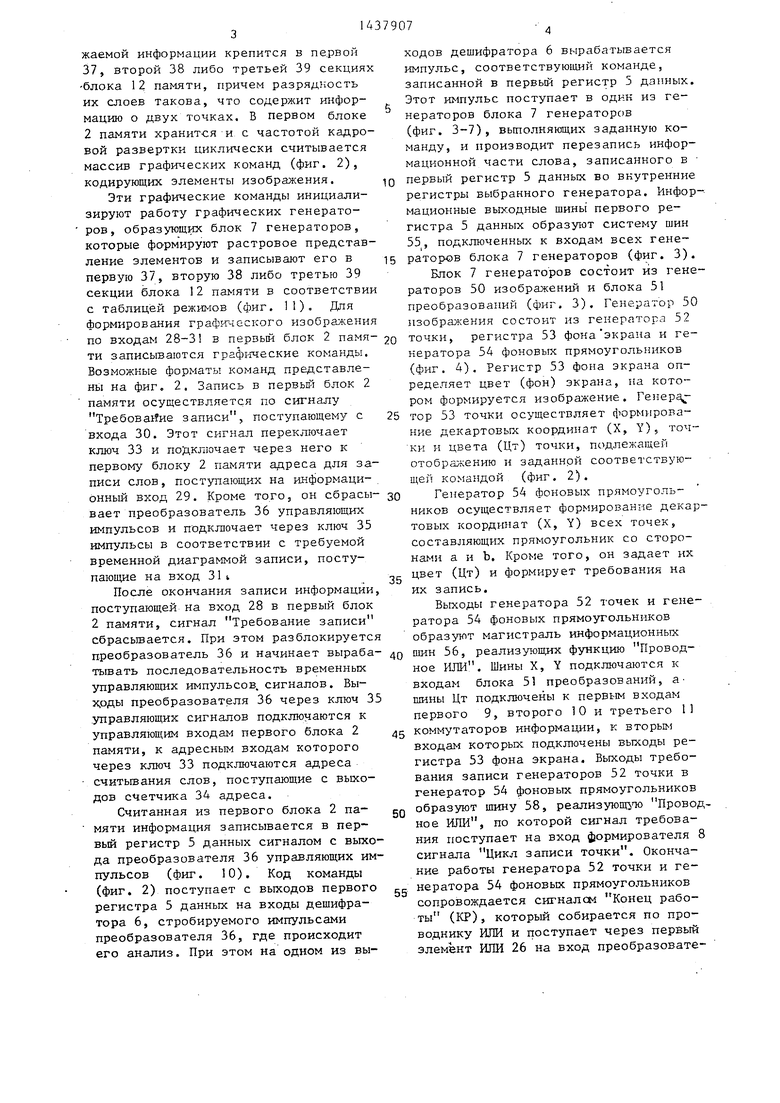

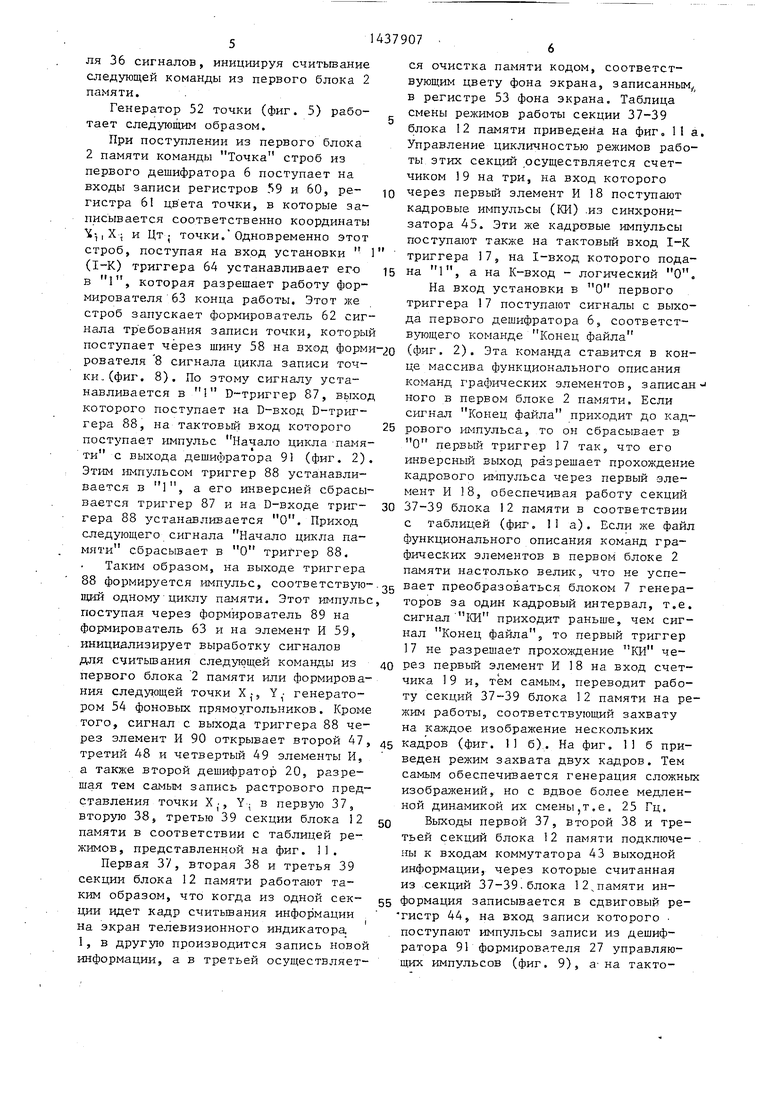

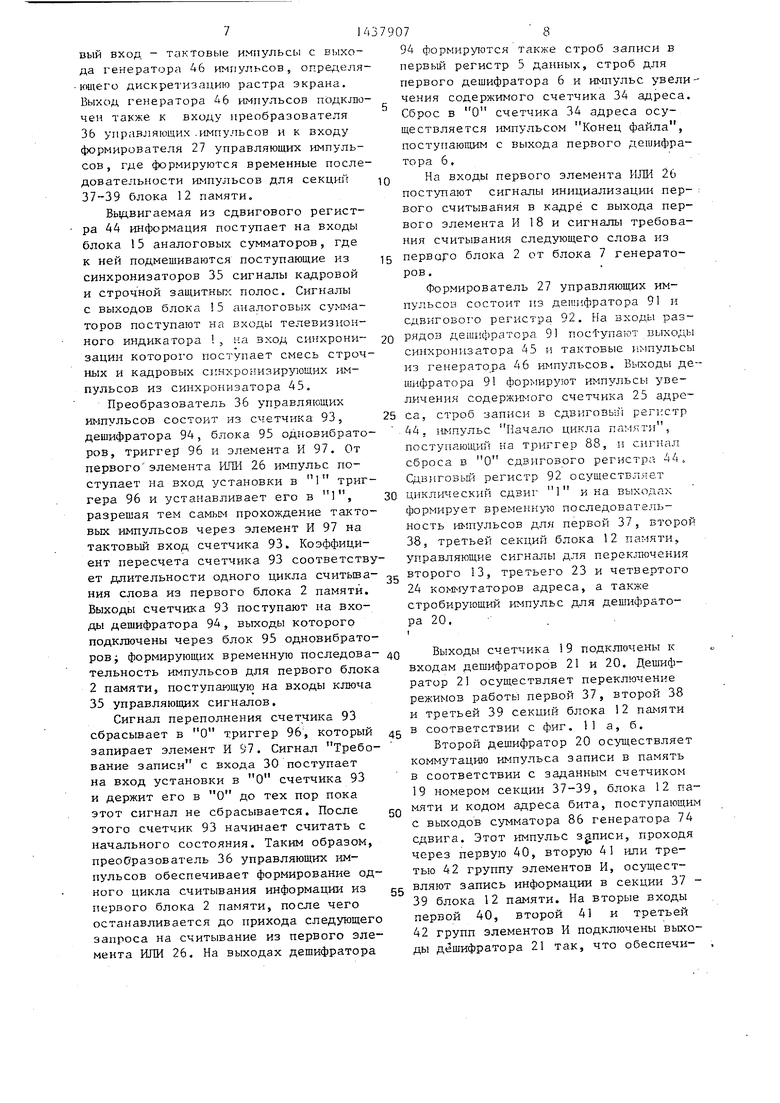

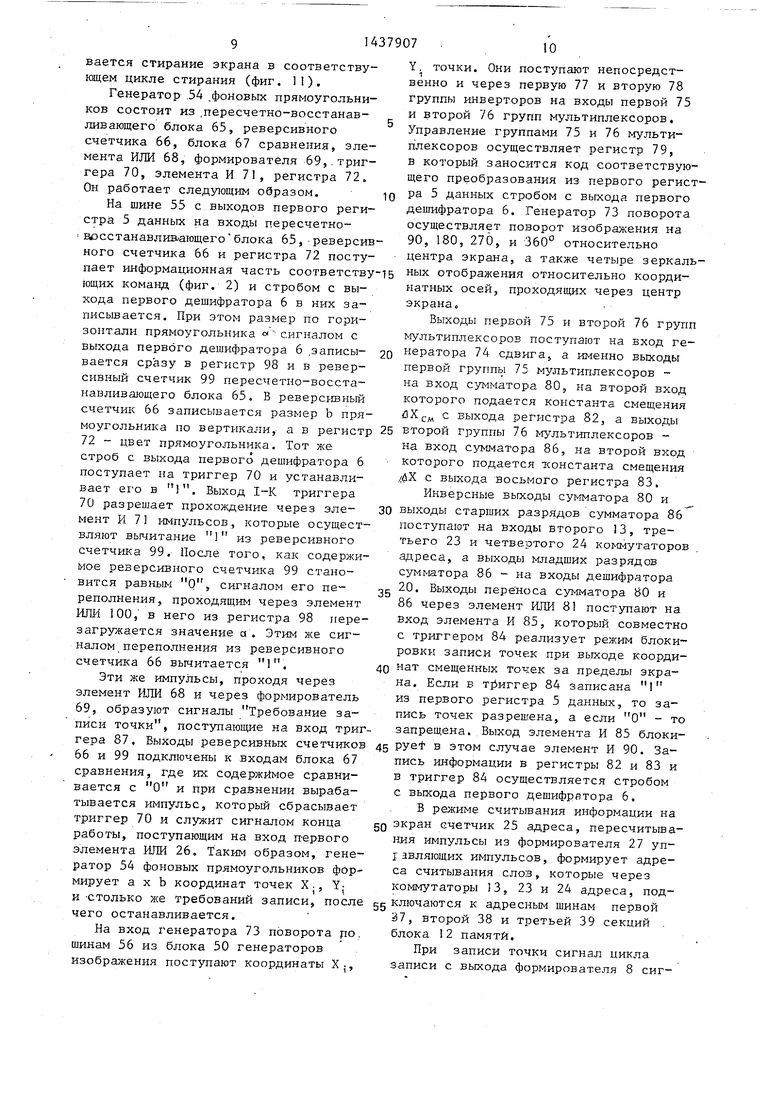

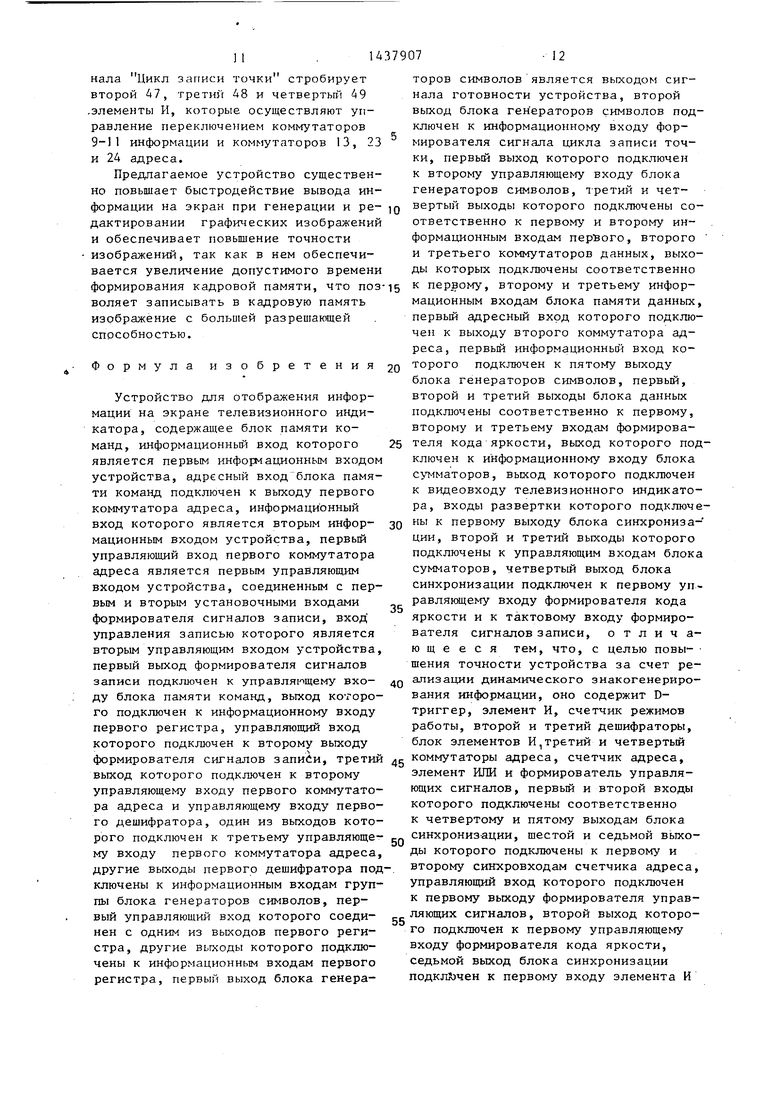

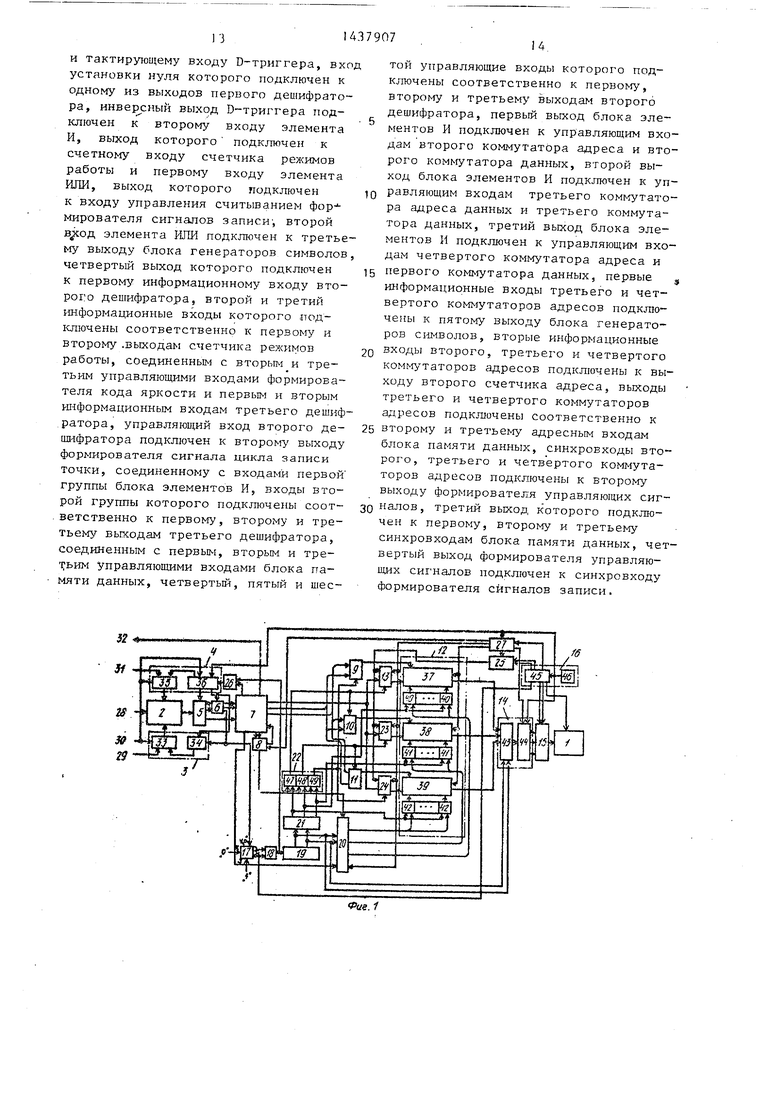

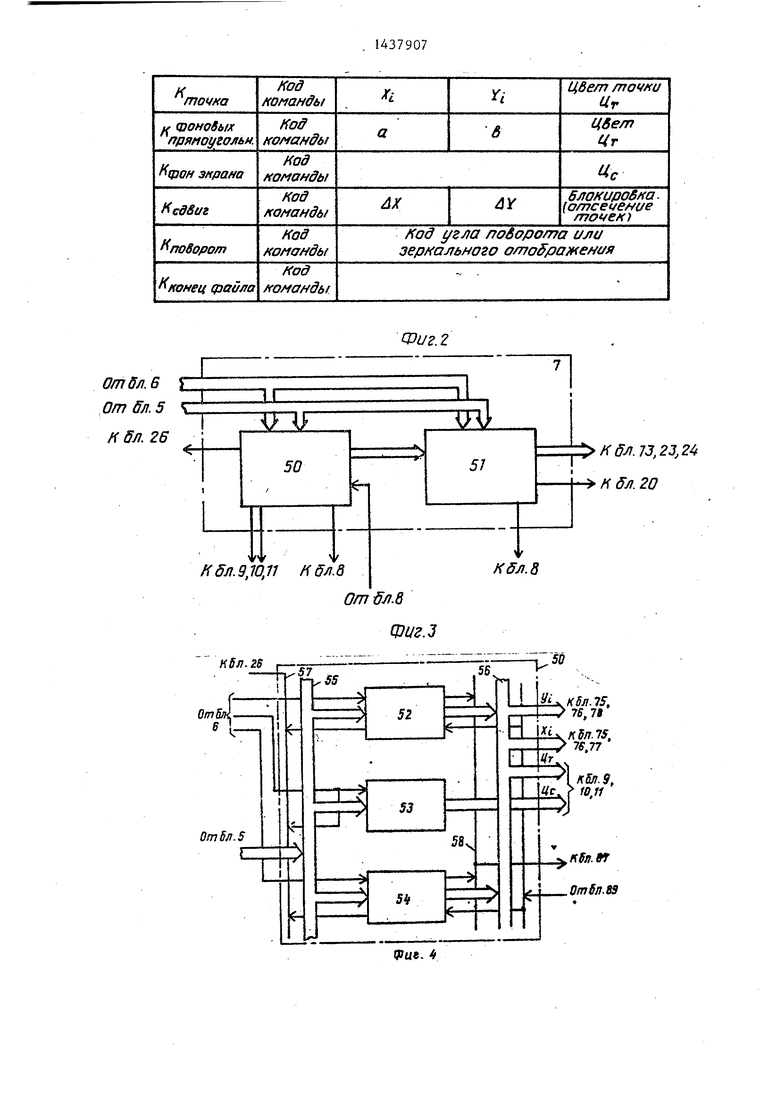

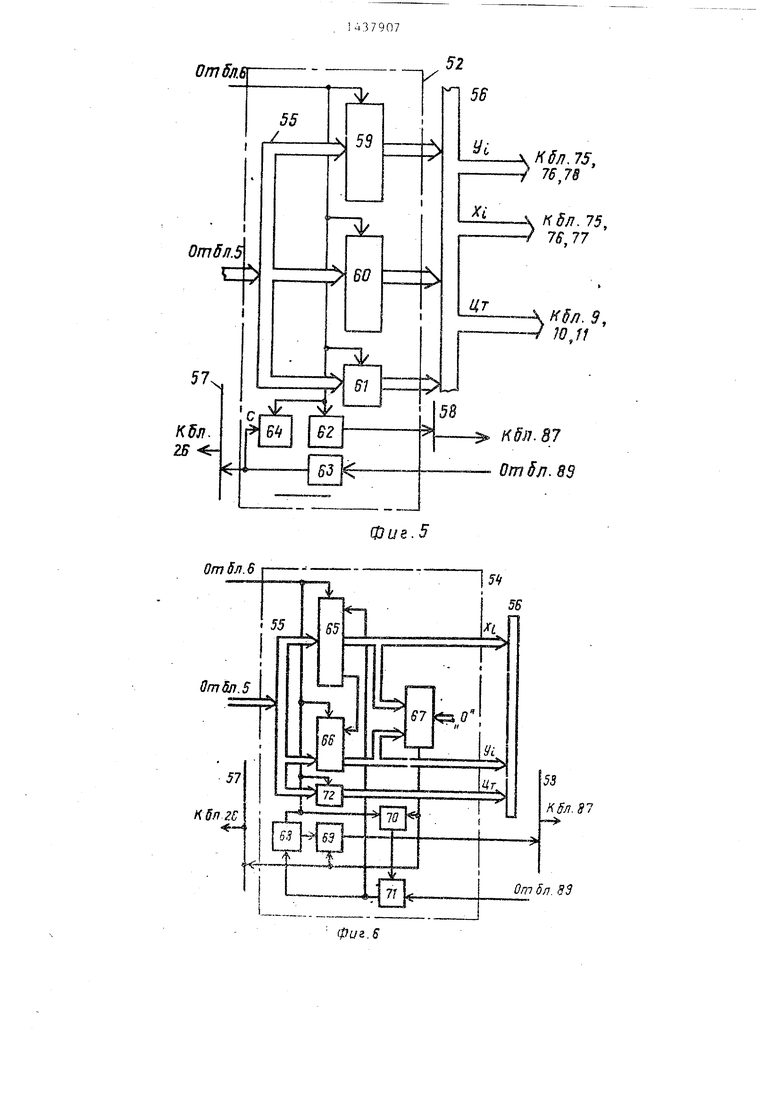

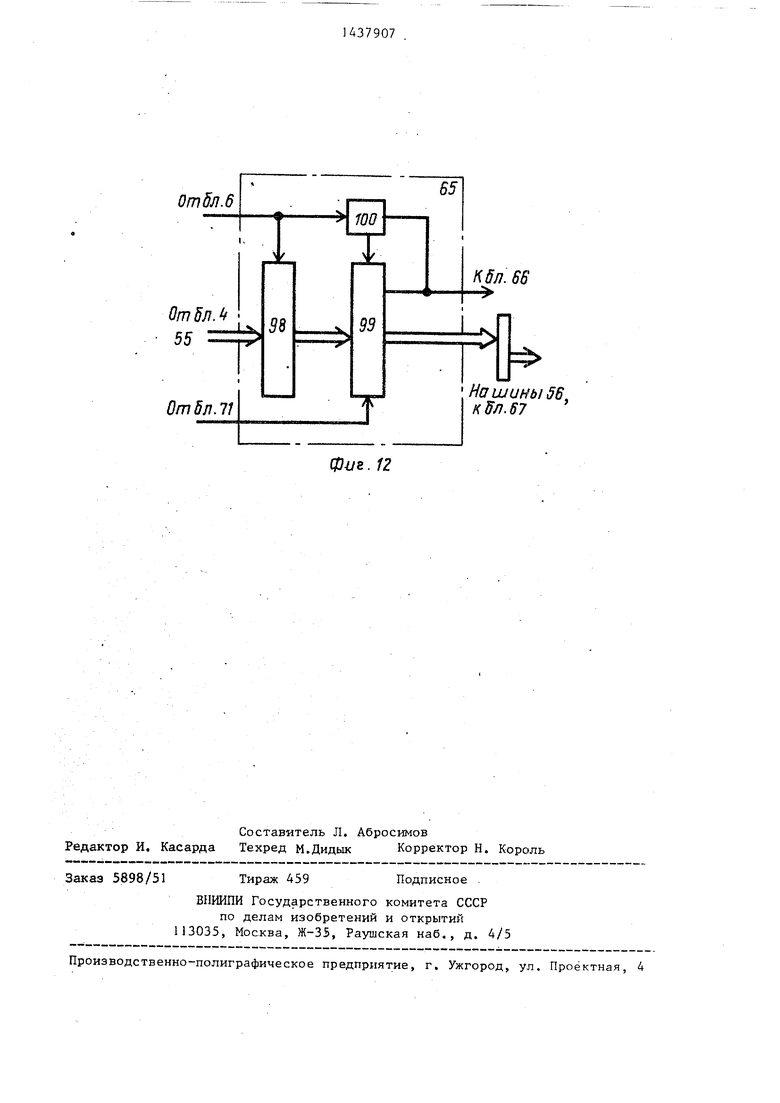

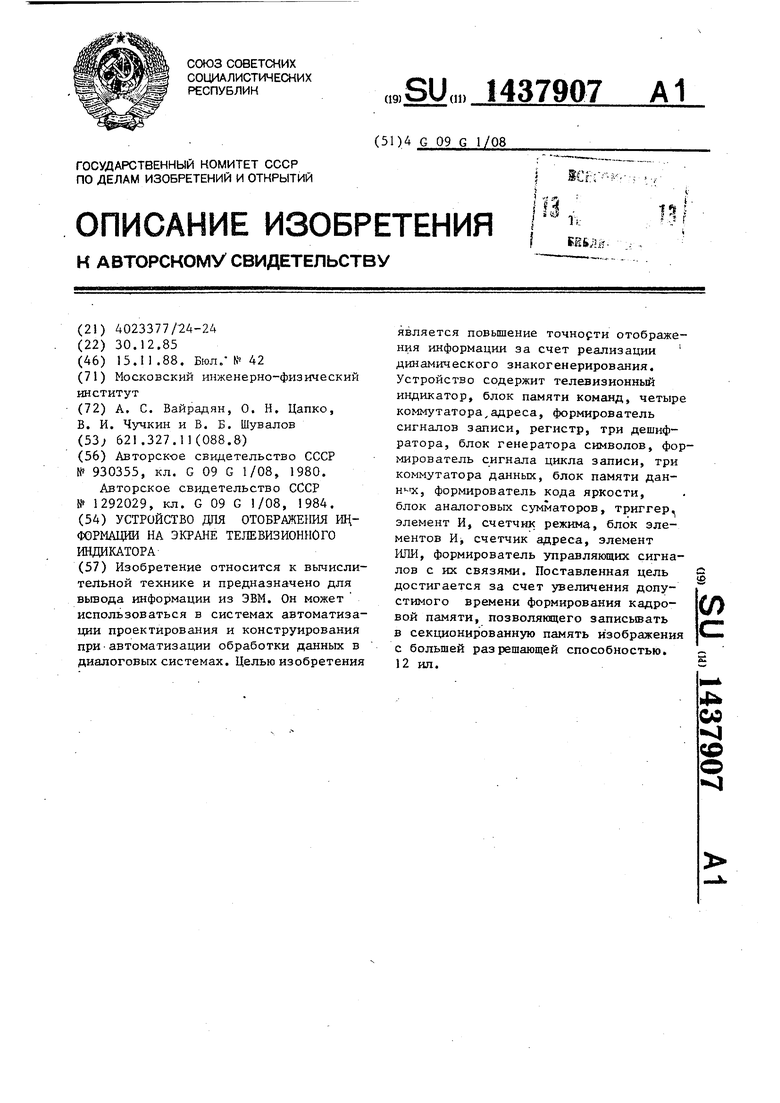

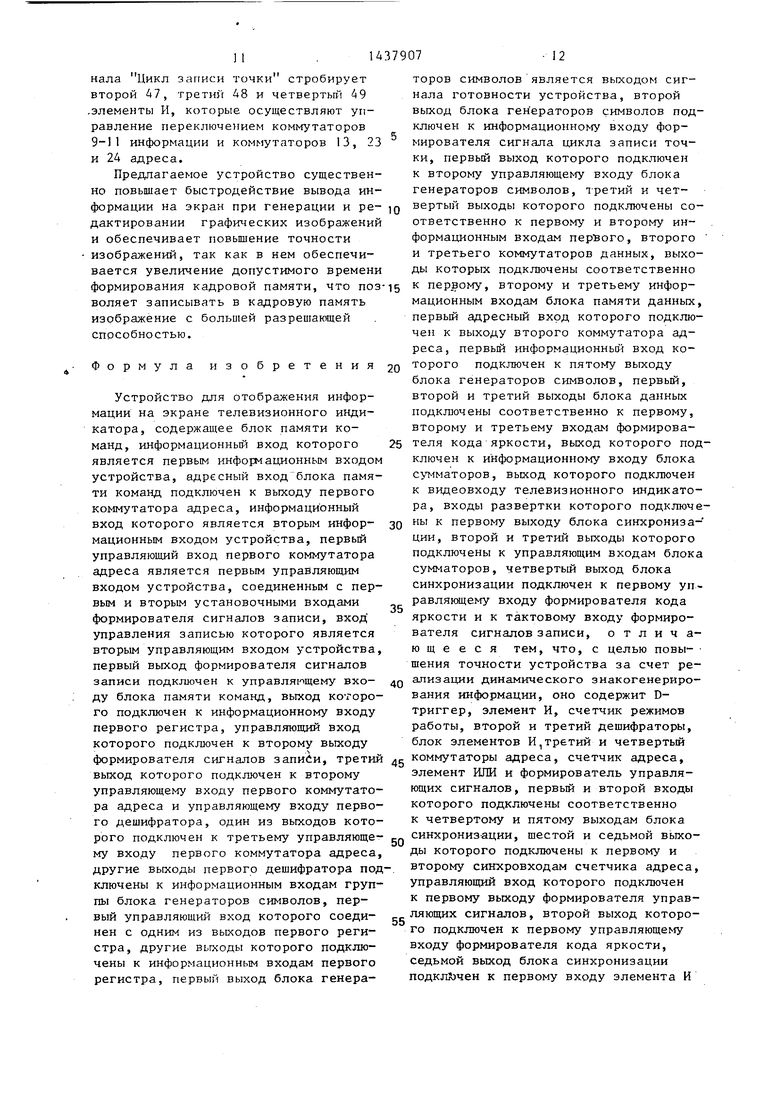

На фиг,.1 представлена блок-схема устройства; на фиг. 2 - форматы графических команд; на фиг. 3 - струк- турная схема блока генераторов символов; на фиг. А - генератор изображе-- НИИ; на фиг, 5 - генератор точки; на фиг„ 6 - генератор фоновых прямоугольников; на фиг. 7 - блок преобразова- НИИ; на фиг. 8 - формирователь сигнала цикла записи точки; на фиг„ 9 - формирователь управляющих импульсов; на фиг. 10 - преобразователь сигналов; на фиг. 11 - таблица смены режи-25 триггер 64. Генератор 54 фоновых пряБлок 12 памяти данных состоит из первой секции 37 блока 12 памяти, второй секции 38 блока 12 памяти,- третьей секции 39 блока 2 памяти, первой группы 40 элементов И, второй группы 41 элементов И, третьей группы 42 элементов И. Формирователь 14 кода яркости содержит коммутатор 43 и сдвиговый регистр 44. Блок 16 синхронизации состоит из синхронизатора 45 и генератора 46 импульсов. Блок 22 элементов И содержит второй элемент И 47, третий элемент И 48, четвертый элемент И 49. Блок 7 генераторов символов содержит генератор 50 изображений и блок 51 преобразований. Генератор, 50 изображений содержит генератор 52 точки, регистр 53 фона экрана, генератор 54 фоновых прямоугольников, входную 55 и выходную 56 шины, входную 57 и выходную 58 цепи.

Генератор 52 точки содержит регистры 59-61, формирователи 62 и 63,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство для вывода графической информации | 1988 |

|

SU1615787A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для отображения информации | 1984 |

|

SU1251062A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1425770A2 |

| Устройство для вывода графической информации | 1989 |

|

SU1644208A1 |

| Устройство для вывода графической информации | 1990 |

|

SU1783572A1 |

| Устройство для отображения графической информации | 1987 |

|

SU1474724A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для вывода графической информации | 1988 |

|

SU1615785A1 |

Изобретение относится к вычислительной технике и предназначено для вывода информации из ЭВМ. Он может использоваться в системах автоматизации проектирования и конструирования при-автоматизации обработки данных в диалоговых системах. Целью изобретения является повьшение точности отображения информации за счет реализации динамического знакогенерирования. Устройство содержит телевизионный индикатор, блок памяти команд, четыре коммутатора,адреса, формирователь сигналов записи, регистр, три дешифратора, блок генератора символов, формирователь сигнала цикла записи, три коммутатора данных, блок памяти дан- н - х, формирователь кода яркости, блок аналоговых сумматоров, триггер. элемент И, счетчик режима, блок элементов И, счетчик адреса, элемент ИЛИ, формирователь управляющих сигналов с их связями. Поставленная цель достигается за счет увеличения допустимого времени формирования кадровой памяти, позволянщего записывать в секционированную память изображения с большей разрешающей способностью. 12 ил. (Л

мов работы секций блока памяти данных; на фиг. 12 - структурная схема пересчетно-восстанавливающего блока.

моугольников содержит пересчетно-вос- станавливающий блок 65, реверсивный счетчик 66, блок 67 сравнения, элемент ИЛИ 68, формирователь 69 импульУстройство содержит телевизионный 30 сов, триггер 70, элемент И 71 и регистр 72.

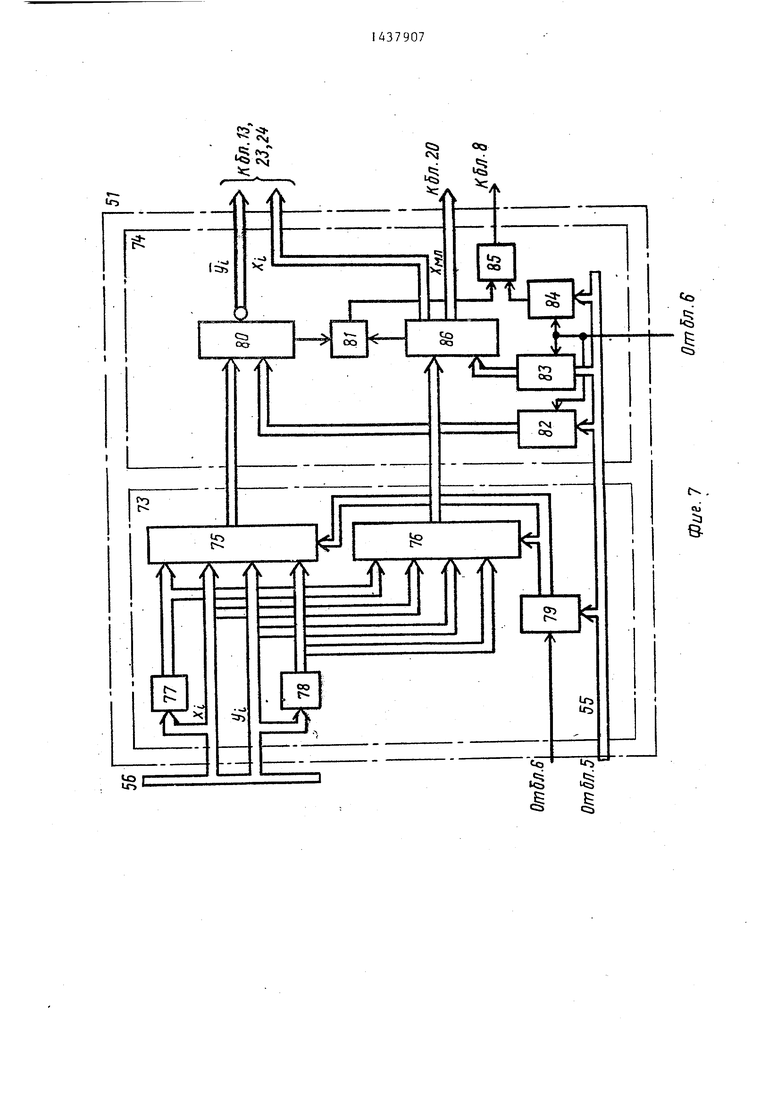

Блок 51 преобразований содерлдат генератор 73 поворота, генератор 74 сдвига, первую.группу 75 мультиплек1шдикатор 1, блок 2 памяти команд, первый коммутатор 3 адреса, формирователь 4 сигналов записи, первый регистр 5, первый дешифратор 6, блок 7

генераторов символов, формирователь 8 5 соров, вторую группу 76 мультиплексоров, первую группу 77 инверторов, ,вторую группу 78 инверторов, регистр 79, сумматор 80, элемент ИЛИ 8, регистры 82 и 83, триггер 84, элемент И 85 и сумматор 86.

сигнала цикла записи точки, первый коммутатор 9 данных, второй коммутатор 10 данных, третий кoм fyтaтop 1 данных, блок 12 памяти данных, второй коммутатор 13 адреса, формирсва- тель 14 кода яркости, блок 15 сумматоров,, блок 16 синхронизации, D-триг- гер 17, первый элемент И 18, счетчик 19 режимов работь, второй дешифратор 20, третий дешифратор 21, блок 22 элементов И, третий коммутатор 23 адреса, четвертый коммутатор 24 адреса, счетчик 25 адреса, первый элемент ИЛИ 26, формирователь 27 управляющих сигналов, первый информационный вход 28 устройства, второй информационный вход 29 устройства, первый управляющий вход 30 устройства, второй управляющий вход 3 устройства, выход 32 сигнала готовности устройства. Первый коммутатор 3 адреса состоит из ключа 33 и счетчика 34. Формирователь 4 -сигналов записи состоит из ключа 35 и преобразователя 36 сигналов.

соров, вторую группу 76 мультиплексоров, первую группу 77 инверторов, ,вторую группу 78 инверторов, регистр 79, сумматор 80, элемент ИЛИ 8, регистры 82 и 83, триггер 84, элемент И 85 и сумматор 86.

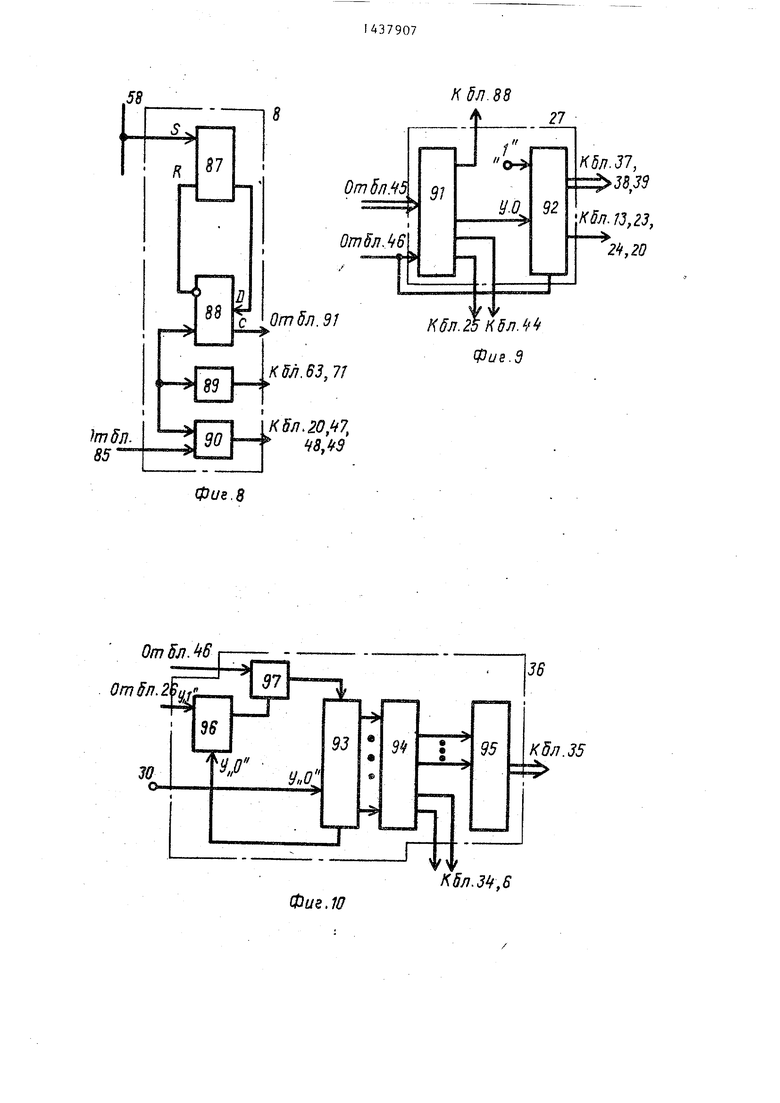

Формирователь 8 сигнала цикла записи точки содержит триггеры 87 и 88, формирователь 89 импульсов и элемент И 90. Формирователь 27 управляющих сигналов содержит дешифратор 91 и сдвиговый регистр 92. Преобразователь 36 сигналов содержит счетчик 93, дешифратор 94, блок 95 одновибрато- ров-, триггер 96 и элемент И 97. Пере- счетно-восстанавливающий блок 65 содержит регистр 98, реверсивный счетчик 99 и элемент ИЛИ 100.

Устройство работает следующим образом.

Устройство обеспечивает отображение на экране цветовой графической информации размером 2 точки по горизонтали и 2 строки по вертикали. При этом растровый эквива,пент отображаемой информации крепится в первой 37, второй 38 либо третьей 39 секциях -блока 12 памяти, причем разрядность их слоев такова, что содержит информацию о двух точках. В первом блоке 2 памяти хранится и с частотой кадровой развертки циклически считывается массив графических команд (фиг. 2), кодирующих элементы изображения.

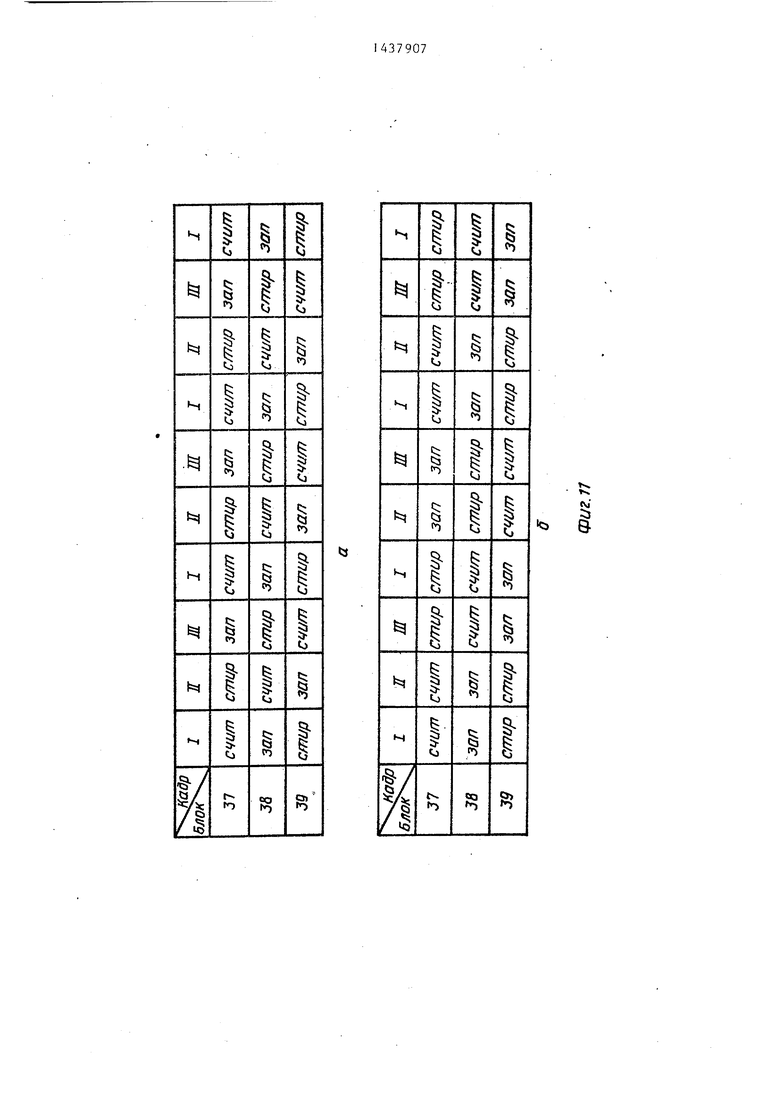

Эти графические команды инициализируют работу графических генераторов, образующих блок 7 генераторов, которые формируют растровое представление элементов и записывают его в первую 37, вторую 38 либо третью 39 секции блока 2 памяти в соответствии с таблицей режимов (фиг. 11). Для фopмиpoвшiия графг-гчсского изображения

по входам 28-3 в первый блок 2 памя- 2о точки, регистра 53 фона экрана и гети записываются граф1-1ческие команды. Возможные форматы команд представлены на фиг, 2. Запись в первый блок 2 памяти осуществляется по сигналу требование записи, поступающему с входа 30. Этот сигнал переключает ключ 33 и подключает через него к первому блоку 2 памяти адреса для записи слов, поступающих на информационный вход 29. Кроме того, он сбрасы- вает преобразователь 36 управляющих импульсов и подключает через ключ 35 импульсы в соответствии с требуемой временной диаграммой записи, поступающие на вход 31k

После окончания записи информации, поступающей на вход 28 в первый блок 2 памяти, сигнал Требование записи сбрасьшается. При этом разблокируется

преобразователь 36 и начинает выраба- о шин 56, реализующих функцию Провод- тывать последовательность временных ное ИЛИ. Шины X, Y подключаются к

управляющих импульсов, сигналов. Вы- х,оды преобразователя 36 через ключ 35 .управляющих сигналов подключаются к управляющим входам первого блока 2 памяти, к адресным входам которого через ключ 33 подключаются адреса считывания слов, поступающие с выходов счетчика 34 адреса.

Считанная из первого блока 2 памяти информация записывается в пер- вьй регистр 5 данных сигналом с выхода преобразователя 36 управляющих импульсов (фиг. 10). Код команды (фиг, 2) поступает с выходов первого регистра 5 данных на входы дешифратора 6, стробируемого импульсами преобразователя 36, где происходит его анализ. При этом на одном из выходов дешифратора 6 вырабатывается импульс, соответствующий команде, записанной в первый регистр 5 данных. Этот импульс поступает в один из генераторов блока 7 генераторов (фиг. 3-7), выполняющих заданную команду, и производит перезапись информационной части слова, записанного в

первый регистр 5 данных во внутренние регистры выбранного генератора. Информационные выходные шины первого регистра 5 данных образуют систему шин 55, подключенных к входам всех генераторов блока 7 генераторов (фиг. 3).

Блок 7 генераторов состоит из генераторов 50 изображений и блока 51 преобразований (фиг. 3), Генератор 50 изображения состоит из генератора 52

о

нератора 54 фоновых прямоугольников (фиг. 4). Регистр 53 фона экрана определяет цвет (фон) экрана, на котором формируется изображение. PeHepai 5 тор 53 точки осуществляет формирование декартовых координат (X, Y), точки и цвета (Цт) точки, подлежащей отобра:;кению и заданной соответствующей командой (фиг. 2).

Генератор 54 фоновых прямоугольников осуществляет формирование декартовых координат (X, Y) всех точек, составляющих прямоугольник со сторонами а и Ъ, Кроме того, он задает их цвет (Цт) и формирует требования на их запись.

Выходы генератора 52 точек и генератора 54 фоновых прямоугольников образуют магистраль информационных

5

входам блока 51 преобразований, а- шины Цт подключены к первым входам первого 9, второго 10 и третьего 11

коммутаторов информации, к вторьм входам которых подключены выходы регистра 53 фона экрана. Выходы требования записи генераторов 52 точки в генератор 54 фоновых прямоугольников

образуют шину 58, реализуювдто Провод- ное или, по которой сигнал требования поступает на вход формирователя В сигнала Цикл записи точки. Окончание работы генератора 52 точки и генератора 54 фоновых прямоугольников сопровождается сигналсм Конец работы (КР), который собирается по проводнику ШШ и поступает через первый элемент ИЛИ 26 на вход преобразователя 36 сигналов, инициируя считывание следующей команды из первого блока 2 памяти.

Генератор 52 точки (фиг. 5) работает следующим образом.

При поступлении из первого блока 2 памяти команды Точка строб из первого дешифратора 6 поступает на входы записи регистров 59 и 60, регистра 61 цв ета точки, в которые записывается соответственно координаты i , |Х и Цт ; точки. Одновременно этот строб, поступая на вход установки 1 (I-K) триггера 64 устанавливает ег-о в 1, которая разрешает работу форся очистка памяти кодом, соответствующим цвету фона экрана, записанным в регистре 53 фона экрана. Таблица смены режимов работы секции 37-39 блока 12 памяти приведена на фиг, 11 а Управление цикличностью режимов работы этих секций осуществляется счетчиком 19 на три, на вход которого

10 через первьй элемент И 18 поступают кадровые импульсы (КИ) .из синхронизатора 45. Эти же кадровые импульсы поступают также на тактовый вход I-K триггера 17, на 1-вход которого пода15 на 1, а на К-вход - логический О,

На вход установки в О первого мирователя 63 конца работы. Этот же триггера 17 поступают сигналы с выхо- строб запускает формирователь 62 сиг да первого дешифратора 6, соответст- нала требования записи точки, который вующего команде Конец файла поступает через шину 58 на вход форми-2о (Фиг. 2). Эта команда ставится в кон- рователя 8 сигнала цикла записи точки, (фиг. 8). По этому сигналу устанавливается в В триггер 87, выход которого поступает на D-вход D-триг- гера 88, на тактовый вход которого

це массива функционального описания команд графических элементов, записан ного в первом блоке 2 памяти. Если сигнал Конец файла приходит до кад- 25 рового 1-1Мпульса, то он сбрасывает в О первый триггер 17 так, что его инверсный выход разрешает прохождение кадрового импульса через первый элемент И 18, обеспечивая работу секций

поступает импульс Начало цикла памяти с выхода дешифратора 91 (фиг. 2). Этим импульсом триггер 88 устанавливается в 1, а его инверсией сбрасыце массива функционального описания команд графических элементов, записан ного в первом блоке 2 памяти. Если сигнал Конец файла приходит до кад- 25 рового 1-1Мпульса, то он сбрасывает в О первый триггер 17 так, что его инверсный выход разрешает прохождение кадрового импульса через первый элемент И 18, обеспечивая работу секций

вается триггер 87 и на D-входе триг- зо 37-39 блока 12 памяти в соответствии

гера 88 устанавливается О. Приход следующего сигнала Начало цикла памяти сбрасывает в О TpHfrep 88. Таким образом, на выходе триггера

с таблицей (фиг. П а). Если же файл функционального описания команд графических элементов в первом блоке 2 памяти настолько велик, что не успе- 88 формируется импульс, соответствую-.g вает преобразоваться блоком 7 генера- щий одному циклу памяти. Этот импульс, торов за один кадровый интервал, т.е. поступая через формирователь 89 на сигнал КИ приходит раньше, чем сигнал Конец файла, то первый триггер 17 не разрешает прохождение КИ че- 40 рез первый элемент И 18 на вход счетчика 19 и, тем самым, переводит работу секций 37-39 блока 12 памяти на режим работы, соответствующий захвату на каждое изображение нескольких рез элемент И 90 открывает второй 47, 45 кадров (фиг. 11 б),. На фиг, 11 б при- третий 48 и четвертый 49 элементы И, веден режим захвата двух кадров. Тем

самым обеспечивается генерация сложных изображений, но с вдвое более медленной динамикой их смены,т.е. 25 Гц. 50 Выходы первой 37, второй 38 и третьей секций блока 12 памяти подключены к входам коммутатора 43 выходной информации, через которые считанная

формирователь 63 и на элемент И 59, инициализирует выработку сигналов для считьюания следующей команды из первого блока 2 памяти или формирования следующей точки Х, генератором 54 фоновых прямоугольников. Кроме того, сигнал с выхода триггера 88 чеа также второй дешифратор 20, разрешая тем самым запись растрового представления точки Х|, Y; в первую 37, вторую 38, третью 39 секции блока 12 памяти в соответствии с таблицей режимов, представленной на фиг. П.

Первая 37, вторая 38 и третья 39 секции блока 12 памяти работают таким образом, что когда из одной секции идет кадр считьшания информации На экран телевизионного индикатора, I, в другую производится запись новой информации, а в третьей осуществляетиз секций 37-39.блока 12,памяти ин- 55 формация записывается в сдвиговый ре- Тистр 44, на вход записи которого . поступают импульсы записи из дешифратора 91 формирователя 27 управляющих импульсов (фиг. 9), а- на тактося очистка памяти кодом, соответствующим цвету фона экрана, записанным в регистре 53 фона экрана. Таблица смены режимов работы секции 37-39 блока 12 памяти приведена на фиг, 11 а. Управление цикличностью режимов работы этих секций осуществляется счетчиком 19 на три, на вход которого

через первьй элемент И 18 поступают кадровые импульсы (КИ) .из синхронизатора 45. Эти же кадровые импульсы поступают также на тактовый вход I-K триггера 17, на 1-вход которого подана 1, а на К-вход - логический О,

На вход установки в О первого триггера 17 поступают сигналы с выхо- да первого дешифратора 6, соответст- вующего команде Конец файла (Фиг. 2). Эта команда ставится в кон-

це массива функционального описания команд графических элементов, записан ного в первом блоке 2 памяти. Если сигнал Конец файла приходит до кад- рового 1-1Мпульса, то он сбрасывает в О первый триггер 17 так, что его инверсный выход разрешает прохождение кадрового импульса через первый элемент И 18, обеспечивая работу секций

из секций 37-39.блока 12,памяти ин- 55 формация записывается в сдвиговый ре- Тистр 44, на вход записи которого . поступают импульсы записи из дешифратора 91 формирователя 27 управляющих импульсов (фиг. 9), а- на такто7

выи вход - тгжтовые импульсы с выхода генератора 46 импульсов, определя- ющего дискретизацию растра экрана. Выход генератора 46 импульсов пbдкJБO- чен также к входу преобразователя 36 управляющих .импульсов и к входу формирователя 27 управляющих импульсов, где формируются временные последовательности импульсов для секций 37-39 блока 12 памяти.

Вьу,вигаемая из сдвигового регистра 44 информация поступает на входы блока 15 аналоговых сумматоров, где к ней подмешиваются поступающие из синхронизаторов 35 сигналы кадровой и строчной защитньк полос. Сигналы с выходов блока 5 аналоговых торов поступают на входы телевизионного индикатора , на вход синхронизации которого поступает смесь строчных и кадровых синхронизирующих импульсов из синхронизатора 45.

Преобразователь 36 управляющих импульсов состоит из счетчика 93, дешифратора 94, блока 95 одновибрато- ров, триггер 96 и элемента И 97. От первого элемента ИЛИ 26 импульс поступает на вход установки в 1 тригСдви1говьй регистр 92 осуществляет 111II

гера 96 и устанавливает его в 1, 30 циклический сдвиг 1 и на выходах разрешая тем самым прохождение такто- формирует временн то последовательность импульсов для первой 37, второй 38, третьей секцирт блока 12 памяти, управляющие сигналы для переключения второго 13, третьего 23 и четвертого

вых импульсов через элемент И 97 на тактовый вход счетчика 93. Коэффициент пересчета счетчика 93 соответствует длительности одного цикла считыва35ВИЯ слова из первого блока 2 памяти.

Выходы счетчика 93 поступают на входы дешифратора 94, выходы которого подключены через блок 95 одновибрато- poBj формирующих временную последова- 40 тельность импульсов для первого блока 2 памяти, поступающую на входы ключа 35 управляющих сигналов,

Сигнал переполнения счетчика 93 сбрасывает в О триггер 96, который 45 запирает элемент И 97. Сигнал Требование записи с входа 30 поступает на вход установки в О счетчика 93 и держит его в О до тех пор пока этот сигнал не сбрасывается. После 0 этого счетчик 93 начинает считать с начального состояния. Таким образом, преоОразователь 36 управляющих импульсов обеспечивает формирование одного цикла считывания информации из gg первого блока 2 памяти, после чего останавливается до прихода следующего запроса на считывание из первого элемента ИЛИ 26, На выходах дешифратора

24 коьмутаторов адреса, а также стробирующий импульс для дешифратора 20. 1

Выходы счетчика 19 подключены к входам дешифраторов 21 и 20, Дешифратор 21 осуществляет переключение режимов работы первой 37, второй 38 и третьей 39 секций блока 12 памяти в соответствии с фиг. 11 а, б.

Второй дешифратор 20 осуществляет коммутацию импульса записи в память в соответствии с заданным счетчиком 19 номером секции 37-39, блока 12 памяти и кодом адреса бита, поступающим с выходов сумматора 86 генератора 74 сдвига. Этот импульс записи, проходя через первую 40, вторую 41 или третью 42 группу элементов И, осуществляют запись информации в секции 37 - 39 блока 12 памяти. На вторые входы первой 40, второй 41 и третьей 42 групп элементов И подключены вько- ды дешифратора 21 так, что обеспечи-- 437907 8

94 формируются также строб записи в первый регистр 5 данных, строб для первого дешифратора 6 и импульс увеличения содержимого счетчика 34 адреса.

Сброс в О счетчика 34 адреса осуществляется 1шпульсом Конец файла, поступающим с выхода первого дешифратора 6 ,

На входы первого элемента ИЛИ 26 поступают сигналы инициализации пер- вого считывания в кадре с выхода первого элемента И 18 и сигналы требования считывания следующего слова из

первого блока 2 от блока 7 генераторов.

Формирователь 27 управляюш;их импульсов состоит из дешифратора 91 и сдвигового регистра 92. На входы разрядов деш1к1)ратора 91 noctynaioT выходы синхронизатора 45 и тактовые импульсы из генератора 46 импульсов. Выходы дешифратора 91 формируют импульсы увеличения содержз-гмого счетчика 25 адреса, строб записи в сдвиговь;й регистр 44. и пульс Начало цикла памяти, поступающий на триггер 88, и сигнал сброса в О сдвигового регистра 44

Сдви1говьй регистр 92 осуществляет 111II

циклический сдвиг 1 и на выходах формирует временн то последовательность импульсов для первой 37, второй 38, третьей секцирт блока 12 памяти, управляющие сигналы для переключения второго 13, третьего 23 и четвертого

24 коьмутаторов адреса, а также стробирующий импульс для дешифратора 20. 1

Выходы счетчика 19 подключены к входам дешифраторов 21 и 20, Дешифратор 21 осуществляет переключение режимов работы первой 37, второй 38 и третьей 39 секций блока 12 памяти в соответствии с фиг. 11 а, б.

Второй дешифратор 20 осуществляет коммутацию импульса записи в память в соответствии с заданным счетчиком 19 номером секции 37-39, блока 12 памяти и кодом адреса бита, поступающим с выходов сумматора 86 генератора 74 сдвига. Этот импульс записи, проходя через первую 40, вторую 41 или третью 42 группу элементов И, осуществляют запись информации в секции 37 - 39 блока 12 памяти. На вторые входы первой 40, второй 41 и третьей 42 групп элементов И подключены вько- ды дешифратора 21 так, что обеспечивается стирание экрана в соответству- 1ацем цикле стирания (фиг. 11),

Генератор .54 ,фоновых прямоугольников состоит из .пересчетно-восстанав- ливающего блока 65, реверсивного счетчика 66, блока 67 сравнения, элемента ИЛИ 68, формирователя 69,.триггера 70, элемента И 71, регистра 72. Он работает следующим образом.

На шине 55 с выходов первого регистра 5 данных на входы пересчетно- восстанавлив ающего блока 65, -реверсивного счетчика 66 и регистра 72 поступает информационная часть соответству-15 ix отображения относительно координатных осей, проходящих через центр экрана.

Выходы первой 75 и второй 76 групп мультиплексоров поступают на вход ге2Q нератора 74 сдвига а именно выходы первой группы 75 мультиплексоров на вход сумматора 80, на второй вход которого подается константа смещения йХ. с выхода регистра 82, а выходы

25 второй группы 76 мультиплексоров - на вход сумматора 86, на второй вход которого подается константа смещения /ДХ с выхода восьмого регистра 83, Инверсные выходы сумматора 80 и

30 выходы старших разрядов сумматора 86 поступают на входы второго 13, третьего 23 и четвертого 24 коммутаторов адреса, а выходы младших разрядов

ющих команд (фиг. 2) и стробом с выхода первого дешифратора 6 в них записывается. При этом размер по горизонтали прямоугольника сигналом с выхода первого дешифратора 6 .записывается сразу в регистр 98 и в реверсивный счетчик 99 пересчетно-восста- навливающего блока 65. В реверсивный счетчик 66 записывается размер b прямоугольника по вертикали, а в регистр 72 - цвет прямоугольника. Тот же строб с выхода первого дешифратора 6 поступает на триггер 70 и устанавливает его в . Выход I-K триггера 70 разрешает прохождение через элемент И 71 импульсов, которые осуществляют вычитание 1 из реверсивного счетчика 99, После того, как содержимое реверсивного счетчика 99 становится равным О сигналом его переполнения, проходящим через элемент ИЛИ 100, в него из регистра 98 перезагружается значение а. Этим же сигналом, переполнения из реверсивного счетчика 66 вычитается 1.

Эти же импульсы, проходя через элемент ИЛИ 68 и через формирователь 69, образуют сигналы Требование засумматора 86 - на входы дешифратора 2g 20. Выходы пере носа сумматора 80 и 86 через элемент ИЛИ 81 поступают на вход элемента И 85, который, совместно с триггером 84 реализует режим блокировки записи точек при выходе коорди- 40 нат смещенных точек за пределы экрана. Если в TjiMrrep 84 записана 1 из первого регистра 5 данных, то запись точек разрешена, а если О - то писи точки, поступающие на вход триг- запрещена. Выход элемента И 85 блоки- гера 87, Выходы реверсивных счетчиков 45 РУ в этом случае элемент И 90. За66 и 99 подключены к входам блока 67 сравнения, где их содержимое сравнивается с О и при сравнении вырабатывается импульс, который сбрасывает триггер 70 и служит сигналом конца работы, поступающим на вход п-ервого элемента ИЛИ 26. Таким образом, генератор 54 фоновых прямоугольников формирует а X b координат точек Х., Y- и -столько же требований записи, после gg чего останавливается.

На вход генератора 73 поворота ро. шинам 56 из блока 50 генераторов изображения поступают координаты Х,-,

пись информации в регистры 82 и 83 и в триггер 84 осуществляется стробом с выхода первого дешифратора 6.

В режиме считывания информации на gg экран счетчик 25 адреса, пересчитывания импульсы из формирователя 27 уп- Jзвляющих импульсов, формирует адреса считывания .слов, которые через коммутаторы 13, 23 и 24 адреса, подключаются к адресным шинам первой 37, второй 38 и третьей 39 секций . блока 12 памяти.

При записи точки сигнал цикла записи с выхода формирователя 8 сигY. точки. Они поступают непосредственно и через первую 77 и вторую 78 группы инверторов на входы первой 75 и второй 76 групп мультиплексоров. Управление группами 75 и 76 мультиплексоров осуществляет регистр 79, в который заносится код соответствующего преобразования из первого регистра 5 данных стробом с выхода первого дешифратора 6. Генератор 73 поворота осуществляет поворот изображения на 90, 180, 270, и 360° относительно центра экрана, а также четыре зеркальg

пись информации в регистры 82 и 83 и в триггер 84 осуществляется стробом с выхода первого дешифратора 6.

В режиме считывания информации на g экран счетчик 25 адреса, пересчитывания импульсы из формирователя 27 уп- Jзвляющих импульсов, формирует адреса считывания .слов, которые через коммутаторы 13, 23 и 24 адреса, подключаются к адресным шинам первой 37, второй 38 и третьей 39 секций . блока 12 памяти.

При записи точки сигнал цикла записи с выхода формирователя 8 сигнала Цикл заггисн точки стробирует второй 47, третий 48 и четвертьш 49 элементы И, которые осуществляют управление переключением коммутаторов 9-11 информации и коммутаторов 13, 23 и 24 адреса.

Предлагаемое устройство существенно повышает быстродействие вывода информации на экран при генерации и редактировании графических изображений и обеспечивает повышение точности изображений, так как в нем обеспечивается увеличение допустимого времени формирования кадровой памяти, что позволяет записывать в кадровую память изображение с большей разрешающей способностью.

Формула изобретения

Устройство для отображения информации на экране телевизионного индикатора, содержащее блок памяти команд, информационный вход которого является первым информационным входом устройства, адресный вход блока памяти команд подключен к выходу первого коммутатора адреса, информационный вход которого является вторым информационным входом устройства, первый управляющий вход первого коммутатора адреса является первым управляющим входом устройства, соединенным с первым и вторым установочными входами формирователя сигналов записи, вход управления записью которого является вторым управляющим входом устройства, первый выход формирователя сигналов записи подключен к управляющему входу блока памяти команд, выход которого подключен к информационному входу первого регистра, управляющий вход которого подключен к второму выходу формирователя сигналов запийи, третий выход которого подключен к второму управляющему входу первого коммутатора адреса и управляющему входу первого дешифратора, один из выходов которого подключен к третьему управляющему входу первого коммутатора адреса другие выходы первого дешифратора под ключены к информационным входам группы блока генераторов символов, первый управляющие вход которого соединен с одним из выходов первого регистра, другие выходы которого подключены к информационным входам первого регистра, первый выход блока генераторов символов является выходом сигнала готовности устройства, второй выход блока ген ераторов символов подключен к информационному входу формирователя сигнала цикла записи точки, первьй выход которого подключен к BTopONty управляющему входу блока генераторов символов, третий и четQ вертый выходы которого подключены соответственно к первому и второму информационным входам первого, второго и третьего коммутаторов данных, выходы которых подключены соответственно

5 к первому, второму и третьему информационным входам блока памяти данных, первый адресный вход которого подключен к выходу второго коммутатора адреса, первьй информационный вход ко0 торого подключен к пятому выходу блока генераторов символов, первьй, второй и третий выходы блока данных подключены соответственно к первому, второму и третьему входам формирова5 теля кода яркости, выход которого подключен к информационному входу блока сумматоров, выход которого подключен к видеовходу телевизионного индикатора, входы развертки которого подключеQ ны к первому выходу блока синхрониза- ции, второй и третий выходы которого подключены к управляющим входам блока сумматоров, четвертьй выход блока синхронизации подключен к первому управляющему входу формирователя кода яркости и к тактовому входу формирователя сигналов записи, отличающееся тем, что, с целью повы- шения точности устройства за счет ализации динамического знакогенериро- вания информации, оно содержит D- триггер, элемент И, счетчик режимов работы, второй и третий дешифраторы, блок элементов И,третий и четвертьй

- коммутаторы адреса, счетчик адреса, элемент ИЛИ и формирователь управляющих сигналов, первьй и второй входы которого подключены соответственно к четвертому и пятому выходам блока синхрониз-ации, шестой и седьмой Bbixo- ды которого подключены к первому и второму синхровходам счетчика адреса, управляющий вход которого подключен к первому выходу формирователя управляющих сигналов, второй выход которого подключен к первому управляющему входу формирователя кода яркости, седьмой выход блока синхронизации подключен к первому входу элемента И

35

50

55

и тактирующему входу D-триггера, вход установки нуля которого подключен к одному из выходов первого дешифратора, инверсный выход D-триггера подключен к второму входу элемента И, выход которого подключен к счетному входу счетчика режимов работы и первому входу элемента ИЛИ, выход которого подключен к входу управления считыванием фор- мирователя сигналов записи-, второй BjkoA элемента ИЛИ подключен к третьему выходу блока генераторов символов четвертый выход которого подключен к первому информационному входу второго дешифратора, второй и третий информационные входы которого подключены соответственно к первому и второму .выходам счетчика режимов работы, соединенньпу с вторым и третьим управляющими входами формирователя кода яркости и первым и вторым ш-1формационным входам третьего дешиф- .ратора, управляющий вход второго дешифратора подключен к второму выходу формирователя сигнала цикла записи точки, соединенному с входами первой группы блока элементов И, входы второй группы которого подключены соот- .ветственно к первому, второму и третьему выходам третьего дешифратора, соединенным с первым, вторым и тре- Управляющими входами блока памяти данных, четвертый, пятый и шес2S

Ц 2 ---4z:

5

той управляющие входы которого под- кхшчены соответственно к первому, второму и третьему выходам второго дешифратора, первый выход блока элементов И подключен к управляющим входам второго коммутатора адреса и второго комьтутатора данных, второй выход блока элементов И подключен к управляющим входам третьего коммутатора адреса данных и третьего коммутатора данных, третий выход блока элементов И подключен к управляющим входам четвертого коммутатора адреса и первого коммутатора данных, первые , ш- формационные входы третьего и четвертого коммутаторов адресов подключены к пятому выходу блока генераторов символов, вторые информационные

Q входы второго, третьего и четвертого коммутаторов адресов подключены к выходу второго счетчика адреса, выходы третьего и четвертого коммутаторов адресов подкл очены соответственно к

5 второму и третьему адресным входам блока памяти данных, синхровходы второго, третьего и четвертого коммутаторов адресов подключены к второму выходу формирователя управляющих сиг0 налов, третий выход которого подключен к первому, второму и третьему синхровходам блока памяти данных, четвертый выход формирователя управляющих сиг налов подключен к синхровходу формирователя сигналов записи.

От йл.6 Фиг.З

CPU г. 2

«Pue.

Kdjf.

2Б Н

фиг. 6

Н$л.75, V 76 JB

-Л К 6л. 75, -/ 7(f.77

-Л К5л. 9,

-V

- Нбл.87

От 5л. 83

.5

53

К5л. 37

С

4гз

§ §

Со

С-- .

(U

:з S

58

R

S7

От 5л.А

QmSnM

1

От 5л. 91

К5л.63,71

ВО

КЬл.20,7 48,if3

Фие.8

Фие.Ю

К 5л. 88

27

1 СНН

Н5Л.37,

.

92

.13,гЗ, 2,20

Кбл.25 Кбл.

Фиг.д

К5л.35

К 5л. 3,6

ics

;::

| Устройство для вывода графической информации | 1979 |

|

SU930355A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1292029A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1988-11-15—Публикация

1985-12-30—Подача