Изобретение относится к импульсной технике и может использоваться в вычислительной технике при моделировании случайных процессов, тестировании каналов связи и аппаратуры.

Известен управляемый генератор случайных импульсов (см. Авт. св. СССР №1818685, кл. H03K 3/84, 1993), содержащий датчик случайных импульсов, первую и вторую группы элементов И, первый многовходовый элемент ИЛИ, входы которого подключены к выходам группы триггеров, К-входы которых подключены к выходам первой группы элементов И, счетчик импульсов, первый и второй элементы И, элемент НЕ и первый элемент ИЛИ, второй и третий многовходовые элементы ИЛИ, второй элемент ИЛИ и датчик случайных двоичных цифр, вход которого соединен с выходом второго многовходового элемента ИЛИ, а выход подключен к вторым входам первой группы элементов И, первые входы которых подключены к выходам соответствующих датчиков случайных импульсов и к входам второго многовходового элемента ИЛИ, выходы первой группы элементов И подключены к первым входам второй группы элементов И, вторые входы которых соединены с выходами группы триггеров, J-входы которых соединены с выходом второго элемента И, R-входы группы триггеров соединены с выходом первого элемента И, причем первые входы первого и второго элементов И соединены с выходами соответственно первого и второго элементов ИЛИ, первые входы которых подключены к выходу переполнения счетчика импульсов, R- и С-входы которого соединены соответственно с выходами третьего и первого многовходовых элементов ИЛИ, входы третьего многовходового элемента ИЛИ соединены с выходами второй группы элементов И, при этом вторые входы первого и второго элементов И соответственно подключены к шинам "Сброс" и "Пуск", а второй вход первого элемента подключен через элемент НЕ ко второму входу второго элемента ИЛИ и к шине "Режим", входы управления датчика случайных и двоичных цифр и счетчика импульсов подключены к соответствующим шинам управления.

В генераторе реализован сложный алгоритм воздействия на базовые последовательности случайных импульсов, позволяющий регулировать вероятности событий (появление единичных импульсов) на выходах устройства, оцениваемые с учетом значений математических ожиданий интенсивности базовых случайных сигналов.

Основными недостатками известного устройства является нелинейная зависимость регулируемой вероятности событий от управляющего воздействия, пониженное быстродействие при программно-аппаратной реализации вследствие сложности алгоритма управления, регулирование вероятности событий только в сторону уменьшения от базовой, вследствие «прореживания» базового потока, невозможность управления параметрами базовых случайных потоков.

Наиболее близким по технической сущности к предлагаемому устройству является генератор псевдослучайных сигналов (см. Авт. св. СССР №1437974, кл. H03K 3/84, 1988), содержащий шину тактовых импульсов, соединенную с входом синхронизации регистра, выходы которого соединены с первыми входами соответствующих элементов И группы элементов И, выходы элементов И которой соединены с входами сумматора по модулю два, первую группу шин, вторую группу шин, соответствующие разряды которой соединены с первой группой информационных входов и входом управления мультиплексора, выходы которого соединены с соответствующими информационными входами оперативного запоминающего устройства, соответствующие шины первой группы шин соединены с первым входом элемента И, с входом установки, с входом управления и с соответствующими информационными входами счетчика импульсов, выходы разрядов которого соединены с соответствующими адресными входами постоянного запоминающего устройства, соответствующие выходы которого соединены с вторыми входами соответствующих элементов И группы элементов И, шина тактовых импульсов соединена с входом управления оперативного запоминающего устройства, со счетным входом счетчика импульсов, выход переполнения которого соединен с вторым входом элемента И, выход которого соединен с входом синхронизации счетчика импульсов, выходы разрядов которого соединены с соответствующими адресными входами оперативного запоминающего устройства, выходы которого соединены с соответствующими информационными входами регистра, j-й выход которого соединен с (j+1)-м входом второй группы информационных входов мультиплексора, первый вход второй группы информационных входов которого соединен с выходом сумматора по модулю два.

Устройство-прототип обеспечивает раздельное управление параметрами псевдослучайных чисел в тактах работы генератора с сохранением предшествующих состояний. Управляемость генератора обеспечивается на уровне задания начальных условий для формируемых псевдослучайных сигналов, на уровне пространственно-временного равномерного распределения нулей и единиц за счет изменения характеристических порождающих полиномов и за счет возможности формирования многомерных полипсевдослучайных потоков данных, порождаемых разными характеристическими порождающими полиномами.

Несмотря на широкие возможности по управлению параметрами генерируемых сигналов, основным его недостатком является сохранение базового равномерного распределения с вероятностью событий (появление логической единицы) Р=0,5 во всех режимах работы.

Целью изобретения является расширение функциональных возможностей генератора за счет управления вероятностями событий на выходных шинах устройства.

Для достижения указанной цели в генератор псевдослучайных сигналов, содержащий блоки оперативной памяти и постоянной памяти, адресные входы которых поразрядно объединены и подключены к выходам двоичного счетчика, суммирующий вход которого подключен к выходу элемента И, первый вход которого является входом задания режима работы генератора, а второй - является входом синхронизации устройства, подключенным к входу записи/чтения блока оперативной памяти и входу синхронизации параллельного регистра, входы которого соединены с выходами данных блока оперативной памяти, входы данных которого подключены к выходам мультиплексора, первая группа информационных входов мультиплексора является шиной задания начальных условий устройства, а вход переключения канала передачи - входом перевода генератора из режима задания начальных условий в режим генерации псевдослучайных сигналов, первый информационный вход второй группы информационных входов мультиплексора соединен с выходом сумматора по модулю два, второй информационный вход - подключен к первому выходу параллельного регистра, каждый j-й информационный вход соединен соответственно с j-1-м выходом параллельного регистра, каждый выход которого дополнительно подключен к первым входам первой группы элементов И, вторые входы которых соединены с выходами блока постоянной памяти, а выходы подсоединены к входам сумматора по модулю два, выходы регистра при этом образуют первую группу выходов устройства, входы задания и записи начальных условий двоичного счетчика являются входами задания базового адреса блоков оперативной и постоянной памяти, дополнительно включены вторая группа элементов И, группа элементов ИЛИ и формирователь импульсов с регулируемой длительностью, первый вход которого соединен с входом синхронизации устройства, второй - является входом задания длительности формируемого импульса, а выход подключен к вторым объединенным входам второй группы элементов И и группы элементов ИЛИ, первые входы которых поразрядно объединены и соединены с выходами параллельного регистра, выходы второй группы элементов И образуют вторую группу выходов устройства, а выходы группы элементов ИЛИ - третью группу выходов устройства.

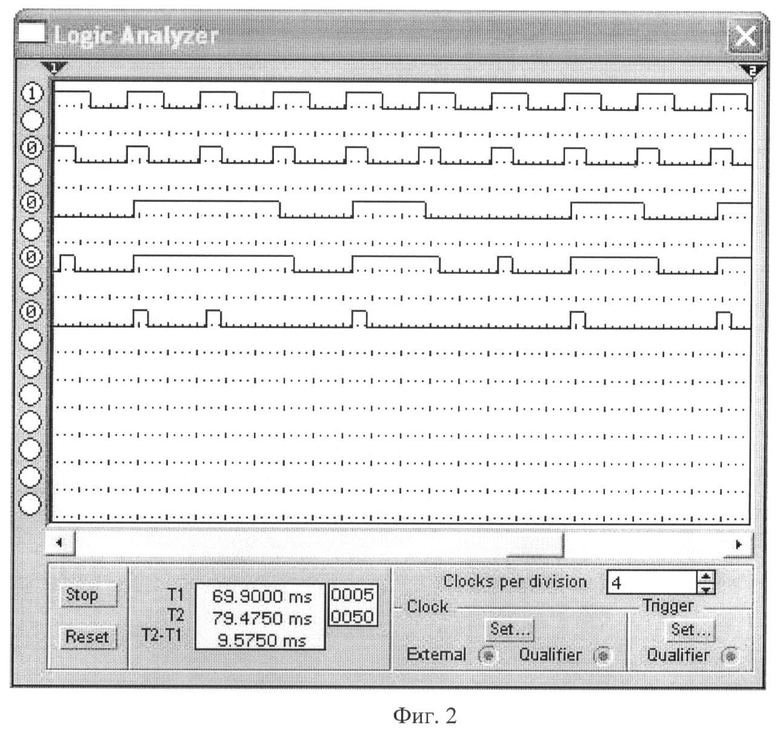

Фиг.1 отображает структурную схему генератора псевдослучайных сигналов.

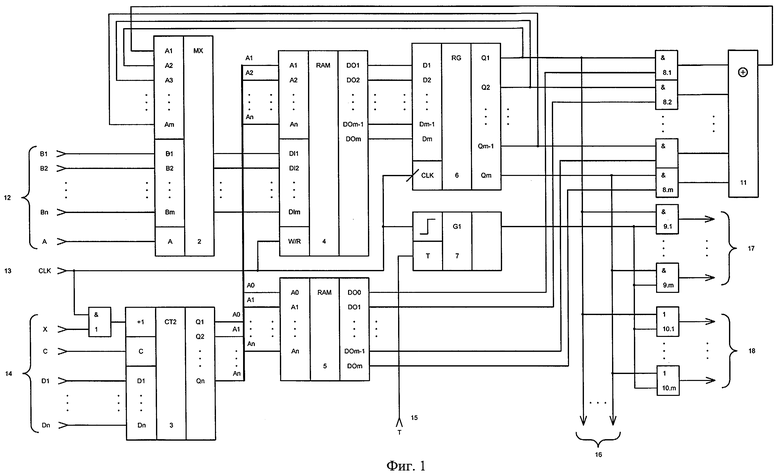

Фиг.2 отображает временные диаграммы работы устройства, полученные при создании компьютерной модели с помощью виртуального логического анализатора.

Генератор псевдослучайных сигналов содержит элемент И 1, мультиплексор 2, двоичный счетчик 3, блок 4 оперативной памяти, блок 5 постоянной памяти, параллельный регистр 6, формирователь импульсов 7 с регулируемой длительностью, первую группу 8 элементов И, вторую группу 9 элементов И, группу 10 элементов ИЛИ, сумматор по модулю два 11, шину 12 задания начальных условий, вход 13 синхронизации устройства, шину управления 14, вход 15 задания длительности формируемого импульса, первую группу 16, вторую группу 17 и третью группу 18 выходов.

Адресные входы блоков 4 и 5 оперативной и постоянной памяти поразрядно объединены и подключены к выходам двоичного счетчика 3, суммирующий вход которого соединен с выходом элемента И 1, первый вход которого является входом Х задания режима работы генератора, а второй является входом CLK синхронизации устройства, подключенным к входу записи/чтения блока 4 оперативной памяти и входу синхронизации параллельного регистра 6. Входы задания (D1-Dn) и записи С начальных условий двоичного счетчика 3 являются входами задания базового адреса блоков оперативной и постоянной памяти и совместно с входом Х задания режима работы генератора образуют шину 14 управления. Первая группа информационных входов (В1-Bm) мультиплексора 2 совместно с входом А переключения канала являются шиной 12 задания начальных условий. Первый информационный вход второй группы информационных входов мультиплексора 2 соединен с выходом сумматора по модулю два 11, второй информационный вход подключен к первому выходу параллельного регистра 6, каждый j-й информационный вход соединен соответственно с j-1-м выходом параллельного регистра 6, каждый выход которого дополнительно подключен к первым входам первой группы 8 элементов И, вторые входы которых соединены с выходами блока 5 постоянной памяти, а выходы подсоединены к входам сумматора по модулю два 11. Выходы мультиплексора 2 поразрядно подключены к входам данных блока 4 оперативной памяти, выходы данных которого соединены с соответствующими входами параллельного регистра 6. Первый вход формирователя импульсов 7 с регулируемой длительностью соединен с входом 13 (CLK) синхронизации устройства, второй - является входом 15 (Т) задания длительности формируемого импульса, а выход подключен к вторым объединенным входам второй группы 9 элементов И и группы 10 элементов ИЛИ, первые входы которых поразрядно объединены и соединены с выходами параллельного регистра 6. Выходы регистра 6 образуют первую группу 16 выходов генератора, выходы второй группы 9 элементов И образуют вторую группу 17 выходов устройства, а выходы группы 10 элементов ИЛИ - третью группу 18 выходов генератора.

Устройство работает следующим образом.

Перед началом работы генератора задаются начальные условия. Режим задания начальных условий состоит в записи в каждую из адресуемых ячеек блока 4 оперативной памяти требуемых данных, являющихся начальными условиями для генерации псевдослучайных сигналов. Записываемые данные формируются на первой группе информационных входов мультиплексора 2 (В1-Bm) при нулевом уровне сигнала на входе А переключения канала. На входе 13 синхронизации устройства при этом присутствует нулевой уровень сигнала, обеспечивающий режим записи блока 4 оперативной памяти при смене адреса. Модификация адресов осуществляется путем изменения сигналов на входах (D1-Dn) задания начального кода счетчика 3, сопровождаемая единичным импульсом на входе С записи начального кода счетчика 3. По окончании задания начальных условий в каждой адресуемой ячейке блока 4 оперативной памяти размещены данные, являющиеся начальными условиями для рабочих режимов генерации псевдослучайных сигналов. Варьирование начальных условий обеспечивает первичную управляемость генератора псевдослучайных сигналов.

Далее возможны два режима работы устройства: при фиксированном значении состояния двоичного счетчика 3 и при изменяющемся.

Режим 1. При фиксированном состоянии двоичного счетчика 3 обеспечивается генерация одномерных псевдослучайных сигналов, порождаемых одним единственным характеристическим полиномом. Состояние двоичного счетчика остается фиксированным за счет нулевого уровня сигнала Х на входе задания режима работы. Прохождение импульсов синхронизации на суммирующий вход счетчика 3 в этом случае заблокировано. Фиксированным состоянием выходов счетчика 3 обеспечивается адресация к одноименным ячейкам блоков 4 и 5 оперативной и постоянной памяти соответственно. В адресуемых многоразрядных ячейках блока 5 постоянной памяти записаны коэффициенты различных порождающих характеристических полиномов, представляющие собой маску, определяющую количество логических обратных связей сумматора 11 по модулю два и воздействующую на него через первую группу 8 элементов И. Каждая адресуемая многоразрядная ячейка блока 4 оперативной памяти представляет собой эквивалентный сдвиговый регистр, что обеспечивается соответствующим соединением выходов сумматора 11 по модулю два и выходов регистра 6 через мультиплексор 2. По переднему фронту синхроимпульса CLK на входе 13 синхронизации данные с выходов блока 4 оперативной памяти переписываются в регистр 6, далее они поразрядно маскируются содержимым блока 5 постоянной памяти, суммируются и при нулевом уровне синхроимпульса CLK переписываются в адресованную ячейку блока 4 оперативной памяти со сдвигом на 1 разряд. При этом в первый разряд записывается результат суммирования, во второй переписывается содержимое первого разряда, в третий - второго разряда и т.д., чем обеспечивается сдвиг информации. На выходах первой группы 16 генератора формируются базовые псевдослучайные сигналы, порождаемые одним характеристическим полиномом. Названные сигналы имеют равномерное распределение с нерегулируемой вероятностью событий Р=0,5. Управление вероятностью событий осуществляется на уровне основного сигнала синхронизации. Формирователь 7 импульсов с регулируемой длительностью формирует импульсы по переднему фронту сигнала CLK и изменяет длительность формируемого выходного импульса в функции сигнала управления на входе 15 в диапазоне от 0 до Т, где Т - период импульсов синхронизации CLK. Благодаря изменяющейся длительности импульсов на выходе формирователя 7, на выходах второй группы 9 элементов И за счет логического умножения вероятность событий Р варьируется в диапазоне 0-0,5; а вероятность событий на выходах группы 10 элементов ИЛИ за счет логического сложения одновременно варьируется в диапазоне 0,5-1. Работа генератора в режиме 1 продолжается по мере формирования импульсов синхронизации CLK.

Режим 2. Работа счетчика 3 разблокирована уровнем логической единицы сигнала Х на первом входе элемента И 1. В этом случае с приходом каждого синхроимпульса CLK состояние счетчика 3 изменяется в сторону увеличения от заданного значения до момента естественного переполнения, а затем, начиная с нулевого значения, изменяется аналогичным образом, пока на входе 13 синхронизации формируются импульсы CLK. Изменяющееся состояние счетчика 3 изменяет адреса блоков 4 и 5 оперативной и постоянной памяти соответственно. Остальные элементы схемы работают аналогично режиму 1. При этом в каждом такте формирования выходных сигналов оказываются задействованными разные характеристические порождающие полиномы. Промежуточные состояния псевдослучайных сигналов, порождаемых разными полиномами, сохраняются в соответствующих адресуемых ячейках блока 4 оперативной памяти. На выходах 16 генератора в этом случае формируются полипсевдослучайные сигналы, порожденные разными характеристическими полиномами с базовой вероятностью событий Р=0,5. Варьирование вероятности событий на выходах 16 и 17 осуществляется аналогично режиму 1.

Работоспособность предложенного устройства проверена на компьютерной модели с помощью виртуального логического анализатора

Сверху вниз на фиг.2 показаны импульсы синхронизации CLK, импульсы с регулируемой длительностью на выходе формирователя 7 импульсов, импульсы порождающей псевдослучайной последовательности и импульсы на соответствующих ей выходах групп 17 и 18 с регулируемой вероятностью.

Длительность импульсов на выходе формирователя импульсов в приведенном примере составляет четверть периода частоты синхронизации. Вероятность событий на выходах групп 17 и 18 оцениваются величинами Р=0,25 и Р=0,75 соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Генератор псевдослучайных сигналов | 1987 |

|

SU1437974A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| Генератор псевдослучайной последовательности | 1987 |

|

SU1528770A1 |

| Устройство для формирования тестов | 1988 |

|

SU1573457A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| Генератор псевдослучайных чисел | 1989 |

|

SU1691839A2 |

Изобретение относится к импульсной технике и может использоваться в вычислительной технике при моделировании случайных процессов, тестировании каналов связи и аппаратуры. Достигаемый технический результат - расширение функциональных возможностей генератора за счет управления вероятностью событий на выходных шинах устройства. Устройство содержит мультиплексор, двоичный счетчик, блоки оперативной и постоянной памяти, элемент И, параллельный регистр, первую и вторую группы элементов И, группу элементов ИЛИ, сумматор по модулю два и формирователь импульсов с регулируемой длительностью. 2 ил.

Генератор псевдослучайных сигналов, содержащий блоки оперативной памяти и постоянной памяти, адресные входы которых поразрядно объединены и подключены к выходам двоичного счетчика, суммирующий вход которого подключен к выходу элемента И, первый вход которого является входом задания режима работы генератора, а второй является входом синхронизации устройства, подключенным к входу записи/чтения блока оперативной памяти и входу синхронизации параллельного регистра, входы которого соединены с выходами данных блока оперативной памяти, входы данных которого подключены к выходам мультиплексора, первая группа информационных входов мультиплексора является шиной задания начальных условий устройства, а вход переключения канала передачи - входом перевода генератора из режима задания начальных условий в режим генерации псевдослучайных сигналов, первый информационный вход второй группы информационных входов мультиплексора соединен с выходом сумматора по модулю два, второй информационный вход подключен к первому выходу параллельного регистра, каждый j-й информационный вход соединен соответственно с j-1-м выходом параллельного регистра, каждый выход которого дополнительно подключен к первым входам первой группы элементов И, вторые входы которых соединены с выходами блока постоянной памяти, а выходы подсоединены к входам сумматора по модулю два, выходы регистра при этом образуют первую группу выходов устройства, входы задания и записи начальных условий двоичного счетчика являются входами задания базового адреса блоков оперативной и постоянной памяти, отличающийся тем, что в него включена вторая группа элементов И, группа элементов ИЛИ и формирователь импульсов с регулируемой длительностью, первый вход которого соединен с входом синхронизации устройства, второй является входом задания длительности формируемого импульса, а выход подключен к вторым объединенным входам второй группы элементов И и группы элементов ИЛИ, первые входы которых поразрядно объединены и соединены с выходами параллельного регистра, выходы второй группы элементов И образуют вторую группу выходов устройства, а выходы группы элементов ИЛИ - третью группу выходов устройства.

| Генератор псевдослучайных сигналов | 1987 |

|

SU1437974A1 |

| Управляемый генератор случайных импульсов | 1990 |

|

SU1818685A1 |

| JP 5327427 A, 10.12.1993. | |||

Авторы

Даты

2011-04-10—Публикация

2009-08-24—Подача