тригтера, единичный выход которого подключен к второму входу элемента И, выход переноса третьего счетчика группы подключен к счетному входу четвертого счетчика группы и к входу установки 1 триггера, други входы сумматора подключены к разрядным выходам четвертого счетчика группы, выходы дополнительного сумматора и элемента И являются другими выходами блока.

3. Устройство по п.1, отличающееся , что синхронизатор содержит первый и второй элементы НЕ, первый и второй элементы задержки, группу элементов И,

5940

причем вход второго элемента задержки является одним из входов и выходов синхронизатора, выход второго элемента задержки подключен к первым входам элементов И группы, вторые входы которых соединены соответственно с выходами первого и второго элементов НЕ и с входом первого элемента НЕ, третий вход одного из элементов И группы соединен с входом второго элемента НЕ, а выход с входом первого элемента задержки, входы элементов НЕ являются другими входами синхронизатора, другими выходами которого являются выходы элементов И группы и первого элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1280457A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1647579A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

1. БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее информационный накопитель, управляющие входы и выход которого подключены соответственно к первомуи второму выходам и входу блока управления, информационные входы - к выходам входного регистра числа, инфо1391ационные выходы - к входам выходного регистра числа, адресные входы - к выходам коммутатора адреса, первый адреснЬш вход которого подключен к выходу счетчика адреса, управляющие входы коммутатора адреса соединены с третьим и четвертым выходами блока управления, вход счетчика адреса подключен к пятому выходу блока управления и к первому входу счетчика числа ячеек памяти, второй вход которого подклюiчен к шестому выходу блока управле:ння, а выход - к входу блока анали.за информации, выход которого явля:ется одним из выходов устройства, :отличающееся тем, что, с целью расширения области применения устройства путем реализации возмож,ности геометрической нормализации записываемой видеоинформации, в него введены накопитель коэффициентов преобразования, сумматор, синхронизатор и блок формирования номера фрагмента изображения, первый выход которого подключен к первому входу накопителя коэффициентов преобразования, второй и третий вьпсоды соединены соответственно с первым и вторым входами синхронизатора, а вход подключен к одному из выходов синхронизатора, третий вход которого соединен с. шестым выходом блока управления, другие выходы синхронизатора соединены соответственно с одними из входов сумматора и вторым входом накопителя коэффициентов преобразования, выход которого соединён с другим входом сумматора первьй выход (Л которого подключен к второму адресному ВХОДУ коммутатора адреса,, а второй выход соединен - с третьим входом накопителя коэффициентов пре§ образования, четвертый вход кото,рого является одним из входов устройства. о сд 2. Устройство по п. 1, отличающееся тем, что блок форсо мирования номера фрагмента изображения содержит группу счетчиков, дополо нительный сумматор, триггер, элемент И, причем счетный вход первого счетчика группы является входом блока, выход переноса подключен к счетному входу второго счетчика группы, к первому входу элемента И и является . одним из выходов блока, разрядные выходы второго счетчика группы подключены к одним из входов дополнительного сумматора, выход переноса к счетному входу третьего счетчика группы и к входу установки О

Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств систем обработки видеоинформации.

Известно буферное запоминающее устройство, содержащее блоки памяти, в которые заносятся коды элементов изображения, и соединенные с блоками памяти счетчики адресов записи-считывания. При построчной развертке элементов изображения запись их в блоки памяти и считывание в устройства регистрации пр изводятся по последовательным адресам - в порядке поступления элементов 1 .

Однако функциональные возможности этого устройства ограничены вследствие невозможности реализации геометрической нормализации видеоинформации, в результате проведения которойпоследовательный характер ввода либо вывода элементов изображения может нарушаться.

Наиболее близким к изобретению является буферное запоминающее устройство, содержащее накопитель, входы которого подключены к одному Из выходов блока управления, выходу входного регистра числа и выходу элемента И-ИЛИ, выход накопителя подключен к входу выходного регистра числа, входы элемента И-ИЛР1 подключены к вьгходам счетчиков адреса записи и чтения, входы которых подключены к соответствующим выходам блока управления и входам счетчика объема накопителя, сумматор, схему сравнения и блок анализа состояния накопителя, причем входы сумматора подключены к выходам счетчика адреса чтения и счетчика объема накопителя, а выход - к схеме сравнения, второй вход которой соединен со счетчиком адреса записи, первый вход блока анализа состояния накопителя подключен к блоку управления, а второй, третий и четвертый являются выходами схемы сравнения 2.

Недостатком данного устройства является невозможность геометрической нормализации видеоинформации в нем, что сужает область применения устройства.

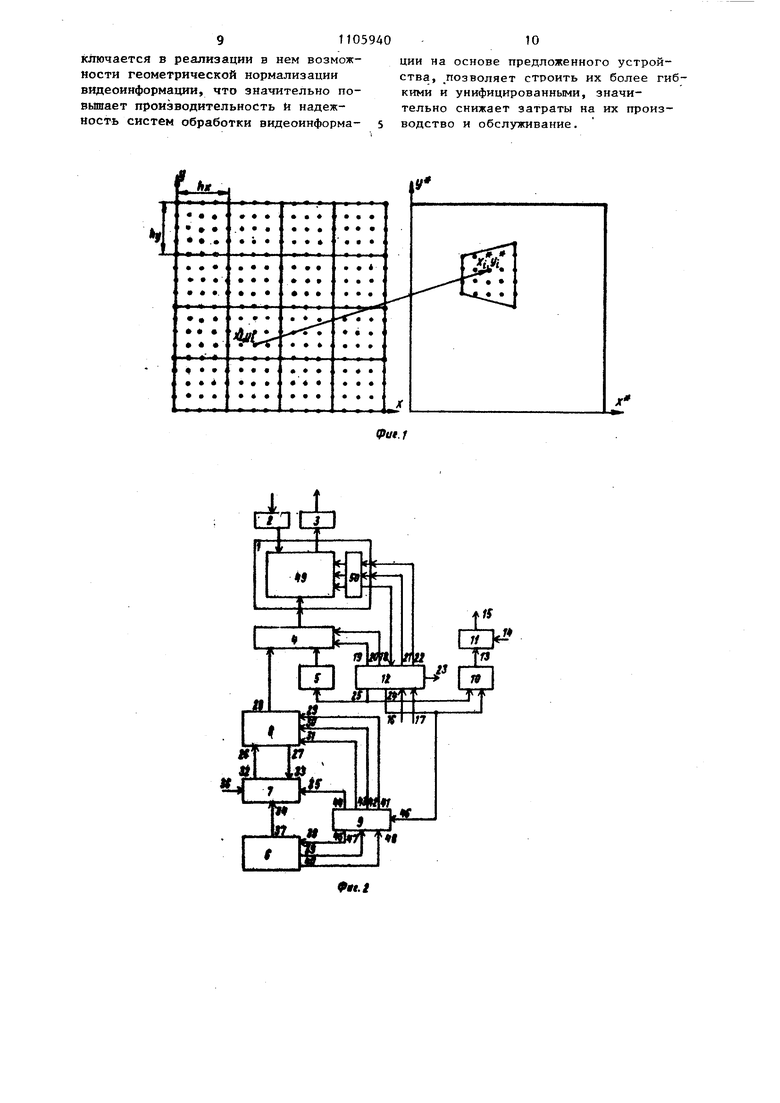

Геометрическая нормализация видеоинформации состоит в преобразовании координат элементов входного изображения согласно преобразованиям

-f(j(,}

(1)

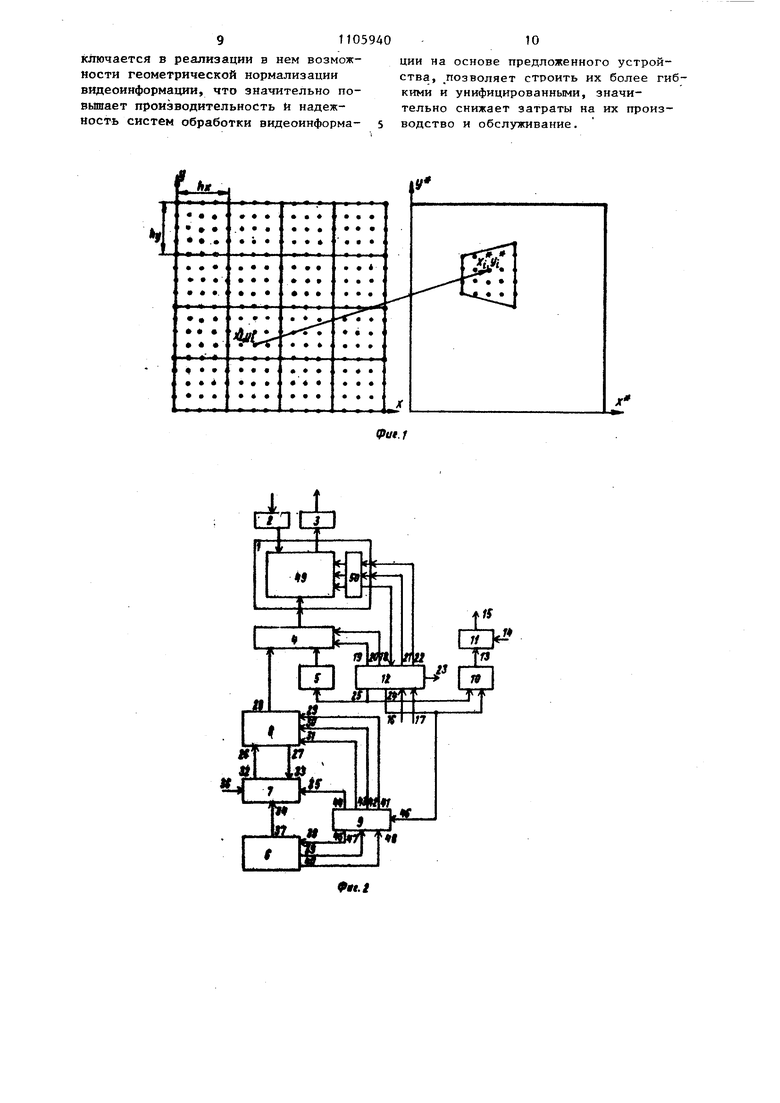

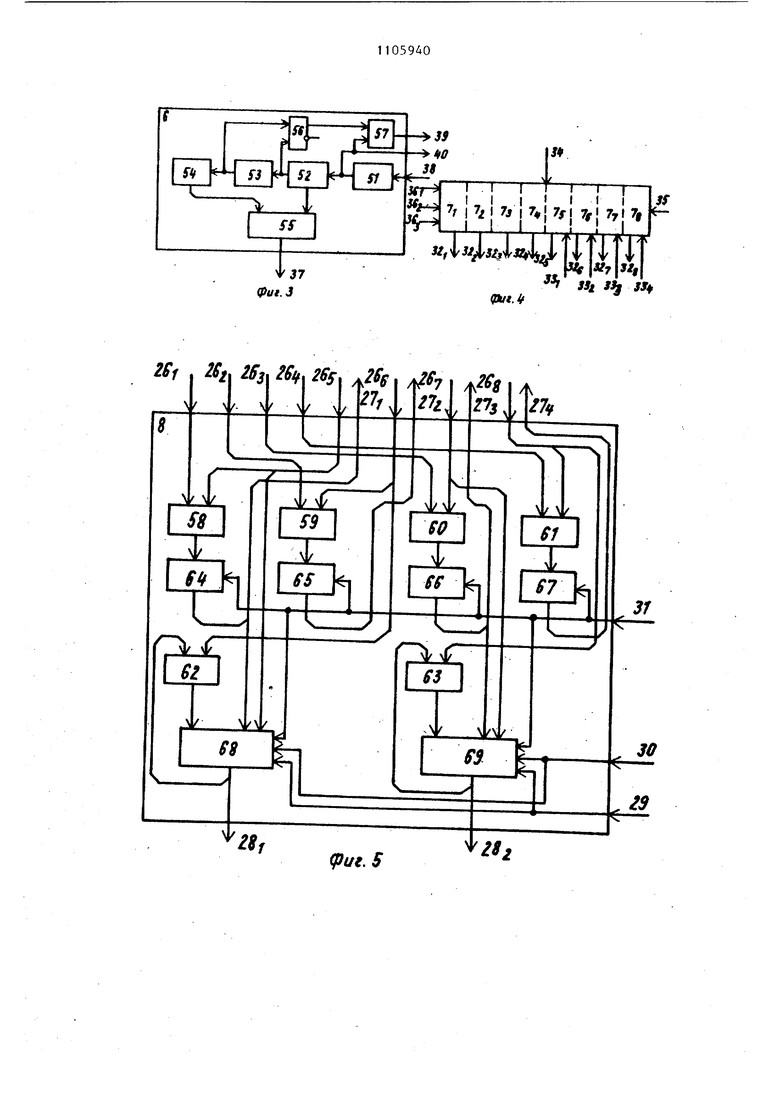

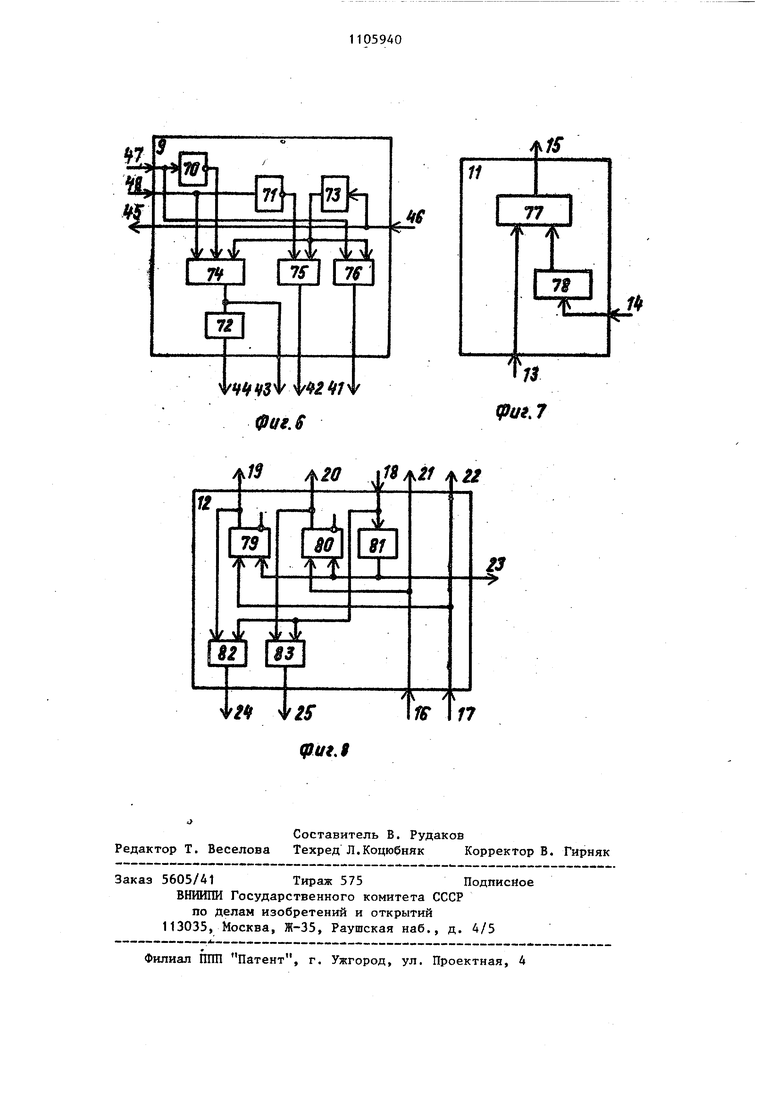

X , У - преобразованные координаты отдельного элемента выходного изображения, X , V - координаты элемента во входном изображении. 3 Элемент изображения характеризуется соответствующим кодом оптической плостности. Цель изобретения - расширение о ласти применения устройства путем реализации возможности геометрической нормализации записываемой видео информации. Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее информационный накопитель, управляющие входы выход которого подключены соответс венно к первому и второму выходам и входу блока управления, информационные входы - к выходам входного регистра числа, информационные выходы - к входам выходного регистра числа, адресные входы - к выходам коммутатора адреса, первый адресный вход которого подключен к выходу счетчика адреса, управляющие входы коммутатора адреса соединены с третьим и четвертым выходами блока управления, вход счетчика адреса по ключен к пятому выходу блока управления и к Первому входу счетчика числа ячеек памяти, второй вход которого подключен к шестому выходу блока управления, а выход - к входу блока анализа информации, выход которого является одним из выходов устройства, введены накопитель коэф фициентов преобразования, сумматор синхронизатор и блок формирования номера фрагмента изображения, первы выход которого подключен к первому входу накопителя коэффициентов прео разования, второй и третий выходы соединены соотвегственно с первым и вторым входами синхронизатора, а вход подключен к одному из выходов синхронизатора, третий вход которо соединен с шестым выходом блока управления, другие выходы синхронизатора соединены соответственно с одними из входов сумматора и вторым входом накопителя коэффициентов преобразования, выход которого соединен с другим входом сумматора, первый выход которого подключен к второму адресному входу коммутатора адреса, а второй выход соединен с третьим входом накопителя коэффици тов преобразования, четвертый вход которого является одним из входов устройства. Блок формирования номера фрагмента изображения содержит группу 404 счетчиков, дополнительный сумматор, триггер, элемент И, причем счетный вход первого счетчика группы является входом блока, выход переноса подключен к счетному входу второго счетчика группы, к первому входу элемента И и является одним из выходов блока, разрядные выходы второго счетчика группы подключены к одним из входов дополнительного сумматора, выход переноса - к счетному входу третьего счетчика группы и к входу установки О триггера, единичный выход которого подключён к второму входу элемента И, выход переноса третьего счетчика группы подключей к счетному входу четвертого счетчика группы и к входу установки 1 триггера, другие входы сумматора подключены к разрядньм выходам четвертого счетчика группы, выходы дополнительного сумматора и элемента И являются другими выходами блока. Синхронизатор содержит первый и второй элементы НЕ, первый и второй элементы задержки, группу элементов И, причем вход второго элементя задержки является одним из входов и выходов синхронизатора, выход второго элемента задержки подключен к первым входам элементов И группы, вторые входы которых соединены соот- ветственно с выходами первого и второго элементов НЕ и с входом первого элемента НЕ, третий вход одного из элементов И группы соединен с входом второго элемента НЕ, а выход - с входом первого элемента задержки, входы элементов НЕ являются другими входами синхронизатора, другими выходами которого являются выходы элементов И группы и первого элемента задержки. На фиг. 1 показан пример геометрической нормализации элемента изображения на фиг. 2 - структурная схема буферного запоминающего устройства, на фиг.3-8 структурные схемы блока формирования номера фрагмента изображения, накопителя коэффициентов преобразования, сумматора, синхронизатора, блока анализа информации и блока управления соответственно. Необходимость преобразования координат элементов входного изображения возникает при компенсации геометрических искажений снимков, их фотограмметрического трансформирования или преобразования в одну, из картограф1гческих проекций. На фиг. 1, где показан номер геометрической нормал зации i-го элемента входного изобм 1 S ражения с координатами х соответствукнцйй ему элемент выходного изображения с координатами х, , элементы изображений условно обозначены точками. При построчной развертке изображения элементы входного изображения (коды оптической плотности) по тупают на обрабсэтку последовательно При этом порядковый нойер элемента однозначно определяют его координат X , во входном изображении. Пуст начало отсчета совмещено с первым элементом какой-либо строки входног изображения, тогда .. 1гпос m ; m - число элементов в строке изображения; t 1 операция вьщеления целой части числа. Последовательный характер поступ ления элементов входного изображения и выдачи их на регистрирующие устройств позволяет операции преобразования координат эффективно пр изводить с использованием буферной памяти. Геометрическая нормализация может производиться по методу прямого либо обратного преобразования. jB случае использования метода преобразования ячейки памяти н копителя, в которые заносятся коды оптической плотности, соответствуют элементам выходного изображения. этом адрес каждой -и ячейки памяти может быть представлен в виде двух составляющих: у - старшие раз ряды, младшие разряды, соответст вующих координатам данного элемента в выходном изображении. Геометрическая нормализация по методу прямого преобразования производится при записи элементов входного изображения в накопитель. Составляющие адреса записи х .V калдого элемента вход ного изображения определяются по выражению (1) подстановкой координат X , данного элемента во входном изображении, для чего могут использоваться специализированные аппаратные средства. В процессе обработки по методу прямого преобразования, реализованному в предлагаемом устройстве, в информационном накопителе формируется выходное преобразованное изображение, выдача элементов которого может производиться считыванием из последовательно расположенных ячеек памяти. В случае использования метода обратного преобразования ячейки памяти накопителя соответствуют элементам входного изображения. Можно показать, что методы прямого и обратного преобразования эквивалентны с точки зрения их аппаратной реализации. Буферное запоминающее устройство (фиг, 2) содержит информационный накопитель 1, входной регистр 2 числа, выходной регистр 3 числа, коммутатор 4 адреса, счетчик 5 адреса, блок 6 формирования номера фрагмента изображения, накопитель 7 коэффициентов преобразования, сумматор 8, синхронизатор 9, счетчик 10 числа ячеек памяти, блок 11 анализа информации, блок 12 управления. Блок 11 анализа информации имеет входы 13 и 14, выход 15. Блок 12 управления имеет входы 16 - 18 и выходы 19-25. Сумматор 8 имеет вход 26, выходы 27 и 28, входы 29 - 31. Накопитель 7 имеет выход 32, входы 33 - 36. Блок 6 формирования номера фрагмента изображения имеет выход 37, вход 38, выходы 39 и 40. Синхронизатор 9 имеет выходы 41 - 45, входы 46 - 48. Накопитель 1 содержит матрицу 49 памяти и блок 50 формирования временной диаграммы.. Блок 6 формирования номера фрагмента изображения (фиг. 3) содержит группу счетчиков 51-54, дополнительный сумматор 55, триггер 56, элемент И 57. Накопитель 7 коэффициентов преобразования (фиг. 4) содержит восемь дополнительных накопителей 7у, - 7g. Сумматор 8 (фиг. 5) содержит блоки 58 - 63 суммирования, регистры 64 - 69. Синхронизатор 9 содержит (см. фиг. 6) первый 70 и второй 71 элементы НЕ, первый 72 и второй 73 элементы задержки, группу элементов И 74 - 76. Блок 11 анализа информации содержит (фиг. 7) блок 77 сравнения и регистр 78, Блок 12 управления содержит (фиг, 8) триггеры 79 и 80, элемент 81 задержки,элементы И 82 и ЯЗ.: 711 Рассмотрим работу буферного запоминающего устройства, реализующего метод прямого преобразования. При поступлении на обработку очередного элемента входного и.зображения в регистр 2 заносится код его оптической плотности, а на вход 17 блока 12 управления вьщается сигнал запроса записи. В блоке 12 управления данный сигнал производит установ ку в единичное состояние триггера 79 и через выход 22 поступает на вхо накопителя 1, запуская блок формирования 50 временной диаграммы. Единичньй сигнал с выхода 19 блока 12 поступает на вход коммутатора 4 адре са, разрешая прохождение кода адреса записи с выхода 28 сумматора 8 на адресные входы накопителя 1. Составляющие кода адреса записи, соответствуклцие координатам данного элемента в выходном изображении, вычисляются с помощью блоков 6 - 9 согласно закойу прямого преобразования координат. По окончании операции записи с выхода накопителя 1 на вход 18 блока 12 поступает сигнал окончания цикла обращения, который через выход 24 блока 12 -поступает на вход 46 синхронизатора 9, разрешая формирование блоками 6-9 адреса записи следующего элемента входного изображения, и «а вход счетчика 10, увеличивая его содержимое на единицу. Про ходя через элемент 81 задержки, с выхода 23 блока 12 сигнал окончания цикла обращения Испо/Лзуется для разрешения формирования следующего запроса к уСгройству и сбрасывает в нулевое состояние триггер 79. В процессе з;аписи элементов входного изображения в накопителе 1 формируется выходное изображение. Вьщача элементов выходного изображения производится из последовательно расположенных ячеек накопителя 1 при заполнении его до определенного объема гарантирующего полноту формирования вьщаваемой части выходного изображения . Сигнал разрешения вьщачи элементов выходного изображения формиру}ется на выходе 15 блока 11. Код обье ма заполнения накопителя 1 с выходов счетчика 10 через вход 13 блока 11 поступает на первые входы блока 77 сравнения, на вторые входы которого с выходов регистра 78 поступает запи санный в него перед началом работы код требуемого объема заполнения. При превьшении кода текущего объема заполнения накопителя заданного кода объема на выходе блока 77 формируется сигнал разрешения вьщачи элементов выходного изображения. При наличии этого сигнала на вход 16 блока 12 управления поступает сигнал запро са считьшания. В блоке 12 управления данный сигнал производит установку в единичное состояние триггера 80 и через выход 21.блока 12 поступает на вход накопителя 1, запуская блок 50. Единичный сигнал с выхода 20 блока 12 поступает на вход коммутатора 4, разрешая прохождение кода адреса считывания с выходов счетчика 5 на входы накопителя 1. По окончании операции считывания с выхода накопителя 1 на вход 18 блока 12 поступает сигнал окончания цикла обращения, который через выход 25 блока 12 поступает на вход счетчика 5, на выходах которого формируется адрес считьшания следующего элемента выходного изображения, и на вход счетчика 10, уменьшая его содержимое на единицу. Проходя через элемент 81 задержки, сигнал окончания цикла обращения сбрасывает в нулевое состояние триггер 80. Считанный код оптической плотности элемента выходного изображения заносится в регистр 3 и далее выдается из устройства. В устройстве, реализующем геометрическую нормализацию по методу обратного преобразования,блоки 6-9 служат для формирования адреса считывания элемента выходного изображения, а счетчик 5 - счетчика адреса записи. В соответствии с этим выход 24 блока 12 управления является выходом сигнала модификации адреса считывания, выход 25 - выходом сигнала модификации адреса записи, вход 16 - входом сигнала запроса записи, вход 17 - входом сигнала запроса считывания, выход 21 - выходом сигнала управления записью в накопителе 1, выход 22 - выходом сигнала управления считьтанием. При этом работа всего устройства и его отдельных блоков происходит аналогично, как и при реализации метода прямого преобразования. Технико-экономическое преимущество предлагаемого устройства заключается в реализации в нем возможности геометрической нормализации видеоинформации, что значительно повышает производительность и надежность систем обработки видеоинформа- s

цин на основе предложенного устройства, .позволяет СТРОИТЬ их более гибкими и унифицированными, значительно снижает затраты на их производство и обслуживание.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство | 1979 |

|

SU824305A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Буферное запоминающее устройство | 1979 |

|

SU822293A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-07-30—Публикация

1982-12-24—Подача