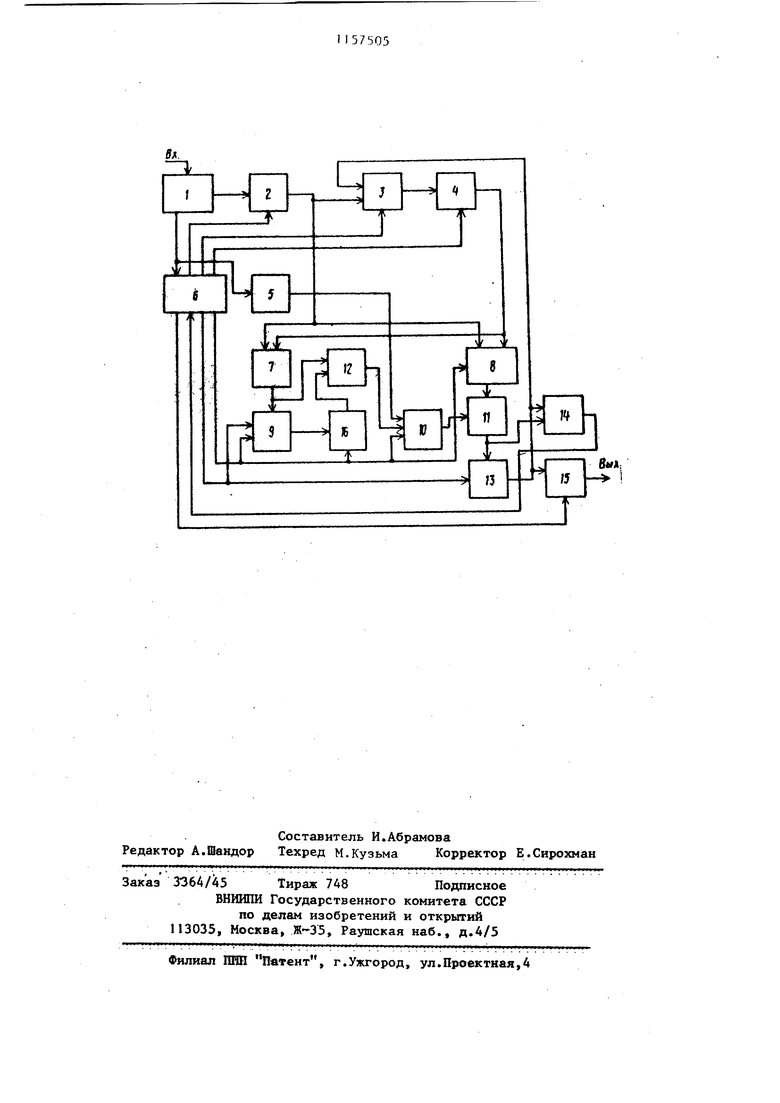

Изобретение относится к иэмери тельным устройствам для геоэлектроразведки и может применяться при. измерениях зашумленных, многократно повторяемых сигналов в методе вызва ной поляризации (ВП) и методе переходных процессов (МГШ). По основному авт.св. № 1073728 известно устройство для нелинейной обработки электроразведочных сигналов, содержащее входной блок, первый и второй регистры схему сравне ния, арифметическое устройство, запоминающее устройство, устройство управления и два коммутатора, приче информационный выход входного блока соединен с входом запоминающего устройства, а служебный выход вход ного блока соединен с входом устрой ства управления, выход запоминающег устройства соединен с первым входом арифметического устройства и через первый коммутатор - с входом первог регистра, выход первого регистра подключен к входу арифметического устройства, выход которого соединен с входом второго регистра и первым входом схемы сравнения, выход второ регистра соединен с вторым входом схемы сравнения и через первый ком- мутатор - с входом первого регистра также выход второго регистра через второй коммутатор соединен с выходом всего устройства, выход схемы сравнения соединен с вторым входом устрой ства управления, выходы устройства управления соединены с управляющими входами первого и второго регистров запоминающего устройства, арифметического устройства и коммутаторов Недостатком этого устройства явг ляется сравнительно низкая скорость сходимости оценок целевых параметров к истинному значению в условиях действия характерных в геоэлектрораз ведке помех, представляющих смесь небольших флуктуационных и редких (аномальных ) импульсных помех большой амплитуды. Недостаток устройства обусловлен тем, что при исключении наиболее удаленных от оценки отсчетов при воздействии лишь неболь ших помех могут быть исключены подряд на нескольких периодах сигнала отсчеты, имеющие одинаковые знаки разности с текущими оценками измеряемых величин, что иногда приводит к смещению оценок. Цель изобретения - повьшление точности оценки измеряемых параметров. Поставленная.цель достигается тем, что в устройство для нелинейной обработки электроразведочньк сигналов, введены регистр знака, буферный регистр, блок деления, счетчик, вторая схема сравнения, схема совпадения знаков и злемент И, причем первый и второй входы второй схемы сравнения подключены к информационным входам арифметического устройства, выход второй схемы сравнения соединен с входом схемы совпадения знаков и входом регистра знака, выход которого подключен к входу буферного регистра, а выход буферного регистра соединен с вторым входом схемы совпадения знаков, управляющий вход буферного регистра подключен к управляющему входу арифметического устройства, первый и второй управляющие входы регистра знака соединены соответственно с управляющими входами арифметического устройства и второго регистра, вход счетчика подключен к служебному выходу входного блока, три входа элемента И соединены соответственно с вьжодом счетчика, выходом схемы совпадения знаков и управляющим входом арифметического устройства, а выход элемента И подключен к управляющему входу блока деления, информационный вход которого соединен с выходом арифметического устройства, а выход - с входами второго регистра и первой схемы сравнения. На чертеже предсгавлена структурная схема устройства. Устройство для нелинейной обработки электроразведочных сигналов содержит входной блок I, запоминающее устройство 2, первый коммутатор 3, первый регистр 4, счетчик 5, устройство 6 управления, вторую схему 7 сравнения, арифметическое устройство 8, регистр 9 знака, элемент И О, блок I деления, схему 12 совпадения знаков, второй рв- гистр 13, первую схему 1А сравнения, второй коммутатор 15 и буферный регистр 16. Информационный выход входного блока 1 соединен с входом запоминающего устройства 2. Служебный выход входного блока 1 соединен с входом устройства 6 управления. Выход запоминающего устройства 2

соединен с первыми входами второй схемы 7 сравнения и арифметического устройства 8, а также через первый коммутатор 3 - с входом первого регистра 4. Выход первого регистра 4 подключен к вторым входам второй схемы 7 сравнения и арифметического устройства 8, Выход арифметического устройства-8 соединен с входом блока 11 деления, выход которого соединен с входом второго регистра 13 и первым входом первой схемы 14 сравне ния. Выход второго регистра 13 соеди иен с вторым входом первой схемы 14 сравнения и через первый коммута тор 3 - с входом первого регистра 4. Выход второго регистра 13 также через второй коммутатор 15 соединен с выходом всего устройства. Вход счетчика 5 соединен со служебным выходом входного блока 1, а его выход - с первым входом элемента И 1

Выход второй схемы 7 сравнения соеди йен с информационным входом регистра знака 9 и с первым входом схемы 12 совпадения знаков. Выход регистра знака 9 подключен к входу буферного регистра 16. Управляющий вход бу фарного регистра 16 соединен с управляющим входом арифметического устройства 8. Второй вход схемы 12 совпадения знаков соединен с выходом буферного регистра 16, а ее выход соединен с вторым входом элемента И 10. Третий вход элемента И 10 соединен с управляющим входом арифметического устройства 8. Первый и второй управляющие входы регистра знака 9 соединены с управляющими входами арифметического устройства 8 и второго регистра 13. Выходы устройства 6 управления соединены с управляющими входами первого 4 и второго 13 регистров, запоминающего устройства 2, арифметического устройства 8 и коммутаторов 3 и 15.

Блок 11 деления предназначен для выполнения операции деления на заданный коэффициент, а при отсутствии сигнала на его управляющем входе передает кодовую комбинацию с входа на выход без изменений.

Счетчик 5 предназначен для выделения периодов с номером больше N+1.

Регистр знака 9 служит для запоминания знака разности между отсчетами и может быть выполнен на основе ЗК-триггера.

Устройство работает следующим образом.

Входной блок 1 осуществляет дискретизацию и преобразование в код входного периодического сигнала и определение в течение одного периода сигнала одного или нескольких целевьпс параметров (одна или несколько точек на переходной характеристике, амплитудные или фазовые параметры }. Каждьй из целевых параметров обрабатывается одинаково, поэтому дальнейшее описание работы для упрощения производится для одного параметра.

По окончании преобразования на служебном выходе входного блока 1 формируется сигнал, по которому .устройство 6 управления формирует команду записи и адрес ячейки запоминающего устройства 2. После прохождения N периодов и записи в запоминающее устройство 2 отсчетов в устройстве осуществляется определение медианы ряда, составленного из сумм х + X , где ; и j могу принимать любые значения от I до N,

Дпя определения медианы устройство 6 управления после записи в запоминающее устройство 2N отсчетов формирует сигнал, разрешающий запись первого отсчета, хранящегося в запоминающем устройстве 2, в первый регистр 4. После этого устройство 6 управления начинает последовательный опрос всех N отсче

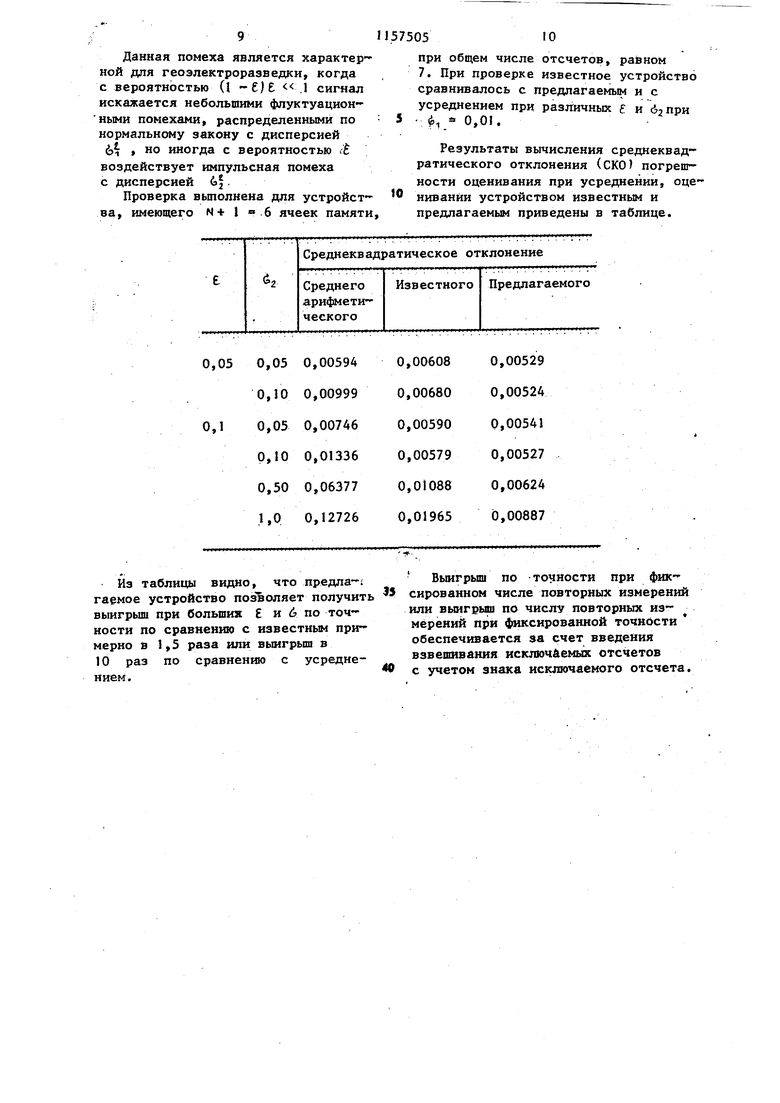

тов,хранящихся в запоминающем устройстве 2, в арифметическом устройстве 8 определяются суммы поступающих отсчетов и отсчета, хранящегося в первом регистре 4. Первая сумма х + Хг записывается через делитель без изменений во второй регистр 13, и с выхода второго регистра 13 поступает на второй вход первой схемы 14 сравнения. Вторая сумма Х+ х поступает на nepBbdt вход первой схемы 14 сравнения, и в том случае, если вторая сумма больше первой, по сигналу с выхода первой схемы 14 сравнения устройство 6 управления разрешает запись во второй регистр 13 новой суммы. Если же вторая сумма меньше первой, то во втором регистре 13 остается первая сумма до тех пор, пока на первый вход первой схемы 14 сравнения не придет сумма, большая по величин чем записанная во втором регистре 13, После перебора всех N отсчетов, хранящихся в запоминающем устройств 2, во втором регистре 13 оказываетс наибольшая из сумм, образующихся с первым отсчетом, т.е. max х + + X. , а в первый регистр 4 записьш ется второй отсчет и повторяется операция перебора. После завершения N+ 1 переборов будет найден наибольший член вариационного ряда. Код адреса слагаемых запоминается в устройстве управления 6 и при опр делении предыдущих членов вариацион ного ряда сумма, образованная этими слагаемыми, не вычисляется. Предьщу щие члены вариационного ряда опреде ляйтся аналогично.. После определени (N+ 1 )+ 2 членов ряда дальнейшее определение прекращается, и в устрой стве 6 управления вырабатьшается сигнал, отпирающий второй коммутатор 15, и содержимое второго регистра 13 (т.е. средний член вариационного ряда I поступает на выход устройства (результат можно разделить на 2 исключением младшего разряда ), Оценка значения измеряемого параметра 0 оп ределяется в промежутке между приходом N-ro и Н отсчетов. После того, как оценка Э по N от счетам определена, сформирован и записан в запоминающее устройство 2N + .l-й отсчет, производится операция по определению и исключению из запоминающего устройства 2 отсчета, наиболее отличающегося от оценки 9-,. Для этого в первый регистр 4 по команде с выхода устройства управления 6 через первый коммутатор 3 записывается с выхода второго реди- стра 13 содержащаяся там оценка 0,. Одновременно с выхода устройства 6 управления поступает сигнал на изменение операции, выполняемой арифметическим устройством 8. После прихода этого сигнала арифметическое устройство 8 выполняет операцию кода I § - X; I , т.е. находит модуль разности между поступающими на его входы отсчетами. Этот же сигнал поступает на первый управляющий вход регистра 9 знака и разрешает запись в регистр 9 знака при поступлении сигнала на его второй « управляющий вход. Устройство 6 управления производит последовательный опрос хранящихся в запоминающем устройстве 2 N + 1 отсчетов. Модуль разности 0 , полученный на выходе арифметического устройства 8, передается блоком 11 деления без изменений и записывается во второй регистр 13. Одновременно знак разности д х, полученный на выходе второй схемы 7 сравнения, записьшается в регистр знака 9. 1 л. Модуль разности , хранящийся во втором регистре 13, сравнивается с модулем разности между оцен- кой §, и вторым отсчетом X2. Если I 0., - Xj I больше разности 8 - , первая схема 14 сравнения вырабатывает сигнал, разрешающий запись во второй регистр 13 значения 1 21 а также в регистр 9 знака знака разности 6, - Хд , Если модуль разности I б - Х2 I меньше ,| ё., - х | , то во втором регистре 13 остается первый модуль разности, а в регистре знака - прежний знак разности до тех пор, пока с выхода арифметического устройства 8 не поступит число, превышающее |б - х . После перебора N4- 1 .отсчетов, хранящихся в запоминающем устройстве 2, во втором регистре 1 3 оказывается наи больший модуль разности, в регистре 9 знака - знак этой разности, а в устройстве управления 6 - код адреса отсчета, наиболее отклоняющегося от полученной по первым N отсчетам оценки 9 , Этот отсчет стирается из запоминающего устройства 2, т.е. в запоминающем устройстве 2 освобождаются ячейки для записи N + .2-го отсчета. Задним фронтом сигнала, переключающего режим работы арифметического устройства 8, производится запись знака разности, хранящегося в регистре 9 знака, в буферный регистр 16. Таким образом,в буферном регистре 16 хранится знак разности между исключенным отсчетом и оценкой , полученной на предыдущем периоде. По оставшимся отсчетам определяется вторая оценка S,т.е. для оставшихся N отсчетов повторяется операция определения медианы ряда, составленного из полусумм. После того,как вторая оценка б определена и в запоминающем устройтве 2 записан N+ 2 отсчет, произОДИТя операция исключения из за- поминающего устройства 2 отсчета, наиболее отличающегося от оценки е., при этом предпочтение отдается отсч там , имеющим знак разности с оценкой б , обратный по сравнению со знаком разности между исключенным на предьщущем периоде отсчетом и оценкой . Для этого в первый регистр 4 по команде с выхода устройства 6 управления через первый коммутатор 3 записьшается с выхода второго регистра 13 содержащаяся там оценка § . Одновременно с выхода устройства 6 управления приходит сигнал на изменение операции, выполняемой арифметическим устройством 8. После получения входным блоком IN 2-й оценки, на выходе счетчика 5 устанавливается сигнал, позволяющий сработать элементу И 10. Устройство 6 управления производит последовател ный опрос хранявшхся в запоминающем устройстве 21 + 1 отсчетов. Знак разности 02 -1 полученный на выходе второй схемы 7 сравнения, поступает на первый вход схемы 12 совпадения знаков, на второй ее вхо поступает знак разности, хранящийся в буферном регистре 16. Если эти знаки совпадают, сигнал с выхода схемы 12 совпадения знаков через элемент И 10 поступает на управляющий вход блока П деления. В этом случае блок I1 деления делит код, соответствующий модулю разности б х) , на заданный коэффициент К. Если же знаки на входе схемы 12 совпадения знаков не совпадают, блок Наделения передает модуль раз ности ( 02 - х, ) на свой выход без изменения. Кодовая комбинация, полу ченная на выходе блока 11 деления, захдасывается во второй регистр 13, а знак разности записьшаетс в регистр 9 знака. Затем определяет знак разности j - х. и сравнивается со знаком, хранящимся в буферном регистре 16. Если знак разности Sj - Xj и знак разности между 9 отсче том, исключенным на предыдущем перио де, совпадают, то модуль разности j 02 2 полученный на выходе арифметического устройства 8, делит ся блоком 11 деления на коэффихщент в противном случае модуль разности I п I ( 2 х, I передается на вход второго регистра 13 и вход первой схемы 14 сравнения без изменения. Если величина --- I § J -X 21 больше j j Х J vK, и К принимают значения либо 1, либо К в зависимости от результата сравнения знаков, соответстяенно, х и 2 1 с° знаком, храняЕ1ИМСЯ в буферном регистре 16), то первая схема 14 сравнения вырабатьша ет сигнал, разрещающий запись во 1 t второй регистр 13значения :г б, х I К 1 , л К„ 1 ; Z Если вел гчина гг- 9, меньше 1Л) 1 1 л I гг-- 9, - X , то во втором регистре KT I -i 1 I J 13 остается ;р I б - тех . 1 пор, пока с выхода блока деления. 11 не поступит число, превышающее 1 1 I г-- 0, - X. L После перебора N + 1 1 отсчета, хранящегося в запоминающем устройстве 2, во втором регистре 13 оказьшается наибольшая из величин 1 А I - 02 Xjl Я i равен заданномукоэффициенту К, если знак разности - Xilсовпадает со знаком разности между оценкой в., и отсчетом, исключенным на предыдущем периоде, в противном случае К 1. В регистре 9 знака хранится знак отсчета, образующего наибольшую из I I / I величин - I 9, - X . I, а в устройстве 6 управления - код адреса этого отсчета. Этот отсчет стирается из запоминающего устройства 2, а по оставщймся N отсчетам определяется следующая оценка 9j. Далее устройство работает аналогично описанному вьше. Устройство проверялось при работе с коэффициентами К, равными 1,5; 2; 3 и 4, наилучший результат бьт получен при К 2. Для проверки предлагаемого устрой ства на его вход при нулевом входном сигнале подавалась помеха, имеющая следующую плотность распреде ления: -- 2 -Iir vjiTr -TIT где t - вероятность появления импульсной помехи, имеющей дисперсию 6 ; 6 - дисперсия флуктуационной помехи, причем 6 «(. Данная помеха является характерной для геоэлектроразведки, когда с вероятностью (l -eiE «1 сигнал искажается небольшими флуктуационными помехами, распределенными по нормальному закону с дисперсией 6i но иногда с вероятностью ft воздействует импульсная помеха с дисперсией 6|. Проверка выполнена для устройства, имеющего N+ 1 .6 ячеек памяти 0510 при общем числе отсчетов, равном 7. При проверке известное устройство сравнивалось с предлагаемым и с усреднением при различных f и 6, при 0,0, Результаты вычисления среднеквадратического отклонения (СКО) погрешности оценивания при усреднении, оце нивании устройством известным и предлагаемым приведены в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для предварительной обработки электроразведочных сигналов | 1984 |

|

SU1203452A2 |

| Устройство для предварительной обработки электроразведочных сигналов | 1986 |

|

SU1539708A1 |

| Устройство сбора данных для цифрового анализатора сигналов | 1990 |

|

SU1751683A1 |

| Устройство для предварительной обработки электроразведочных сигналов | 1981 |

|

SU983620A1 |

| Устройство для нелинейной обработки электроразведочных сигналов | 1982 |

|

SU1073728A1 |

| Устройство преобразования сейсмической информации | 1979 |

|

SU930187A1 |

| Адаптивный коммутатор | 1976 |

|

SU618861A1 |

| Цифровой фазометр | 1982 |

|

SU1075187A1 |

| Устройство для деления | 1988 |

|

SU1621023A1 |

| Устройство для сжатия информации | 1983 |

|

SU1129638A1 |

УСТРОЙСТВО ДЛЯ НЕЛИНЕЙНОЙ ОБРАБОТКИ ЭЛЕКТРОРАЗВЕДОЧНЫХ СИГНАЛОВ по авт. св. № 1073728, отличающееся тем, что, с целью повышения точности оценки измеряемых параметров,в него введены регистр знака, буферный регистр, блок деления, счетчик, вторая схема сравнения, схема совпадения знаков и элемент И, причем первый и второй входы второй схемы сравнения подключены к информационным входам арифметического устройства, вькод второй схемы сравнения соединен с входом схемы совпадения знаков и входом регистра знака, выход которого подключен к входу буферного регистра, а выход буферного регистра соединен с вторым входом схемы совпадения знаков, управляющий вход буферного регистра подключен к управляющему входу арифметического устройства, первый и второй управляющие входы регистра знака соединены соответственно с управляющими входами арифметического устройства и второго (Л регистра, вход счетчика подключен к служебному выходу входного блока, три входа элемента И соединены соответственно с выходом счетчика, выходом схемы совпа;цения знаков и управляющим входом арифметического устройства, а выход элемента И подключен к управляющему входу блока ел Сл деления, информационный вход которого соединен с выходом арифметического устройства, а выход - с входами о ел второго регистра и первой схемы сравнения.

Из таблицы видно, что предла ; гаемое устройство позволяет получить выигрыш при больших и по точности по сравнению с известным примерно в 1,5 раза или выигрыш в 10 раз по сравнению с усреднением.

Выигрьш по -точности при фиксированном числе повторных измерений или выигрьш по числу повторных измерений при фиксированной точности обеспечивается за счет введения взвешивания исключаемых отсчетов с учетом знака исключаемого отсчета.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для нелинейной обработки электроразведочных сигналов | 1982 |

|

SU1073728A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-05-23—Публикация

1983-12-23—Подача