1

(21)4607850/24

(22)15009,88

(46) 15,01.91, Bran, № 2

(71)Казахский филиал Всесоюзного научно-исследовательского института разведочной геофизики Научно-производственного объединения Рудгеофизи- ка

(72)П„Ко Аполонов, ГоК„ Жиров и Г.Ио Маялвин

(53)681.325(088.8)

(56)Авторское свидетельство СССР № 615477, кл. G 06 F 7/52, 1977.

Оранский ЛоМ. Аппаратурные методы в ЦВТ„ Минск: БГУ, 1977, с. 62, 63, рис„ 3.4.

(54)УСТРОЙСТВО ДНЯ ДЕЛЕНИЯ

(57)Изобретение относится к вычислительной технике к может быть использовано при построении устройств деления двоичных чисел число-импульсным методом. Цель изобретения - повышение быстродействия устройства при требовании относительной точности деления, обратно пропорциональной числу делителя. Устройство для деления содержит генератор 1 тактовых импульсов, элемент И 2, триггер 3, счетчик 4 результата, делитель 5 частоты, двоичный умножитель 6, управляемый делитель 7 частоты, счетчик 8 делимого, сдвиговый регистр 9 делителя, блок 10 управления, вход 11 делимого устройства, вход 12 делителя устройства, вход 13 управления и установочный вход 14 устройства, соединенные между собой функционально. 1 з0п0 ф-лы, 2 ил о

о

31

Изобретение относится к вычислительной технике и может быть использовано при построении устройств деления двоичных чисел число-импульсным методом. „

Цепь изобретения - повышение быстродействия устройства при требовании относительной точности деления „ обратно пропорциональной числу делителя,

На фиг„ 1 представлена функциональная схема устройства для деления; на фиг„ 2 - то же, блока управления

Устройство для деления содержит генератор 1 тактовых импульсов, элемент И 29 триггер 3, счетчик 4 результата, делитель 5 частоты, двоичный умножитель 6, управляемый делитель 7 частоты, счетчик 8 делимого, сдвиговый регистр 9 делителя, блок 1 управления; вход 11 делимого устройства, вход 12 делителя устройства вход 13 управления и установочный вход 14, соединенные между собой функционально„

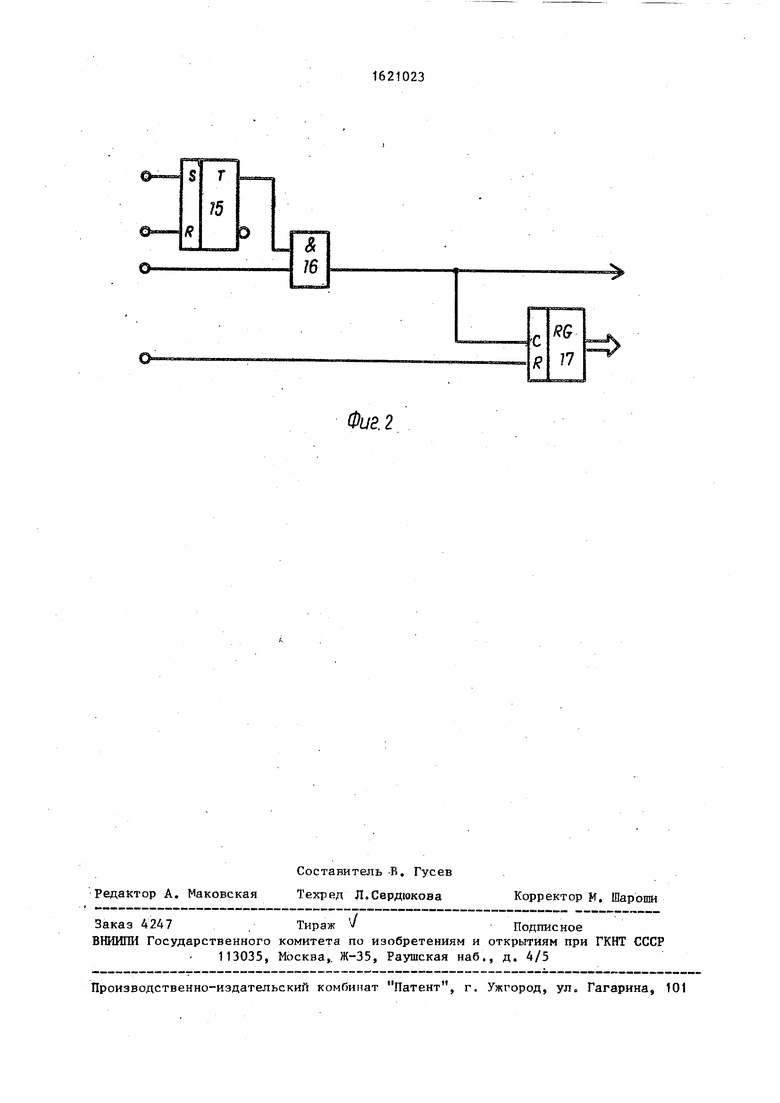

Блок управления (фиг„ 2) содержит триггер 15, элемент И 16 и регистр 170

Устройство работает следующим образом.

На вход 11 счетчика 8 делимого поступает код числа делимого в дополнительном коде, а на вход 12 парал- лельного приема информации сдвиговог регистра 9 делителя - код числа делителя в прямом коде. На установочньй вход 14 операндов деления подается импульс, при этом коды чисел делимог и делителя заносятся в счетчик 8 делимого и сдвиговый регистр Ч делителя соответственно, а блок 10 управления устанавливается в исходное состояние (в нулевое состояние устанавливается сдвиговый регистр 17 блока 10 управления)„ Для выполнения деления чисел на вход 13 управления подается импульс„ Блок 10 управления пропускает импульсы тактовой частоты с генератора 1 на вход синхронизации последовательного сдвига сдвигового регистра 9 делителя,, Код числа делителя в сдвиговом регистре 9 сдвигается в сторону старших разрядов, и при совпадении старшего разряда числа делителя ср старшим разрядом сдвигового регистра 9 сигнал логической последнего поступает на

блок 10 управления и триггер 3„ При этом блок 10 управления блокирует дальнейшее прохождение импульсов тактовой частоты с генератора 1 на сдвиговый регистр 9, а триггер 3 переключается и разрешает прохождение импульсов тактовой частоты f0 с генератора 1 через элемент И 2 на входы счетчика 4 результата и делителя 5 частоты. С выхода делителя 5 частоты импульсы с частотами, равными

5

0

5

5 0

0

45

50

..

v

4

1

(О

- f . f 3 f

Я, Го ГП

1

§ Г0 и

поступают на динамические входы двоичного умножителя 6, на управляющие входы которого со сдвигового регистра 9 поступает код числа делителя„ В результате на выходе двоичного умножителя 6 частота повторения импульсов будет равна

, Г

где В - цифровой код числа делителя; m - количество сдвигов числа В в сдвиговом регистре 9 (до совпадения старшего разряда числа делителя со старшим разрядом сдвигового регистра 9); К - количество разрядов двоичного

умножителя 6„

Поэтому при любом значении числа делителя, не равном нулю, в пределах

. (2) С выхода двоичного умножителя 6 имV

f,. находится

о

пульсы частотой повторения fu, поступают на счетный вход управляемого делителя 7 частоты, на управляющий вход которого поступает код с блока 10 управления, при этом коэффициент деления N управляемого делителя 7 частоты зависит от количества сдвигов числа В в сдвиговом регистре 9 делителя следующим образом:

,ГЧ-1

N

(3)

С выхода управляемого делителя 7 частоты импульсы с частотой повторения

v 1-Ґ« - «

поступают на счетный вход счетчика 8 делимого, и когда количество этих импульсов будет равно числу делимого

А, счетчик 8 переполнится Поэтому через время Т на выходе счетчика 8 появится импульс переполнения

А А -9К т -- ----(с,

fTt i-F

te B to

Импульс переполнения со счетчика 8 делимого поступает на триггер 3, который переключается и блокирует прохождение тактовых импульсов с генератора 1 через элемент И 2 на делитель 5 частоты и счетчик 4 результата. За время деления, равное Т, в счетчик 4 результата поступает количество импульсов

- f . Т - Г° L В

(6)

Таким образом, в счетчике 4 фиксируется результат деления числа А на число В.

При введении дополнительного управляемого делителя частоты получается обратно пропорциональная числу делителя относительная точность деления устройства, что приводит к по- вышению быстродействия при максимальном значении числа целителя за счет снижения избыточной точности деления. А при максимальном значении числа делителя быстродействие повышает- ся за счет предварительных сдвигов в сторону старших разрядов числа делителя, что повышает выходную частот двоичного умножителя.

Формула изобретения

1. Устройство для деления, содержащее счетчик делимого, установочные входы которого являются входом делимого устройства, а выход соединен с входом установки в О триггера, выхо которого соединен с первым входом элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, а выход элемента И соединен со счетным входом счетчика результата и тактовым входом делителя частоты, разрядные выходы которого соединены соответственно с входами первой группы двоичного умножителя,

0

5

0

5 о

0

5

0

входы второй группы которого соединены соответственно с разрядными выходами буферного регистра, информационный вход которого является входом | делителя устройства, отличающееся тем, что, с целью повышения быстродействия устройства при требовании относительной точности деления, обратно пропорциональной числу делителя, в него введены блок управления и управляемый делитель частоты, а буферный регистр выполнен в виде сдвигового, причем управляющий вход управляемого делителя частоты соединен с первым выходом блока управления, второй выход которого соединен с синхровходом сдвигового регистра, выход старшего разряда которого соег динен с входом запуска блока управления и входом установки в 1 триггера, выход двоичного умножителя соединен с тактовым входом управляемого делителя частоты, выход которого соединен со счетным входом счетчика делимого, выход генератора тактовых импульсов соединен с синхровходом блока управления, вход признака останова которого соединен с входом управления устройства, установочный вход которого соединен с входами разрешения записи счетчика делимого и сдвигового регистра и входом установки в О блока управления. 2. Устройство по По 1, о т л и- чающееся тем, что блок управления содержит триггер, входы установки и О которого являются соответственно входами запуска и признака останова блока управления, прямой выход триггера соединен с первым входом элемента И, второй вход которого является синхровходом блока управления, а выход элемента И соеди

тактовым входом сдвигового ре- в О которо- 0

нен с

гистра, вход установки го является входом установки в блока управления, первый выход которого соединен с выходом сдвигового регистра, а второй выход блока управления соединен с выходом элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1982 |

|

SU1104508A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Делительное устройство | 1983 |

|

SU1168929A1 |

| Делительное устройство | 1972 |

|

SU468238A1 |

| Усредняющий частотомер | 1978 |

|

SU871096A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

Фиг. 2

Авторы

Даты

1991-01-15—Публикация

1988-09-15—Подача