1

Изобретение относится к информационно-измерительным системам и может применяться в многоканальных системах, использующим квазиобратимое сжатие данных.

Известен адаптивный коммутатор, содержащий входной регистр, блок синхронизации и управления, блок памяти, блоки коммутации, схемы сравнения, аналого-цифровой преобразователь, выходной регистр, блок формирования адреса 1.

Однако этот адаптивный коммутатор работает с аналоговыми сигналами, что является недостатком ввиду того, что больщинство информационно-измерительных систем работает с дискритизацией и преобразованием аналоговых сигналов в цифровую форму.

Наиболее близким по технической сущности к предлагаемому изобретению является адаптивный коммутатор, содержащий входной регистр, выход которого подключен к первому информационному входу арифметического блока, управляющий выход которого подключен к входу формирователя функции приоритета, блок задания апертур, выход которого соединен с управляющим входом арифметического блока, оперативный запоминающий блок, выход и вход которого подключены к информационному

входу и к первому информационному выходу арифметического блока соответственно, блок синхронизации и управления, первый выход которого подключен к входному регистру, второй выход соединен с синхронизирующими входами арифметического блока и оперативного запоминающего блока, а третий выход подключен к входу формирователя адреса и к синхронизирующему входу формирователя функции приоритета, и выходной регистр 2.

Так как адаптивный коммутатор передает свои сигналы в радиолинии с циклической частотой, то поиск отсчета коммутации должен обязательно произойти за наперед заданный период времени, что приводит к потере коммутируемых сигналов и неэффективной работе адаптивного коммутатора.

Целью изобретения является сокращение потерь коммутируемых сигналов.

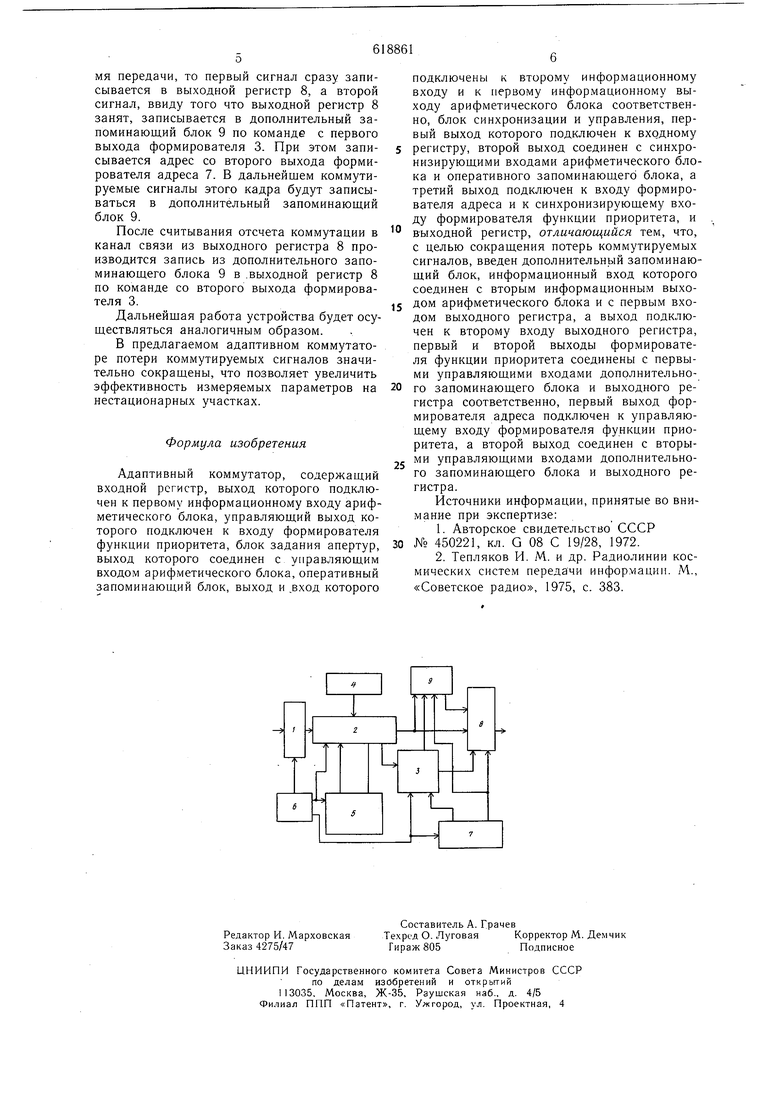

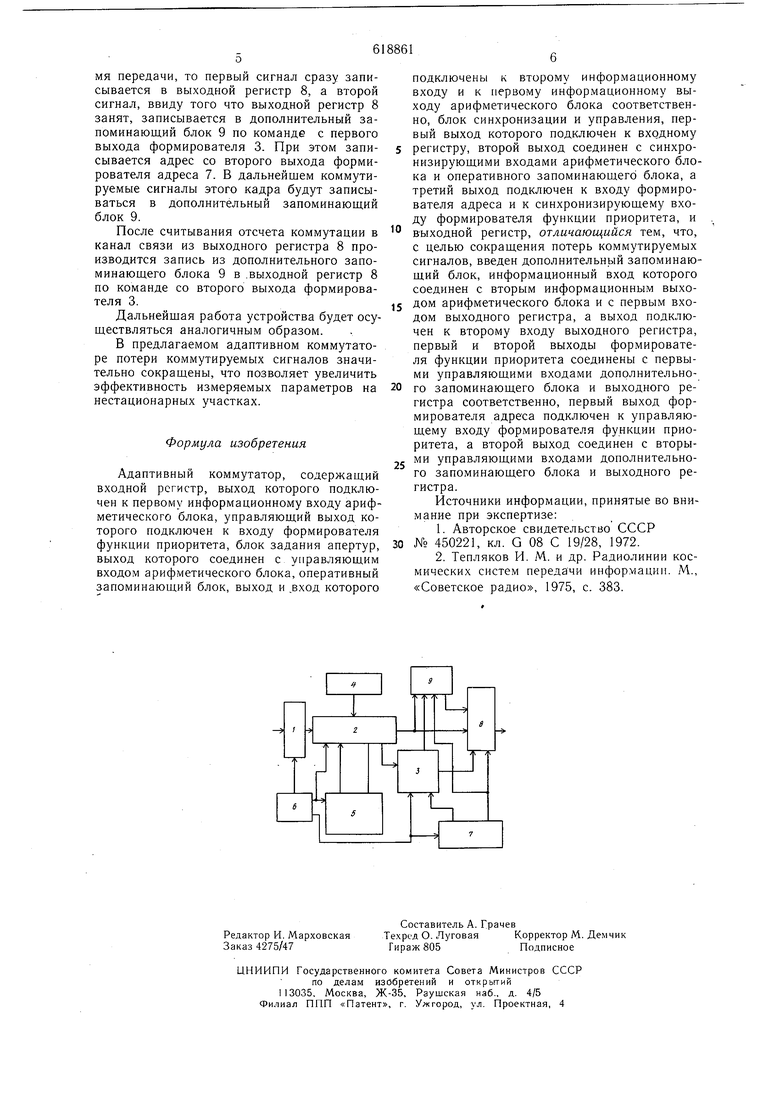

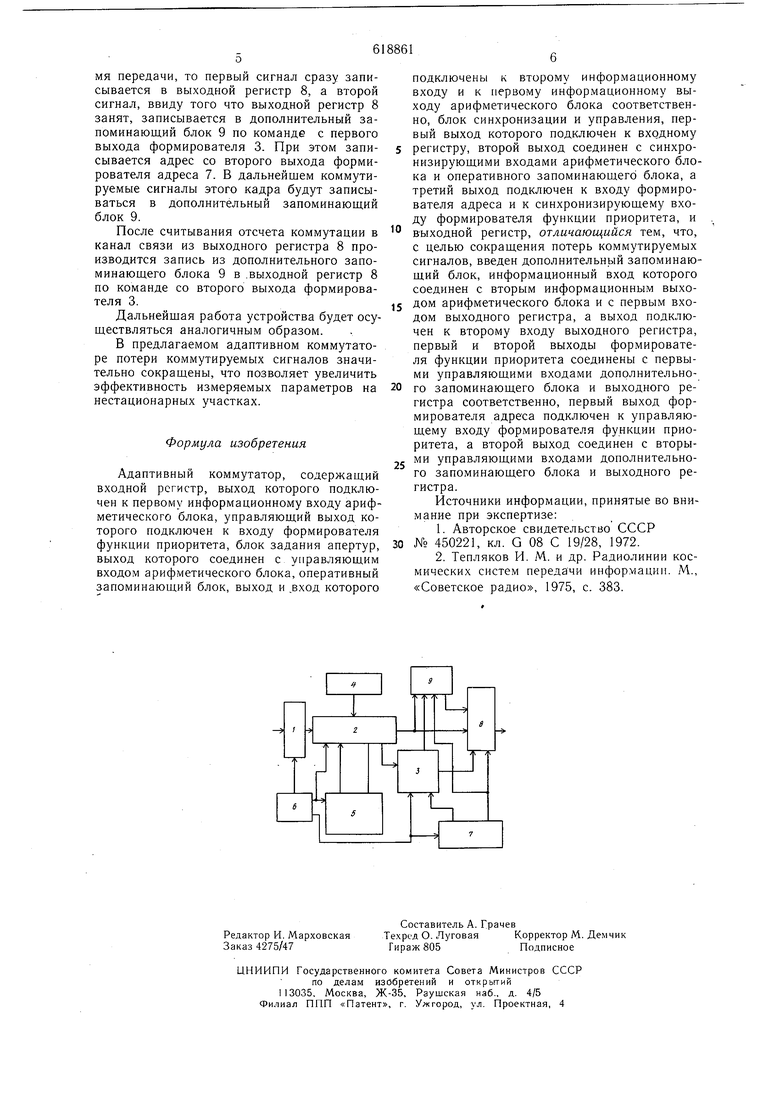

Q Для этого в адаптивный коммутатор, содержащий входной регистр, выход которого подключен к первому информационному входу арифметического блока, управляющий выход которого подключен к входу формирователя функции приоритета, блок задания апертур, выход которого соединен с управляющим входом арифметического блока, оперативный запоминающий блок, выход и вход которого подключены к второму ипформационному входу и к первому информационному выходу арифметического блока соответственно, блок синхронизации и управления, первый выход которого подключен к входному регистру, второй выход соединен с синхронизирующими входами арифметического блока и оперативного запоминающего блока, а третий выход подключен к входу формирователя адреса и к синхронизирующему входу формирователя функции приоритета, и выходной регистр, введен дополнительный запоминающий блок, информационный вход которого соединен со вторым информационным выходом арифметического блока и с первым входом выходного регистра, а выход подключен к второму входу выходного регистра, первый и второй выходы формирователя функции приоритета соединены с первыми управляющими входами дополнительного запоминающего блока и выходного регистра соответственно, первый выход формирователя адреса подключен к управляющему вхбду формирователя функции приоритета, а второй выход соединен со вторыми управляющими входами дополнительного запоминающего блока и выходного регистра. На чертеже изображена структурная электрическая схема предлагаемого адаптивного коммутатора. Адаптивный коммутатор содержит входной регистр 1, выход которого, подключен к первому информационному входу арифметического блока 2, управляющий выход которого подключен к входу формирователя 3 функции приоритета, блок 4 задания апертур, выход которого соединен с управляющим входом арифметического блока 2, оперативный запоминающий блок 5, выход и вход которого подключены к второму информационному входу и к первому информационному выходу арифметического блока 2 соответственно, блок 6 синхронизации и управления, первый выход которого подключен к входному регистру 1, второй выход соединен с синхронизирующими входами арифметического блока 2 и оперативного запоминающего блока 5, а. третий выход подключен к входу формирователя 7 адреса и к синхронизирующему входу формирователя 3 функции приоритета и выходной регистр 8. кроме того коммутатор содержит дополнительный запоминающий блок 9, информационный вход которого соединен с вторым информационным выходом арифметического блока 2 и с первым входом выходного регистра 8, а выход подключен к второму входу выходного регистра 8, первый и второй выходы формирователя 3 функции приоритета соединены с первыми управляющими входами дополнительного запоминающего блока 9 и выходного регистра 8 соответственно. Первый выход формирователя 7 адреса подключен к управляющему входу формирователя 3 функции приоритета, а второй выход соединен с вторыми управляющими входами дополнительного запоминающего блока 9 и выходного регистра 8. Адаптивный коммутатор работает следующим образом. Входные сигналы в цифровой форме поступают с циклической частотой на входной регистр 1. Работу всего устройства и управление осуществляет блок 6 синхронизации. С выхода входного регистра 1 сигналы поступают на арифметический блок 2. Сигналы первого кадра через арифметический блок 2 записываются в оперативный запоминающий блок 5. Начиная со второго кадра, с приходом сигнала из i-ro канала в арифметический блок 2 сигналами управления блока 6 синхронизации переносится сигнал из оперативного запоминающего блока 5 с адресом того же канала. Затем арифметический блок 2 вычисляет разность между поступивщим сигналом из i-ro канала и сигналом того же канала, хранящимся в оперативном запоминающем блоке 5, и сравнивает эту разность с допустимыми границами, задаваемыми блоком 4 задания апертур по тому или иному закону. При превыщении верхней или нижней границы сигнал считается неизбыточньш. При этом с управляющего выхода арифметического блока 2 в формирователь 3 поступает сигнал неизбыточности, по которому со второго вь1хода формирователя 3 на первый управляющий вход выходного регистра 8 поступает сигнал разрещения для записи в выходной регистр 8 коммутируемого сигнала, поступающего с выхода арифметического блока 2. При этом происходит также запись адреса канала в выходной регистр 8 с формирователя 7 адреса. В формирователе 3 задается число отсчетов коммутации за кадр, которые будут переданы. Таких отсчетов может быть несколько, но не больще числа каналов. В случае, когда в формирователе 3 задается конкретное число для передачи отсчетов коммутации, время, через которое будут передаваться отсчеты в канал связи, будет равно частному от деления количества каналов на заданное конкретное число для передачи отсчетов. Передача сигналов в канал связи осуществляется управлением выходного регистра 8 с первого выхода формирователя 7 адреса через второй выход формирователя 3. Для того чтобы существенные сигналы, найденные за время, меньшее времени передачи, не терялись, имеется запоминающий блок 9, емкость которого равна количеству слов, передаваемых за кадр. В случае, если два подряд следуемых сигнала определены коммутируемыми за время передачи, то первый сигнал сразу записывается в выходной регистр 8, а второй сигнал, ввиду того что выходной регистр 8 занят, записывается в дополнительный запоминающий блок 9 по команде с первого выхода формирователя 3. При этом записывается адрес со второго выхода формирователя адреса 7. В дальнейшем коммутируемые сигналы этого кадра будут записываться в дополнительный запоминающий блок 9. После считывания отсчета коммутации в канал связи из выходного регистра 8 производится запись из дополнительного запоминающего блока 9 в .выходной регистр 8 по команде со второго выхода формирователя 3. Дальнейщая работа устройства будет осуществляться аналогичным образом. В предлагаемом адаптивном коммутаторе потери коммутируемых сигналов значительно сокращены, что позволяет увеличить эффективность измеряемых параметров на нестационарных участках. Формула изобретения Адаптивный коммутатор, содержащий входной регистр, выход которого подключен к первому информационному входу арифметического блока, управляющий выход которого подключен к входу формирователя функции приоритета, блок задания апертур, выход которого соединен с управляющим входом арифметического блока оперативный запоминающий блок, выход и .вход которого подключены к второму информационному входу и к первому информационному выходу арифметического блока соответственно, блок синхронизации и управления, первый выход которого подключен к входному регистру, второй выход соединен с синхронизирующими входами арифметического блока и оперативного запоминающего блока, а третий выход подключен к входу формирователя адреса и к синхронизирующему входу формирователя функции приоритета, и выходной регистр, отличающийся тем, что, с целью сокращения потерь коммутируемых сигналов, введен дополнительньш запоминающий блок, информационный вход которого соединен с вторым информационным выходом арифметического блока и с первым входом выходного регистра, а выход подключен к второму входу выходного регистра, первый и второй выходы формирователя функции приоритета соединены с первыми управляющими входами дополнительного запоминающего блока и выходного регистра соответственно, первый выход формирователя адреса подключен к управляющему входу формирователя функции приоритета, а второй выход соединен с вторыми управляющими входами дополнительного запоминающего блока и выходного регистра. Источники информации, принятые во внимание при экспертизе: 1. Авторское свидетельство СССР № 450221, кл. G 08 С 19/28, 1972. 2. Тепляков И. М. и др. Радиолинии космических систем передачи информации. М., «Советское радио, 1975, с. 383.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный коммутатор | 1979 |

|

SU782173A2 |

| Устройство для передачи информации | 1977 |

|

SU746660A1 |

| Адаптивный коммутатор телеизмерительной системы | 1980 |

|

SU877597A1 |

| Адаптивный коммутатор телеизмерительной системы | 1988 |

|

SU1508260A1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Устройство для передачи информации | 1981 |

|

SU1073786A2 |

| Устройство для обработки изображений | 1989 |

|

SU1772806A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

Авторы

Даты

1978-08-05—Публикация

1976-06-14—Подача