Изобретение относится к электроизмерительной технике и может быть использовано при разработке осциллографов с цифровой памятью и цифровых анализаторов аналоговых сигналов.

Известен осциллограф с цифровым запоминанием формы исследуемого сигнала, содержащий блок синхронизации, блок автосдвига, нуль-орган, генератор импульсов, цифроаналоговый преобразователь, регистр, оперативный запоминающий блок, цифроаналоговый преобразователь вертикального отклонения, индикатор, адресный счетчик, цифроаналоговый преобразователь горизонтального отклонения и счетчик импульсов,

Недостатком известного устройства является невозможность регистрации однократных сигналов.

Наиболее близким к предлагаемому по технической сущности является модульный осциллограф, содержащий сменный модуль сбора данных, содержащий шину для подключения к модульному осциллографу, аналоговое устройство согласования, аналого-цифровые преобразователи, буферную память, состоящую из нескольких блоков, состоящих из нескольких элементов, входной преобразователь, выходной мультиплексор, устройство управления параметрами сбора данных, генератор тактовой частоты и схему управления аналого-цифровыми преобразователями.

Все элементы сменного блока сбора данных управляются при помощи ЭВМ, входящей в состав модульного осциллографа.

Схема управления аналого-цифровыми преобразователями представляет собой мультиплексоры, подключающие к входам синхронизации аналого-цифровых преобразователей одну из двух фаз тактовой частоты. Устройство управления параметрами сбора данных представляет собой средства для хранения кодов управления и средства для управления параметрами элементов структурной схемы.

Применяя указанный осциллограф, можно использовать следующие режимы регистрации данных: регистрацию сигналов по двум каналам: регистрацию сигналов по одному каналу с удвоенной частотой отсчетов; регистрацию сигналов по одному каналу с удвоенной разрешающей способностью по уровню.

Алгоритм регистрации повторяющихся сигналов в указанном устройстве не отличается от алгоритма регистрации однократных сигналов.

Недостатком известного устройства является невозможность улучшения разрешающей способности по времени выше значения, соответствующего максимальной частоте отсчетов при регистрации повторяющихся сигналов

Цель изобретения - повышение разрешающей способности по времени при регистрации повторяющихся сигналов

Поставленная цель достигается тем, что устройство сбора данных для цифрового,

0 анализатора сигналов, содержащее два согласующих блока, первые входы которых являются входами устройства, вторые входы подключены к первому и второму входам блока управления, а выходы - к первому и

5 второму входам распределителя, третий вход которого связан с третьим выходом блока управления, а выходы - с аналоговыми входами первого и второго аналого-цифровых преобразователей, выходы которых

0 подключены к соответствующим входам двух блоков буферной памяти, выходы которых связаны с соединительной шиной, подключенной к блоку управления, четвертый выход которого подключен к первому входу

5 блока многофазного генератора выходы которого связаны с соответствующими входами двух блоков коммутаторов, управляющие входы которых подключены к пятому и шестому выходам блока управления соответст0 венно, а выходы - к синхронизирующим входам первого и второго аналого-цифровых преобразователей и буферной памяти соответственно, седьмой выход блока управления подключен к управляющим вхо5 дам блоков буферной памяти, введены два блока совпадения, информационные входы которых подключены к выходам первого и второго аналого-цифровых преобразователей соответственно, а управляющие входы

0 - к первому управляющему выходу блока управления, и блока запуска, первый и второй входы которого подсоединены к выходам первого и второго блоков совпадения, тактовый вход которого подключен к выходу

5 первого блока коммутатора, а управляющие входы - к второму управляющему выходу блока управления, восьмой выход которого подключен к одному из входов каждого блока коммутатора, причем эти входы отключе0 ны от блока многофазного генератора выход блока запуска соединен с вторым входом блока многофазного генератора и входом блока управления.

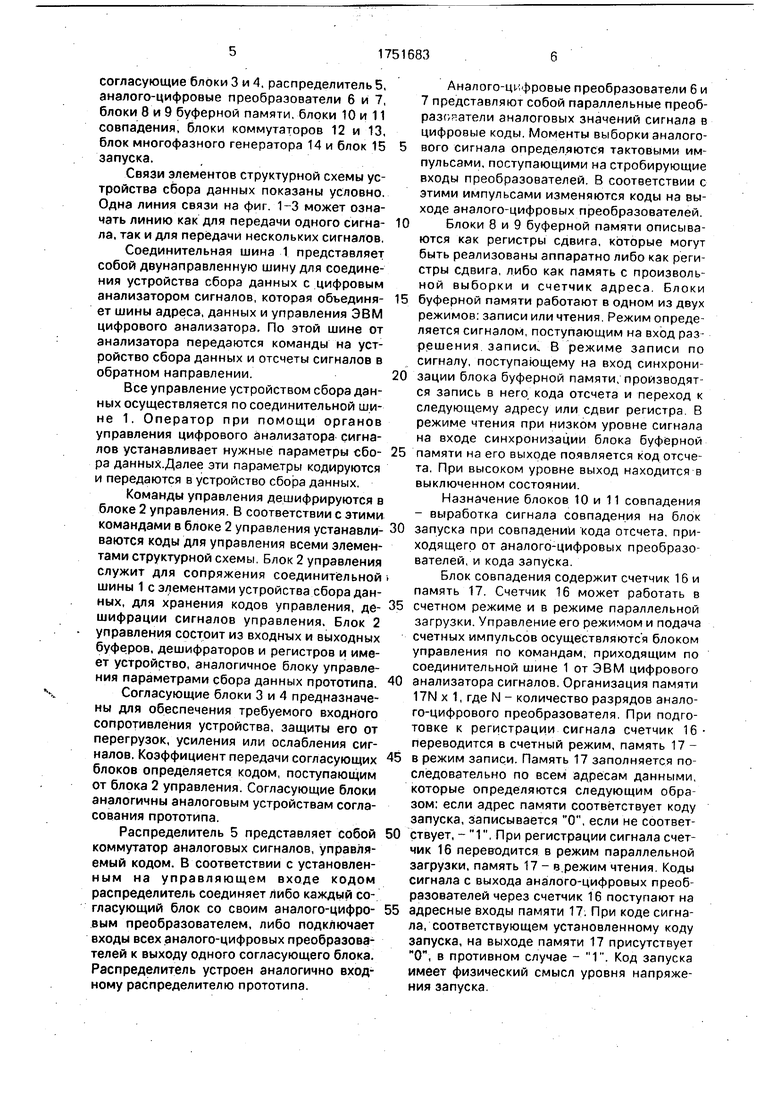

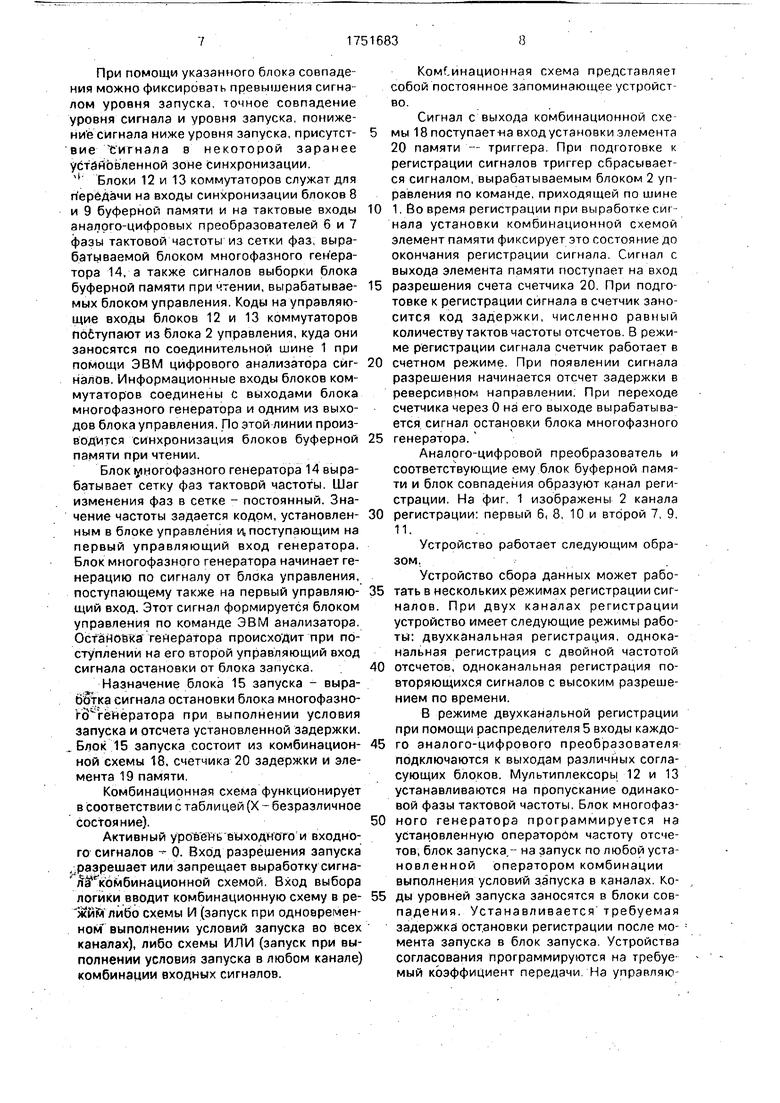

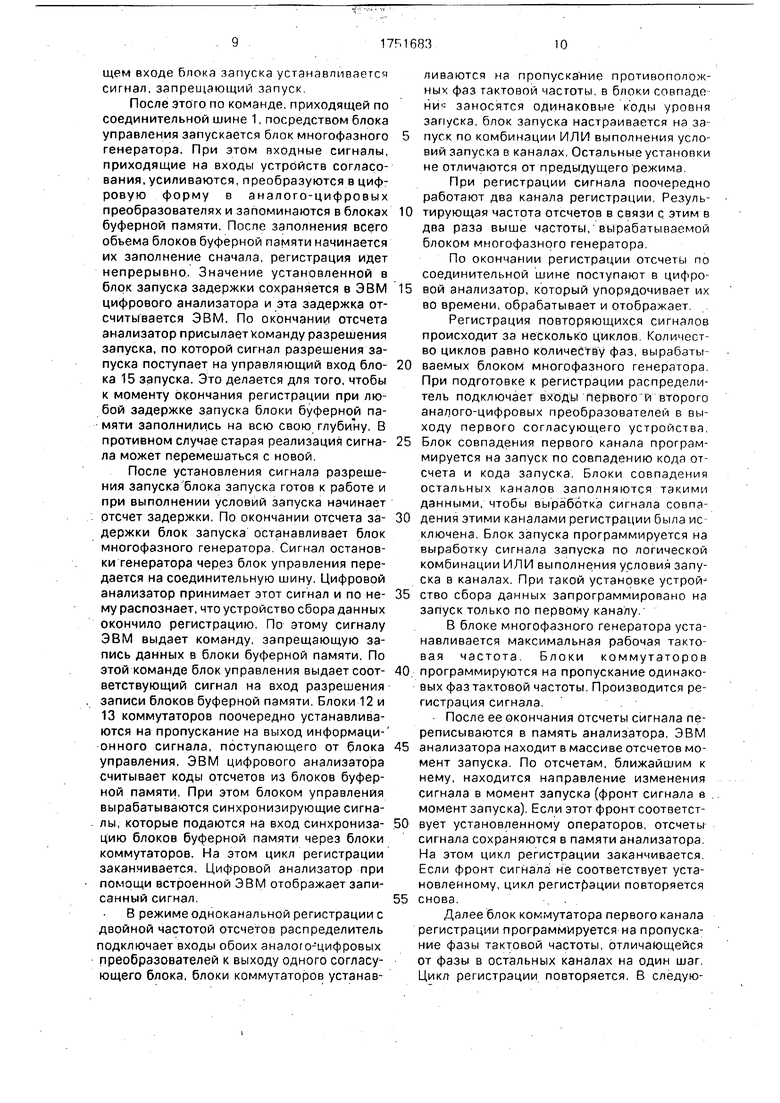

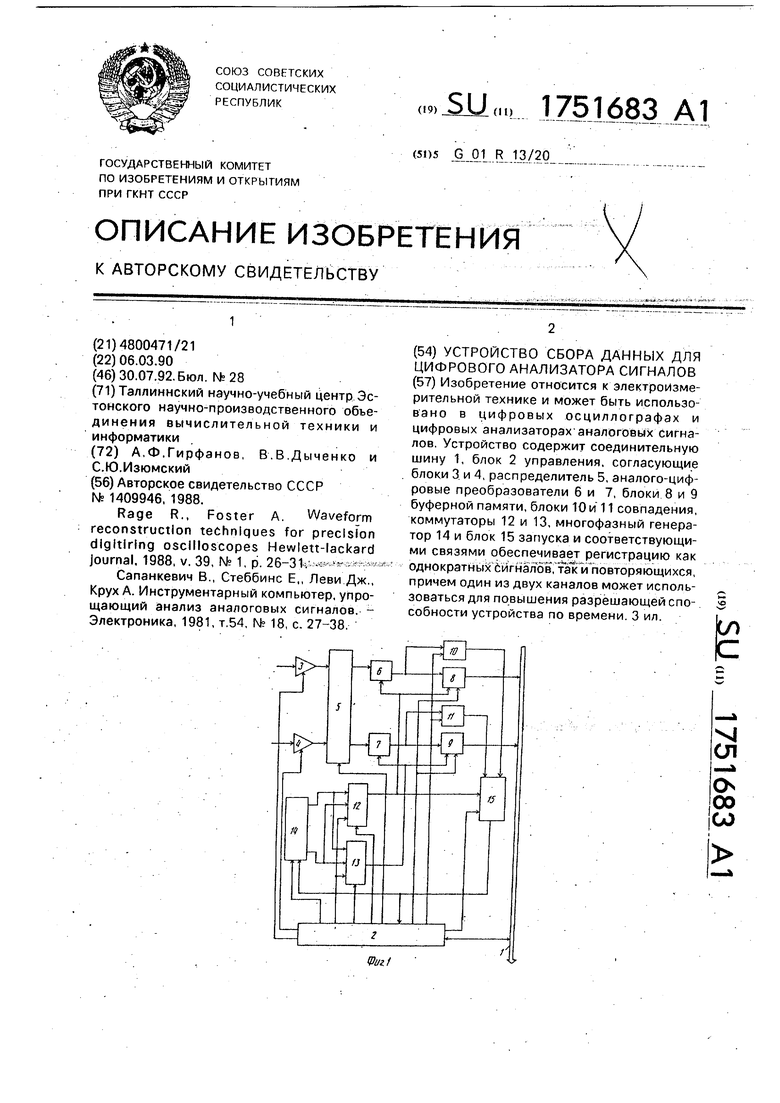

На фиг, 1 изображена структурная схе5 ма устройства сбора данных для цифрового анализатора сигналов; на фиг 2 - структурная схема блока совпадения на фиг 3 - схема блока запуска.

Устройство сбора данных содержит соединительную шину 1, блок 2 управления,

согласующие блоки 3 и 4, распределитель 5, аналого-цифровые преобразователи 6 и 7, блоки 8 и 9 буферной памяти, блоки 10 и 11 совпадения, блоки коммутаторов 12 и 13, блок многофазного генератора 14 и блок 15 запуска.

Связи элементов структурной схемы устройства сбора данных показаны условно. Одна линия связи на фиг. 1-3 может означать линию как для передачи одного сигна- ла, так и для передачи нескольких сигналов,

Соединительная шина 1 представляет собой двунаправленную шину для соединения устройства сбора данных с цифровым анализатором сигналов, которая объединя- ет шины адреса, данных и управления ЭВМ цифрового анализатора. По этой шине от анализатора передаются команды на устройство сбора данных и отсчеты сигналов в обратном направлении.

Все управление устройством сбора данных осуществляется по соединительной шине 1. Оператор при помощи органов управления цифрового анализатора сигналов устанавливает нужные параметры сбо- ра данных.Далее эти параметры кодируются и передаются в устройство сбора данных.

Команды управления дешифрируются в блоке 2 управления. В соответствии с этими командами в блоке 2 управления устанавли- ваются коды для управления всеми элементами структурной схемы. Блок 2 управления служит для сопряжения соединительной шины 1 с элементами устройства сбора данных, для хранения кодов управления, де- шифрации сигналов управления. Блок 2 управления состоит из входных и выходных буферов, дешифраторов и регистров и имеет устройство, аналогичное блоку управления параметрами сбора данных прототипа.

Согласующие блоки 3 и 4 предназначены для обеспечения требуемого входного сопротивления устройства, защиты его от перегрузок, усиления или ослабления сигналов. Коэффициент передачи согласующих блоков определяется кодом, поступающим от блока 2 управления. Согласующие блоки аналогичны аналоговым устройствам согласования прототипа.

Распределитель 5 представляет собой коммутатор аналоговых сигналов, управляемый кодом. В соответствии с установлен- ным на управляющем входе кодом распределитель соединяет либо каждый согласующий блок со своим аналого-цифро- вым преобразователем, либо подключает входы всех аналого-цифровых преобразователей к выходу одного согласующего блока. Распределитель устроен аналогично входному распределителю прототипа.

Аналого-цифровые преобразователи 6 и 7 представляют собой параллельные преобразователи аналоговых значений сигнала в цифровые коды. Моменты выборки аналогового сигнала определяются тактовыми импульсами, поступающими на стробирующие входы преобразователей. В соответствии с этими импульсами изменяются коды на выходе аналого-цифровых преобразователей.

Блоки 8 и 9 буферной памяти описываются как регистры сдвига, которые могут быть реализованы аппаратно либо как регистры сдвига, либо как память с произвольной выборки и счетчик адреса Блоки буферной памяти работают в одном из двух режимов: записи или чтения. Режим определяется сигналом, поступающим на вход разрешения записи. В режиме записи по сигналу, поступающему на вход синхронизации блока буферной памяти, производятся запись в него кода отсчета и переход к следующему адресу или сдвиг регистра В режиме чтения при низком уровне сигнала на входе синхронизации блока буферной памяти на его выходе появляется код отсчета, При высоком уровне выход находится в выключенном состоянии.

Назначение блоков 10 и 11 совпадения - выработка сигнала совпадения на блок запуска при совпадении кода отсчета, приходящего от аналого-цифровых преобразователей, и кода запуска.

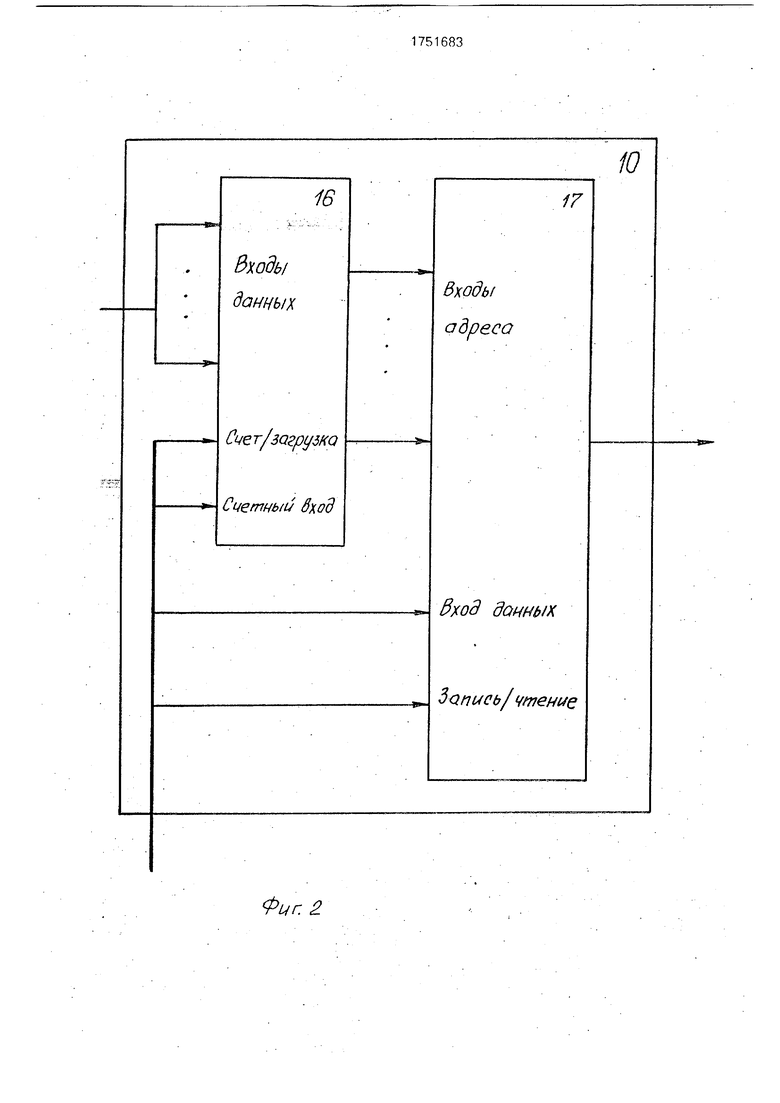

Блок совпадения содержит счетчик 16 и память 17. Счетчик 16 может работать в счетном режиме и в режиме параллельной загрузки. Управление его режимом и подача счетных импульсов осуществляются блоком управления по командам, приходящим по соединительной шине 1 от ЭВМ цифрового анализатора сигналов. Организация памяти 17N х 1, где N - количество разрядов аналого-цифрового преобразователя. При подготовке к регистрации сигнала счетчик 16 переводится в счетный режим, память 17 - в режим записи. Память 17 заполняется последовательно по всем адресам данными, которые определяются следующим образом: если адрес памяти соответствует коду запуска, записывается О, если не соответствует, - 1, При регистрации сигнала счетчик 16 переводится в режим параллельной загрузки, память 17-е режим чтения. Коды сигнала с выхода аналого-цифровых преобразователей через счетчик 16 поступают на адресные входы памяти 17. При коде сигнала, соответствующем установленному коду запуска, на выходе памяти 17 присутствует О, в противном случае - 1. Код запуска имеет физический смысл уровня напряжения запуска.

При помощи указанного блока совпадения можно фиксировать превышения сигнэ лом уровня запуска, точное совпадение уровня сигнала и уровня запуска, пониже- ни е сигнала ниже уровня запуска, присутствие сигнала в некоторой заранее установленной зоне синхронизации. Блоки 12 и 13 коммутаторов служат для п ередачи на входы синхронизации блоков 8 и 9 буферной памяти и на тактовые входы аналого-цифровых преобразователей б и 7 фазы тактовой частоты из сетки фаз, вырабатываемой блоком многофазного генератора 14, а также сигналов выборки блока буферной памяти при чтении, вырабатываемых блоком управления. Коды на управляющие входы блоков 12 и 13 коммутаторов побтупают из блока 2 управления, куда они заносятся по соединительной шине 1 при помощи ЭВМ цифрового анализатора сигналов. Информационные входы блоков коммутаторов соединены с выходами блока многофазного генератора и одним из выходов блока управления, По этой линии производится синхронизация блоков буферной памяти при чтении.

Блок многофазного генератора 14 вырабатывает сетку фаз тактовой частоты. Шаг изменения фаз в сетке - постоянный. Значение частоты задается кодом, установленным в блоке управления и, поступающим на первый управляющий вход генератора. Блок многофазного генератора начинает генерацию по сигналу от блока управления, поступающему также на первый управляющий вход. Этот сигнал формируется блоком управления по команде ЭВМ анализатора. Остановка генератора происходит при поступлении на его второй управляющий вход сигнала остановки от блока запуска.

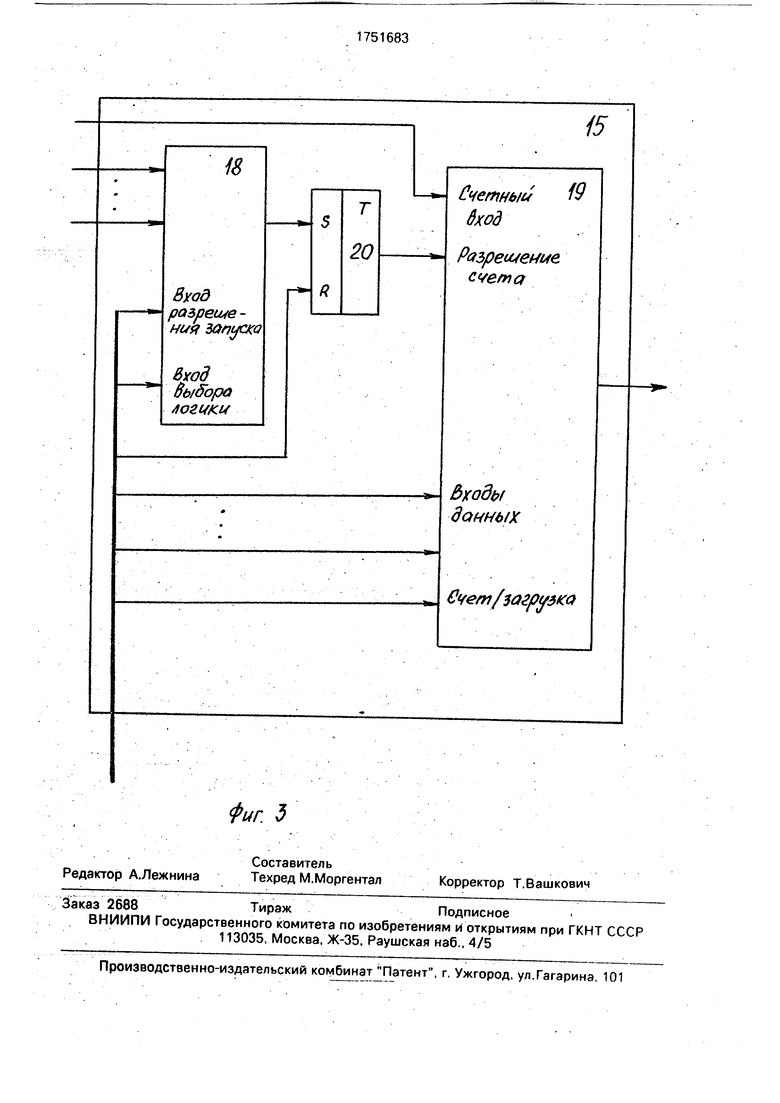

Назначение блока 15 запуска - выработка сигнала остановки блока многофазно- гй генератора при выполнении условия запуска и отсчета установленной задержки. „ Блок 15 запуска состоит из комбинационной схемы 18, счетчика 20 задержки и элемента 19 памяти,

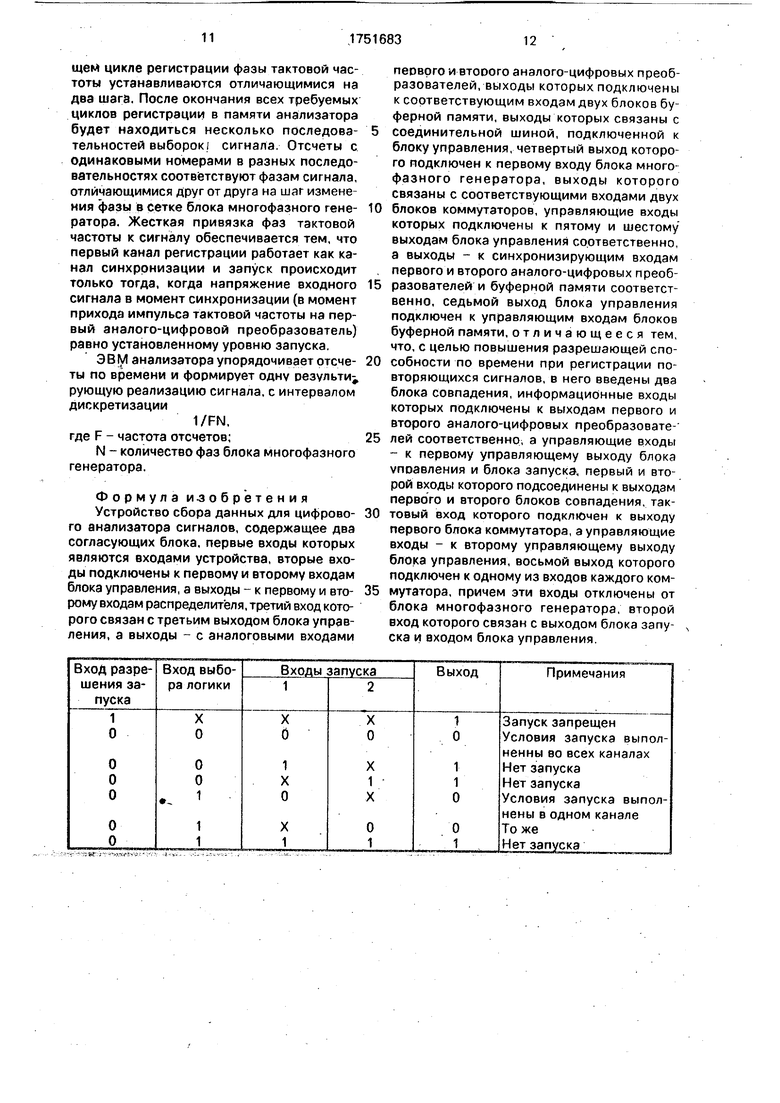

Комбинационная схема функционирует в соответствии с таблицей (X - безразличное состояние).

Активный уров еМь выходного и входного сигналов - 0. Вход разрешения запуска разрешает или запрещает выработку сигна- / комбинационной схемой. Вход выбора логики вводит комбинационную схему в ре- жйм либо схемы И (запуск при одновременном выполнении условий запуска во всех каналах), либо схемы ИЛИ (запуск при выполнении условия запуска в любом канале) комбинации входных сигналов.

Комбинационная схема представляет собой постоянное запоминающее устройст во.

Сигнал с выхода комбинационной схе

мы 18 поступает-на вход установки элемента 20 памяти - триггера При подютовке к регистрации сигналов триггер сбрасывается сигналом, вырабатываемым блоком 2 управления по команде, приходящей по шине

0 1. Во время регистрации при выработке CHI нала установки комбинационной схемой элемент памяти фиксирует это состояние до окончания регистрации сигнала Сигнал с выхода элемента памяти поступает на вход

5 разрешения счета счетчика 20. При подготовке к регистрации сигнала в счетчик заносится код задержки, численно равный количеству тактов частоты отсчетов В режиме регистрации сигнала счетчик работает в

0 счетном режиме. При появлении сигнала разрешения начинается отсчет задержки в реверсивном направлении. При переходе счетчика через 0 на его выходе вырабатывается сигнал остановки блока многофазного

5 генератора.

Аналого-цифровой преобразователь и соответствующие ему блок буферной памяти и блок совпадения образуют канал регистрации. На фиг, 1 изображены 2 канала

0 регистрации: первый 6, 8, 10 и второй 7, 9, 11.

Устройство работает следующим образом.

Устройство сбора данных может рабо5 тать в нескольких режимах регистрации сигналов. При двух каналах регистрации устройство имеет следующие режимы работы: двухканальная регистрация, однока- нальная регистрация с двойной частотой

0 отсчетов, одноканальная регистрация повторяющихся сигналов с высоким разрешением по времени.

В режиме двухканальной регистрации при помощи распределителя 5 входы каждо5 го аналого-цифрового преобразователя подключаются к выходам различных согласующих блоков. Мультиплексоры 12 и 13 устанавливаются на пропускание одинаковой фазы тактовой частоты. Блок многофаз0 ного генератора программируется на установленную оператором частоту отсчетов, блок запуска,- на запуск по любой уста- новленной оператором комбинации выполнения условий запуска в каналах. к.о5 ды уровней запуска заносятся в блоки совпадения. Устанавливается требуемая задержка остановки регистрации после момента запуска в блок запуска Устройства согласования программируются на требуе мый коэффициент передачи На управляющем входе блока запуска устанавливается сигнал, запрещающий запуск

После этого по команде, приходящей по соединительной шине 1, посредством блока управления запускается блок многофазного генератора. При этом входные сигналы, приходящие на входы устройств согласования, усиливаются, преобразуются в цифровую форму в аналого-цифровых преобразователях и запоминаются в блоках буферной памяти. После заполнения всего объема блоков буферной памяти начинается их заполнение сначала, регистрация идет непрерывно. Значение установленной в блок запуска задержки сохраняется в ЭВМ цифрового анализатора и эта задержка отсчитывается ЭВМ. По окончании отсчета анализатор присылает команду разрешения запуска, по которой сигнал разрешения запуска поступает на управляющий вход блока 15 запуска. Это делается для того, чтобы к моменту окончания регистрации при любой задержке запуска блоки буферной памяти заполнились на всю свою глубину. В противном случае старая реализация сигнала может перемешаться с новой

После установления сигнала разрешения запуска блока запуска готов к работе и при выполнении условий запуска начинает отсчет задержки. По окончании отсчета задержки блок запуска останавливает блок многофазного генератора Сигнал остановки генератора через блок управления передается на соединительную шину. Цифровой анализатор принимает этот сигнал и по нему распознает, что устройство сбора данных окончило регистрацию. По этому сигналу ЭВМ выдает команду, запрещающую запись данных в блоки буферной памяти. По этой команде блок управления выдает соответствующий сигнал на вход разрешения записи блоков буферной памяти Блоки 12 и 13 коммутаторов поочередно устанавливаются на пропускание на выход информаци- онного сигнала, поступающего от блока управления, ЭВМ цифрового анализатора считывает коды отсчетов из блоков буферной памяти. При этом блоком управления вырабатываются синхронизирующие сигналы, которые подаются на вход синхронизацию блоков буферной памяти через блоки коммутаторов. На этом цикл регистрации заканчивается. Цифровой анализатор при помощи встроенной ЭВМ отображает записанный сигнал

В режиме однокамальной регистрации с двойной частотой отсчетов распределитель подключает входы обоих аналого-цифровых преобразователей к выходу одного согласующего блока, блоки коммутаторов устанавливаются на пропускание противоположных фаз тактовой частоты в блоки совпаде ни заносятся одинаковые коды уровня запуска блок запуска настраивается на за пуск по комбинации ИЛИ выполнения условий запуска в каналах Остальные установки не отличаются от предыдущего режима

При регистрации сигнала поочередно работают два канала регистрации Резуль0 тирующая частота отсчетов в связи с этим в два раза выше частоты, вырабатываемой блоком многофазного генератора

По окончании регистрации отсчеты по соединительной шине поступают в цифро5 вой анализатор, который упорядочивает их во времени, обрабатывает и отображает

Регистрация повторяющихся сигналов происходит за несколько циклов Количество циклов равно количеству фаз, вырабаты

0 ваемых блоком многофазного генератора При подготовке к регистрации распределитель подключает входы первого и второго аналого-цифровых преобразователей в выходу первого согласующего устройства

5 Блок совпадения первого канала программируется на запуск по совпадению кода отсчета и кода запуска Блоки совпадения остальных каналов заполняются такими данными, чтобы выработка сигнала совпа0 дения этими каналами регистрации была ис ключена Блок запуска программируется на выработку сигнала запуска по логической комбинации ИЛИ выполнения условия запуска в каналах При такой установке устрой5 ство сбора данных запрограммировано на запуск только по первому каналу

В блоке многофазного генератора устанавливается максимальная рабочая тактовая частота Блоки коммутаторов

0 программируются на пропускание одинаковых фаз тактовой частоты Производится регистрация сигнала

После ее окончания отсчеты сигнала переписываются в память анализатора. ЭВМ

5 анализатора находит в массиве отсчетов момент запуска По отсчетам, ближайшим к нему, находится направление изменения сигнала в момент запуска (фронт сигнала е момент запуска) Если этот фронт соответст0 вует установленному операторов отсчеты сигнала сохраняются в памяти анализатора На этом цикл регистрации заканчивается Если фронт сигнала не соответствует установленному, цикл регистрации повторяется

5 снова

Далее блок коммутатора первого канала регистрации программируется на пропускание фазы тактовой частоты, отличающейся от фазы в остальных каналах на один шаг Цикл регистрации повторяется В следующем цикле регистрации фазы тактовой частоты устанавливаются отличающимися на два шага. После окончания всех требуемых циклов регистрации в памяти анализатора будет находиться несколько последова- тельностей выборок; сигнала. Отсчеты с одинаковыми номерами в разных последовательностях соответствуют фазам сигнала, отличающимися друг от друга на шаг изменения фазы в сетке блока многофазного гене- ратора. Жесткая привязка фаз тактовой частоты к сигналу обеспечивается тем, что первый канал регистрации работает как канал синхронизации и запуск происходит только тогда, когда напряжение входного сигнала в момент синхронизации (в момент прихода импульса тактовой частоты на первый аналого-цифровой преобразователь) равно установленному уровню запуска.

ЭВМ анализатора упорядочивает отсче- ты по времени и формирует одну оезульти рующую реализацию сигнала, с интервалом дискретизации

1/FN, где F - частота отсчетов;

N - количество фаз блока многофазного генератора.

Формула изобретения Устройство сбора данных для цифрово- го анализатора сигналов, содержащее два согласующих блока, первые входы которых являются входами устройства, вторые входы подключены к первому и второму входам блока управления, а выходы - к первому и вто- рому входам распределителя, третий вход которого связан с третьим выходом блока управления, а выходы - с аналоговыми входами

первого и ВТОРОГО аналого-цифровых преобразователей, выходы которых подключены к соответствующим входам двух блоков буферной памяти, выходы которых связаны с соединительной шиной, подключенной к блоку управления, четвертый выход которого подключен к первому входу блока многофазного генератора, выходы которого связаны с соответствующими входами двух блоков коммутаторов, управляющие входы которых подключены к пятому и шестому выходам блока управления соответственно, а выходы - к синхронизирующим входам первого и второго аналого-цифровых преобразователей и буферной памяти соответственно, седьмой выход блока управления подключен к управляющим входам блоков буферной памяти, отличающееся тем, что, с целью повышения разрешающей способности по времени при регистрации повторяющихся сигналов, в него введены два блока совпадения, информационные входы которых подключены к выходам первого и второго аналого-цифровых преобразователей соответственно, а управляющие входы - к первому управляющему выходу блока управления и блока запуска первый и второй входы которого подсоединены к выходам первого и второго блоков совпадения, тактовый вход которого подключен к выходу первого блока коммутатора, а управляющие входы - к второму управляющему выходу блока управления, восьмой выход которого подключен к одному из входов каждого коммутатора, причем эти входы отключены от блока многофазного генератора, второй вход которого связан с выходом блока запуска и входом блока управления.

Фиг. 2.

«

Вход

разрешения запуска

вход

Вы&ора

логики

Счетный 19 вход

Разрешение, счета

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дистанционного определения упругих свойств донных осадков | 1987 |

|

SU1649482A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство регистрации сигналов акустической эмиссии | 1987 |

|

SU1516960A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ РЕГИСТРАТОР СИГНАЛОВ | 2016 |

|

RU2616346C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗЛИЧИЙ В ЧУВСТВИТЕЛЬНОСТИ ЭЛЕМЕНТОВ МАТРИЦЫ ФОТОПРИЕМНИКОВ | 1995 |

|

RU2108685C1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС РЕГИСТРАЦИИ И СИНТЕЗА РАДИОТЕХНИЧЕСКИХ СИГНАЛОВ | 2007 |

|

RU2351979C2 |

| Устройство контроля скорости заполнения вакуум-камеры металлом при вакуумировании | 1990 |

|

SU1712426A1 |

Изобретение относится к электроизмерительной технике и может быть использовано в цифровых осциллографах и цифровых анализаторах аналоговых сигналов Устройство содержит соединительную шину 1, блок 2 управления, согласующие блоки 3 и 4, распределитель 5, аналого-цифровые преобразователи 6 и 7, блоки 8 и 9 буферной памяти, блоки 10 и 11 совпадения, коммутаторы 12 и 13, многофазный генератор 14 и блок 15 запуска и соответствующими связями обеспечивает регистрацию как однократных сигналов, так и повторяющихся, причем один из двух каналов может использоваться для повышения разрешающей способности устройства по времени 3 ил. w Ё 1 сл Ск 00 СО Фаг/

&ходы донных

Счет/загрузка

| Цифровой осциллограф | 1986 |

|

SU1409946A1 |

| Rage R., Foster A | |||

| Waveform reconstruction techniques for precision digitirfng oscilloscopes Hewlett-lackard journal | |||

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| - - Сапанкевич В., Стеббинс Е,, Леви Дж., Крух А | |||

| Инструментарный компьютер, упрощающий анализ аналоговых сигналов | |||

| - Электроника, 1981, т 54, N 18, с, 27-38. | |||

Авторы

Даты

1992-07-30—Публикация

1990-03-06—Подача