селе переменного напряжения, первый элемент И выходом соединенный с формирователем коротких импульсов, а входами с формирователем гшпульсов контроля и выходом элемента задержки, и общий регистр-распределитель с числом разрядов, равным числу преобразовательных ячеек, выходы которого соединены с синхронизирующими -входами 1иротно импульсных модуляторов и элементов задержки соответствующих ячеек, общий элемент И выход которого соединен с тактовой шиной регистра-распределентеля, а входы- - с вьпсодами формиропателей коротких импульсов и задающим генератором, обп1Ий измерительный узел цепи обратной связи, входами соеди7532

ненньй с выходными выводами, а выходом - с управляющими входами широтно-импульсных модуляторов, отличающийся, что, с целью устранения возможности появления . повьииенных пульсаций выходного напряжения стабилизатора при работе его с отказами отдельных преобразовательных ячеек, в него введен узел начальной установки регистра-распределителя, вход которого соединен с выходом задающего генератора, а выход с установочным входом S первого разряда и установочными входа.г-ш R остальных разрядов регистрараспределителя, информационньй вход которого соединен с его иоформационным выходом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1422223A1 |

| Многофазный импульсный стабилизаторпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU824161A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1985 |

|

SU1348801A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Многозвенный импульсный стабилизатор | 1984 |

|

SU1157533A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1979 |

|

SU855639A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483440A1 |

| Многофазный импульсный стабилизатор напряжения постоянного тока | 1986 |

|

SU1416957A1 |

| Многофазный импульсный стабилизатор напряжения | 1986 |

|

SU1390605A1 |

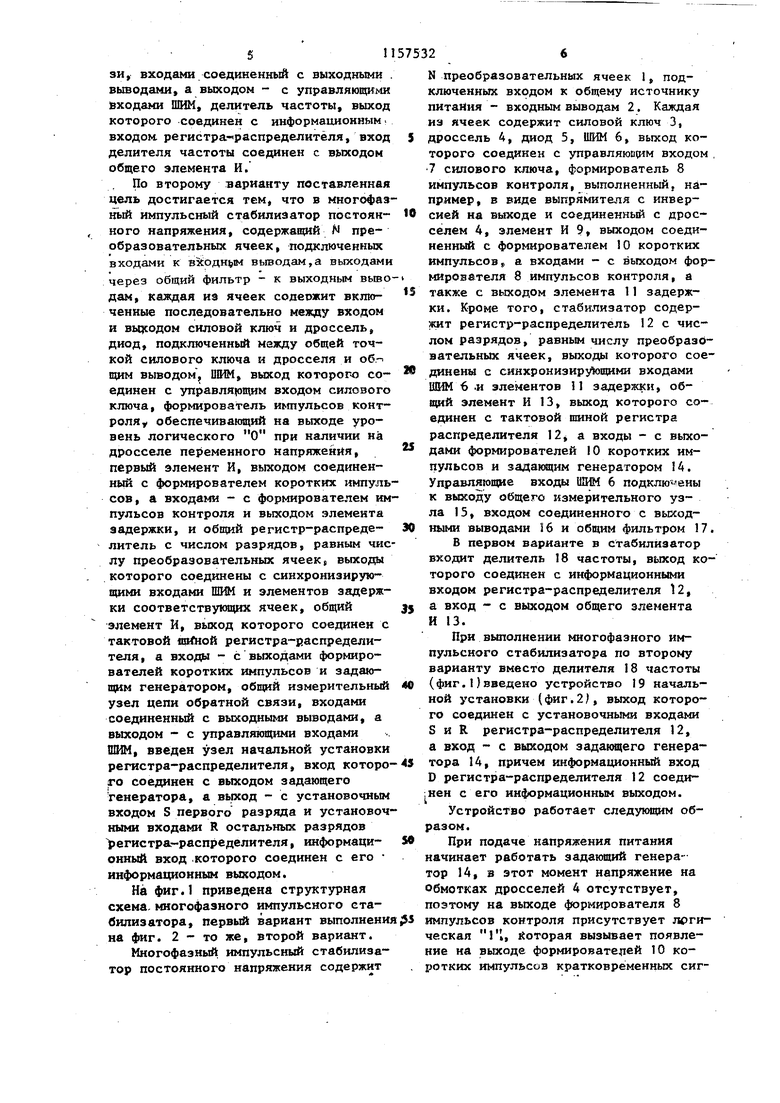

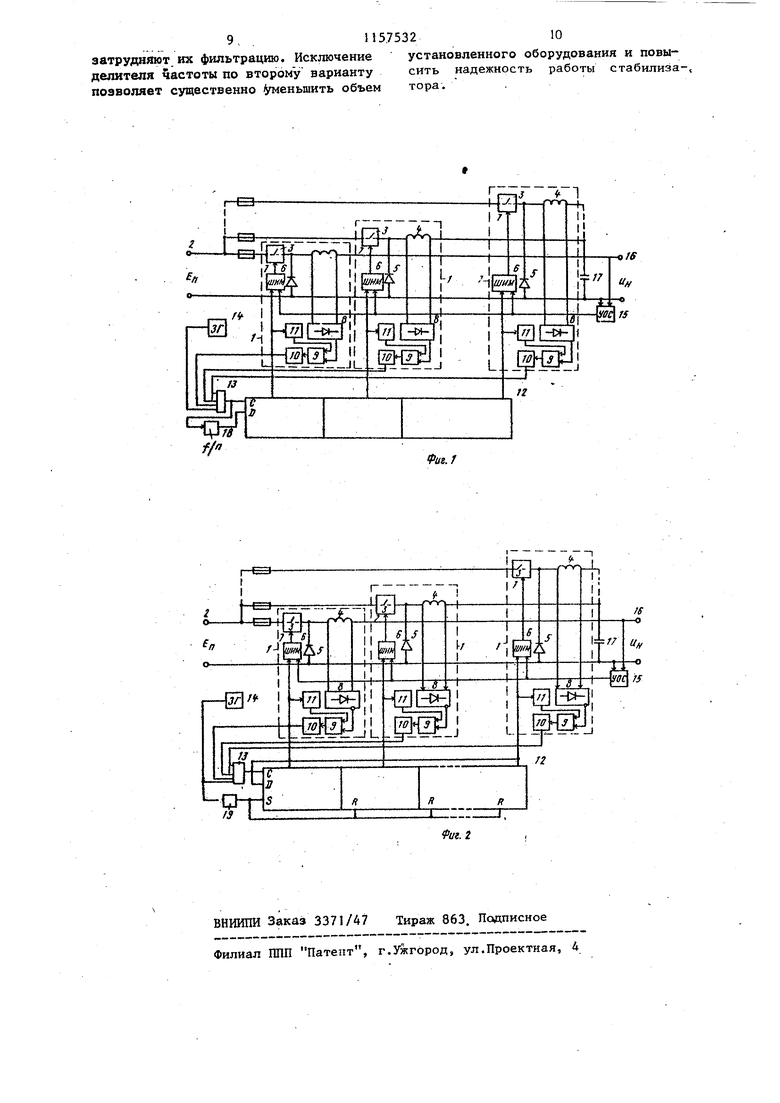

Многофазный импульсный стабилизатор постоянного напряжения, содержащий N преобразовательных ячеек, подключенных входами к входным выводам, а выходами через общий фильтр к выходным выводам, каждая из ячеек содержит включенные последовательно между входом и выходом силовой ключ и дроссель, диoд подключенный между общей точкой силового ключа и дросселя и общим вьгоодом, широтноимпульсный модулятор, выход которого соединен с управляющим входом силового ключа, формирователь импульсов контроля, обеспечивающий на выходе уровень логического О при наличии на дросселе переменного напряжения, первый элемент И, выходом соединенный с формирователем коротких импульсов, а входами - с формирователем импульсов контроля и выходом элемента задержки и общий регистр-распределитель с числом разрядов, равным числу преобразовательных ячеек, выходы которого соединены с синхронизирующими входами широтно-импульсных модуляторов и элементов задержки соответствующих ячеек, общий элемент И, выход которого соединен с тактовой шиной регистра- распределителя, а входы с выходами формирователей коротких импульсов и задающим генератором, общий измерительный узел цепи обратной связи, входами соединенный с выходными выводами, а выходом - с управляющими входами широтно-импульсных модуляторов, делитель частотны, выход которого соединен с информационным входом регистра-распределителя .отличающийся тем, что, с (Л целью устранения возможности появления повышенных пульсаций выходного напряжения стабилизатора при работе его с отказами отдельных цреобразовательных ячеек, вход делителя частоты соединен с выходом общего элемента И. 2. Многофазный импульсный стабиСП лизатор постоянного напряжения,со держащий N преобразовательных ячеек, СП подключенных входами к входным выводам, со ю а выходами через общий фильтр - к выходным выводам, каждая из ячеек содержит включенные последовательно между входом и выходом силовой ключ и дроссель, диод, подключенный между общей точкой силового ключа и ;5росселя и общим выводом, широтноимпульсный модулятор,, выход которого соединен с управлякяцим входом силового ключа,формирователь импульсов контроля обеспечивающий на выходе уровень логического О при наличии на дрос

Изобретение относится к электротехнике, в частности к устройствам стабилизации постоянного напряжения, и может быть применено в системах электропитания повьоиенной надежности для. аппаратуры, требующей стабилизированного постоянного напря женин с малым уровнем пульсаций,

Известен многофазньй импульсный стабилизатор постоянного напряжен-ия, содержащий часть, выполненную в виде параллельно соединенных преобразовательных ячеек, каждая из которызс состоит из сшювого ключа, диода и дросселя, подключеннызс к фильтру и нагрузке, управляющую част содержащую широтно-импульсных модуляторов (ШИМ) по числу ячеек, измерительное устройство цепи обратной связи, задающий генератор и распределитель импульсов с числом выходов, равным числу- преобразовательных ячеек 1.

Недостаток известного импульсного

стабилизатора заключается в том, что ,в нем не- предусмотрено устранение провалов в вьссодном напряжении при отказе одной из нескольких ершовых преобразовательньпс ячеек.

Наиболее близким по технической сущности к иаобретеншо является мног фазный импульсный стабилизатор постоянного напряжения, содержащий И

преобразовательных ячеек, подключен ных входами к входным выводам, а выходами через общий фильтр - к выходным выводам, каждая из ячеек содержит включенные последовательно между входом и выходом силовой ключ и дроссель, диод, подключенный между общей/точкой силового ключа и дросселя-и общим выводом ШИМ, выход которого соединен с управляющим входом силового ключа, формирователь импульсов контроля, обеспечивающий на выходе уровень логического О при наличии на дросселе переменного напряжения, первый элемент И, выходом соединенный с формирователем коротких импульсов, а входами - с формирователем импульсов контроля и выходами элемента задержки, и общий регистр-распределитель с числом раз- рядов, равным числу преобразовательны : ячеек, выходы которого соединенны с синхронизирующими входами ШИМ Н -элемеитов задержки соответствующих ячеек, обилий элемент И, выход которого соединен с тактовой шиной регистра-распределителя, а входы с выходами формирователей коротких импульсов и задающим генератором, общий измерительный узел цепи обратной связи, входами соединенный с выходными вьшодами, а выходом - с управляющими входами ,ШИМ. Кроме то3го, стабилизатор содержит делитель частоты, вход которого соединен с выходом задающего генератора, а выход - с информационньп входом регист ра-распределителя J. Хотя известный стабилизатор обеспечивает обнаружение отказавших преобразовательных ячеек и подключение вместо них исправных избыточных, однако это не избавляет от появления провалов в выходном напряжении при появлении отказавших преобразовательных ячеек. Происходит это потому, что частота работы ячеек постоянна и равна частоте сигнала на выходе делителя частоты. Поскольку коэффициент делителя постоянен и равен максимальному числу ячеек, то сигнал с его выхода, поступающий на информационный вход регистра-распределителя, поступает как раз в то время, когда предыдуя1ий такой сигнал, сдвигаясь по разрядам регистра и распределяясь по преобразовательным ячейкам, достигает последнего разряда в случае отсутствия отказавших ячеек. При появлении отказа в одной из ячеек и при появлении запускающего данную ячейку сигнала на выходе соответствующего разряда регистрараспределителя генерируется на тактовой шине регистра-распределителя лишний тактовый импульс, поступающий с выхода генератора коротких импульсов отказавшей ячейки, который -сдвигает информацию в регистрераспределителе на один разряд вправо, обеспечивая запуск следующей исп равной ячейки. Таким образом, устраняется провал выходного напряжения в момент запуска отказавшей ячейки. Однако это приводит к соответствующему опережению в движении информации по регистру- аспределителю относительно состояния делителя частоты. Сигнал в распределителе, таким образом, раньше достигает послед него разряда, чем появляется на его информационном входе новый. В этот момент в работе стабилизатора появляется нежелательная пауза, длительность которой равна произведению числа отказавших ячеек на период задающего генератора, а в выходном напряжении - провал. Такое положение не может быть исправлено увеличением числа преобразовательных ячеек, так как в этом случае может быть o6ecne 324 чена нормальная работа при наличии отказов. Но если исправны все ячейки, то возникает другое нежелательное явление - появление сигнала с вькода делителя частоты раньше, чем предыдущий такой сигнал достигнет последнего разряда регистра-распределителя, при этом одновременно срабатывают две ячейки: первая и одна из последних, а в выходном напряжении появляется выброс. Таким образом, известный многофазный импульсньй стабилизатор не обеспечивает равномерной работы всех исправных ячеек, и соответственно минимального уровня пульсаций вькодного напряжения стабилизатора при работе его с отказом ;Отдельных преобразовательных ячеек. Целью изобретения является устранение возможности появления повышенных пульсаций выходного напряжения стабилизатора при работе его с отказами отдельных преобразовательных ячеек. По первому варианту поставленная цель достигается тем, что в многофазном испульсном стабилизаторе постоянного напряжения, содержащем N преобразовательных ячеек, прдалюченных входами к входным выводам, а выходами через общий фильтр - к выходным выводам, каждая из йчеек додержит включенные последовательно кежду входом и выходом силовой ключ и дроссель, диод, подключенный между .общей точкой силового ключа и дросселя и общим выводом, ШИМ, выход которого соединен с управляющим входом силового ключа, формирователь импульсов контроля, обеспечивающий на выходе уровень логического О При наличии на дросселе переменного напряжения, первый элемент И, вы- . ходом соединенный с формирователем коротких импульсов, а входами - с формирователем импульсов контроля и выходом элемента задержки, и общий регистр-распределитель с числом разрядов, равным числу преобразовательных ячеек, выходы которого соединены с синхронизирующими входами ШШ и элементов задержки соответствующих ячеек, общий элемент И, выход которого соединен с тактовой шиной регистра-распределителя, а входы - с выходами формирователей коротких импульсов и задающим генератором, общий измерительный узел цепи обратной свя51зи, входами соединенный с выходными выводами, а выходом - с управляющими входами ШИМ, делитель частоты, выход которого соединен с информационным входом, регистра-чраспределитёля, вход делителя частоты соединен с вьпсодом общего элемента И. По второму варианту поставленная цель достигается тем, что в многофаз ный импульсный стабилизатор постоянкого напряжения, содержащий N преобразовательных ячеек, подключенных входами к BkoAHfeiM вьшодам,а выходам через общий фильтр - к выходным вьгоо дам, каждая из ячеек содержит включенные последовательно между входом и вьцсодом силовой ключ и дроссель, диод, подключенный мажду общей точкой силового ключа и дросселя и об.щим выводом, ОШМ, выход которого соединен с управля ощим входом силового ключа, формирователь и myльcoв контроля у обеспечивающий на выходе уровень логического О при наличии на дросселе переменного напряжения, первый элемент И, выходом соединенный с формирователем коротких импуль сов, а входами - с формирователем им пульсов контроля и выходом элемента задержки, и общий регистр-распределитель с числом разрядов, равным чис лу преобразовательных ячеек( выходы которого соединены с синхронизирующими входами ШИМ и элементов задержки соответствуклцих ячеек, общий элемент И, выход которого соединен с тактовой язйИой регистра-распределителя, а входы - с выходами формирователей коротких импульсов и задающим генератором, общий измерительный узел цепи обратной связи, входами соединенный с выходными выводами, а выходом - с управляющими входами ШИМ, введен узел начальной установки регистра-распределителя, вход которо го соединен с выходом задающего генератора, а вьрсод - с установочным входом S первого разряда и установоч ными входами R остальных разрядов регистра-распределителя, информационный вход .которого соединен с его информационным выходом. На фиг.1 приведена структурная схема, многофазного импульсного стабилизатора, первый вариант выполнени на фиг. 2 - то же, второй вариант. Многофазный импульсный стабилизатор постоянного напряжения содержит 2 N преобразовательных ячеек 1, подключенных входом к общему источнику питания - входным выводам 2. Каждая из ячеек содержит силовой ключ 3, дроссель 4, диод 5, ШИМ 6, выход которого соединен с управляюп им входом , 7 силового ключа, формирователь 8 импульсов контроля, выполненный, например, в виде выпрямителя с инверсией на выходе и соединенный с дросселем 4, элемент И 9, выходом соединенный с формирователем 10 коротких импульсов а входами - с выходом формирователя 8 импульсов контроля, а также с выходом элемента 11 задержки. Кроме того, стабилизатор содерясит регистр-распределитель 12 с числом разрядов, равным числу преобразовательных ячеек, выходы которого соединены с синхронизирующими входами ШИМ 6 .и элементов П задержки, общий элемент И 13, выход которого соединен с тактовой шиной регистра распределителя 12, а входы - с выходами формирователей 10 коротких импульсов и задающим генератором 14. Управляющие входы ШИН 6 подклю«-ены к выходу общего измерительного узла 15, входом соединенного с выходными выводами J6 и общим фильтром 17. В первом варианте в стабилизатор входит делитель 18 частоты, выход которого соединен с информационными входом регистра-распределителя 12, а вход - с выходом общего элемента И 13. При выполнении многофазного импульсного стабилизатора по второму варианту вместо делителя 18 частоты (фиг.1)введено устройство 19 начальной установки (фиг.2, выход которого соединен с установочными входами S и R регистра-распределителя 12, а вход - с выходом задающего генератора 14, причем информационный вход D регистра-распределителя 12 соединен с его информационным выходом. Устройство работает следующим обазом. При подаче напряжения питания ачинает работать задающий генераор 14, в этот момент напряжение на бмотках дросселей 4 отсутствует, оэтому на выходе формирователя 8 мпульсов контроля присутствует лргиеская , Которая вызывает появлеие на выходе формирователей 10 коотких импульсов кратковременных сиг71

налов логической , которые устанавливают все, кроме первого, разряды регистра-распределителя 12 в логический О, так как на информационном входе регистра 12 сигнал появляется только через N тактов работы задающего генератора 14. По появлении N+I тактового импульса с выхода задающего генератора 14 на первом выходе регистра-распределителя 12 появляется сигнал , который вызывает включение первой ячейки и появление логической 1 на выходе ее формирователя 8 импульсов контроля. Следующий тактовый импульс вызывает срабатьшание второй ячейки и т.д., стабилизатор выходит на нормальную работу, причем измерительный узел 15 цепи обратной связи устанавливает такой режим работы ШИМ 6, при котором генерируемые ими импульсы, управляющие силовыми ключами 3, обеспечивают передачу мощности Е от источника питания через дроссели 4, диоды 5, сглаживающий фильтр 17 на выходные клеммы 16 с заданным на пряжением. Через каждые N импульсов на выходе делителя 18 частоты ;появ.ляются импульсы с частотой в N раз меньшей частоты задающего генератора 14, которые, поступая на информационный вход . регистра-распределителя 12, поочередно передаются из разряда в разряд, обеспечивая поочередное равномерное срабатывание преобразовательных ячеек.

В случае отказа одной из ячеек напряжение на обмотке дросселя этой ячейки пропадет и появится сигнал логического О на выходе формирователя 8 импульсов контроля отказавшей ячейки, затем по приходе запускающего сигнала на эту ячейку с выхода соответствующего разрядарегистра-распределителя 12 этот сигнал, пройдя через элемент П задержки, вызывает срабатывание формирователя 10 коротких импульсов, выходной импульс которого, пройдя через общий элемент И 13, инициирует внеочередное изменение состояния регистра-распределителя 12, и jia следующем его. выходе появляется сигнал, запускающий следующую преобразовательную ячейку вместо отказавшей. Таким образом, провал выходного напряжения в момент запуска отказавшей ячейки устраняется. Благодаря введенной свя8

зи входа делителя частоты с выходом общего элемента И 13 выходной импульс формирователя 10 коротких импульсов отказавшей ячейки вызывает

5 внеочередное срабатывание и делителя 18 частоты и его состояние также изменится на один такт, поэтому появление отказавших ячеек не вызьгаает появления несинхронности между окончанием цикла распределения по всем ячейкам одного сигнала с выхода делителя 18 частоты и моментом появления следукяцего, который появляется .на информационнвм входе регистра5 распределителя 12 как раз в момент срабатывания последнего разряда, независимо от числа отказавших ячеек. Это гарантирует отсутствие нежелательных пауз в работе преобразовательных ячеек и провалов в выходном напряжении.

Работа второго варианта аналогична первому и отличается только тем,

3 что в момент включения стабилизатора на установочных входах S и R регистра-распределителя присутствует сигнал, устанавливающий все разряды в логический О, кроме первого, который устанавливается в логическую 1. Сразу же после появления импульсов на выходе задающегогенератора 14 установочный сигнал с регист.ра-распределителя 12 снимается и

5 начинается нормальный процесс распределения, так как было описано выше. Сигнал логической I, сдвигаясь по разрядам распределителя 12, обеспечивает равномерное срабатывание преобразовательных ячеек, по достижении им последнего разряда, вновь поступает на вход регистра и процесс повторяется.

Технико-экономические преимущества от применения предлагаемого стаби- . -лизатора заключаются в том, что оно позволяет полностью исключить появление повышенных пульсаций выходного

напряжения в случае работы стабилизатора с отказами отдельных ячеек. Это в свою очередь позволяет снизить вес и габариты и сглаживающего фильтра, так как из спектра выходного то ка стабилизатора исключаются составляющие с частотой работы одной ячейки, сравнительно низкая частота которых и значительная амплитуда весьма

затрудняют их фильтрацию. Исключение установленного оборудования и повыделителя частоты по второму варианту сить надежность работы стабилиза-. позволяет существенно гменьшить объем тора.

1

e/ff

fue-f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Юрченко А.И., Головацкий Б.П., Брагин В.П., Темляков Л.С., Картаев П.И | |||

| и Колосова Г.И | |||

| Мгонофазный импульсньй стабилизатор постоянного напряжения.- Электронная техника в автоматике | |||

| Под ред.Ю.И.Конева, М., Советское радио, 1978, вып.10, с.107-113 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многофазный импульсный стабилизаторпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU824161A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-05-23—Публикация

1984-01-16—Подача