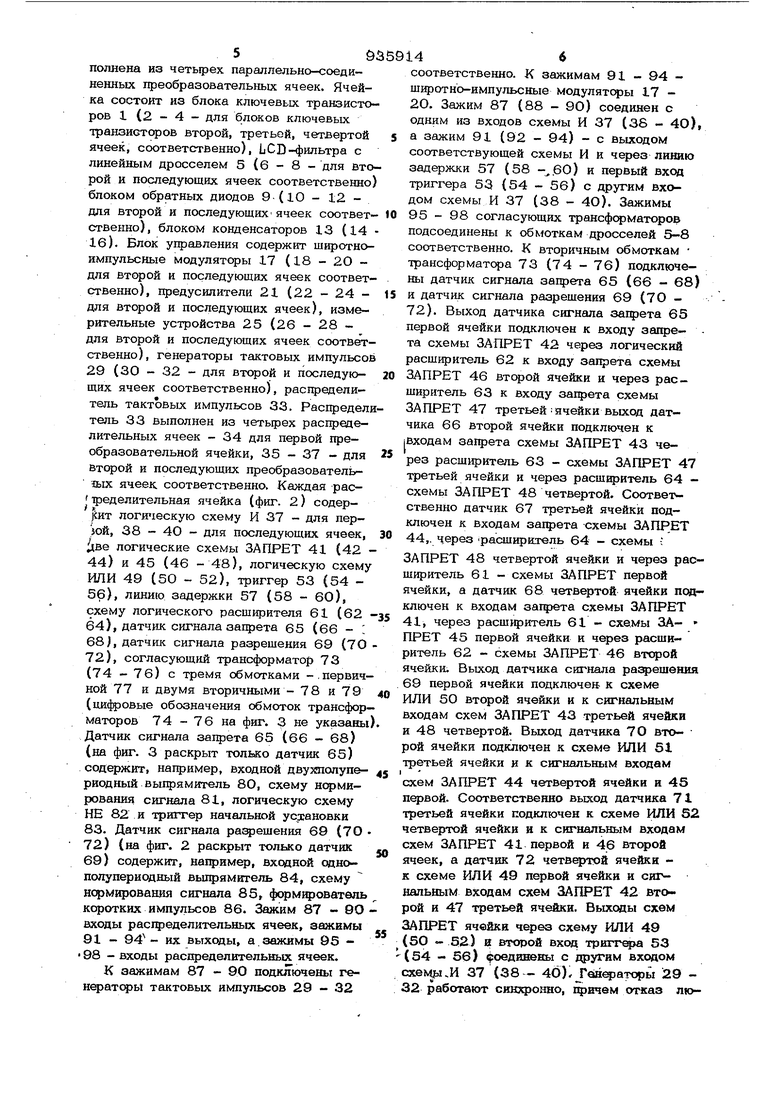

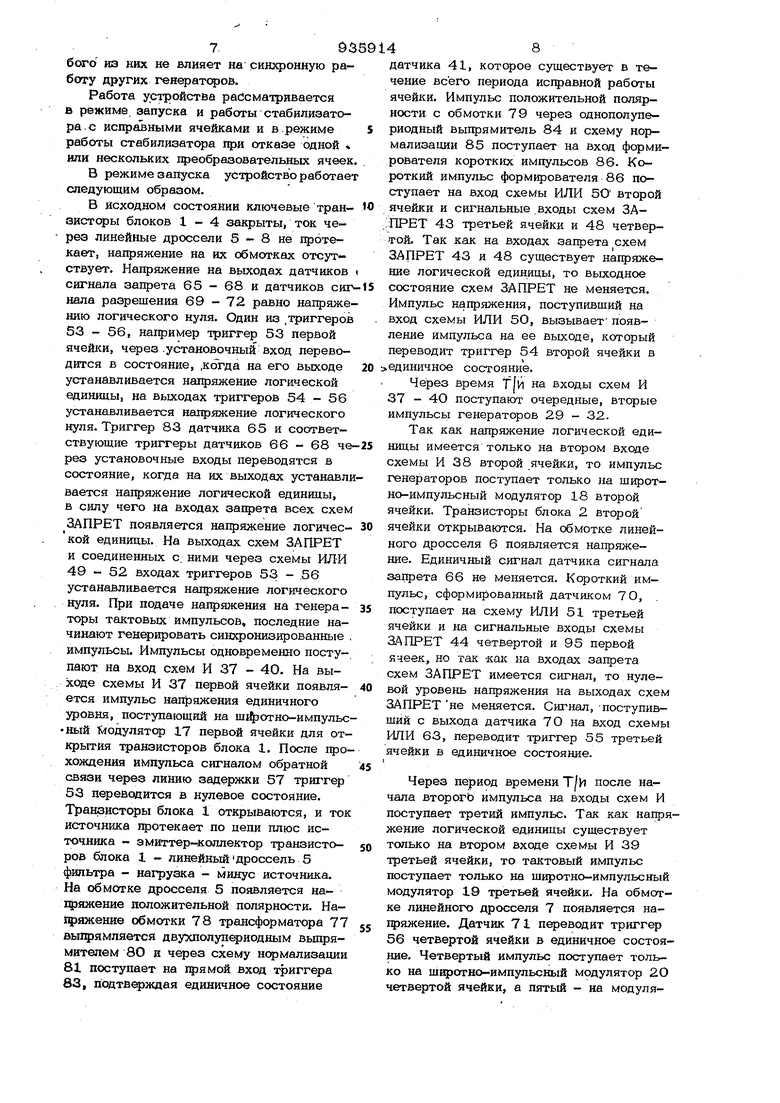

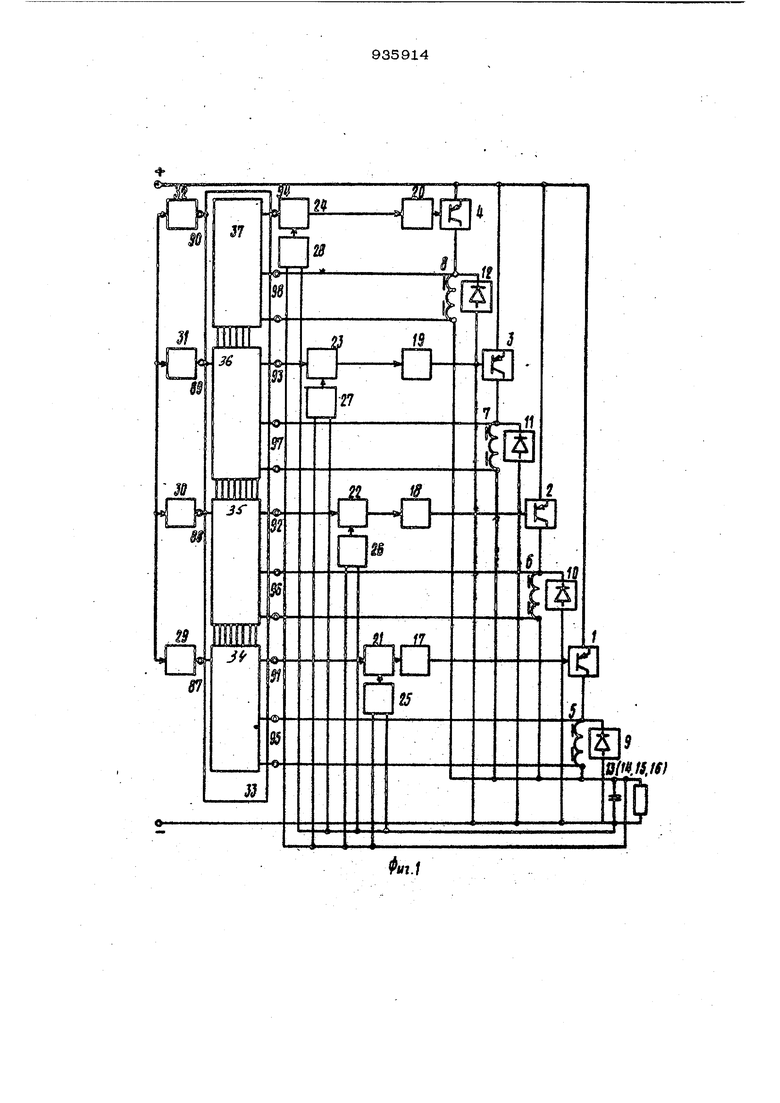

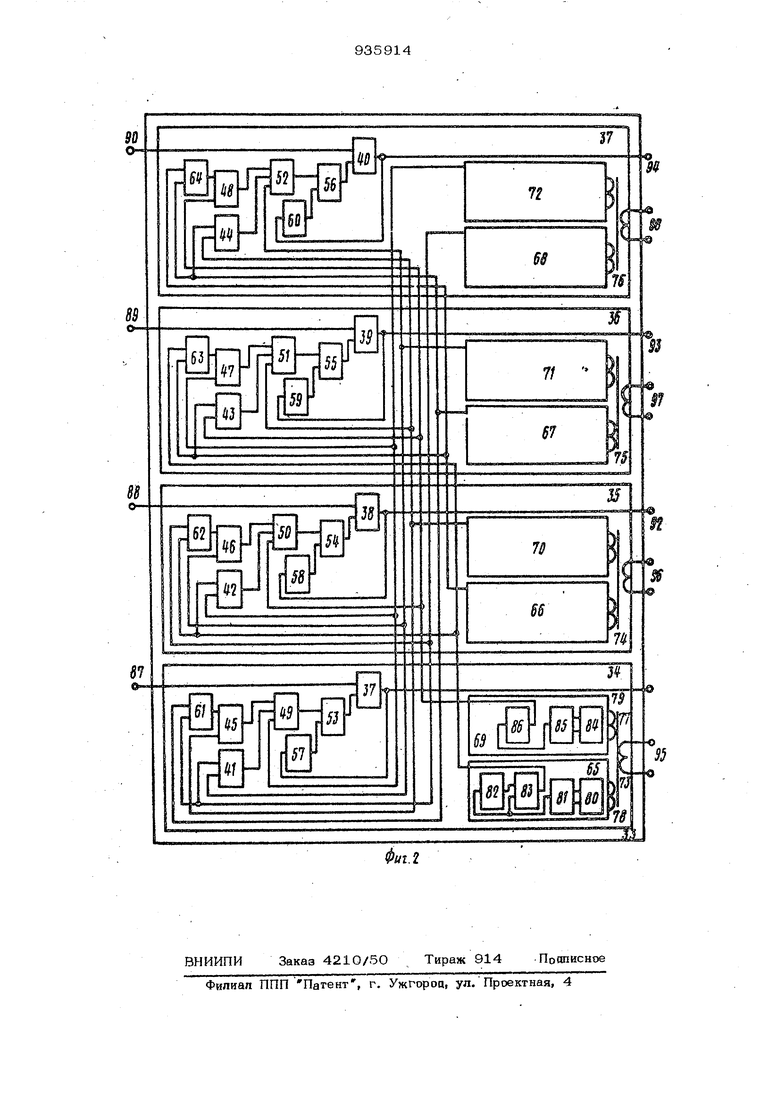

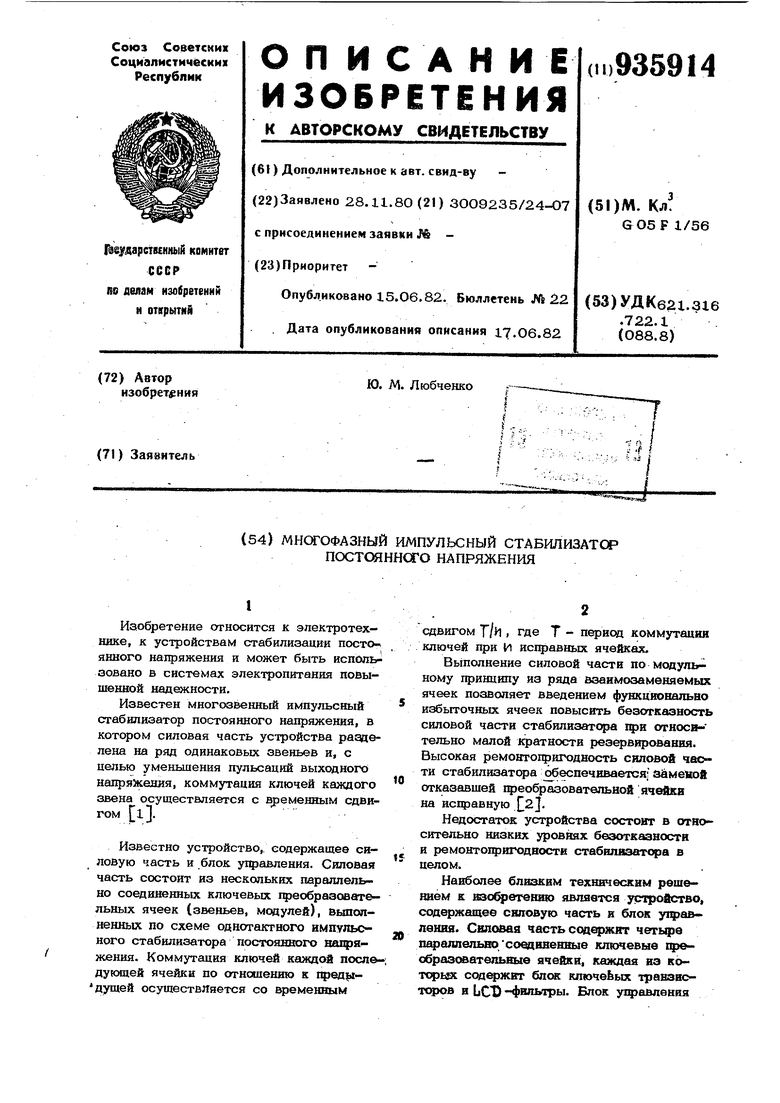

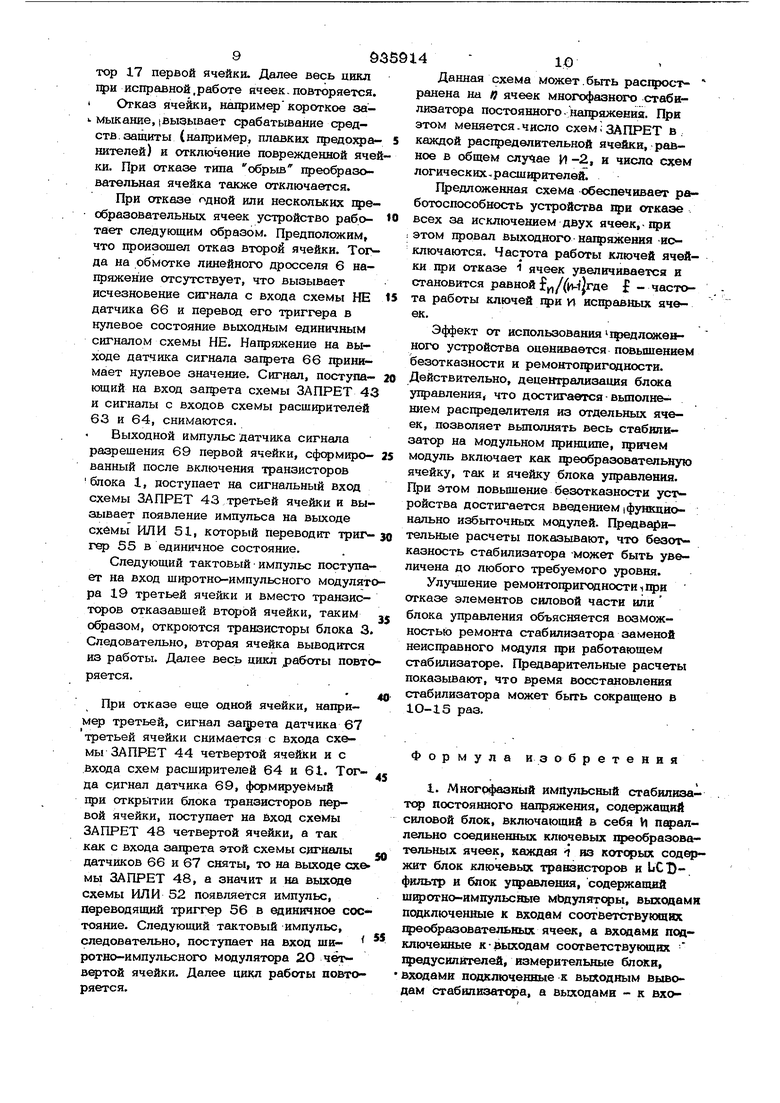

Изобретение относится к электротехнике, к устройствам стабилизации постоянного напряжения и может быть испольаовано в системах электропитания повышенной надежности. Известен многозвенный импульсный стабилизатор постоянного напряжения, в котором силовая часть устройства разделена на ряд одинаковых звеньев и, с целью уменьшения пульсаций выходного напрязкання, коммутация ключей каждого звена осуществляется с временным сдвигом l . Известно устройство, содержащее силовую часть и .блок ущэавления. Силовая часть состоит из нескольких параллельно соединенных ключевых 1реобразоввте- льных ячеек (звеньев, модулей), выполненных по схеме однотактного импульсного стабилизатора постоянного sespaжения. Коммутация ключей каждой после дующей ячейка по отнсшению к пред|)1дущей осуществляется со временным сдвигом г/и . где Т - период коммутации ключей при И исправных ячейках. Выполнение силовой части по модульному принципу из ряда взаимозаменяемых ячеек позволяет введением функционально избыточных ячеек повысить безотказность силовой части стабилизатора пря относительно малой кратности резервирования. Высокая ремоЕггощ)игодность силовой части стабилизатора обеспечивается; заменой отказавшей феобразовательной ячейки на исщзавную 2 J. Недостаток устройства состоит в относительно низких уровнях безотказности и ремонтощ)И1Ч двости стабилизатора в целом. Наиболее близким техническим решением к изо етеаию является устройство, содержащее силовую часть и блок yi aaленва. Свповая честь содержит четьфе параллельносоединенные ключевые itpeобраз жатеш Еыа ячейки, каждая из которь содержит блсж ключеЬых транзисторов и LCD -фильтры. Блок ухфавления ЙЗ содержит для каждой из ячеек широтноимпульсные модупятчры, предусилители, измерительные устройства, генераторы . тактовых-импульсов и распределитель импульсов. Ключевая преобразовательная ячейка выполнена по схеме одНотактного понижающего импульсного стабилизатора постоянного напряжения. Управление ключевыми транзисторами компенсационного : типа обеспечивается широтно-импульс ( ным модулятором с предусилителем и измерительным устройством. Сдвиг по времени в коммутации транзисторов осуществляется расщ)еделителем импульсов, выполненном на основе ЭК триггеров как регистр-распределитель З. Недос1аток устройства состоит в отно сительно низких уровнях безотказности и ремонтопригодности стабилизатора в целом, что связано с централизованным блоком управления. Блок управления не выполним по модульному пршщ1шу из-за применяемых в таких устройствах распре делителей тактовых импульсов, схемы которых не допускают их деления на отдельные ячейки в силу жестдих связей между элементами. Это не позволяет вы полнить стабилизатор из отдельных модулей, каждый из которых бы включал как элементы силовой части, так и элементы блока управления. Данное обстоятельство является причиной противоречин между высокой безотказностью и ; ремонтопригодностью силовой части и относительно низких уровней безотказ ости и ремонтопригодности блока управ леш1я, а значит и стабилизатора :В целом Целью изобретения является повышеше безотказности и ремонтопригодности многофазного импульсного стабилизатора постоянного напряжения. Поставленная цель достигается тем, что в многофазном импульсном стабилизаторе постоянного напряжения, содержащим силовой блок, включающий в себя И параллельно -соедине1шых ключевых пр образовательных ячеек, каждая -1 из которых содержит блок ключевых транзисторов и LCD -фильтр, и блок управления, содержащий ш отно-импульсные модуляторы, выходами подключенные ко входам соответствующих преобразователь ных ячеек, а входами подключенные к выходам соотВетствукмцих предусилителей, измерительные блоки, входами подключенные к выходным выводам стабили затора, а выходами ко входам, соответствующих предусилителеЙ генерат ры та 4 товых импульсов по числу преобразоваельных ячеек, подключегшые к6 входам аспределителя тактовых импульсов, выходы которого подключены к каждому из предусилителей. Распределитель тактовых импульсов выполнен из,И распределцтельных ячеек, каждая 1 из которых содержит логическую схему И, И -2 логических схем ЗАПРЕТ, логическую схему ИЛИ, триггер, линию задержки, схему логического расширителя, датчик сигнала запрета, датчик сигнала разрещения, при этом датчики подключены к дросселю ЬСТ) фильтра -i преобразовательной ячейки непосредственно или через согласующий трансформатор, один из входов схемы И соединен с генератором тактовых импульсов, а выход связан с щиротно-импульсным модулятором 1 -ой преобразовательной ячейки и через линию задержки и первый вход триггера с другим входом схемы И,второй вход триггера через схему ИЛИ соединен с выходами схем ЗАПРЕТ и с Выходом датчика сигнала разрешения 1-1 распределительной ячейки, сигнальный вход каждой ой из У1 -2 схем ЗАПРЕТ соединен с выходом датчика сигнала разре шения -f-J-l распределительной ячейки, а ее вход запрета- с выходами датчшсов сигнала запрета с i-l-ой до -j -j-1-ой распределительных ячеек непосредственно или через схему логического расширителя. Причем датчик сигнала эащэета содержит триггер начальной установки, выход которого является -Выходом датчика, логическую схему НЕ, последовательно соединенные Входной двухполупериодный вьшрямитель i и схему нормирования сигнала, один из выходов которой соединен с первым из Входов триггера начальной установки непосредственно, а другой - со вторым входом триггера датчика через схем| НЕ. Кроме того, датчик сигнала разрешения содержит последовательно соединенные входной однополупериодный вьшрямитель, выходом подключенный ко входу схема нормирования сигнала и формирователь коротких импульсов, выход которого является выходом датчика, а вход подклю- чек к выходу схемы нормирования сигнаНа фиг. 1 представлена принципиальная электрическая схема стабилизатора для четырех ключевых преобразовательных ячеек; на фиг. 2 - принципиальная электрическая схема распределителя { актовых импульсов. Стабилизатор содержит силовую часть и блок у1фавлекия. Силовая часть выполнена из четырех параллельно-соединенных преобразовательных ячеек. Ячейка состоит из блока ключевых транзисторов 1 (2 - 4 - для блоков ключевых транзисторов второй, третьей, четвертой ячеек, соответственно), LCD-фильтра с линейным дросселем 5 (б - 8 - для второй и последующих ячеек соответственно) блоком обратных диодов 9(lO - 12 для второй и последующихячеек соответственно), блоком конденсаторов 13 (14 16). Блок управления содержит широтноимпульсные модуляторы 17 (18-20для второй и последующих ячеек соответственно), предусилители 21 (22 - 24 для второй и последующих ячеек), измерительные устройства 25 (26 - 28 для второй и последующих ячеек соответственно), генераторы тактовых импульсов 29 (30 - 32 - для второй и последующих ячеек соответственно), распределитель тактовых импульсов 33. Распределитель 33 выполнен из четырех распределительных ячеек - 34 для первой преобразовательной ячейки, 35 - 37 - для Второй и последующих преобразовательных ячеек соответственно. Каждая рас тределительная ячейка (фиг. 2) содер)ит логическую схему И 37 - для пер)ой, 38 - 4О - для последующих ячеек, ilBe логические схемы ЗАПРЕТ 41 (42 44) и 45 (46 - 48), логическую схему ИЛИ 49 (50 - 52), триггер 53 (54 56), линию задержки 57 (58 - 60), схему логического расщирителя 61 (62 64), датчик сигнала запрета 65 (66 - , 68), датчик сигнала разрещения 69 (70 72), согласующий трансформатор 73 (74 - 76) с тремя обмотками -.первичной 77 и двумя вторичными - 78 и 79 (ци4ровые обозначения обмоток трансформаторов 74 - 76 на фиг. 3 не указаны Датчик сигнала запрета 65 (б6 - 68) (на фиг. 3 раскрыт только датчик 65) содержит, например, входной двухполупериодный выпрямитель 80, схему нсрмирования сигнала 81, логическую схему НЕ 82 и триггер начальной установки 83. Датчик сигнала разрешения 69 (70 72) (на фиг. 2 раскрыт только датчик 69) содержит, например, входной однополупериодный вьшрямкгель 84, схему нфмирования сигнала 85, формирователь коротких импульсов 86. Зажим 87 - 9О входы расхфеделительных ячеек, зажнмы 91 - их выходы, а зажимы 95 98 - входы распределительных ячеек.

К зажимам 87 - 90 подключены генератфы тактовых импульсов 29-32

соответственно. К зажимам 91 - 94 щиротно-импульсные модулятс зы 17 20. Зажим 87 (88 - 90) соединен с одним из входов схемы И 37 (38 - 40), а зажим 91 (92 - 94) - с выходом соответствующей схемы И и через линию задержки 57 (58 -,60) и первый вход триггера 53 (54-56) с другим входом схемы И 37 (38 - 4О). Зажимы 95-98 согласующих трансформаторов подсоединены к обмоткам дросселей 5-8 соответственно. К вторичным обмоткам трансферматфа 73 (74 - 76) подключены датчик сигнала запрета 65 (66 - 68) и датчик сигнала разрещения 69 (7О 72). Выход датчика сигнала запрета 65 первой ячейки подключен к входу запрета схемы ЗАПРЕТ 42 через логический расщиритель 62 к входу запрета схемы ЗАПРЕТ 46 втсрой ячейки и через расщиритель 63 к входу защэета схемы ЗАПРЕТ 47 третьейЯчейки выход датчика 66 второй ячейки подключен к |Входам запрета схемы ЗАПРЕТ 43 через расщиритель 63 - схемы ЗАПРЕТ 47 третьей ячейки и через расщиритель 64 схемы ЗАПРЕТ 48 четвертой. Соответственно датчик 67 третьей ячейки подключен к Входам защ)ета схемы ЗАПРЕТ 44,. ч,ерез расщиритель 64 - схемы ; ЗАПРЕТ 48 четвертой ячейки и через расщиритель 61 - схемы ЗАПРЕТ первой ячейки, а датчик 68 четвертой ячейки подключен к входам запрета схемы ЗАПРЕТ 41, через расщиритель 61 - схе.мы ЗА- ПРЕТ 45 первой ячейки и через расщиритель 62 - схемы ЗАПРЕТ 46 второй ячейки. Выход датчика сигнала раг ешения 69 первой ячейки подключен- к схеме ИЛИ 50 второй ячейки и к сигнальным входам схем ЗАПРЕТ 43 третьей ячейки и 48 четвертой. Выход датчика 7 О второй ячейки подключен к схеме ИЛИ 51 третьей ячейки и к сигнальным входам схем ЗАПРЕТ 44 четвертой ячейки и 45 первой. Соответственно выход датчика 71 третьей ячейки подключен к схеме ИЛИ 52 четвертой ячейки и к сигнальным входам схем ЗАПРЕТ 41 первой и 46 второй ячеек, а датчик 72 четвертой ячейки к схеме ИЛИ 49 первой ячейки и сш нальным входам схем ЗАПРЕТ 42 второй я 47 третьей ячейки. Выходы схем ЗАПРЕТ ячейки через схему ИЛИ 49 (5О - 52) и второй вход триггера 53 (54 - 5б) фоединены с другим входом ,И 37 (38 - 4б)- Генераторы 29 32 работают сиюфонно, причем отказ любого иа них не влияет на синхронную работу других reHeparqpoB. Работа устройства рассматривается в режиме запуска и работы стабилизатора, с исправными ячейками и в.режиме работы стабилизатора при отказе одной или нескольких преобразовательных ячеек В режиме запуска устройство работает следующим образом. В исходном состоянии ключевые транзисторы блоков 1-4 закрыты, ток через линейные дроссели 5 - 8 не протекает, напряжение на их обмотках отсутствует. Напряжение на выходах датчиков сигнала запрета 65 - 68 и датчиков сиг нала разрешения 69-72 равно напряже нию логического нуля. Один из .триггеров 53 - 56, например триггер 53 первой ячейки, через .установочный вход переводится в состояние, .когда на его выходе устанавливается напряжение логической единицы, на выходах триггеров 54-56 устанавливается напряжение логического нуля. Триггер 83 датчика 65 и соответствующие триггеры датчиков 66-68 че рез установочные входы переводятся в состояние, когда на их выходах устанавл вается напряжение логической единицы, в силу чего на входах загфета всех схем ЗАПРЕТ появляется напряжение логической единицы. На выходах схем ЗАПРЕТ и соединенных с, ними через схемы ИЛ-И 49 - 52 входах триггеров 53 - 56 устанавливается напряжение логического нуля. При подаче напряжения на генера торы тактовых импульсов, последние начинают генфировать синхронизированные импульсы. Импульсы одновременно поступают на вход схем И 37 - 40. На выходе схемы И 37 первой ячейки появляется импульс напряжения единичного уровня, поступающий на шфотно-импульс ный Модулятор 17 первой ячейки для открытия транзисторов блока 1. После про хождения импульса сигналом обратной связи через линию задержки 57 триггер 53 переводится в нулевое состояние. Транзисторы блока 1 открываются, и ток источника протекает по цепи плюс источника - эмиттер-коллектор транзисторов блока 1 - линейньШдроссель 5 фильтра - нагрузка - минус источника. На обмотке дросселя 5 появляется нах яжение положительной полярности. На15эяжение обмотки 78 трансформатора 77 выпрямляется двухполупфиодным вьшрямителем 80 и через схему нормализации 81 поступает на юрямой вход триггера 83, подтверждая единичное состояние датчика 41, которое существует в течение всего периода исгравной работы ячейки. Импульс положительной полярности с обмотки 79 через однополупериодный выпрямитель 84 и схему нормализации 85 поступает на вход формирователя коротких импульсов 86. Короткий импульс формирователя 86 поступает на вход схемы ИЛИ 50 второй ячейки и сигнальные .входы схем ЗАПРЕТ 43 третьей ячейки и 48 четвертой. Так как на входах запрета схем ЗАПРЕТ 43 и 48 существует напряжение логической единицы, то выходное состояние схем ЗАПРЕТ не меняется. Импульс напряжения, поступивщий на вход схемы ИЛИ 5О, вызывает появление импульса на ее выходе, который переводит триггер 54 второй ячейки в единичное состояние. Через время f И на входы схем И 37 - 40 поступают очередные, вторые импульсы генераторов 29 - 32. Так как напряжение логической единицы имеется только на втором входе схемы И 38 второй ячейки, то импульс генераторов поступает только на широтно-импульсный модулятор 18 второй ячейки. Транзисторы блока 2 второй ячейки открываются. На обмотке линейного дросселя 6 появляется напряжение. Единичный сигнал датчика сигнала запрета 66 не меняется. Короткий импульс, сформированный датчиком 7 О, , поступает на схему ИЛИ 51 третьей ячейки и на сигнальные входы схемы ЗАПРЕТ 44 четвертой и 95 первой ячеек, но так -как на входах запрета схем ЗАПРЕТ имеется сигнал, то нулевой уровень напряжения на выходах схем ЗАПРЕТ не меняется. Сигнал, -поступивший с выхода датчика 7 О на вход схемы ИЛИ 63, переводит триггер 55 третьей ячейки в единичное состояние. Через период времени Т/И после начала второгЬ импульса на входы схем И поступает третий импульс. Так как напряжение логической единицы существует только на втором входе схемы И 39 третьей ячейки, то тактовый импульс поступает только на щиротно-импульсный модулятор 19 третьей ячейки. На обмотке линейного дросселя 7 появляется нафяжение. Датчик 71 переводит триггер 56 четвертой ячейки в единичное состояние. Четвертый импульс поступает только на швротно-импульсный модулятор 2 О четвертой ячейки, а пятый - на модулятор 17 первой ячейки. Далее весь цикл при исправной,работе ячеек.повторяется, Отказ ячейки, например короткое за мыкание, (Вызывает срабатывание средств. защиты (например, плавких гфедохра- 5 нителей) и отключение поврежденной ячейки. При отказе типа обрьш преобразовательная ячейка также отключается. При отказе одной или нескольких ipeобразовательных ячеек устройство рабо- 0 тает следующим образом. Предположим, что произошел отказ второй ячейки. Тог да на обмотке линейного дросселя 6 напряжение отсутствует, что вызывает исчезновение сигнала с входа схемы НЕ датчика 66 и перевод его триггера в нулевое состояние выходным единичным сигналом схемы НЕ. Нащэяжение на выходе датчика сигнала загдэета 66 принимает нулевое значение. Сигнал, поступа- ющий на вход загрета схемы ЗАПРЕТ 43 и сигналы с входов схемы расширителей 63 и 64, снимаются. Выходной импульс датчика сигнала разрешения 69 первой ячейки, сфсрмированный после включения транзисторов блока 1, поступает на сигнальный вход схемы ЗАПРЕТ 43 третьей ячейки и вызывает появление импульса на выходе схбмы ИЛИ 51, который переводит триггер 55 в единичное состояние.. Следующий тактовый импульс поступает на вход широтно-импульсного модулят ра 19 третьей ячейки и вместо транзисторов отказавшей второй ячейки, таким образом, откроются транзисторы блока 3 Следовательно, вторая ячейка выводится из работы. Далее весь цикл работы повт ряется. При отказе еще одной ячейки, например третьей, сигнал за |рета датчика 67 третьей ячейки снимается с входа схемы ЗАПРЕТ 44 четвертой ячейки и с Входа схем расширителей 64 и 61. Тогда сигнал датчика 69, формируемый при открытии блока транзисторов первой ячейки, поступает на Вход схемы ЗАПРЕТ 48 четвертой ячейки, а так как с входа запрета этой схемы сигналы датчиков 66 и 67 сняты, то на выходе сх& мы ЗАПРЕТ 48, а значит и на выходе схемы ИЛИ 52 появляется импульс, переводящий триггер 56 в единичное сос тояние. Следующий тактовый импульс, следовательно, поступает на вход широтно-импульсного модулятора 2О четвертой ячейки. Далее цикл работы повторяется. Данная схема может.быть paciqxx-Tранена на п ячеек многофазного стабилизатора постоянного-1 ш1фяжения. При этом меняется.число схем;ЗАПРЕТ в. каждой распределительной ячейки, равное в общем случае И -2, и число схем логических-расширителей. Предложенная схема обеспечивает работоспособность устройства 1фи отказе всех за исключением двух ячеек,-при этом провал выходного напряжения исключаются. Частота работы ключей ячейки при отказе 1 ячеек увеличивается и становится равной Дм|где - частота работы ключей 1фи и исщэавных ячеек. Эффект от использования т юдложе ного устройства оценивается повышением безотказности и ремонто1)игодности. Действительно, децентрализация блока управления, что достигается вьшолнением распределителя из отдельных ячеек, позволяет выполнять весь стабилизатор на модульном принципе, 1Ц}ичем модуль включает как хфеобразоватепьную ячейку, так и ячейку блока управления. При йтом повьш1ение безотказности устройства достигается введением{функционально избыточных модулей. Предварнтельные расчеты показывают, что беаотказность стабилизатора может быть увеличена до любого требуемого уровня. Улучшение ремонтогфигодности при отказе элементов силовой части или блока управления объясняется возможностью ремонта стабилизатора заменой неисправного модуля щж работающем стабилизаторе. Предварительные расчеты показывают, что время восстановления стабилизатора может быть сокращено в Ю-15 раз. Формула изобретения 1. Многофазный импульсный стабилизаTqp постоянного напряжения, содержащий силовой блок, включающий в себя И пфаллетшно соединенных ключевых щюобразовательных ячеек, каждая i из которых содержит блок ключевых транзисторов и LCDфильтр и блок у1Ц}авления, содержащий ш отно-импульсные мЬдуляторы, выходами подключенные к входам соответствующих хфеобразовательных ячеек, а входвмн подключенные к-выходам соответствующих 1федусилителей, измерительные блоки, входами подключенные к выходным выводам стабилизат Чв« в выходами - к входам соответствующих предусилитепей, генераторы тактовых импульсов по числу преобразовательных ячеек, подключенные к входам распределителя тактовых импуль сов, выходы которого подключены к каждо му из предусилителей, отличающийся тем, что, с целью повьпиения безотказности и ремонтопригодности стагбилизатора, распределитель тактовых импульсов выполнен иэ и распределительных ячеек, каждая i из которых содержит логическую схему И, И -2 логических схем ЗАПРЕТ, логическую схему ИЛИ триггер, линию задержки, схему логического расширителя, датчик сигнала захфета, датчик сигнала разрещения, при этом датчики подключены к дросселю ,L,CD -фильтра -J хфеобразовательной ячейки непосредственно или через согласующий трансформатор, один из входов схемы И соединен с генератором тактовых импульсов, а выход связан с широтно-импульсным модулятором I-той тфеобразоййтеяьной ячейки и через линию задержки и первый вход триггера - с другим Входом схемы И, втсрой вход триггера через схему ИЛИ соединен с выходами схем ЗАПРЕТ и с выходом датчика сигнала разрешения i -1 распределительной ячейки, сигнальный вход кажНой j -ой jaa V1-2 схем ЗАПРЕТ соединен с выходом датчика сигнала разрешения -f - j -1 распределительной ячейки, а ее вход 3ajqjeTa с выходами датчиков сигнала зафета с -1 -t до 1 - j -1 распределительных ячеек непосредственно или схеМу логического расширителя.

2. Стабилизатор поп, 1,отличают и и с я тем, что датчик сигнала

I защэета содержит триггер начальной установки, выход которого является выходом датчика, логическую схему НЕ, последовательно соединенные входной двухполупериодный вьичэямитель и схему нормирования сигнала, один из выходов которой соединен с первым из входов триггера начальной установки непосредственно, а другой - с вторым входом триггера датчика через схему НЕ.

3. Стабилизатор по п. 1, отличающийся тем, что датчик сигнала разрешения содержит последовательно соединенные входной однополупериодный выпрямитель, выходом подключенный к входу схемы норм1фования сигнала, и формирователь коротких импульсов, выход которого является выходом датчика, а вход подключен к выходу схемы нормирования сигнала.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № .327462, кл. G 05 F 1/56, 1972.

2.Юрченко А. И. и др. Многофазный импульсный стабилизатор постоянного напряжения. Электронная техника в автоматике. Под ред. Ю. И. Конева. М., Советское радио, 1978, вып. 10, рис. 1. с. 108, рис. 2 с. 111.

3.Юрченко А. И. Многофазный импульсный стабилизатор постоянного напряжения на высоковольтных транзисторах. Электронная ftexHHKa в автоматике. Под. ред. КЗ, И. Конева. М., Советское

радио, 1977, вьш. 9, рис. 1, с. 57, рис. 2 с. 59.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1561068A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1985 |

|

SU1348801A1 |

| Многофазный импульсный стабилизаторпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU824161A1 |

| Стабилизированный преобразователь постоянного напряжения | 1981 |

|

SU995227A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1979 |

|

SU855639A1 |

| Устройство для управления многофазным импульсным регулятором | 1981 |

|

SU957411A1 |

| Многофазный импульсный стабилизатор напряжения | 1986 |

|

SU1390605A1 |

| Устройство для управления N - фазным импульсным преобразователем напряжения | 1989 |

|

SU1791925A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

В 7 --jy

71

je

я

7S

вч

&

«5

p 4Г

57

4f

J

. 9

71

t«

5

S5

7J1

шп 7S

Авторы

Даты

1982-06-15—Публикация

1980-11-28—Подача