Изобретение относится к электротехнике, к устройствам стабилизации постоянного напряжения, и может быт использовано в системах питания аппаратуры, требующей стабилизирован- ного постоянного напряжения с малым уровнем амплитуды пульсаций.

Целью изобретения явояется повышение надежности при работе с одной или несколькими отказавшими преоб- разовательными ячейками при малом уровне пульсаций.

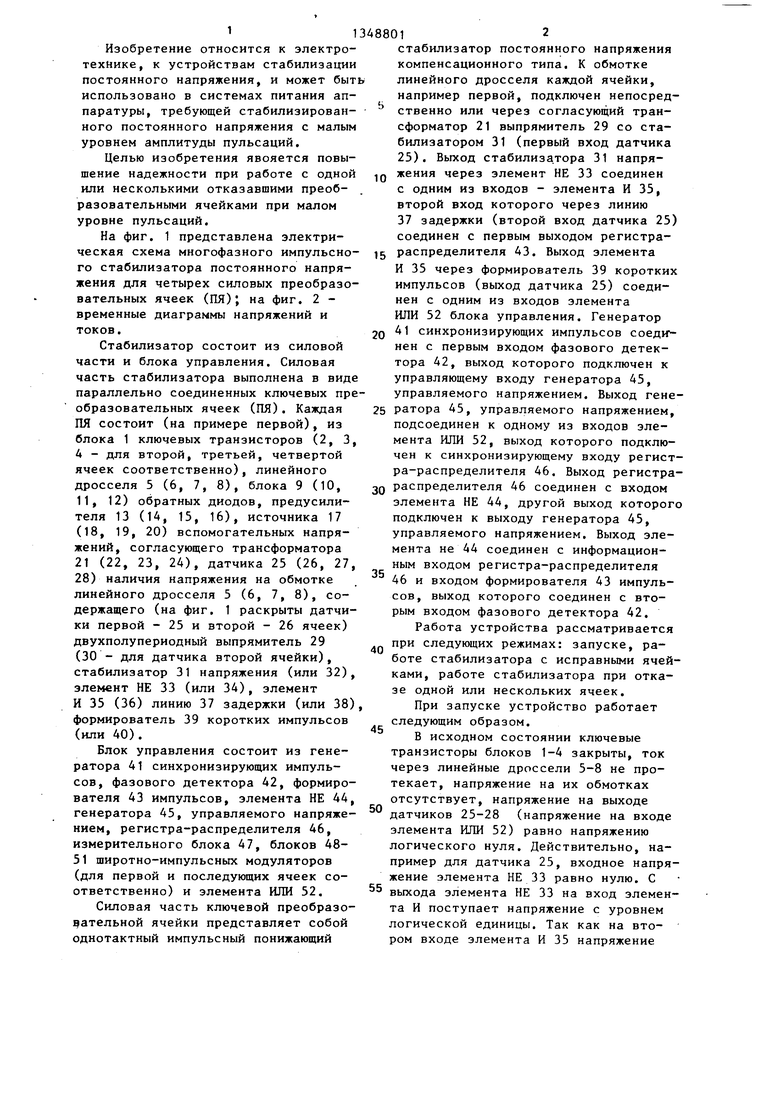

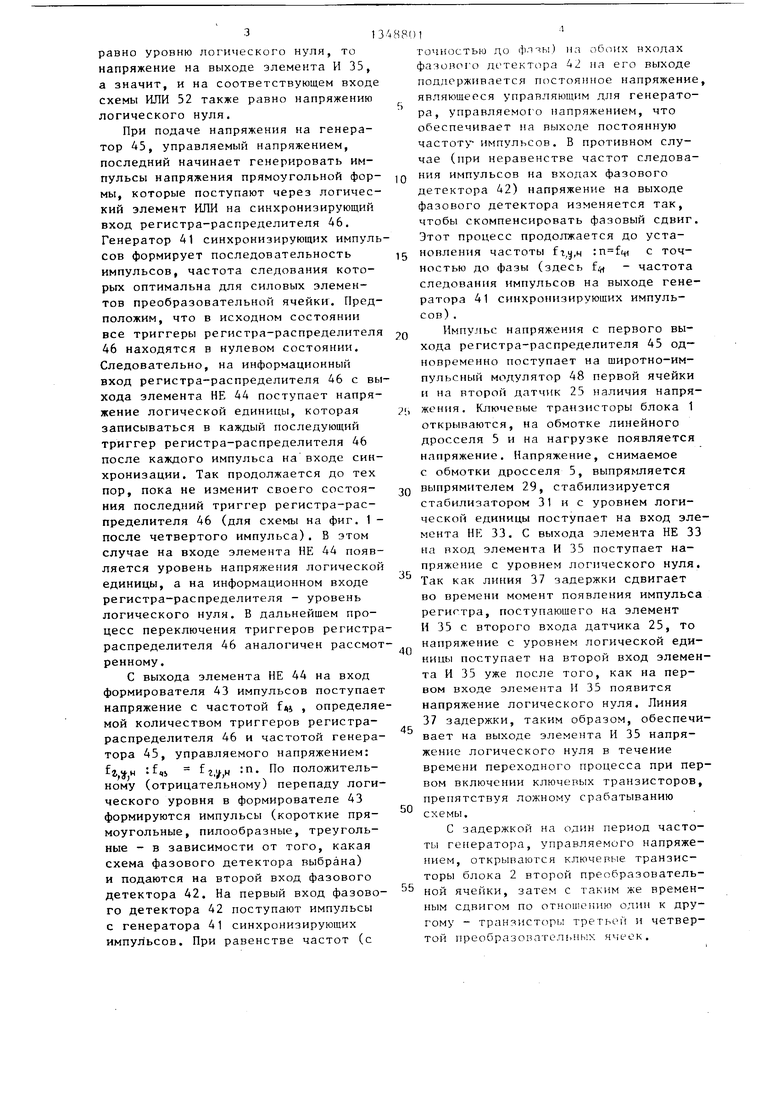

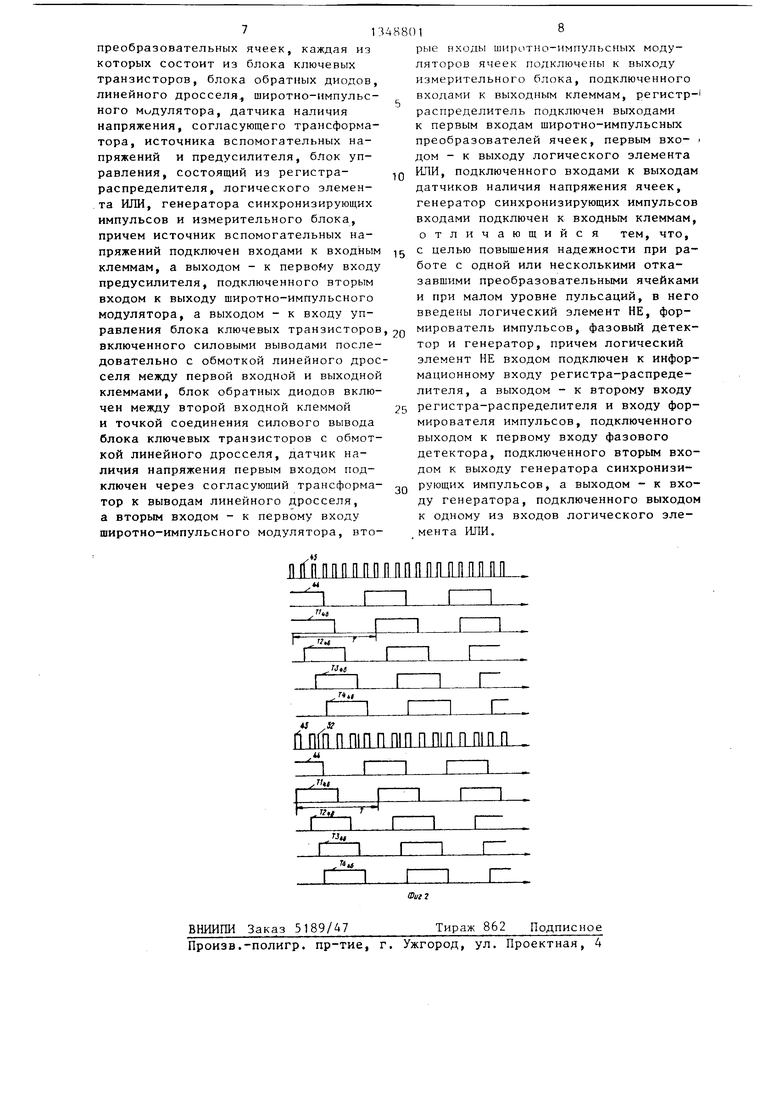

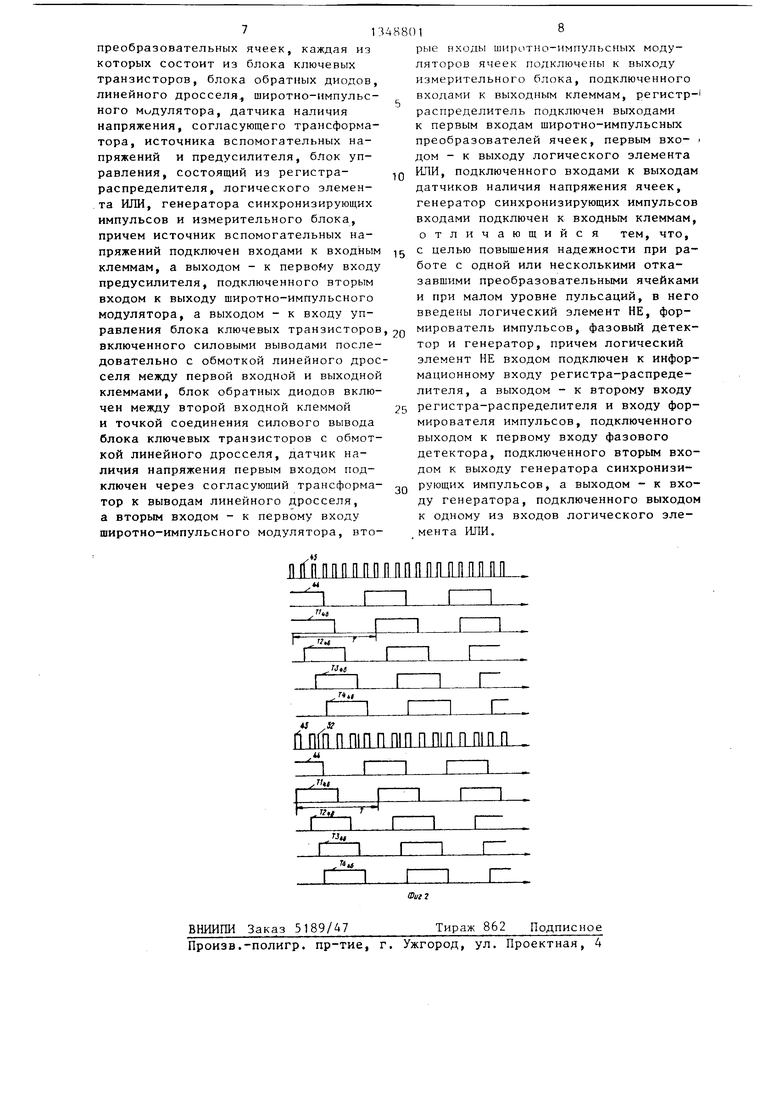

На фиг. 1 представлена электрическая схема многофазного импульсного стабилизатора постоянного напряжения для четырех силовых преобразовательных ячеек (ПЯ)J на фиг. 2 - временные диаграммы напряжений и токов.

Стабилизатор состоит из силовой части и блока управления. Силовая часть стабилизатора выполнена в виде параллельно соединенных ключевых преобразовательных ячеек (ПЯ). Каждая ПЯ состоит (на примере первой), из блока 1 ключевых транзисторов (2, 3, 4 - для второй, третьей, четвертой ячеек соответственно), линейного дросселя 5 (6, 7, 8), блока 9 (10, 11, 12) обратных диодов, предусили- теля 13 (14, 15, 16), источника 17 (18, 19, 20) вспомогательных напряжений, согласующего трансформатора 21 (22, 23, 24), датчика 25 (26, 27, 28) наличия напряжения на обмотке линейного дросселя 5 (6, 7, 8), содержащего (на фиг. 1 раскрыты датчики первой - 25 и второй - 26 ячеек) двухполупериодный выпрямитель 29 (30 - для датчика второй ячейки), стабилизатор 31 напряжения (или 32), элемент НЕ 33 (или 34), элемент И 35 (36) линию 37 задержки (или 38) формирователь 39 коротких импульсов (или 40).

Блок управления состоит из генератора 41 синхронизирующих импульсов, фазового детектора 42, формирователя 43 импульсов, элемента НЕ 44, генератора 45, управляемого напряжением, регистра-распределителя 46, измерительного блока 47, блоков 48- 51 широтно-импульсных модуляторов (для первой и последующих ячеек соответственно) и элемента ИЛИ 52.

Силовая часть ключевой преобразо- ательной ячейки представляет собой однотактный импульсный понижающий

стабилизатор постоянного напряжения компенсационного типа. К обмотке линейного дросселя каждой ячейки, например первой, подключен непосредственно или через согласующий трансформатор 21 выпрямитель 29 со стабилизатором 31 (первый вход датчика 25). Выход стабилиза.тора 31 напряжения через элемент НЕ 33 соединен с одним из входов - элемента И 35, второй вход которого через линию 37 задержки (второй вход датчика 25) соединен с первым выходом регистрараспределителя 43. Выход элемента И 35 через формирователь 39 коротких импульсов (выход датчика 25) соединен с одним из входов элемента ИЛИ 52 блока управления. Генератор

41 синхронизирующих импульсов соеди нен с первым входом фазового детектора 42, выход которого подключен к управляющему входу генератора 45, управляемого напряжением. Выход генератора 45, управляемого напряжением, подсоединен к одному из входов элемента ИЛИ 52, выход которого подключен к синхронизирующему входу регистра-распределителя 46. Выход регистрараспределителя 46 соединен с входом элемента НЕ 44, другой выход которого подключен к выходу генератора 45, управляемого напряжением. Выход элемента не 44 соединен с информационным входом регистра-распределителя 46 и входом формирователя 43 импульсов, выход которого соединен с вторым входом фазового детектора 42.

Работа устройства рассматривается при следующих режимах: запуске, работе стабилизатора с исправными ячейками, работе стабилизатора при отказе одной или нескольких ячеек.

При запуске устройство работает следующим образом.

В исходном состоянии ключевые транзисторы блоков 1-4 закрыты, ток через линейные дроссели 5-8 не протекает, напряжение на их обмотках отсутствует, напряжение на выходе

датчиков 25-28 (напряжение на входе

элемента ИЛИ 52) равно напряжению логического нуля. Действительно, например для датчика 25, входное напряжение элемента НЕ 33 равно нулю. С 5 выхода элемента НЕ 33 на вход элемента И поступает напряжение с уровнем логической единицы. Так как на втором входе элемента И 35 напряжение

равно уровню логического нуля, то напряжение на выходе элемента И 35, а значит, и на соответствующем входе схемы ИЛИ 52 также равно напряжению логического нуля.

При подаче напряжения на генератор 45, управляемый напряжением, последний начинает генерировать импульсы напряжения прямоугольной формы, которые поступают через логический элемент ИЛИ на синхронизирующий вход регистра-распределителя 46. Генератор 41 синхронизирующих импульсов формирует последовательность импульсов, частота следования которых оптимальна для силовых элементов преобразовательной ячейки. Предположим, что в исходном состоянии все триггеры регистра-распределителя 46 находятся в нулевом состоянии. Следовательно, на информационный вход регистра-распределителя 46 с выхода элемента НЕ 44 поступает напряжение логической единицы, которая записываться в каждый последующий триггер регистра-распределителя 46 после каждого импульса на входе синхронизации. Так продолжается до тех пор, пока не изменит своего состояния последний триггер регистра-распределителя 46 (для схемы на фиг. 1 - после четвертого импульса). В этом случае на входе элемента НЕ 44 появляется уровень напряжения логической единицы, а на информационном входе регистра-распределителя - уровень логического нуля. В дальнейщем процесс переключения триггеров регистра распределителя 46 аналогичен рассмотренному.

С выхода элемента НЕ 44 на вход формирователя 43 импульсов поступает напряжение с частотой fw , определяемой количеством триггеров регистра- распределителя 46 и частотой генератора 45, управляемого напряжением: :Е« г,/,н По положительному (отрицательному) перепаду логического уровня в формирователе 43 формируются импульсы (короткие прямоугольные, пилообразные, треугольные - в зависимости от того, какая схема фазового детектора выбрана) и подаются на второй вход фазового детектора 42. На первый вход фазового детектора 42 поступают импульсы с генератора 41 синхронизирующих импульсов. При равенстве частот (с

5

20

8801

точностью до фты) на обоих входах фазового детектора 42 на его выходе под/юрживается постоянное напряжение, являющееся управляющим для генератора, управляемого напряжением, что обеспечивает на выходе постоянную частоту импульсов. В противном случае (при неравенстве частот следоваJQ ния импульсов на входах фазового детектора 42) напряжение на выходе фазового детектора изменяется так, чтобы скомпенсировать фазовый сдвиг. Этот процесс продолжается до уста15 новления частоты fr,,4 с точностью до фазы (здесь f - частота следования импульсов на выходе генератора 41 синхронизирующих импульсов) ,

Импульс напряжения с первого выхода регистра-распределителя 45 одновременно поступает на широтно-им- пульсный модулятор 48 первой ячейки и на второй датчик 25 наличия напря2, жения. Ключевые транзисторы блока 1 открываются, на обмотке линейного дросселя 5 и на нагрузке появляется напряжение. Напряжение, снимаемое с обмотки дросселя 5, выпрямляется

2Q выпрямителем 29, стабилизируется стабилизатором 31 и с уровнем логической единицы поступает на вход элемента НЕ 33. С выхода элемента НЕ 33 на вход элемента И 35 поступает напряжение с уровнем логического нуля. Так как линия 37 задержки сдвигает во времени момент появления импульса регистра, поступающего на элемент И 35 с второго входа датчика 25, то напряжение с уровнем логической единицы поступает на второй вход элемента И 35 уже после того, как на первом входе элемента И 35 появится напряжение логического нуля. Линия 37 задержки, таким образом, обеспечивает на выходе элеме})та И 35 напряжение логического нуля в течение времени переходного процесса при первом включении ключевых транзисторов, препятствуя ложному срабатыванию схемы.

С задержкой на один период частоты генератора, управляемого напряжением, открываются ключевые транзисторы блока 2 второй преобразовательной ячейки, затем с таким же временным сдвигом по отношению один к другому - транзисторы гретым и четвертой преобразовательных ячеек.

35

40

45

50

55

5

Запирание ключевых транзисторов блоков осуществляется широтно-импул ными модуляторами 48-51. Этот проце вызывает изменение полярности напряжения на обмотке линейного дросселя однако изменения сигнала на выходе датчиков 25-28 наличия напряжения не происходит (из-за двухполупериод ного выпрямления), и при условии непрерывности токов линейного дроссел на выходе соответствующего датчика наличия напряжения в течение всего времени исправной работы ячейки обепечивается напряжение с уровнем лог ческого нуля.

Временные диаграммы напряжений и токов при исправных ячейках и устновившемся режиме работы представлены на фиг. 2.

Отказ ячейки, например при коротком замыкании на выходе ПЯ, вызывае срабатывание средств защиты (плавки предохранителей и т.д.) и отключени поврежденной ячейки. При отказе тип обрыв преобразовательная ячейка также отключается.

При отказе одной или нескольких преобразовательных ячеек устройство работает следующим образом.

Предположим, что произошел отказ второй ячейки. Тогда на обмотке линейного дросселя 6 напряжение отсутствует. Напряжение на выходе элемента НЕ 34 равно напряжению логической единицы в течение всего времени работы устройства с отказавшей ячейкой. Импульс напряжения с выхода регистра-распределителя 46 поступает на вход широтно-импульсного модулятора 49 и через линию задержки - на вход элемента И 36. На выходе элемента И 36 появляется напряжение с уровнем логической единицы, существующее в течение всего времени импульса регистра-распределителя 46. Напряжение с выхода элемента И 35 поступает на вход формирователя 40 коротких импульсов. Импульс с выхода формирователя 40 поступает через элемент ИЛИ 52 на синхронизирующий вход регистра-распределителя 46 Внеочередной синхронизирующий импуль изменяет состояние регистра-распределителя 46, и на выходе третьего триггера регистра появляется импульс напряжения, который открывает ключевые транзисторы блока 3 третьей ячейки.

6

Таким образом, вместо отказавшей второй ячейки подключаЕется третья, следующая по счету ячейка. Время задержки подключения третьей ячейки определяется параметрами лиНии 38 задержки, элементов И 36, ИЛИ 49 и формирователя 40 импульсов. Следующий, очередной импульс генератора, управляемого напряжением, переводит регистр в новое состояние. Появляется импульс напряжения на широтно-им- пульсном модуляторе 28 четвертой ячейки, а затем - первой. В дальнейшем процесс повторяется. При равенстве частот следования импульсов генератора 41 синхронизирующих импульсов последнего триггера регистра- распределителя 46 с точностью до фазы в момент, предшествующий отказу,

5

0

5

0

5

0

после появления отказа импульс на выходе последнего разряда регистра- распределителя 46, а значит, а на входе фазового детектора 42 появится с опережением и в дальнейшем частота следования импульсов на втором входе фазового детектора 42 будет вьше частоты генератора 41 синхронизирующих импульсов. Следовательно, на выходе фазового детектора 42 напряжение будет меняться так, чтобы частота следования импульсов на выходе генератора, управляемого напряжением, удовлетворяла соотношению ft,v,u :(п-1), а частота логических перепадов на выходе последнего триггера регистра-распределителя 46 с точностью до фазы равнялась частота генератора синхронизирующих импульсов.

Таким образом, период работы ключевых транзисторов при отказе одной ячейки не изменяется и равен Т/| , где - период следования импульсов генератора 41 синхронизирующих импульсов .

Использование предлагаемого устройства позволит по сравнению с прототипом повысить надежность за счет оптимальных режимов ЭРЭ при постоянной частоте переключения ключевых переключающих ячеек.

Формула изобретения

Многофазный импульсный стабилизатор постоянного напряжения, содержащий силовую часть, выполненную в виде параллельно соединенных ключевых

7i

преобразовательных ячеек, каждая из которых состоит из блока ключевых транзисторов, блока обратных диодов, линейного дросселя, широтно-импульс- ного Модулятора, датчика наличия напряжения, согласующего трансформатора, источника вспомогательных напряжений и предусилителя, блок управления, состоящий из регистра- распределителя, логического элемента ИЛИ, генератора синхронизирующих импульсов и измерительного блока, причем источник вспомогательных напряжений подключен входами к входным клеммам, а выходом - к первому входу предусилителя, подключенного вторым входом к выходу широтно-импульсного модулятора, а выходом - к входу управления блока ключевых транзисторов включенного силовыми выводами последовательно с обмоткой линейного дрос селя между первой входной и выходной клеммами, блок обратных диодов включен между второй входной клеммой и точкой соединения силового вывода блока ключевых транзисторов с обмоткой линейного дросселя, датчик наличия напряжения первым входом подключен через согласующий трансформатор к выводам линейного дросселя, а вторым входом - к первому входу широтно-импульсного модулятора, втод If i п п п п ммймиишж

48801

рые входы широтно-импульсных модуляторов ячеек подключены к выходу измерительного блока, подключенного входами к выходным клеммам, регистр- распределитель подключен выходами к первым входам широтно-импульсных преобразователей ячеек, первым вхо- ; дом - к выходу логического элемента

Q ИЛИ, подключенного входами к выходам датчиков наличия напряжения ячеек, генератор синхронизирующих импульсов входами подключен к входным клеммам, отличающийся тем, что,

1g с целью повышения надежности при работе с одной или несколькими отказавшими преобразовательными ячейками и при малом уровне пульсаций, в него введены логический элемент НЕ, фор- 20 мирователь импульсов, фазовый детектор и генератор, причем логический элемент НЕ входом подключен к информационному входу регистра-распределителя, а выходом - к второму входу

25 регистра-распределителя и входу формирователя импульсов, подключенного выходом к первому входу фазового детектора, подключенного вторым входом к выходу генератора синхронизиgg рующих импульсов, а выходом - к входу генератора, подключенного выходом к одному из входов логического элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизаторпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU824161A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1561068A1 |

| Многофазный импульсный стабилизатор постоянного напряжения (его варианты) | 1984 |

|

SU1157532A1 |

| Многофазный импульсный стабилизатор напряжения | 1986 |

|

SU1390605A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1422223A1 |

| Многофазный импульсный стабилизатор напряжения постоянного тока | 1986 |

|

SU1416957A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1979 |

|

SU855639A1 |

| Многофазный параметрический стабилизатор постоянного напряжения | 1989 |

|

SU1658130A1 |

Изобретение относится к вторичным источникам питания и может быть использовано в системах питания аппярлтуры, требующ(М1 стабилизированного постоянного напряжения с малым )оп.чем амплитуды пульсаций. Цель изоГфетения - повьш1ение надежности п) ныходе ИИ строя одной, двух или н тксльких к.пючепых преобразовательных ячеек и малом уровне амплитудных пульсаций . С этой целью в устройство пш дея, логически) элемент НЕ 33, формирс ватель импульсов 43, генератор 45 и фазовый детектор 42. Пред- :ui i- HiKie техническое решение обеспечивает постоянную частоту переключении ключевь х перек.1 ючающих ячеек, НС чанисящую от числа исправных пе- pt к, 1ючак1щих ячеек. Это обеспечивает 1иггимлти,нь:е режимы работы элементов. При ;1тказе неисправная ячейка отклю- ЧЛ1 п я, л взамен подключается следу- юшля по счету ячейка. Период работы к.пк1чер1ых транзисторов 2 при отказе ячеики не изменяется и равен периоду следования импульсов генератора синхронизирующих импульсов 41. 2 ил. (Л со 4 СХ) 00

rjtl

Jltl

4J ,Д

|1ПГППП1ППП1ППП1ППП1ПП .

Ш

г .

тг

ВНИИПИ Заказ 5189/47

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Тираж 862 Подписное

| Элементарная техника в автоматике./Под ред | |||

| Ю.И | |||

| Конева, А.И | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | |||

| М.: Советское: радио, 1978, вып | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Счетный сектор | 1919 |

|

SU107A1 |

| Многофазный импульсный стабилизаторпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU824161A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-10-30—Публикация

1985-10-28—Подача