1

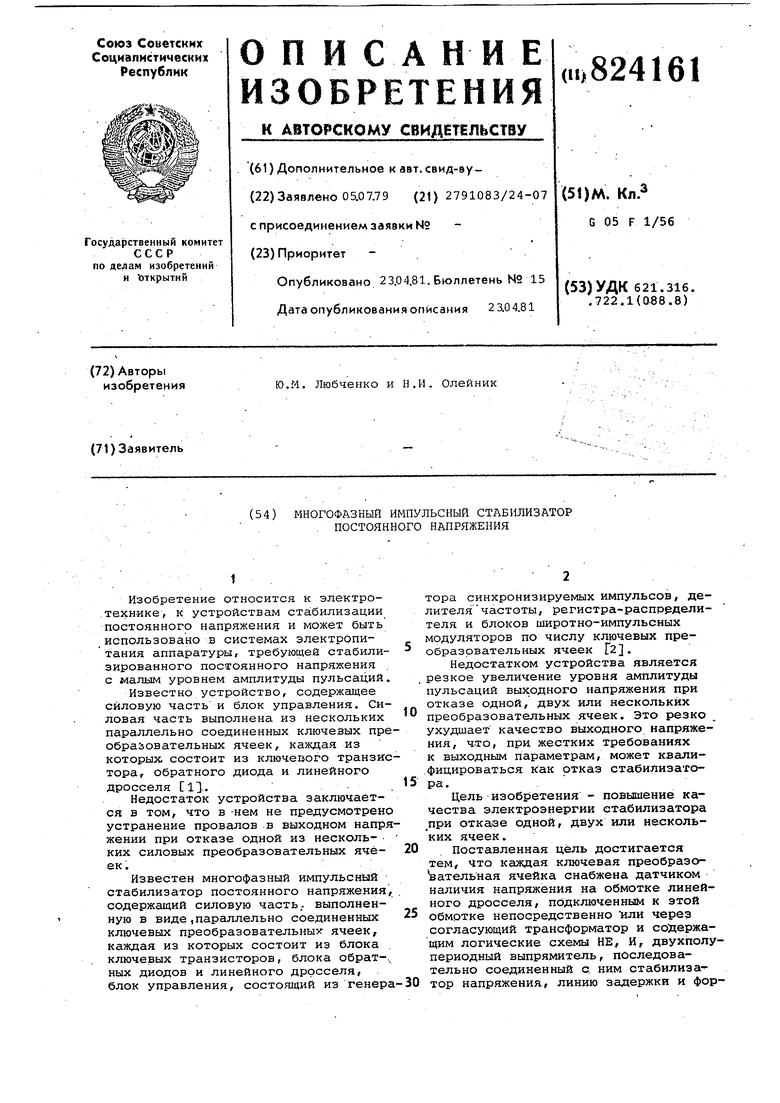

Изобретение относится к электро,технике, к устройствам стабилизации постоянного напряжения и может быть использовано в системах электропитания аппаратуры, требующей стабилизированного постоянного напряжения . с малым уровнем амплитуды пульсаций.

Известно устройство, содержащее силовую часть и блок управления. Силовая часть выполнена из нескольких параллельно соединенных ключевых преобразовательных ячеек, каждая из которых, состоит из ключевого транзистора , обратного диода и линейного

дрооселя 1,.

Недостаток устройства заключается в том, что в -нем не предусмотрено устранение провалов в выходном напряжении при отказе одной из несколь- ких силовых преобразовательных ячеек .

Известен многофазный импульсный стабилизатор постоянного напряжения, содержащий силовую часть,- выполненную в виде)параллельно соединенных ключевых преобразовательны ячеек, каждая из которых состоит из блока . ключевых транзисторов, блока обрат-., ных диодов и линейного дросселя, блок управления, состоящий из генератора синхронизируемых импульсов, делителя частоты, регистра-распределителя и блоков широтно-импульсных модуляторов по числу ключевых преобразовательных ячеек Г2.

Недостатком устройства является резкое увеличение уровня амплитуды пульсаций выходного напряжения при отказе одной, двух или нескольких

0 преобразовательных ячеек. Это резко ухудшает качество выходного напряжения, что, при жестких требованиях к выходным параметрс1М, может квалифицироваться как отказ стабилизатора.

Цель изобретения - повышение качества электроэнергии стабилизатора при отказе одной, двух или нескольких ячеек.

0

Поставленная цель достигается тем, что каждая ключевая преобраэо вательная ячейка снабжена датчиком наличия напряжения на обмотке линейного дросселя, подключенным к этой

5 обмотке непосредственно или через согласующий трансформатор и содержащим логические схемы НЕ, И, двухполупериодный выпрямитель, последовательно соединенный с. ним отабилиза0 тор напряжения, линию задержки и формировательКОРОТ.КИХ импульсов, в блок управления введена логическая схема ИЛИ, причем выход генератора синхронизирукяцих импульсов соединен . с одним из входов логической схемы ИЛИ, выход стабилизатора напряжения через логическую схему ИЛИ подключен к одирму из входов И, второй вход которой через линию задержки содинен с соответствующим выводом регитра-распределителя, -а выход через формирова тель коротких импульсов с одним из входов схемы ИЛИ, выход которой подключен к входу регистрараспределителя .

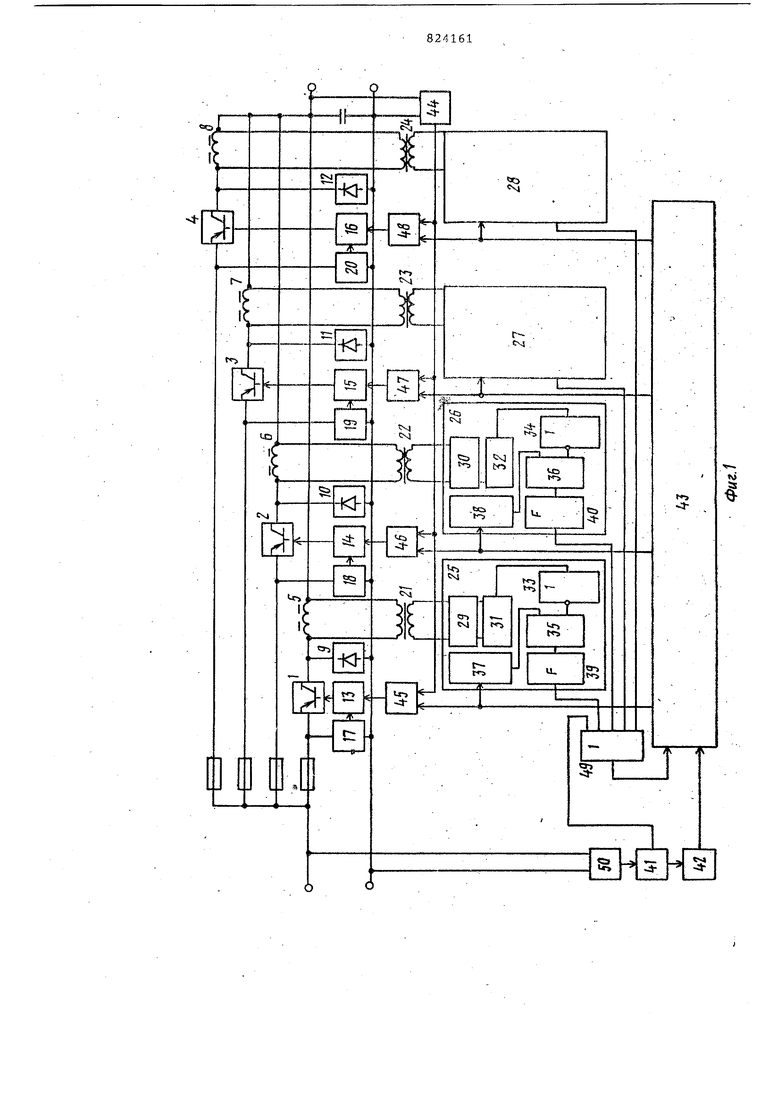

На фиг. 1 представлена электрическая схема стабилизатора, для четырех силовых преобразовательных ячеек, на фиг. 2 - временные диаграммы напряжений и токов.

Стабилизатор содержит силовую часть и блок управления. Силовая часть стабилизатора выполнена в виде параллельно соединенных ключевых преобразовательных ячеек. Каждая ячейка состоит из блока ключевых транзисторов 1 - для блока первой ячейки (2, 3 и 4 - для блоков второй третьей, четвертой ячеек, соответственно) , линейного дросселя 5 (б, 7 и 8 - для второй и последующих ячеек, соответственно), блока обратных диодов 9 (10, 11 и 12 - для блоков второй и последующих ячеек, соответственно), предусилителя 13 (14, 15 и 16 - для-блоков второй и последукедих ячеек, соответственно) источника вспомогательных 17 напряжений (18, 19 и 20 - для второй и последующих ячеек, соответственно), согласукицего трансфору;атора 21 (22, 23 К 24), Датчика наличия напряжения 2 (26, 27 и 28) на обмотке линейного дросселя, содержащего (на фиг. 1 раскрыты датчики первой - 25 и второй - 26 ячеек) двухполупериодный выпрямитель 29 (30 - для датчика второй ячейки), стабилизатор напряжения 31 (или 32), логическую схему НЕ 33 (или 34), логическую схему И 3 (или 36), линии задержки 37, 38, формирователь коротких импульсов 39 (или 40) .

Блок управления состоит из генератора 41 синхронизируюлшх импульсов, делителя 42 частоты/ регистра - распределителя 43, измерительного устройства 44, блоков 45-48 широтноимпульсных модуляторов (для первой и последующих ячеек, соответственно) югической схемы ИЛИ 49 и источника вспомогательных напряжений 50 блока управления.

Силовая часть ключевой преобразовательной ячейки представляет собой однотактный импульсный понижающий стабилизатор постоянного напряжения компенсационного типа. К обмотке линейного дросселя каждой ячейки ,

например, первой, подключен непосредственно или через согласующий трансформатор 21 выпрямитель 29 qo стабилизатором напряжения 31 (первы вход датчика 25). Выход стабилизатора напряжения 31 через логическую схему НЕ 33 соединен с одним из входов схемы И 35, второй вход которой через линию задержки 37 (второй вхо датчика 25) соединен с первым выходом регистра-распределителя 4 3. Выход схемы И 35 через формировател коротких импульсов 39 (выход датчика 25)соединен с одним из п+1 входов логической схемы ИЛИ 49 блока управления. Генератор синхронизирующих импульсов 41 соединен одним выходом через делитель частоты 42 с сигнальным (информационным) входом регистра 43, а вторым - с входом логической схемы ИЛИ 49, выход которой подключен к синхронизирующему входу регистра 43.

Работа устройства рассматривается при следующих режимах: режим запука и работы стабилизатора с исправными ячейками; режим работы стабилизатора при отказе одной или нескольких ячеек.

В режиме запуска устройство работает следующим образом.

В исходном состоянии ключевые транзисторы блоков 1, 2, 3, 4 закрыты, ток через линейные дроссели .5, 6, 7, 8 не протекает, напряжение на их обмотках отсутствует. Напряжение на выходе датчиков 25, 26, 27, 28 (напряжение на входе схемы ИЛИ 49) равно напряжению логического нуля. Действительно, например, для датчика 25, входное напряжение схемы НЕ 33 равно нулю. С выхода схемы НЕ 33 на вход схемы И поступает напряжение с уровнем логической единицы. Так как на втором входе схемы И 35 напрялсение равно уровню напряжения логического нуля, то напряжение на выходе схемы И 35, а значит и на соответствующем входе схемы ИЛИ 49 также равно напряжению логического нуля.

При подаче напряжения на генератор синхронизирующих импульсов 41 последний начинает генерировать импульсы напряжения прямоугольной формы, которые поступают на вход делителя частоты 42 и через логическую схему ИЛИ 49 на синхронизирующий вход регистра 43. Делитель частоты 42 формирует выходное напряжение, период следования импульсов которого в 2 раз больше периода изменения выходного напряжения генератора синхронизирующих импульсов, где m количество Т-триггеров делителя (для рассматриваемой схемы m 2, период выходного напряжения делителя частоты в четыре раза больше периода синхронизирующих импульсов).

Следовательно, на сигнальный вход регистра 13 поступает напряжение: период следования импульсов которого в четыре раза больше периода импульсов на синхронизирующем входе. Регистр 43 представляет собой обычный сдвиговый регистр, выполненный на п синхронных- К5- риггерах, состояние которого меняется после окончания каждого синхронизирующего импульса.

Импульс напряжения с первого выхода регистра одновременно поступает на широтно-импульсный модулятор 45 первой ячейки и на второй вход датчика наличия напряжения 25. Ключевые транзисторы блока 1 открываются, на обмотке линейного дросселя 5 и на нагрузке появляется напряжение.

Напряжение, снимаемое с обмотки дросселя 5., выпрямляется вы.прямителем 29 и стабилизируется стабилизатором 31 и с уровнем логической единицы поступает на вход схемы НЕ. 33. С выхода схемы НЕ 33 на вход схемы И 35 поступает напряжение с уровнем логического нуля. Так как линия задержки 37 сдвигает по времени момент появления импульса регистра, поступающего на схему И 35 со второго входа датчика 25, то напряжение с уровнем логической единицы поступает на второй вход схемы И 35 уже после того, как на первом входе схемы И 35 появится напряжение логического нуля. Линия задержки 37, таким образом, обеспечивает на вы-. ходе схемы И 35 напряжение логического нуля в течение времени переходного процесса при первом включении ключевых транзисторов, препятствуя ложному срабатыванию схемы.

Черед период времени Т/п открываются ключевые транзисторы- блока 2 второй преобразовательной ячейки завем с таким же временным сдвигом по отношению друг кдругу открываются транзисторы третьей и четвертой преобразовательных ячеек.

Закрытие ключевых транзисторов блоков осуществляется с временным сдвигом .Т/п широтно-импульсными модуляторами 45, 46, 47, 48. Закрытие транзисторов вызывает изменение полярности напряжения на обмотках линейного дросселя. Однако изменения сигнала на выходе датчиков наличия напряжения 25, 26, 27, 28 не происходит (из-за двухполупериодного выпрямления) и при условии непрерывности .токов линейного дросселя на выходе соответствующего датчика наличия напряжения в течение всего времени исправной работы ячейки обеспечивается напряжение с уровнем логического нуля.

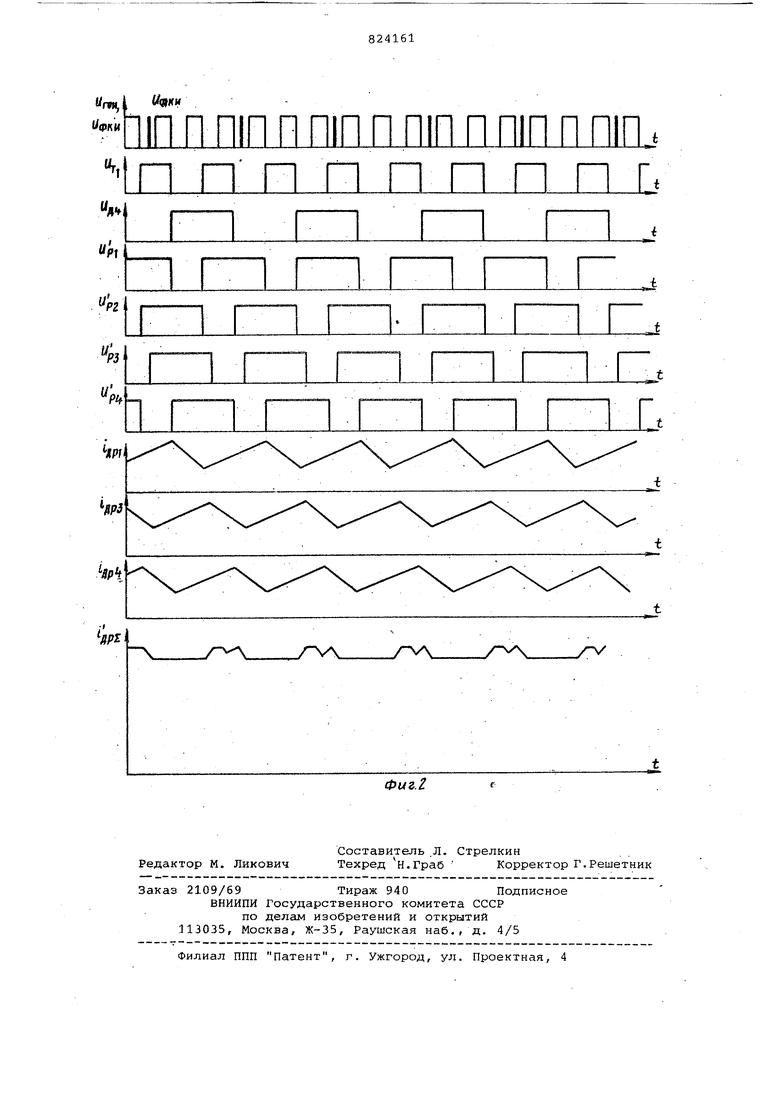

Временные диаграммы напряжений и токов при исправных ячейках и

установившемся режиме работы не отличаются от соответствующих временных диаграмм для,схемы прототипа, которые представлены на фиг. 2.

Отказ ячейки, например, короткое 3aNibiKaHHe, вызывает срабатывание средств защиты (например, плавких предохранителей) и отключение поврежденной ячейки. -При отказе типа обрыв преобразовательная ячейка также отключается.

0

При отказе одной или нескольких преобразовательных ячеек устройство работает следующим образом. Предположим, что произошел отказ второй ячейки. Тогда на обмотке линейного

5 дросселя 6 напряжение отсутствует. Напряжение на выходе логической схемы НЕ 34 равно напряжению логической единицы в течение всего времени работы устройства с отказавшей

0 ячейкой. Импульс напряжения с выхода регистра 43 поступает на вход широтно-импульсного модулятора 46 и через линию задержки на вход логической схемы И 36. На выходе логической схемы И 36 появляется напряже- . ние с уровнем логической единицы, существующее в течение всего времени импульса регистра - распределителя. Напряжение с выхода логической схемы И 35 поступает на входоформи0рователя коротких импульсов 40. Импульс кратковременной длительности с выхода формирователя 40 поступает через логическую схему ИЛИ 49 на синхронизирующий вход регистра-расп5ределителя 43. Внеочередной синхронизирующий импульс изменяет состояние регистра 43 и на выходе третьего триггера регистра появляется импульс напряжения, который открывает ключе0вые транзисторы блока 3 третьей ячейки.

Таким образом, вместо отказавшей второй ячейки подключается третья, следующая по счету/ ячейка. Время задержки подключения третьей ячейки

5 определяется параметрами линии задержки 38, схем И 36, ИЛИ 49 и формирователя импульсов 40. Следующий, очередной, импульс синхронизирующего генератора переводит регистр в новое

0 состояние. Появляется импульс напряжения на широтно-импульсном молудяторе 28 четвертой ячейки, а затем на первой. В дальнейшем процесс работы повторяется.

5

Период времени работы ключевых транзисторов при отказе одной ячейки изменяется и становится равным Т (п-1)п.

Широтно-импульсные модуляторы исправных ячеек (45, 47, 48) изменя0ют относительное время открытого состояния ключевых транзисторов таким образом, чтобы восстановить . уровень стабилизированного напряже5ния. На фиг. 2 представлены временные диаграилмы напряжений и токов устрой ства при отказе одной ячейки, напри мер, второй где Uj-си напряжение на выходе генератора синхронизирующи;с импульсов, ифки - напряжение на выходе формирователя ..коротких импул сов, UT - выходное напряжение первого триггера делителя частоты, .выходное напряжение второго триггера делителя (выходное напряже ние делителя частоты), Up U} , ирз РА напряжение на первом, втором, третьем, четвертом выходах регистра при отказе одной ячейки, AJ, f АР5 ок, протекакж.ий через первый, трет.ий, четвертый линейные дроссели, соответственно, при отказе одной ячейки, ivvp - сум марный ток при отказе ячейки. При выходе из строя еще одной ячейки, например, третьей, вместо второй и третьей ячеек подключается соответственно, четвертая и первая. Несмотря на то, что время задержки подключения четвертой ячейки в этом случае увеличивается, величина ампл туды пульсаций выходного напряжения значительно меньше амплитуды пульс ций при отказе двух ячеек из четырех- по сравнению с устройством, выполненным по схеме прототипа. Период работы ключевых транзисто ров при выходе ячеек из строя в общем случае равен Т(п-К)/п, где К количество отказавших ячеек. Эффект от использования предложенного устройства оценивается снижением амплитуды пульсаций по сравнению с и;с крОвнем в существующих устройствах при отка преобразовательных ячеек. Q Эффект возрастает по мере увеличения числа отказавших ячеек. Таким образом, предлагаемый стабилизатор позволяют уменьшить величину амплитуды пульсаций выходного напряжения при отказе одной, двух и более ячеек и тем самым улучшить качество напряжения, что особенно важно при питании потребителей, тре бующих напряжения с Малыми допустимыми величинами амплитуды пульсаций Формула изобретения : Многофазный импульсный стабилиза Tqp постоянного напряжения, содержа щий силовую часть, выполненную в виде параллельно соединенных ключевых преобразовательных ячеек, каждая из которых состоит из блока, ключевых транзисторов, блока обратных диодов и линейного дросселя,и блок управления, состоящий из генератора синхронизирующих импульсов, делителя частоты, регистра-распределителя и блоков широтно-импульсных модуляторов по числу ключевых преобразовательных ячеек, .отличающийся тем, .что, с целью повышения качества электроэнергии стабилизатора при отказе одной, двух или нескольких преобразовательных ячеек, каждая ключевая преобразовательная..ячейка снабжена датчиком наличия напряжения на обмотке линейного дросселя, подключенным к этой обмотке непосредственно или через согласующий трансформатор и содержащим логические схемы НЕ, И, двухполупериодный выпрямитель, последовательно соединенный с ним стабилизатор напряжения, линию задержки и формирователь корот-ких импульсов, в блок управления введена логическая схема ИЛИ, причем выход генератора синхронизирующих импульсов соединен с одним из входов логической схемы- ИЛИ, выход стабилизатора напряжения каждой преобразовательной ячейки через логическую схему НЕ подключен к одмому из входов схемы И, второй вход которой через линию задержки соединен с соответствующим выходом регистра-распределителя, а выход через формирователь коротких импульсов - с. одним из входов схемы или, выход которой подключен к входу регистра-распределителя. Источники информации, ринятые во внимание при экспертизе 1.Авторское свидетельство СССР 327462, кл. G 05 F1/56, 1972. 2.Юрченко А.И. и др. Многофазый импульсный стабилизатор постояного напряясения.. - Электронная техика в ав.томатике Под ред. Ю.И. Коева. М., Советск ое радио, 1978, ып. 10, с. 107-113. (рис. 1, стр. 09, рис. 2, с. 1-11) ,

1П П П1П П П1П П П1П П П1П П П1П .

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор постоянного напряжения | 1985 |

|

SU1348801A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Многофазный импульсный стабилизатор постоянного напряжения (его варианты) | 1984 |

|

SU1157532A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1561068A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1422223A1 |

| Многофазный импульсный стабилизатор напряжения | 1986 |

|

SU1390605A1 |

| Многофазный параметрический стабилизатор постоянного напряжения | 1989 |

|

SU1658130A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1979 |

|

SU855639A1 |

| Многофазный импульсный стабилизатор напряжения постоянного тока | 1986 |

|

SU1416957A1 |

ЯP

yvv

-Л.

У

yv

Авторы

Даты

1981-04-23—Публикация

1979-07-05—Подача