:л

со

00

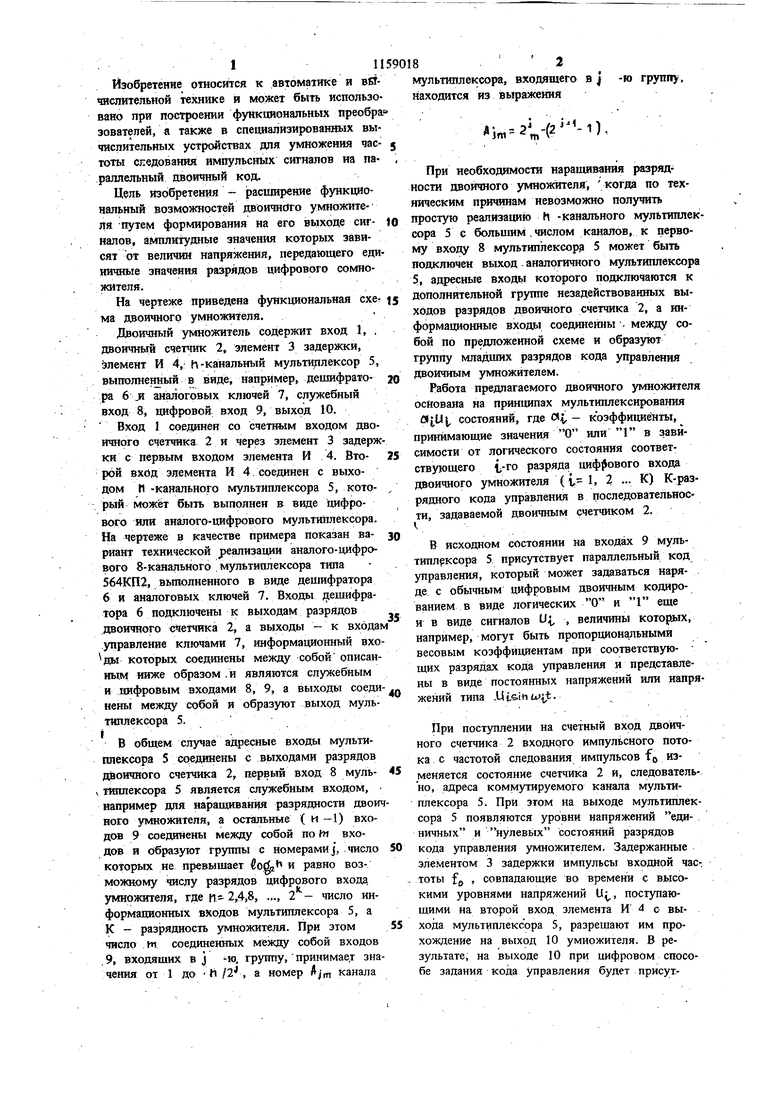

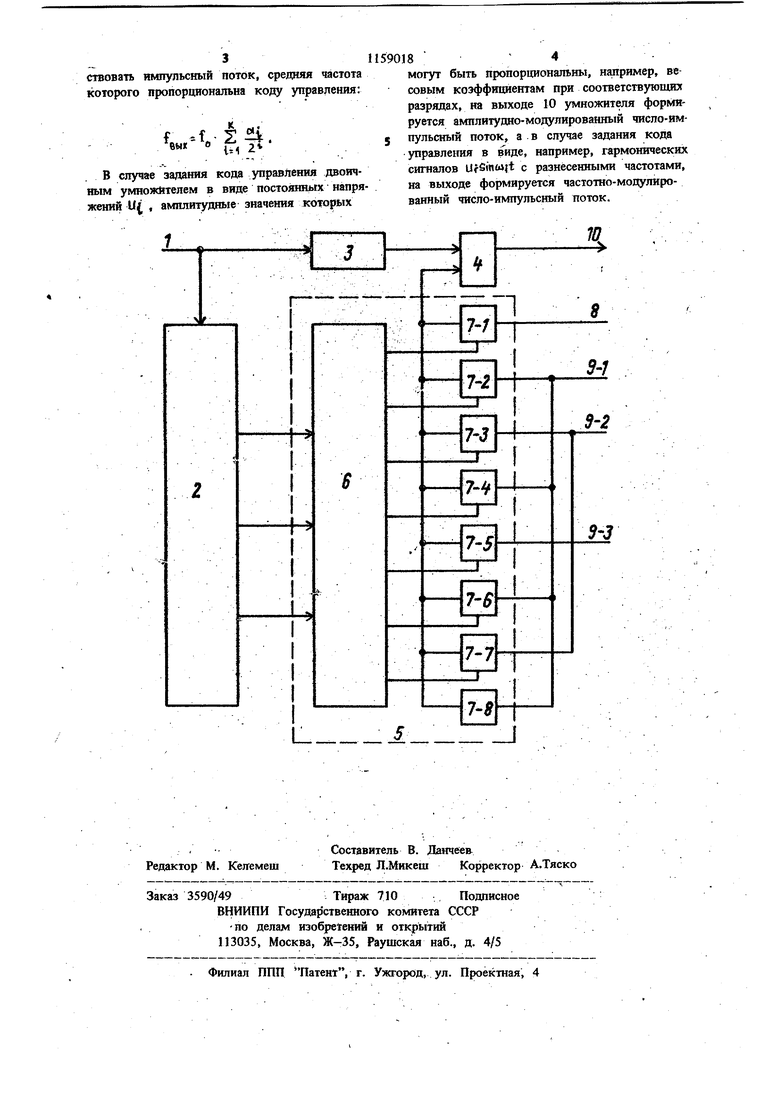

Изобретение относится к автоматике и sSf числительной технике и может быть использо вано при построении функциональных преобр эователей, а также в специализированных вы числительных устройствах для умножения час тоты скедованяя импульсных сигналов на параллельный двоичный код. Цель изобретения - расширение функциональный возможностей двоичного умножителя путем формирования на его выходе сигналов, амплитудные значения которых зависят от величин напряжения, передающего еди ничные значения разрядов цифрового сомножителя. На чертеже приведена функциональная схе ма двоичного умножителя. Двоичный умножитель содержит вход 1, , двоичный счетчик 2, элемент 3 задержки, элемент И 4, h-канальный мультиплексор 5, выполненный в виде, например, дешифратора 6л аналоговых ключей 7, служебный вход 8, цифровой вход 9, выход 10. Вход 1 соединен со счетным входом двоичного счетчика 2 и через злемент 3 задерж ки с первым входом элемента И 4. Второй вхйд элемента И 4 соединен с выходом И-канального мультиплексора 5, который может быть выполнен в виде цифрового или аналого-цифрового мультиплексора. На чертеже в качестве примера показан вариант технической реализации аналого-цифрового 8-канального мультиплексора типа 564КП2, вьпюлненного в виде дешифратора 6 и аналоговых ключей 7. Входы ; ешифратора 6 подключены к выходам разрядов двоичного счетчика 2, а выходы - к входам .управление ключами 7, информационный вхоWi которых соединены между собой описанньхм ниже образом .и являются служебным и цифровым входами 8, 9, а выходы соединены между собой и образуют выход мультиплексора 5. В общем случае адресные входы мультиплексора 5 соединены с выходами разрядов двоичного счетчика 2, первый вход 8 мульV пншексора 5 является служебным входом, например для наращивания разрядности двоич ного умножителя, а остальные { и -1) входов 9 соединены между собой по Ж входов и образуют группы с номерами, число которых не превыщает odz и равно возможному числу разрядов цифрового входа умножителя, где п-2,4,8, ..., число информационных вкодов мультиплексора 5, а К - разрядность умножителя. При этом число т соединенных между собой входов 9, входящих в j -ю, группу, принимает значения от 1 до h /2 , а номер А;щ канала мультиплексора, входящего в| -ю группу, находится из выражения (, При необходимости наращивания разрядности двоичного умножителя, когда по техническим причинам невозможно получить простую реализацию h -канального мультиплексора 5 с большим. числом каналов, к первому входу 8 мультиплексора 5 может быть подключен выход аналогичного мультиплексора 5, адресные BXOJU I которого подключаются к дополнительной группе незадействованных выходов разрядов двоичного счетчика 2, а информационные соединенны - между собой по предложенной схеме и образуют группу младших разрядов кода управления двоичным ут шожйтелем. работа предлагаемого двоичного умножителя основала на пртнхшпах мультиплексирования состояний, где с«(, - коэффшдае 1ты, принимающие значения О или 1 в зависимости от логического состояния соответствующего ii-ro разряда цифрового входа двоичного умножителя (i 1, 2 ... К) К-разрядного кода управления в гюследовательности, задаваемой двоичным счетчиком 2. В исходном состоянии на входах 9 мультиплрксора 5 присутствует параллельный код управления, который может задаваться наряде с обычным цифровым двоичным кодированием в виде логических О и 1 еще и в виде сигналов U|, , величины KOTOpwx, например, могут быть пропорциональными весовым коэффициентам при соответствую- щих разрядах кода управления и представлены в вИде постоянных напряжений или напряжений типа .Ц te-iti . При поступлении на счетный вход двоичного счетчика 2 входного импульсного потока с частотой следования импульсов f изменяется состояние счетчика 2 и, следовательно, адреса коммутируемого канала мультиплексора 5. При этом на выходе мультиплексора 5 появляются уровни напряжений еда- . ничных и нулевь1х состояний разрядов кода управления умножителем. Задержанные элементом 3 задержки импульсы входной час: тоты f(, , совпадающие во времени с высокими уровнями напряжений U, поступающими на второй вход элемента И 4 с выхода мультиплексора 5, разрешают им прохождение на выход 10 умножителя. В результате, на выходе 10 при цифровом способе задания кода управления будет присутствовать импульсный поток, средняя частота которого пропорциональна коду управления: 2. еы в В случае задания кода управления двоичным умножителем в виде постоянных напряжений U( , амплитудные значення которых могут быть пропорциональны, например, весовым коэффициентам при соответствующие разрядах, на выходе 10 умножителя формируется амплитудно-модулированный число-импульсный поток, а в случае задания кода управления в виде, например, гармонических сигналов UfSinoijt с разнесенными частотами, на выходе формируется частотно-модулированный число-импульсный поток.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Преобразователь кода в частоту | 2023 |

|

RU2805259C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2005 |

|

RU2285946C1 |

| Цифровой функциональный преобразователь | 1988 |

|

SU1543401A1 |

| Устройство для измерения расстояния | 1984 |

|

SU1219922A1 |

| НЕЙРОСЕТЕВОЙ ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2008 |

|

RU2380752C2 |

| ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА | 1991 |

|

RU2050585C1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Коммутирующее устройство | 1986 |

|

SU1510075A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

тОКЧвЬ УШОтПЪПЬ, содеряящий двсжчный счетчик, элемент И и эяеъ/кюг задержки, вход которого соединен с входом счетчика и входом двоичного умяожйтеля, в выход - с пе{жым входом зяемепта И, о т л и ч а lof щ и и с я ВСЕСОЮЗНАЯ -и 13 TElHfiqtaig ВЙЙЛ ОТЁЙА 1«Ч ОМЖм„г «ijnacRwsi-iSXirB тем, что, с целью расширения функщюнальиых возможностей путем формирования сигналов, амш1итуднь1е значения которых зависят от величин напряжения, передающего единичные значения разрядов входа цифрового сомножителя, в него введен п- канальный мультиплексор, адресные входы которого соединены с выходами paspjfaoB двоичного счетчика, выход соединен с вторым входом элемента И, первый информационный вход мультиплексора соединен со служебным входом умножителя, а остальные fi -1 информационных входов Мультиплексора соеданеиы с входами разрядов цифрового входа двоичного умножителя таким образом, что вход i-то разряда щ|фрового / 1воичмого умножителя соединен с

,А

| - Спраиочник по шпеграпьиым микросхемам | |||

| Под ред | |||

| Б | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Тарабрина, М.: Энергия 1980, с | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

| : Пиеот США № 3414720, кл | |||

| , 1974. | |||

Авторы

Даты

1985-05-30—Публикация

1983-12-05—Подача