I

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах.

Цель изобретения - повышение быстродействия устройства.

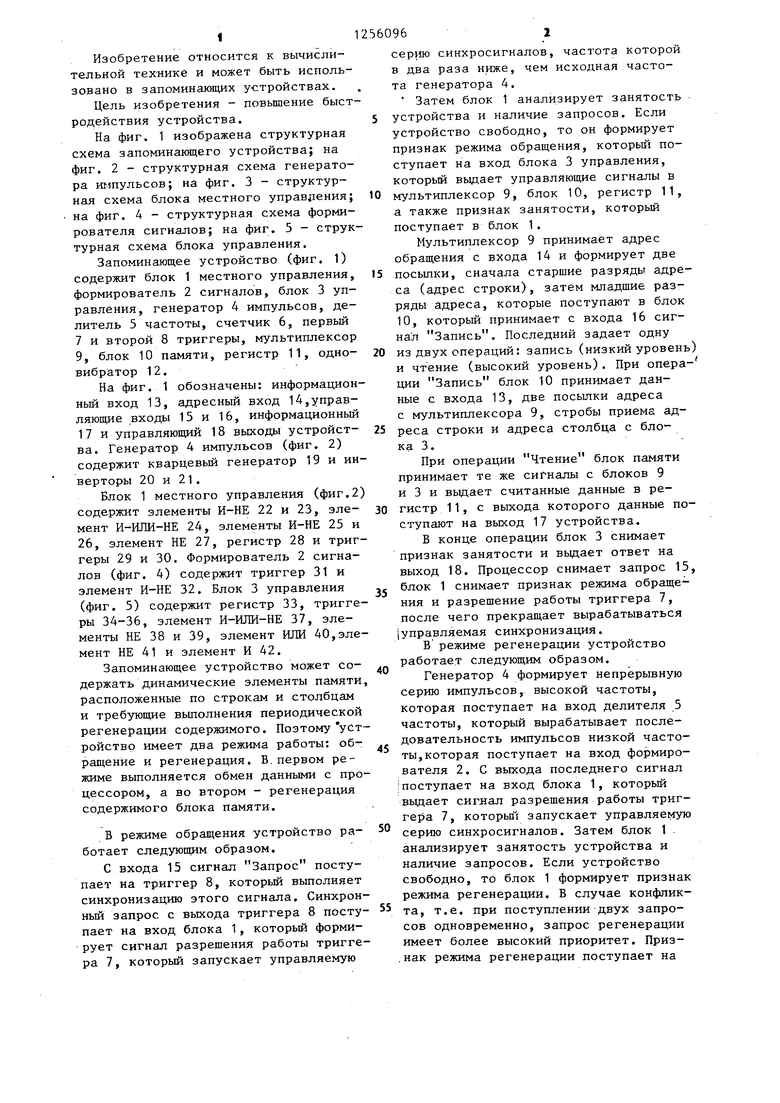

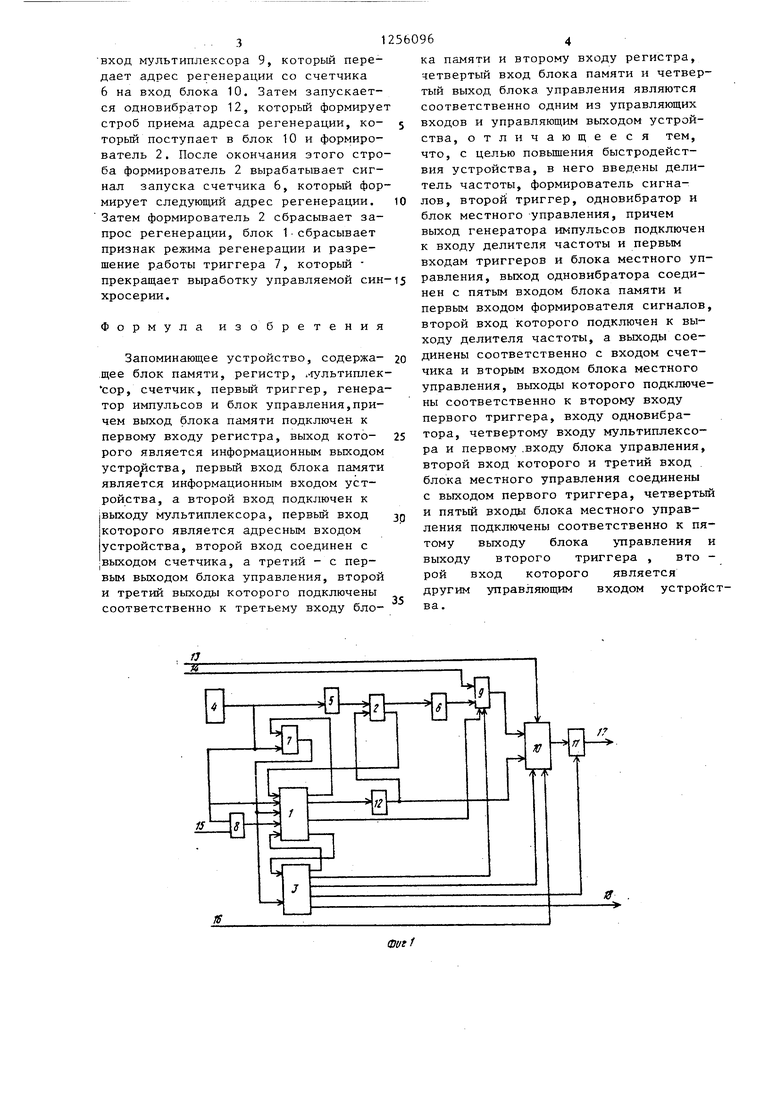

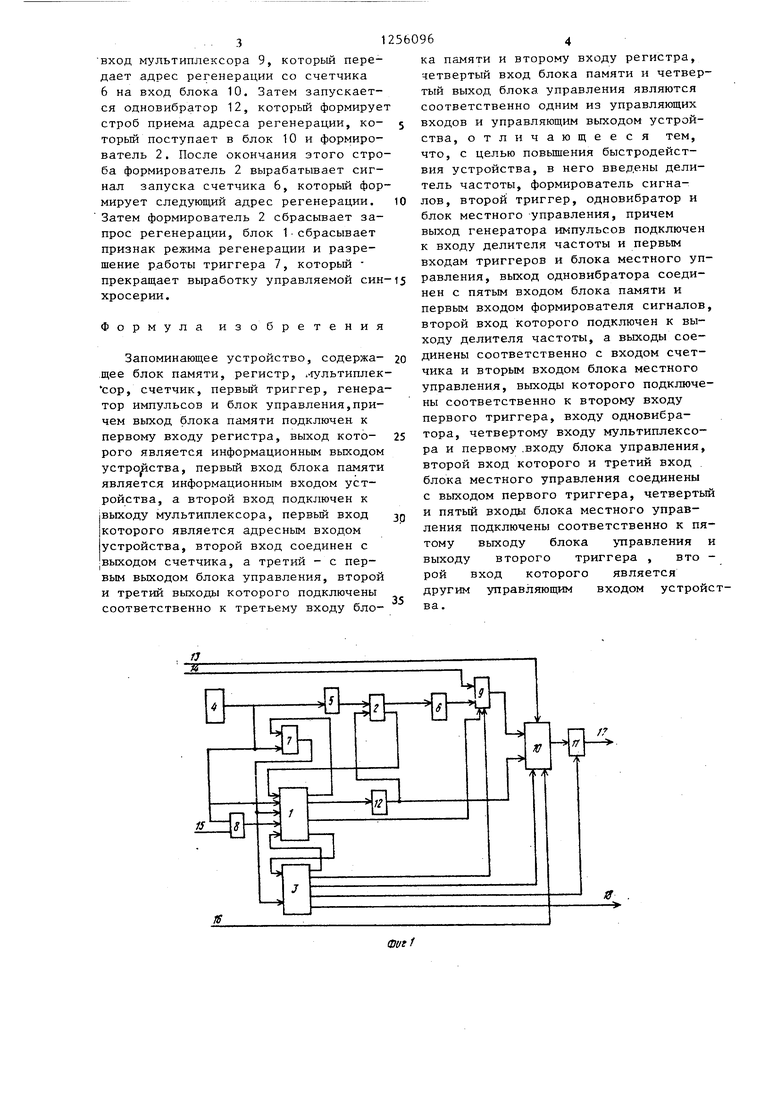

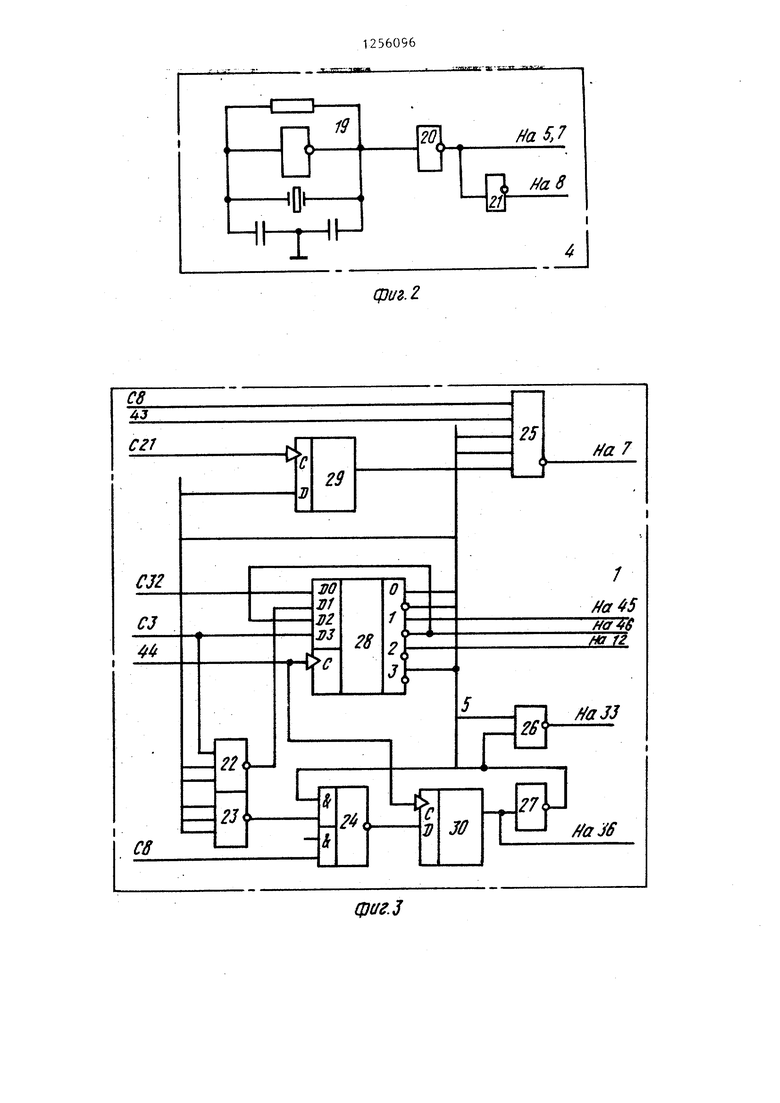

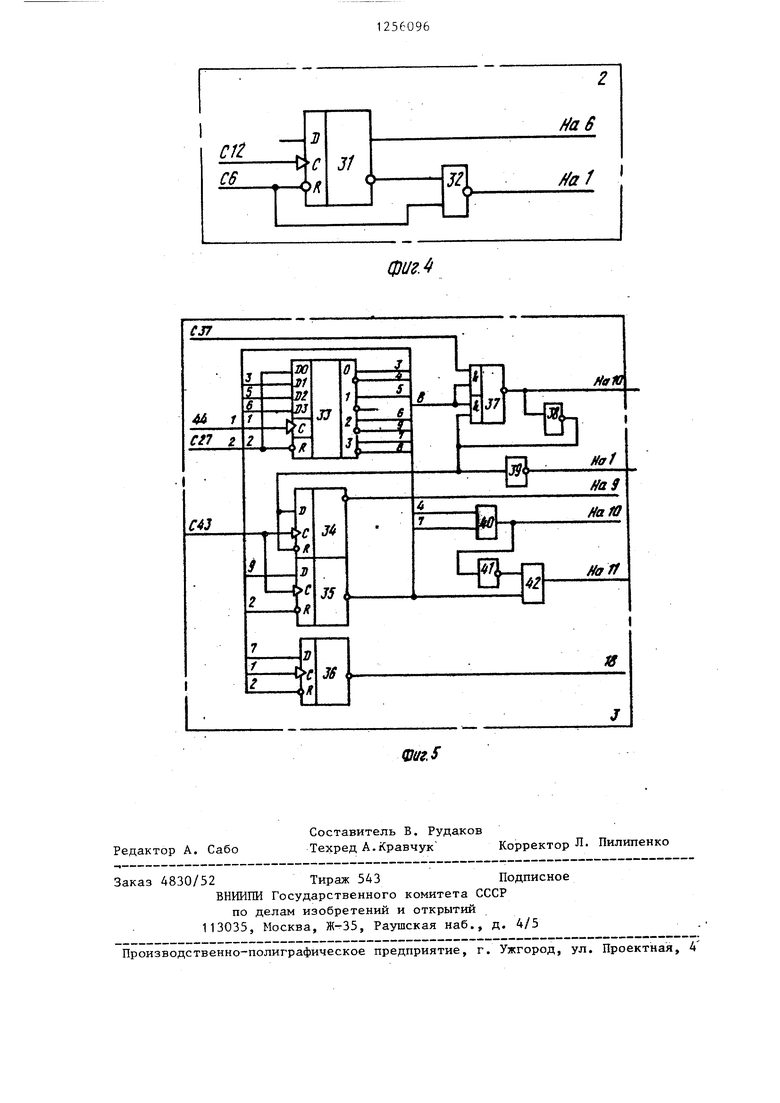

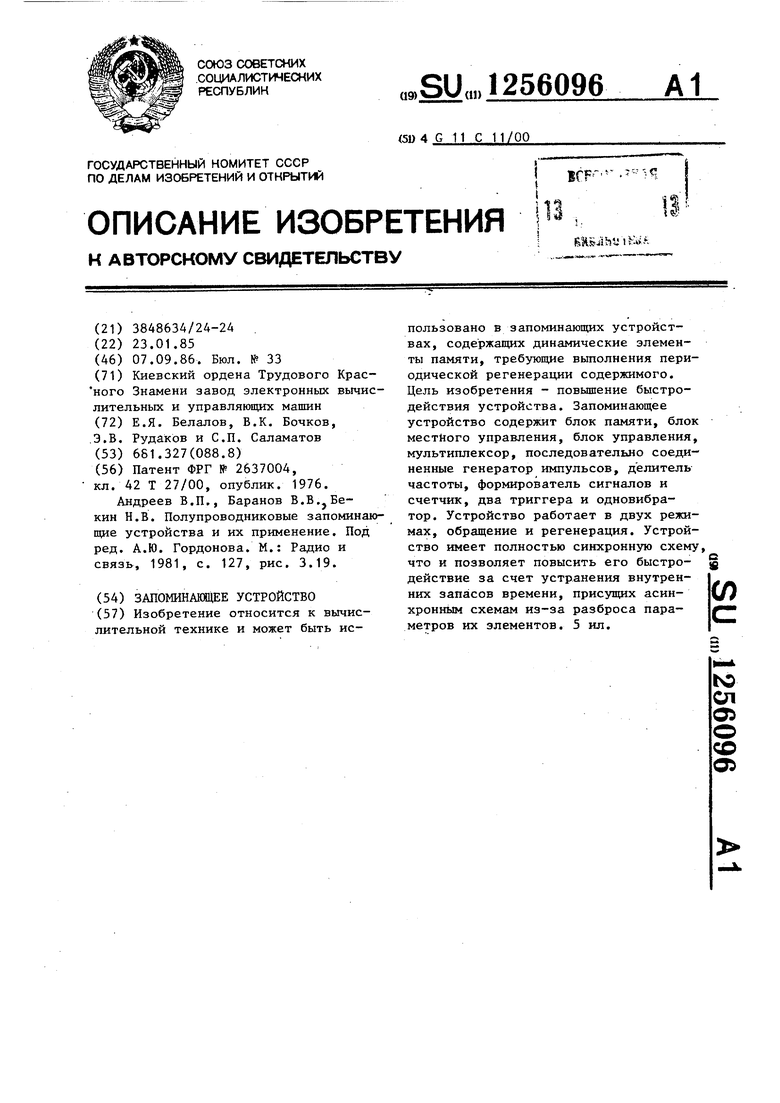

На фиг. 1 изображена структурная схема запоминающего устройства; на фиг. 2 - структурная схема генератора импульсов; на фиг. 3 - структурная схема блока местного управления; на фиг. 4 - структурная схема формирователя сигналов; на фиг. 5 - структурная схема блока управления.

Запоминающее устройство (фиг. 1) содержит блок 1 местного управления, формирователь 2 сигналов, блок 3 управления, генератор 4 импульсов, делитель 5 частоты, счетчик 6, первый 7 и второй 8 триггеры, мультиплексор 9, блок 10 памяти, регистр 11, одно- вибратор 12.

На фиг. 1 обозначены: информационный вход 13, адресный вход 14,управляющие входы 15 и 16, информационный 17 и управляющий 18 выходы устройства. Генератор 4 импульсов (фиг. 2) содержит кварцевый генератор 19 и инверторы 20 и 21.

Блок 1 местного управления (фиг.2 содержит элементы И-НЕ 22 и 23, элемент И-ИЛИ-НЕ 24, элементы И-НЕ 25 и 26, элемент НЕ 27, регистр 28 и триггеры 29 и 30. Формирователь 2 сигналов (фиг. 4) содержит триггер 31 и элемент И-НЕ 32. Блок 3 управления (фиг. 5) содержит регистр 33, триггеры 34-36, элемент И-ИЛИ-НЕ 37, элементы НЕ 38 и 39, элемент ИЛИ 40,элемент НЕ 41 и элемент И 42.

Запоминающее устройство может содержать динамические элементы памяти расположенные по строкам и столбцам и требующие вьшолнення периодической регенерации содержимого. Поэтому у т ройствр имеет два режима работы: обращение и регенерация. В. первом режиме выполняется обмен данными с процессором, а во втором - регенерация содержимого блока памяти.

В режиме обращения устройство работает следуюш 1М образом.

С входа 15 сигнал Запрос поступает на триггер 8, который выполняет синхронизацию этого сигнала. Синхронный запрос с выхода триггера 8 поступает на вход блока 1, который формирует сигнал разрешения работы триггера 7, который запускает управляемую

серию синхросигналов, частота которой в два раза ниже, чем исходная частота генератора 4.

Затем блок 1 анализирует занятость устройства и наличие запросов. Если устройство свободно, то он формирует признак режима обращения, который поступает на вход блока 3 управления, которьй выдает управляющие сигналы в мультиплексор 9, блок 10, регистр 11, а также признак занятости, который поступает в блок 1.

Мультиплексор 9 принимает адрес обращения с входа 14 и формирует две посылки, сначала старшие разряды адреса (адрес строки), затем младшие разряды адреса, которые поступают в блок 10, который принимает с входа 16 сигнал Запись. Последний задает одну из двух операций: запись (низкий уровень) и чтение (высокий уровень). При опера- ции Запись блок 10 принимает данные с входа 13, две посылки адреса с мультиплексора 9, стробы приема адреса строки и адреса столбца с блока 3 .

При операции Чтение блок памяти принимает те же сигналы с блоков 9 и 3 и выдает считанные данные в регистр 11, с выхода которого данные поступают на выход 17 устройства.

В конце операции блок 3 снимает признак занятости и вьщает ответ на выход 18. Процессор снимает запрос 15, блок 1 снимает признак режима обращения и разрешение работы триггера 7, после чего прекращает вырабатываться управляемая синхронизация.

В режиме регенерации устройство работает следующим образом.

Генератор 4 формирует непрерывную серию импульсов, высокой частоты, которая поступает на вход делителя 5 частоты, который вырабатывает последовательность импульсов низкой частоты, которая поступает на вход формирователя 2. С выхода последнего сигнал I поступает на вход блока 1, который выдает сигнал разрешения работы триггера 7, которьш запускает управляемую серию синхросигналов. Затем блок 1 . анализирует занятость устройства и наличие запросов. Если устройство свободно, то блок 1 формирует признак режима регенерации. В случае конфликта, т.е. при поступлении двух запросов одновременно, запрос регенерации имеет более высокий приоритет. Приз- .нак режима регенерации поступает на

3

ВХОД мультиплексора 9, который передает адрес регенерации со счетчика 6 на вход блока 10. Затем запускается одновибратор 12, который формируе строб приема адреса регенерации, который поступает в блок 10 и формирователь 2. После окончания этого строба формирователь 2 вырабатьшает сигнал запуска счетчика 6, который формирует следующий адрес регенерации. Затем формирователь 2 сбрасывает запрос регенерации, блок 1сбрасывает признак режима регенерации и разрешение работы триггера 7, который прекращает выработку управляемой син хросерии.

Формула изобретения

Запоминающее устройство, содержа- щее блок памяти, регистр, .-(ультиплек сор, счетчик, первый триггер, генератор импульсов и блок управления,причем выход блока памяти подключен к первому входу регистра, выход кото- рого является информационным выходом устройства, первый вход блока памяти является информационным входом устройства, а второй вход подключен к выходу мультиплексора, первый вход которого является адресным входом устройства, второй вход соединен с выходом счетчика, а третий - с первым выходом блока управления, второй и третий выходы которого подключены

соответственно к третьему входу бло

ка памяти и второму входу регистра, четвертый вход блока памяти и четвертый выход блока управления являются соответственно одним из управляющих

входов и управляющим выходом устройства, отличающееся тем, что, с целью повьшения быстродействия устройства, в него введены делитель частоты, формирователь сигналов, второй триггер, одновибратор и

блок местного управления, причем выход генератора импульсов подключен к входу делителя частоты и первым входам триггеров и блока местного управления, выход одновибратора соединен с пятым входом блока памяти и первым входом формирователя сигналов, второй вход которого подключен к выходу делителя частоты, а выходы соединены соответственно с входом счетчика к вторым входом блока местного управления, выходы которого подключены соответственно к второму входу первого триггера, входу одновиБра- тора, четвертому входу мультиплексора и первому .входу блока управления, второй вход которого и третий вход блока местного управления соединены с выходом первого триггера, четвертый и пятый входы блока местного управления подключены соответственно к пятому выходу блока управления и выходу второго триггера , вто - рой вход которого является другим управляющим входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления динамической памятью | 1990 |

|

SU1735858A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Динамическое запоминающее устройство и формирователь синхросигналов для него | 1980 |

|

SU936030A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для начальной установки динамической памяти | 1983 |

|

SU1215134A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| УСТРОЙСТВО ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2217791C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах, содержащих динамические элементы памяти, требующие выполнения периодической регенерации содержимого. Цель изобретения - повышение быстродействия устройства. Запоминающее устройство содержит блок памяти, блок MecTkoro управления, блок управления, мультиплексор, последовательно соединенные генератор импульсов, делитель частоты, формирователь сигналов и счетчик, два триггера и одновибра- тор. Устройство работает в двух режимах, обращение и регенерация. Устройство имеет полностью синхронную схему, что и позволяет повысить его быстродействие за счет устранения внутренних запасов времени, присущих асинхронным схемам из-за разброса параметров их элементов. 5 ил. (Л N3 СЛ 05 О QD а

сриг.2

фс/г.З

фигЛ

so

SI

SI га

С

J7

L

37

НвЮ

-f

Редактор А. Сабо

Составитель В. Рудаков

Техред А.Кравчук Корректор Л. Пилипенко

Заказ 4830/52Тираж 5АЗПодписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| СОДЕРЖАЩИЕ ФОТОИНИЦИАТОР ОСНОВНЫЕ И УПЛОТНИТЕЛЬНЫЕ МАССЫ НА ОСНОВЕ СЕРОСОДЕРЖАЩИХ ПОЛИМЕРОВ, СПОСОБ ИХ ОТВЕРЖДЕНИЯ И НАНЕСЕНИЯ, А ТАКЖЕ ИХ ПРИМЕНЕНИЕ | 2013 |

|

RU2637004C2 |

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Андреев В.П., Баранов В.В.Бе- кин Н.В | |||

| Полупроводниковые запоминающие устройства и их применение | |||

| Под ред | |||

| А.Ю | |||

| Гордонова | |||

| М.: Радио и связь, 1981, с | |||

| Способ получения морфия из опия | 1922 |

|

SU127A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-07—Публикация

1985-01-23—Подача