го разряда, вторые входы -го элемента И из группы элементов И, где 1 ,...,, соединены с выходом сумматора первого разряда, соответствующим числу В+1-1, в последнем разряде первые входы группы элементов И соединены с выходом второго элемента И последнего разряда, второй вход

t-го элемента И из группы элементов И, гдеk 1,...,-, соединены с выходом, соответствующим числу +I-k, сумматора первого разряда, а второй вход 6-го элемента И из группы элементов И последнего разряда соединен с выходом,соответствующим числу О сумматора первого разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик импульсов | 1986 |

|

SU1398090A2 |

| Счетчик импульсов | 1982 |

|

SU1051731A1 |

| Реверсивное пересчетное устройство | 1982 |

|

SU1115240A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Реверсивное пересчетное устройство | 1988 |

|

SU1522399A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1965 |

|

SU169891A1 |

| Счетчик импульсов | 1985 |

|

SU1261112A1 |

| Счетчик импульсов | 1983 |

|

SU1187263A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Десятичный сумматор | 1973 |

|

SU491947A1 |

СЧЕТЧИК ИМПУЛЬСОВ, содержащий входную шину и п раэрадов, каждый из которых содержит многоустойчивую пересчетную схему,сумматор, два элемента И, в каждом разряде выходы многоустойчивой пересчетной схемы соединены с первой группой входов сумматора, вторая группа входов которого соединена с выходами сумматора последующего разреда, в котором прямой вход первого и первый вход второго элементов И соединены с выходом второго элемента И предьздущего разряда, прямой вход первого и первый вход второго элементов И первого разряда соединены с входной шиной, в каядзом разряде дополнительный выход сумматора соеданен с соответствующей выходной . шиной, отличающийся тем, что, с целью расширения функциональных возможностей путем реализации реверсивного счета, в него введены две шины управления; а в каяздый разряд - элемент ИЛИ, третий, четвертый, пятый, шестой, седьмой элементы И и группа из 8 элементов И, где равно контрольному числу, в каждом разряде первая и вторая шины управления соединены соответственно с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с выходом сумматора, соответствующнм контрольному числу и, и с нулевым выходом многоустойчивой пересчетной схемы, выходц третьего и четвертого элементов И соединены с входами элемента ИЛИ, выход которого соединен с вторьм входом второго элемента И и с инверсным входом первого элемента И, (Л выход которого соединен с первыми входами пятого и шестого элементов И, вторые входы которых соеди- ; нены соответственно с первой н второй шинами управления, выходы пятого и шестого элементов И соединены соответственно с входами сложения и вычитания многоустойчивой пересчет- , ной схемы, вход установки нулевого состояния которой соединен с выходом седьмого элемента И, первый и второй входы которого соединены соответственно с выходом второго элемента Инс первой шиной управления,в группе на В элементов И, выходы эле ентов И с первого по 6-и соединены соответственно с входами установки в первое, ... ,6 -е состояния многоустойчивой пересчетной схемы, в каждом разряде, кроме последнего, первые входы группы элементов И соединены с входом вычитания многоустойчнвой пересчетной схемы последующе

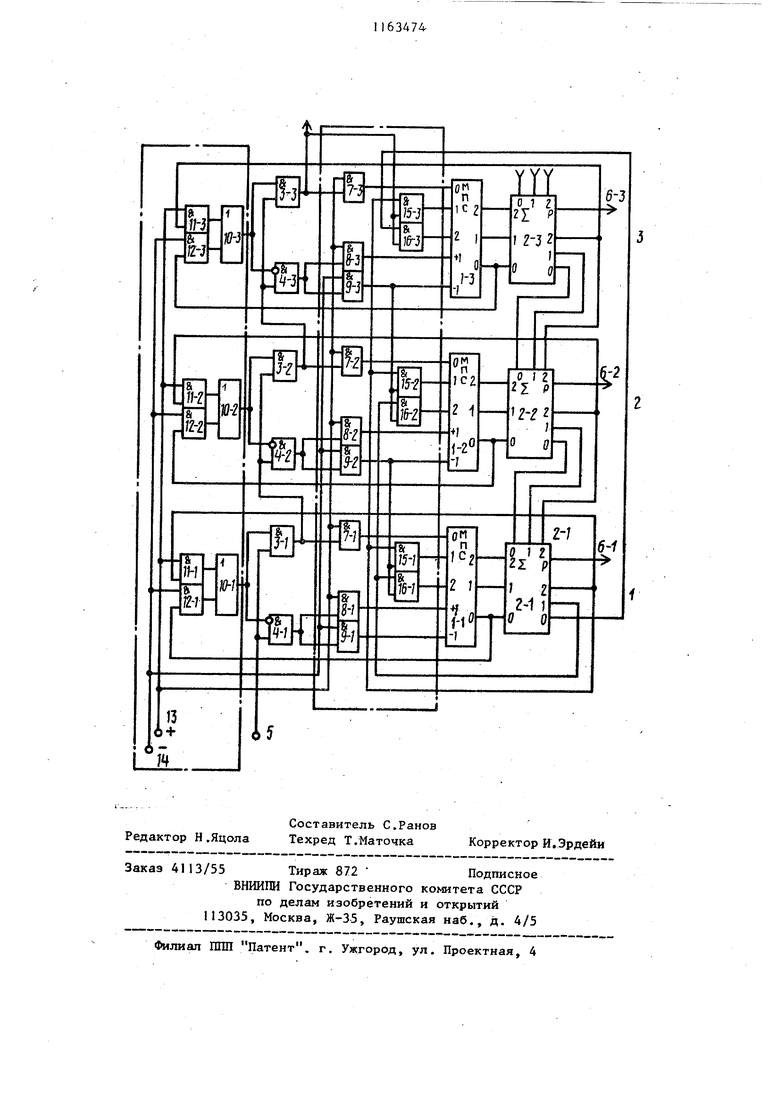

Изобретение относится к цифровы устройствам и предназначено для помехоустойчивого счета импульсов, а также для работы в качестве поме хоустойчивых распределителей импул сов и пересчетных схем. Известен счетчик импульсов с по мехоустойчивым кодом работы, каяоды разряд которого содержит триггер, сумматор, элемент ИЛИ, элемент НЕ и элементы И Q, Недостатком этого устройства . являются ограниченные функциональные возможности, так как оно работает только в режиме прямого счета Известен также счетчик импульсо содержащий входную шину и д разрядов j каждый из которых содержит мн гоустойчивую пере.счетную схему, су матор, два элемента И, в каждом разряде выходы многоустойчивой пересчетной схемы соединены с первой группой входов сумматора, вторая группа входов которого соединена с выходами сумматора последующего разрода, в котором прямой вход пер вого и первый вход второго элемент И соединены с выходом второго элемента И предыдущего разряда, пря мой вход первого и первый вход вто рого элементов И первого разряда с динены со входной Шиной, в калщом разряде дополнительный выход сумматора соединен с соответствующей выходной шиной, выход сумматора, соответствующий контрольному числу с , соединен с инверсным входом .первого и вторым входом второго элементов И C2l . Недостатком известного устройства являются ограниченные функциональные возможности, так как оно работает только в режиме суммирования. Цель изобретения - расширение функциональных возможностей путем реализации реверсивного счета. Поставленная цель достигается тем, что в счетчик импульсов, содержащий входную шину и п разрядов , каждый из которых содержит многоустойчивую пересчетную схему, сумматор, два элемента И, в каждом разряде выходы многоустойчивой пересчетной схемы соединены с первой группой входов сумматора, вторая группа входов которого соединена с выходами сумматора последующего разряда, в котором прямой вход первого и первый вход второго элементов И соединены с выходом второго элемента И предыдущего разряда, прямой вход первого и первый -вход второго элементов И первого разряда соединены с входной шиной, в каждом разряде дополнительный выход сумматора соединен с соответствующей выходной шиной, введены две шины управления, а в каждый разрад - элемент ИЛИ, третий, четвертый, пятый, шестой, седьмой элементы И и группа из ь элементов И, где равно контрольному числу, в каждом разряде первая и вторая шина управления соединены соответственно с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответ ственно с выходом сумматора, соответствующим контрольному числу , и с нулевым выходом многоустойчивой пересчет-ной схемы, выходы третьего и четвертого элементов И сое динены с входами элемента ИЛИ, выход которого соединен с вторым вхо дом второго элемента И и с инверсным входом первого элемента И, вых которого соединен с первыми входами пятого и шестого элементов И, вторые входы которых соединены соответственно с первой и второй шинами управления, выходы пятого и шестого элементов И соединены соответственно с входами сложения и вычитания многоустойчивой пересчетной схемы, вход установки нулевого состояния которой соединен с выходом седьмого элемента И, первый и второй входы которого соединены соответственно с выходом второго элемен та И и с первой шиной управления, в группе из элементов И выходы элементов И с первого по 6-и, соединены соответственно с входами установ ки в первое, ...,6-е состояние многоустойчивой пересчетной схемы, в каждом разряде, кроме последнего, первые входы группы элементов И сое динены с входом вычитания многоустойчивой пересчетной схемы последую щего разряда, вторые входыi-го элемента И из группы элементов И, где t ,... ,6, соединены с выходом сумматора первого р азряда, соответствующим числу 6+1-1, в последнем ра ряде первые входы группы элементов И соединены с выходом второго элемента И последнего разряда, второй вход k-го элемента И из группы элементов И, где ,... ,f-l, соединен с выходом, соответствующим числу &+1-К, сумматора первого разряда, а второй вход 2-го элемента И из группы элементовИ последнего разряда соединен с выходом, соответствующим числу О сумматора первого разряда. На чертеже приведена блок-схема счетчика импульсов на три разряда. Число состояний N предлагаемой структуры счетчика определяется биномиальным коэффициентом: PJ(-p)l где 11- р - контрольное число; р - число разрядов счетчика В рассматриваемом счетчике при р-3, ип 5 е 2. Счетчик импульсов содержит разряды 1, 2 и 3, многоустойчивые пере счетные схемы 1-1 - 1-3 соответственно разрядов 1-3 счетчика импульсов, сумматоры 2-1 -2-3 соответственно разрядов 1-3 счетчика импульсов, элементы И 3-1 - 3-3 и 4-1 - 4-3, входную шину 5, выходные шины 6-1 - 6-3-соответственно разрядов I-3 счетчика импульсов, элементы И 7-1 - 7-3, 8-1 - 8-3 и 9-1 9-3 элементы ИЛИ 10-1 - 10-3 элементы И 11-1 - 11-3 и 12-1 - 12-3, шины 13 и 14 управления, группу элементов И 15-1 и 16-1 разряда 1, группу элементов И 15-2 и 16-2 разряда 2, группу элементов И 15-3 и 16-3 разряда 3. Выходы многоустойчивых пересчетных схем 1-1 - 1-3 соединены соответственно с первыми группами входов сумматоров 2-1.- 2-3, вторые группы входов сумматоров 2-1 и 2-2 соединены соответственно с выходами сумматоров 2-2 и 2-3; прямые входы элементов И 4-1 - 4-3 соединены соответственно с входной шиной 5, с выходами элементов И 3-1 и 3-2; первые входы элементов И 3-1 - 3-3 соединены соответственно с входной шиной 5, с выходами элементов И 3-1 и 3-2, дополнительные выходы сумматоров 2-1 2-3 соединены соответственно .с выходными шинами 6-1 - 6-3, шина 13 управления соединена с первыми входами элементов И 11-1 - 11-3, шина 14 управления соединена с первыми входами элементов И 12-1 - 12-3, вторые входы элементов И 11-1 - 11-3 соединены соответственно с выходами сумматоров 2-1 - 2-3, соответствующим контрольному числу два; вторые входы элементов 12-2 - 12-3 соединены соответственно с нулевы- ми выходами многоустойчивых пересчет- ных схем 1-1-1-3; выходы элементов И 11-1 и 12- соединены с входами элемента ИЛИ 10-1 выходы элементов 11-2 и 12-2 соединены с входами элемента ИЛИ 10-2; выходы элементов 11-3 и 12-3 соединены с входами элемента ШШ 10-3J выходы элементов ИЛИ 10-1-10-3 соединеш 1 соответственно с вторыми входами элементов И 3-1-3-3; выходы элементов ИЛИ 10-1-10-3.соединены соответственно с инверсными входами элементов И 4-1-4-3, выходы которых соеинены соответственно с первыми вхо-;; ани элементов И 8-1-8-3, выходы которых соединены соответственно с входами сложения многоустойчивых пересчетньк схем 1-1-1-3; выходы элементов И 4-1-4-3 соединены соответственно с первыми входами элементов И 9-1-9-3, выходы которых соединены соответственно с входами вычитания многоуйтойчивых пересчетных схем 1-1-1-3, входы установки нулевых состояний которых соединены соответственно с выходами элементов И 7-1-7-3, первые входы которых соединены соответственно с выходами элементов И 3.-1-3-3, вторы входы элементов И 7-1-7-3 соединены с шиной 13 управления и с вторыми входами элементов И 8-1-8-3, вторые входы элементов И 9-1-9-3 соеди нены с шиной 14 управления, выходы элементов И 15-1-15-3 соединены соответственно с входами установки первое состояние многоустойчивых пересчетных схем 1-1-1-3, входы установки во второе состояние которых соединены соответственно с выходами элементов И 16-1-16-3, первые входы элементов И 15-1-15-3 сое динены соответственно с входами вычитания многоустойчивых пересчетных схем 1-2 и 1-3 и с выходом элемента И 3-3, первые входы элементов И 16-1-16-3 соединены соответственно с входами вычитания многоустойчивых пересчетных схем 1-2 и 1-3 и с выходом элемента И 3-3, вторые входы элементов И 15-1-15-3 соединены с выходом, соответствующим числу два, сумматора 2-1; вторые входы элементов И 16-1 и 16-2 соеди нены с выходом, соответствующим чис лу один, сумматора 2-1; второй вход элемента И 16-3 соединен с выходом соответствующим числу ноль, сумматора 2-1. Счетчик импульсов работает следующим обраэом. При выполнении операции сложения на щину 13 подается сигнал единихда производится подготовка элементов И 7-1-7-3, 8-1-а-З и 11-1-11-3 к подаче сигналов|. Сигнал с выхода мн гоустойчивой пересчетной схемы, на пример, 1-2, соответствующий какойто цифре (номеру состояния , посту пает на один иэ входов сумматора 2 на один иэ вторых входов которого поступает сигнал с одного иэ выход сумматора 2-3 старшего разряда 3. Если сумма цифр рассматриваемого и старших раэрядов счетчика равна контрольному числу (в этомслучае младшие разряды счетчика при правильном функционировании будут равны нулю), то на соответствующем выходе сумматора 2-2 вырабатывается сигнал, поступающий на вход элемента И . Поскольку другой вход элемента И 112 соединен с шиной 13, на его вьгеоде вырабатывается сигнал, который череэ элемент ИЛИ 10-2 поступает на вход элемента И 3-2 и инверсный вход элемента И 4-2 . Тем самым будет запрещено поступление счетного импульса на вход элемента И 8-2, выход которого соединен с входом сложения многоустойчивой пересчетной схемы 1-2. Счетный импульс поступает на соседний старший разряд, где в многоустойчивую пересчетную схему 1-3 будет добавлена единица, и на вход элемента И 7-2, с выхода которого сигнал поступает на вход установки в нулевое состояние многоустойчивой пересчетной схемы 1-2 и устанавливает ее в ноль. Если на выходе, соответствующем контрольному числу, сумматора 2-3 сигнал не появляется, то на этом процессе образование единицы переноса и счета по данному счетному импульсу оканчивается. В том случае, когда на выходе, соответствующем контрольному числу, сумматора 2-3 появляется сигнал, то в соответствии с уже ранее рассмотренным алгоритмом происходит установка в ноль соответствуквдей ему пересчетной схемы 1-3 и передача единицы в старший соседний разряд. Разрешенные последовательные состояния счетчика для указанных р и П будут иметь вид: 000,001, 002, 010, 011, 020, 100, 101, ПО, 200. При выполнении операции вычитаия разрешающий сигнал единицы подается на шину 14, чем произвоится подготовка к передаче сигалов элементами И 8-1-8-3 и 12-112-3. Сигналы с выходов многоустойчивых пересчетных схем 1-1-1-3, соответствующие их состояниям, поступают на входы сумматоров 2-1-2-3. На вторые входы сумматоов 2-1 и 2-2 поступают также сигалы выходов сумматоров соседних тарших разрдцов 2-2 и 2-3. Таким

образом, на выходе сумматора 2-1 сигнал будет соответствовать сумме цифр (номеров состояний) всех многоустойчивых пересчетных схем счетчика.

Предположим, что сигнал на выходе многоустойчивой пересчетной схемы, например 1-1, соответствует нулю. При этом также предположим, что в один из старших разрядов занесена цифра, отличная от нуля. Сигнал с нулевого выхода многоустойчивой пересчетной схемы 1-1 поступает на вход элемента И 12-1, второй вход которого соединен с шиной 14. На выходе элемента И 12-1 вырабатывается сигнал, который через элемент ИЛИ 10-1 поступает на вход элемента И 3-1 и инверсный вход элемента И 4-1, тем самым будет запрещено поступление счетного импульса на вход элемента И 9-1, выход которого соединен с входом вычитания многоустойчивой пересчетной схемы 1-1. Счетный импульс поступает на соседний старший разряд, где при наличии разрешения поступает на один вход элемента И 9-2. Другой вход последнего соединен с шиной 14, поэтому на его выходе вырабатывается сигнал, поступакшщй на вход вычитания многоустойчивой пересчетной схемы 1-2 и на один вход группы элементов И 16-1 и 15-1. На другом входе одного из элементов И 15-1 и 16-1 имеется сигнал, соответствуншщй сумме цифр всех

разрядов счетчика, поэто у на выходе этого элемента вырабатывается сигнал, записывающий в многоустойчивую пересчетную схему 1-1 5 цифру, которая дополняет сумму цифр всех разрядов счетчика до контрольного числа,

Если в соседнем старшем разряде сигнал многоустойчивой пере0 счетной схемы соответствует нулю, то счетный импульс в соответствии с уже ранее рассмотренным алгоритмом будет передан в следующий старший разряд. Если все разряды счетчика содержат нули, то на выходе

элемента И 3-3 будет выработан сигнал эаема, который поступает на один вход элементов И и 16-3, на другой вход последнего из которых

0 пода:ется сигнал с нулевого выхода

сумматора 2-1. Выработанный на выходе элемента И 16-3 сигнал устанавливает многоустойчивую пересчетную схему 1-3 в состояние 2 и, таким образом, весь счетчик - в исходное состояние.

Таким образом, по сравнению с известным предлагаемое устройство обладает расширенными функциональными возможностями за счет выполнения

операции вычитания, сохранив при этом помехоустойчивость основного счетчика. Помехоустойчивость счетчика сохраняется за счет того, что и при операции вычитания происходит сравнение суммы всех цифр счетчика с контрольным числом, превышение которого свидетельствует о наличии ошибки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство по заявке № 3479062,кл.Н 03 К 23/00 | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Счетчик импульсов | 1982 |

|

SU1051731A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-06-23—Публикация

1983-09-14—Подача