и

ел ю ю

со со со

. //

/«

fuf.1

Изобретение относится к цифровой электроизмерительной и вычислительной технике и может быть использовано в цифровых системах автоматического контроля и управления.

Цель изобретения - расширение I функциональных возможностей за счет I увеличения диапазона коэффициентов i пересчета пересчетного устройства с ; возможностью оперативного управления коэффициентом пересчета.

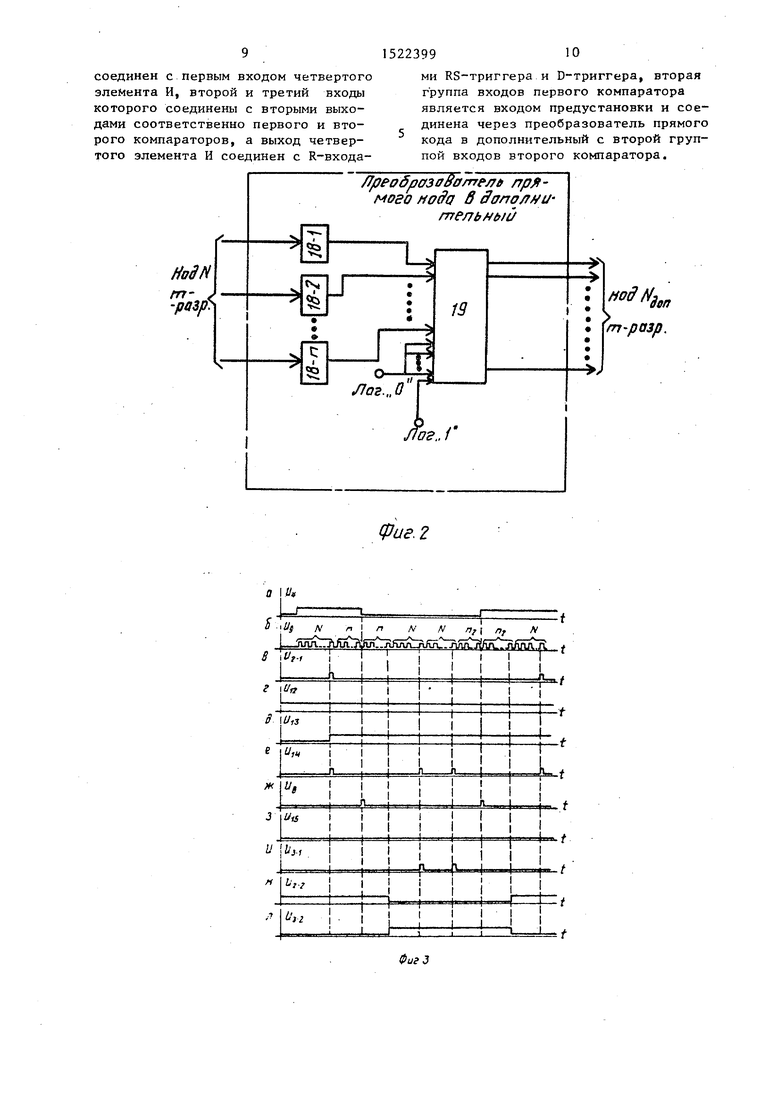

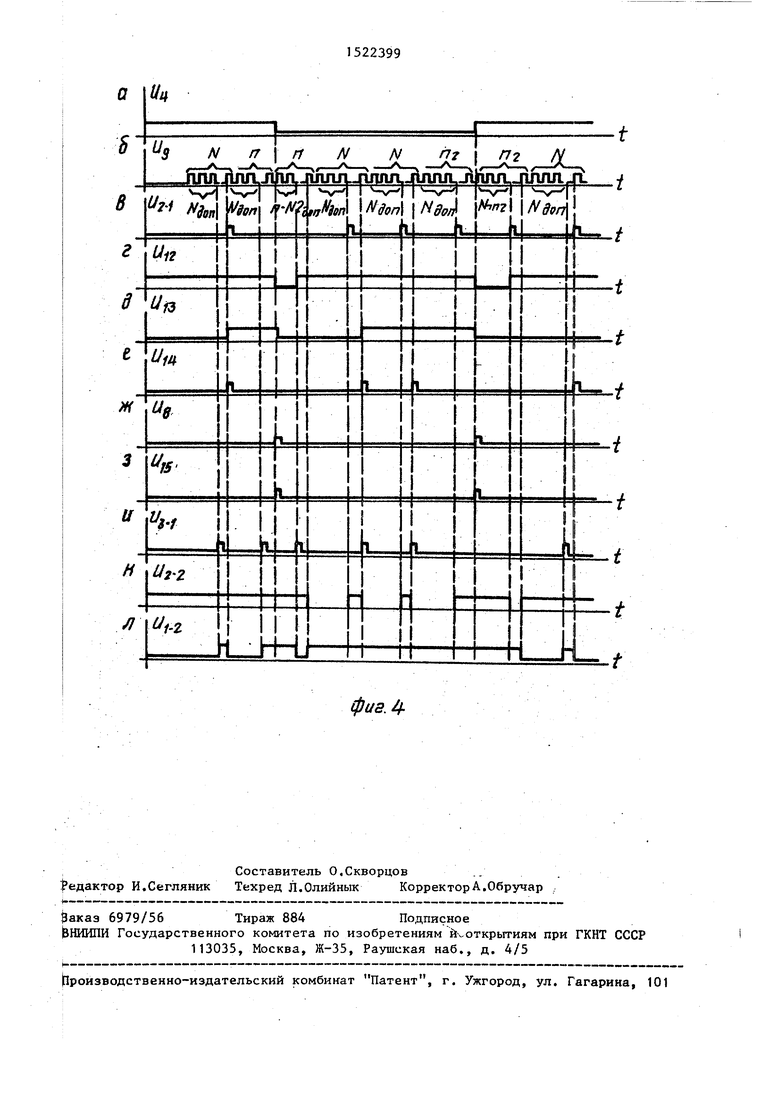

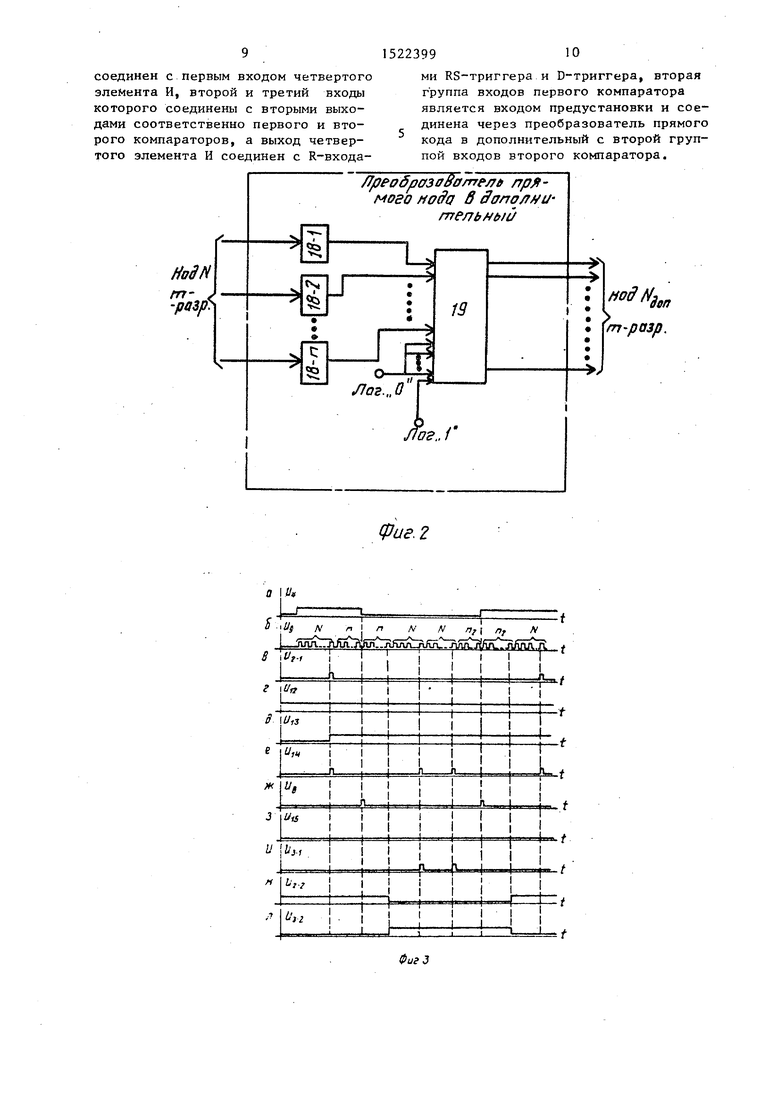

На фиг.1 представлена структурная схема реверсивногопересчетного ; устройства; на фиг.2 - структурная схема преобразователя прямого кода в дополнительный; на фиг.З - временные диаграммы работы устройства; на фиг.4 - то,же.

.На фиг.1 выходы реверсивного счет чика j соединены соответственно с первой группой входов первого 2 и втрого 3 компараторов, первый вход реверсивного счетчика 1 является перв входом устройства (вх,1) и соединен шиной 4 управления пересчетного устройства, Через элемент НЕ 5 с первым входом первого элемента И 6, I с первым входом второго элемента И : 7 и входом,формирователя 8 импульсов I а счетный вход реверсивного счетчика j 1 является вторым входом устройства ,(вх. 2) и соединен с шиной 9 импуль i сов, первый выход первого компаратор i 2 соединен со вторым входом второго I элемента И 7, выход которого соеди- i нен с первым входом элемента ИЛИ 10, I выход которого соединен-с первым входом третьего элемента И 11, S- входом первого RS-триггера 12 и счет I ным входом D-триггера 13, выход кото рого соединен с вторым входом третьего элемента И 11, выход которого . соединен с выходной шиной 14 пересчетного устройства и R-входом реверсивного счетчика 1, первый выход второго компаратора 3 соединен со вторым входом первого элемента И 6, выход которого соединен со вторым входом элемента ИЛИ 10, выход формирователя 8 импульсов соединен с первым входом четвертого элемента И 15, второй и третий входы которого соединены со вторыми вькодами соответ- CTJBeHHO первого 2 и второго. 3 кокпа- раторов, а выход че вертого элемента И 15 соединен с R-входами первого триггера 12 и D-триггёра 13, выход первого триггера 12 соединен с D-BXO

0

5

Q 5 Q Q

5

0

дом D-триггера 13, вторая группа входов первого компаратора 2 соединена соответственно со входами преобразователя 16 прямого кода в дополнительный и входной шиной 17 предустановки коэффициента пересчета, выходы преобразователя 16 прямого кода в дополнительный соединены соответственно со второй группой входов второго компаратора 3.

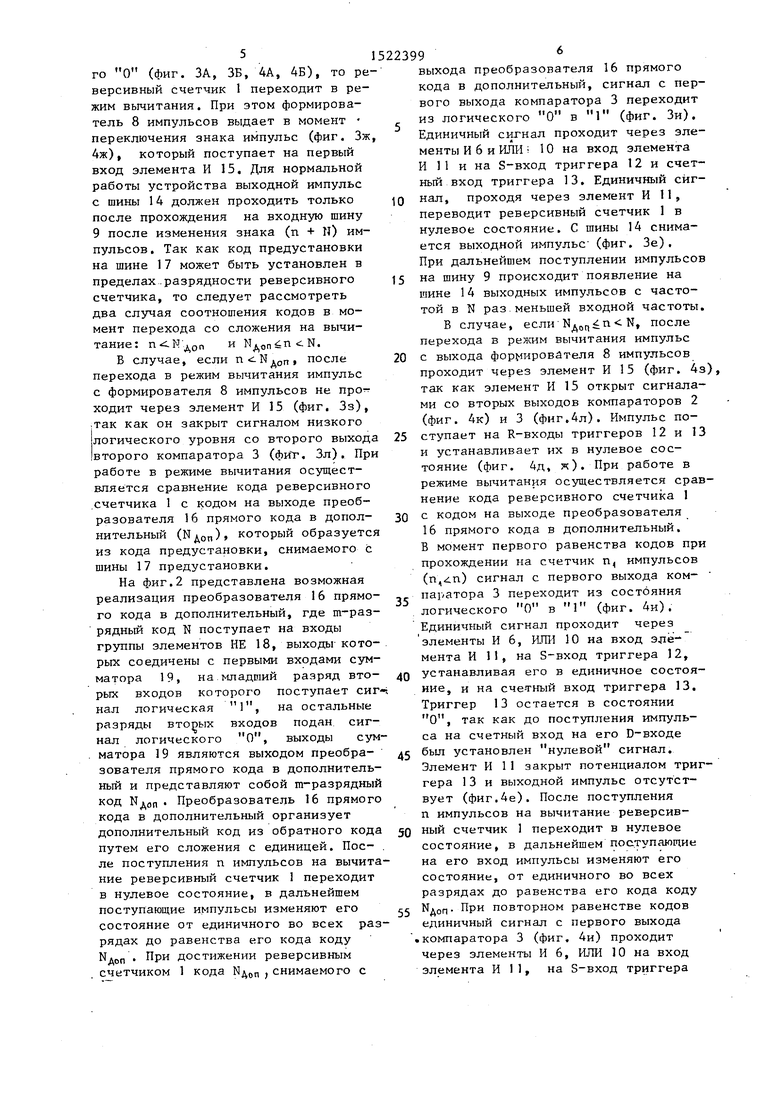

Реализация преобразователя 16 прямого кода в дополнительный представлена на фиг.2..

Устройство работает следующим образом.

В исходном состоянии реверсивный счетчик 1 и триггер 13 находятся в состоянии логического О, триггер 12 находится в состоянии логической 1. В режиме сложения на шину 4 управления поступает сигнал положительной полярности (фиг. За, 4а) .и реверсивный счетчик 1 изменяет свое состояние по.переднему фронту

входных импульсов, поступающих ,1,3

шину 9 (фиг. Зб, 4б) при этом производится сравнение кода на выходе реверсивного счетчика 1 с кодом предустановки с помощью компаратора 2. При достижении реверсивным счетчиком 1 кода предустановки сигнал с первого выхода компаратора 2 переходит из состояния О в 1 (фиг. Зв, 4в). В режиме сложения единичный сигнал с первого выхода компаратора 2 проходит через элементы И 7, ИЛИ 10, устанавливая триггер 13 в единичное состояние, и на вход элемента И 11. На вьжоде триггера 13 устанавливается логическая 1, тем самым устанавливая на выходе элемента И 11 единичный уровень . Единичный сигнал переводит реверсивный счетчик в нулевое состояние. С шины 14 снимается выходной импульс (фиг, Зе, 4е). Длительность импульса определяется временами срабатывания триггера 13 и переходом реверсивного счетчика 1 JB нулевое состояние. В дальнейшем при поступлении импульсов на шину 9 происходит появление на шине 14 выходных импульсов с частотой в N раз меньшей входной частоты, где N - код предуста- новки на шине 17,

Если после поступления п импульсов на сложение () на шину 4 управления поступил.сигнал логическо

го О (фиг. ЗА, ЗБ, 4А, 4Б), то реверсивный счетчик 1 переходит в режим вычитания. При этом формирователь 8 импульсов выдает в момент переключения знака импульс (фиг. Зж, 4ж), который поступает на первый вход элемента И 15, Для нормальной работы устройства выходной импульс с шины 14 должен проходить только после прохождения на входную шину 9 после изменения знака (п + Tl) импульсов , Так как код предустановки на шине 17 может быть установлен в пределах.разрядности реверсивного счетчика, то следует рассмотреть два соотношения кодов в момент перехода со сложения на вычитание: и МдопбпсЫ.

В случае, если после Перехода в режим вычитания импульс с формирователя 8 импульсов не проходит через элемент И 15 (фиг. Зз), так как он закрыт сигналом низкого логического уровня со второго выхода второго компаратора 3 (фиТг. 3л). При работе в режиме вычитания осуществляется сравнение кода реверсивного счетчика 1 с кодом на выходе преобразователя 16 прямого кода в дополнительный (,), который образуется из кода предустановки, снимаемого с шины 17 предустановки.

На фиг.2 представлена возможная реализация преобразователя 16 прямого кода в дополнительный, где т-раз- рядный код N поступает на входы группы элементов НЕ 18, выходы которых соединены с первыми входами сумматора 19, на младший разряд вторых входов которого поступает сиг-;

нал логическая разряды

I111I i I

на остальные

входов подан сигвторых

нал логического О, выходы сум- матора 19 являются выходом преобразователя прямого кода в дополнительный и представляют собой т-разрядный код Кдоп . Преобразователь 16 прямого кода в дополнительный организует дополнительный код из обратного кода путем его сложения с единицей. Пос- . ле поступления п импульсов на вычитание реверсивный счетчик 1 переходит в нулевое состояние, в дальнейшем поступающие импульсы изменяют его состояние от единичного во всех разрядах до равенства его кода коду доп При достижении реверсивным счетчиком 1 кода Nдoп , снимаемого с

0

5

0

5

0

5

0

5

0

5

выхода преобразователя 16 прямого кода в дополнительный, сигнал с первого выхода компаратора 3 переходит из логического О в 1 (фиг. Зи). Единичный сигнал проходит через элементы И 6 и ИЛИ ; 10 на вход элемента И 11 и на S-вход триггера 12 и счетный вход триггера 13. Единичный сигнал, проходя через элемент И 11, переводит реверсивный счетчик 1 в нулевое состояние. С шины 14 снимается выходной импульс- (фиг. Зе). При дальнейшем поступлении импульсов на шину 9 происходит появление на шине 14 выходных импульсов с частотой в N раз.меньшей входной частоты.

В случае, если Кд п N, после перехода в режим вычитания импульс с выхода фор{ ирователя 8 импульсов проходит через элемент И 15 (фиг. 4з), так как элемент И 15 открыт сигналами со вторых выходов компараторов 2 (фиг. 4к) и 3 (фиг.4л). Импульс поступает на R-входы триггеров 12 и 13 и устанавливает их в нулевое состояние (фиг. 4д, ж). При работе в режиме вычитания осуществляется сравнение кода реверсивного счетчика 1 с кодом на выходе преобразователя 16 прямого кода в дополнительный. В момент первого равенства кодов при прохождении на счетчик п, импульсов (п,г:п) сигнал с первого выхода ком- паратора 3 переходит из состояния логического О в 1 (фиг. 4и). Единичный сигнал проходит через элементы И 6, ИЛИ 10 на вход элемента И 11, на S-вход триггера 12, устанавливая его в единичное состояние, и на сче-тный вход триггера 13. Триггер 13 остается в состоянии О, так как до поступления импульса на счетный вход на его D-входе был установлен нулевой сигнал. Элемент И 11 закрыт потенциалом триггера 13 и выходной импульс отсутствует (фиг.4е). После поступления п импульсов на вычитание реверсивный счетчик 1 переходит в нулевое состояние, в дальнейшем поступающие на его вход импульсы изменяют его состояние, от единичного во всех разрядах до равенства его кода коду Кдоп. При повторном равенстве кодов единичный сигнал с первого выхода компаратора 3 (фиг. 4и) проходит через элементы И 6, ИЛИ 10 на вход элемента И 11, на S-вход триггера

10

1522399

меняя его состояния, на вход триггера 13, переводя . Триггер 13 открывает И 11, и единичный сигнал проR-вход реверсивного счетчиреводя его в нулевое состоя ины 14 снимается выходной (фиг. 4е) .

ьнейшем при поступлении имна шину 9 происходит появлешине 14 выходных импульсов ой в N раз меньшей входной

гичным образом устройство и при переходе от вычитания ию. Формирователь 8 импульсов момент переключения знака (фиг. Зж, 4ж), который пона Первый :вход элемента И 15 также возможно два случая:

15

20

в

111

N

сч сч че ци бы 15 из да

Ф

ст дв ко ре ме пе щ ши за не сч оп то ко ко те эл и сч пе ро ве вх вы вх ны ля ус ко вт со Ш пе Sдоди ме вы со сч па пе со ИЛ

п„ N и

NAOP

п- g,N, где и - число импул1 сс в, поступившее на реверсивный счетчик 1 за период между обнулением и моментом перехода от вычитания к сложению.

В первом случае () элемент И 15 будет закрыт сигналом низкого логического уровня со второго выхода первого компаратора 2 (фиг. Зв), реверсивный счетчик 1 работает на сложение по поступлению на его.входную шину 9 импульсов до тех пор, пока Не обнулится после его переполнения, в дальнейшем его работа про

исходит так, как объяснено в первой части описания работы (фиг. 3).

Во втором случае (NдQp ng N) так же, как и во втором случае ра- боты на вычитание, элемент, И 15 от крыт и сигнал в формирователе 8 импульсов (фиг. 4ж) поступает на R-входы триггеров 12 и 13 и устанавливает их в нулевое состояние (фиг . 4и, д) Обнуление реверсивного счетчика i 1 и выдача выходного импулса при этом происходит только в момент второго равенства состояния реверсивного счетчика и кода N(фиг.4 На шине 14 наблюдаются импульсы с частотой N раз меньшей входной часто ты.

в реверсивном пересчетном устройстве, таким образом, правильно выдается сигнал деления частоты в случае изменения направления счета при любом состоянии реверсивного счетчика при любом коэффициенте пересчета N, который может быть установлен

0

22399

8

в пределах от 2 до (N - 1), где

111 1-1 m

N 2 , m-разрядность реверсивного

счетчика. Например, если в качестве счетчика 1 используется реверсивный четырехразрядный счетчик, то коэффициент пересчета устройства может быть установлен в пределах от 2 до 15 и при необходимости его можно изменять в этих пределах путем подачи нового кода на шину 17.

Формула изобретен

5

0

5

0

5

40

45

50

55

Реверсивное пересчетное устройство, содержащее реверсивный счетчик, два элемента И, элемент НЕ, вход которого соединен с первым входом реверсивного счетчика, а выход элемента НЕ соединен с первым входом первого элемента И, отличающееся тем, что, с целью расширения функциональных возможностей за счет увеличения диапазона изменения коэффициента пересчета пересчетного устройства с возможностью оперативного управления коэффициентом пересчета введены первый и второй компараторы, преобразователь прямого кода в дополнительный, формирователь импульсов, третий и четвертый элементы И, элемент Ю Ш, RS-триггер и D-триггер, выходы реверсивного счетчика соединены соответственно с первой группой входов первого и второго компараторов, аервый вход реверсивного счетчика является первым входом устройства и соединен с первым входом второго элемента И и входом формирователя импульсов, счетный вход реверсивного счетчика является вторым входом Пересчетного устройства, первый выход первого компаратора соединен с вторым входом второ.го элемента И, выход которого соединен с первым входом элемента ШШ, выход которого соединен с первым входом третьего элемента И, Sвходом RS-триггера и тактовым входом D-триггера, выход которого соединен с вторым входом третьего элемента И, выход которого является выходом пересчетного устройства и соединен с R-входом реверсивного счетчика, первый выход второго компаратора соединен с вторым входом первого элемента И, выход которого соединен с вторым входом элемента ИЛИ. выход формирователя импульсов

соединен с первым входом четвертого элемента И, второй и третий входы которого соединены с вторыми выходами соответственно первого и второго компараторов, а выход четвертого элемента И соединен с R-входа152239910

ми RS-триггера и D-триггера, вторая группа входов первого компаратора является входом предустановки и соединена через преобразователь прямого кода в дополнительный с второй группой входов второго компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивное пересеченное устройство | 1989 |

|

SU1598173A2 |

| Устройство для управления встречно-параллельно включенными тиристорами | 1979 |

|

SU884144A1 |

| Сенсорный переключатель | 1982 |

|

SU1051720A1 |

| Система управления многопозиционной индукционной нагревательной установкой | 1983 |

|

SU1121789A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПЕРЕМЕЩЕНИЙ | 1989 |

|

RU2022231C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ЦЕЛЫХ ФАЗОВЫХ ЦИКЛОВ | 1991 |

|

RU2022279C1 |

| Конвейерные весы | 1989 |

|

SU1643945A2 |

| Сенсорный переключатель | 1986 |

|

SU1401593A2 |

| Устройство для измерения времени установления выходного сигнала цифро-аналоговых преобразователей | 1985 |

|

SU1298916A1 |

| Измеритель характеристик электрического сигнала | 1987 |

|

SU1429053A1 |

Изобретение относится к цифровой электроизмерительной и вычислительной технике и может быть использовано в цифровых системах автоматического контроля и управления. Цель изобретения - расширение диапазона коэффициентов пересчета устройства с возможностью оперативного управления коэффициентом пересчета - достигается за счет новой организации пересчетного устройства, а именно при прямом счете осуществляется сравнение кода счетчика 1, работающего в режиме суммирования импульсов, и прямого кода предустановки коэффициента на шине 17 пересчета компаратором 2. При обратном счете осуществляется сравнение кода счетчика 1, работающего в режиме вычитания, и дополнительного кода предустановки коэффициента пересчета компаратором 3. Коэффициент пересчета определяется кодом, поданным на шину 17 предустановки коэффициента пересчета, при этом код предустановки может принимать любые значения и ограничиваться сверху только разрядностью реверсивного счетчика. 4 ил.

фиг. 2

а

ifn

и,

N Г7 fi N

9пг

%/т| -А йгЛл

Ndon

фаз.4

| Двоично-десятичное пересчетное устройство | 1977 |

|

SU746947A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Реверсивное пересчетное устройство | 1982 |

|

SU1083365A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-15—Публикация

1988-01-12—Подача