Известны сумматоры с фазоимиульсным представлением чисел, содержащие преобразователи фазы в число импульсов (клавиатура и 1-енератор чисел, триггер, ключи и схемы «ИЛИ, декадный счетчик на лампах с холодным катодом).

Предложенный сумматор отличается тем, что в нем первый вход триггера преобразования первого слагаемого во время-импульсное представление подключен к источнику импульсов первого слагаемого, его второй вход подсоединен к источникам нулевых опорных импульсов основного и дополнительного тактов. Выход триггера подключен к первому входу схемы «И преобразования первого слагаемого в прямой унитарный код, второй вход которой подсоединен к источнику импульсов основного такта, а ее выход подключен к первому входу схемы «ИЛИ. Первый вход триггера преобразования второго слагаемого во время-импульсное представление соединен с источником импульсов второго слагаемого, его второй вход - с источником импульсов основного и дополнительного тактов. Прямой выход триггера подключен к первому входу трехвходовой схемы «И преобразования второго слагаемого в прямой унитарный код, ее два других входа - к источнику импульсов основного такта от первого до девятого и к источнику команды сложения. Инверсный выход триггера подключен к первому входу трехвходовой схемы «И преобразования второго слагаемого в дополнительный унитарный код, ее два других входа - к источнику импульсов основного такта от первого до восьмого. Выходы этих схем «И подсоединены ко второму и третьему входам схемы «ИЛИ, выход последней- к счетному входу фазоимпульсного многоустойчивого элемента. Вход сброса этого элемента подключен к источнику нулевых опорных импульсов, вход тактовых импульсов - к источнику импульсов дополнительного такта. Выход фазоимпульсного многоустойчивого элемента подключен к первым входам схем совпадения выделения суммы и схемы формирования импульса переноса (запрета заема), вторые входы которых подсоединены к источникам импульсов дополнительного и основного тактов соответственно. Выход схемы формирования импульса переноса (запрета заема) подсоединен к единичному входу регистра, его нулевой вход-к источнику импульсов первого слагаемого, а выход регистра -

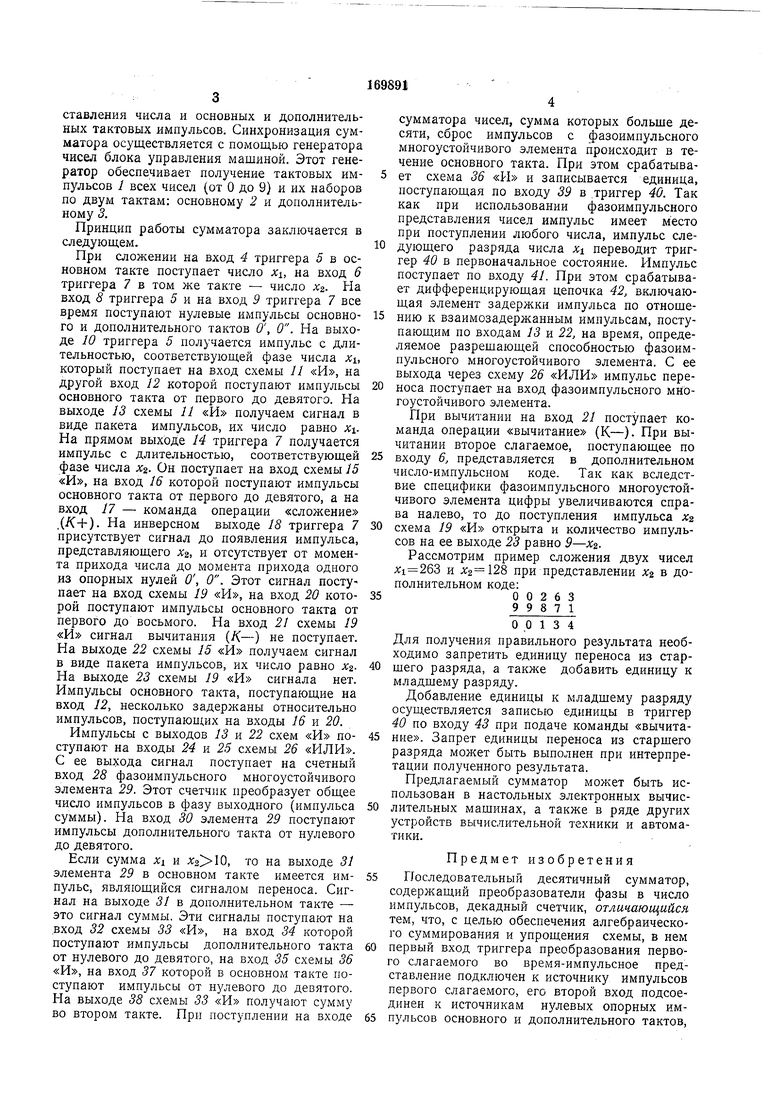

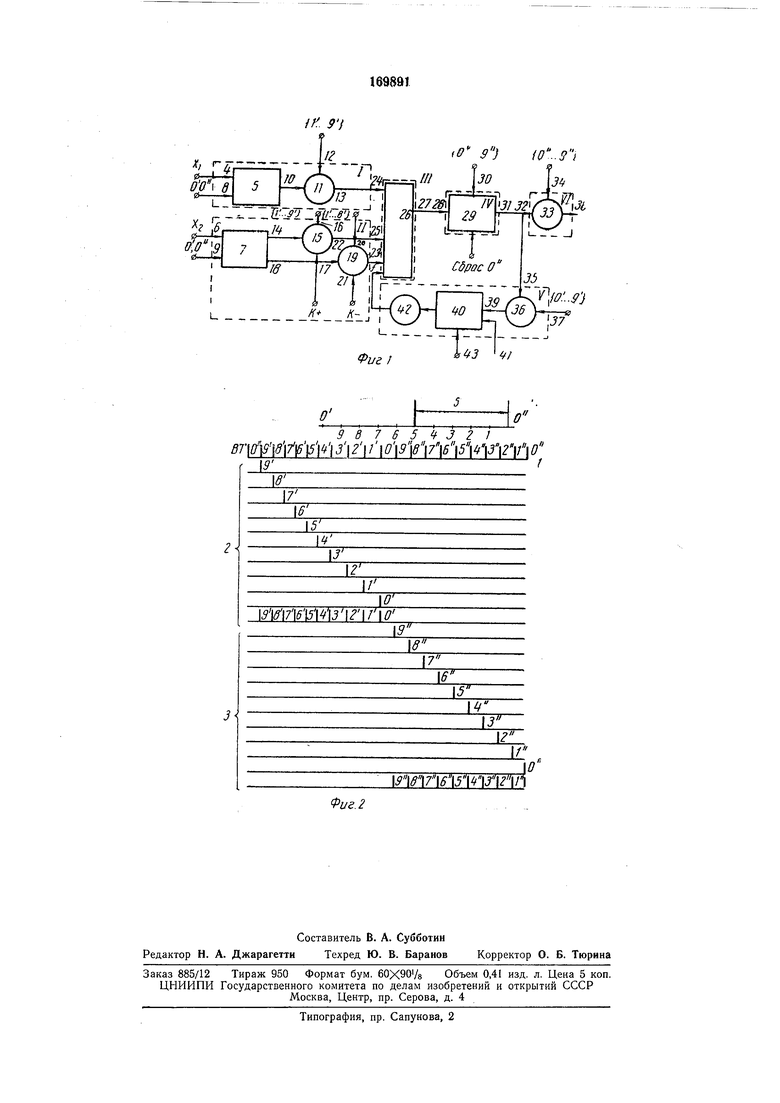

через дифференцирующую цепочку к четвертому входу схемы «ИЛИ. Это дает возможность осуществить алгебраическое суммирование и уиростить схему. На фиг. 1 изображена блок-схема сумматоставления числа и основных и дополнительных тактовых импульсов. Синхронизация сумматора осуществляется с помощью генератора чисел блока управления мащлной. Этот генератор обеспечивает получение тактовых импульсов / всех чисел (от О до 9} и их наборов по двум тактам: основному 2 и дополнительному 3,

Принцип работы сумматора заключается в следующем.

При сложении на вход 4 триггера 5 в основном такте поступает число Xi, на вход 6 триггера 7 в том же такте - число х. На вход 8 триггера 5 и на вход 9 триггера 7 все время поступают нулевые импульсы основного и дополнительного тактов О , О. На выходе 10 триггера 5 получается импульс с длительностью, соответствующей фазе числа х, который поступает на вход схемы // «И, на другой вход 12 которой поступают импульсы основного такта от первого до девятого. На выходе 13 схемы 11 «И получаем сигнал в виде пакета импульсов, их число равно xi. На прямом выходе 14 триггера 7 получается импульс с длительностью, соответствующей фазе числа хг. Он поступает на вход схемы 15 «И, на вход 16 которой поступают импульсы основного такта от первого до девятого, а на вход 17 - команда операции «сложение X/C-f). На инверсном выходе 18 триггера 7 присутствует сигнал до появления импульса, представляющего лз, и отсутствует от момента прихода числа до момента прихода одного из опорных нулей О , О. Этот сигнал поступает на вход схемы 19 «И, на вход 20 которой поступают импульсы основного такта от первого до восьмого. На вход 21 схемы 19 «И сигнал вычитания (К.-) не поступает. На выходе 22 схемы 15 «И получаем сигнал в виде пакета импульсов, их число равно Х2. На выходе 23 схемы 19 «И сигнала нет. Импульсы основного такта, поступающие на вход 12, несколько задержаны относительно импульсов, поступающих на входы 16 и 20.

Импульсы с выходов 13 и 22 схем «И поступают на входы 24 и 25 схемы 26 «ИЛИ. С ее выхода сигнал поступает на счетный вход 28 фазоимпульсного многоустойчивого элемента 29. Этот счетчик преобразует общее число импульсов в фазу выходного (импульса суммы). На вход 30 элемента 29 поступают импульсы дополнительного такта от нулевого до девятого.

Если сумма Xi и , то на выходе 31 элемента 29 в основном такте имеется импульс, являющийся сигналом переноса. Сигнал на выходе 31 в дополнительном такте - это сигнал суммы. Эти сигналы поступают на вход 32 схемы 33 «И, на вход 34 которой поступают импульсы дополнительного такта от нулевого до девятого, на вход 35 схемы 36 «И, на вход 37 которой в основном такте поступают импульсы от нулевого до девятого. На выходе 38 схемы 33 «И получают сумму во втором такте. При поступлении на входе

сумматора чисел, сумма которых больше десяти, сброс импульсов с фазоимпульсного многоустойчивого элемента происходит в течение основного такта. При этом срабатывает схема 36 «РЬ и записывается единица, поступающая по входу 39 в .триггер 40. Так как при использовании фазоимпульсного представления чисел импульс имеет место при поступлении любого числа, импульс следующего разряда числа Xi переводит триггер 40 в первоначальное состояние. Импульс поступает по входу 41. При этом срабатывает дифференцирующая цепочка 42, включающая элемент задержки импульса по отнощению к взаимозадержанным импульсам, поступающим по входам 13 и 22, на время, определяемое разрещающей способностью фазоимпульсного многоустойчивого элемента. С ее выхода через схему 26 «ИЛИ импульс переноса поступает на вход фазоимпульсного многоустойчивого элемента.

При вычитании на вход 21 поступает команда операции «вычитание (К-). При вычитании второе слагаемое, поступающее по

входу 6, представляется в дополнительном число-импульсном коде. Так как вследствие специфики фазоимпульсного многоустойчивого элемента цифры увеличиваются справа налево, то до поступления импульса Х2

схема 19 «И открыта и количество импульсов на ее выходе 23 равно 9-Xs.

Рассмотрим пример сложения двух чисел и JC2-128 при представлении лга в дополнительном коде:

00263

99871

00134

Для получения правильного результата необходимо запретить единицу переноса из старщего разряда, а также добавить единицу к младщему разряду.

Добавление единицы к младщему разряду осуществляется записью единицы в триггер 40 по входу 43 при подаче команды «вычитание. Запрет единицы переноса из старщего разряда может быть выполнен при интерпретации полученного результата.

Предлагаемый сумматор может быть использован в настольных электронных вычислительных мащинах, а также в ряде других устройств вычислительной техники и автоматики.

Предмет изобретения

Последовательный десятичный сумматор, содержащий преобразователи фазы в число импульсов, декадный счетчик, отличающийся тем, что, с целью обеспечения алгебраического суммирования и упрощения схемы, в нем

выход триггера подключен к первому входу схемы «И преобразования первого слагаемого в прямой унитарный код, второй вход которой подсоединен к источнику импульсов основного такта, а ее выход подключен к первому входу схемы первый вход триггера преобразования второго слагаемого во время-импульсное представление соединен с источником импульсов второго слагаемого, его второй вход подсоединен к источнику импульсов основного и дополнительного тактов, прямой выход триггера подключен к первому входу трехвходовой схемы «И преобразования второго слагаемого в прямой унитарный код, ее два других входа подсоединены к источнику импульсов основного такта от первого до девятого, и к источнику команды сложения, инверсный выход триггера подключен к первому входу трехвходовой схемы «И преобразования второго слагаемого в дополнительный унитарный код, ее два других входа подсоединены к источнику импульсов основного такта от первого до восьмого, выходы этих схем «И подсоединены ко второму и третьему входам схемы «ИЛИ, выход которой подсоединен к счетному входу

фазоимпульсного многоустойчивого элемента, второй вход сброса которого подключен к источнику нулевых опорных импульсов, вход тактовых импульсов подсоединен к источнику импульсов дополнительного такта, выход фазоимпульсного многоустойчивого элемента подключен к первым входам схем совпадения выделения суммы и схемы формирования импульса переноса (запрета заема), вторые входы которых подсоединены к источникам импульсов дополнительного и основного тактов, соответственно, выход схемы формирования импульса переноса (запрета заема) подсоединен к единичному входу регистра, нулевой вход которого подключен к источнику импульсов первого слагаемого, а выход регистра-через дифференцирующую цепочку к четвертому входу схемы «ИЛИ.

& S) W..,

U/

| название | год | авторы | номер документа |

|---|---|---|---|

| Десятичный сумматор | 1973 |

|

SU491947A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧИСЕЛ, НРЕДСТАВЛЕННЫХ ФАЗОИМПУЛЬСНЫМИ ДЕСЯТИЧНЫМИ КОДАМИ | 1973 |

|

SU384104A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК | 1973 |

|

SU362490A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1972 |

|

SU430512A1 |

| ОДНОРАЗРЯДНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК | 1971 |

|

SU300958A1 |

| Реверсивный счетчик импульсов | 1972 |

|

SU437231A1 |

| Фазо-импульсный сумматор | 1977 |

|

SU651343A1 |

| Устройство для умножения чисел, представленных фазо-импульсными кодами | 1972 |

|

SU439807A1 |

0

Br( 3 2in 0

Ж

0

Даты

1965-01-01—Публикация