1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при реализации технических средств ЭЦВМ для суммирования чисел в десятичном коде.

Р1звестен десятичный сумматор, содержащий фазо-имнульсный многоустойчивый элемент, первый и второй входы которого соединены соответственно с шиной установки в «О и выходом элемента «ИЛИ, а первый и второй выходы - соответственно с шиной суммы устройства и с первым входом узла выработки импульсов заема, второй вход которого подключен к шине импульсов опроса заема, а выход - к шине импульсов заема в старший разряд устройства, причем первый вход элемента «ИЛИ соединен с выходом элемента «И, подключенного входами соответственно к шине тактовых импульсов и к шине импульсов заема, второй вход - с шиной импульсов переноса, а третий вход -с выходом преобразователя фазо-нмпульсного кода в число-импульсный, с первого по третий входы которого подключены соответственно к шине тактовых импульсов, к шине второго слагаемого и к шине импульсов опорной частоты, и узел выработки импульсов переноса, вход которого соединен с шиной опроса переноса, а выход - с шиной импульсов переноса в старший разряд.

Недостатком известного сумматора является низкое быстродействие, одна из причин которого состоит в том, что слагаемые поступают ма вход фазо-импульсного многоустойчивого элемента, входяш,его в состав сумматора, последовательно.

Целью изобретения является повышение быстродействия сумматора.

Поставленная цель достигается тем, что

предлагаемый сумматор содержит дополнительный преобразователь фазо-импульсного кода в число-импульсный, с первого по третий входы которого соединены соответственно с шиной тактовых импульсов, с шиной первого

слагаемого и с шиной импульсов опорной частоты, а первый и второй выходы - соответственно с дополнительным входом элемента «И и первым дополнительным входом узла выработки импульсов переноса, второй

дополнительный вход которого соединен с дополнительным выходом преобразователя фазо-импульсного кода в число-импульсный код, третий дополнительный вход - к шине знака первого слагаемого, к четвертому входу дополнительного преобразователя фазо-импульсного кода в число-импульсный и к первому дополнительному входу узла выработки импульса заема, а четвертый дополнительный вход - к шине знака второго слагаемого, к

дополнительному входу преобразователя фазо-импульсного кода в число-импульсный и ко второму дополнительному входу узла выработки импульсов заема.

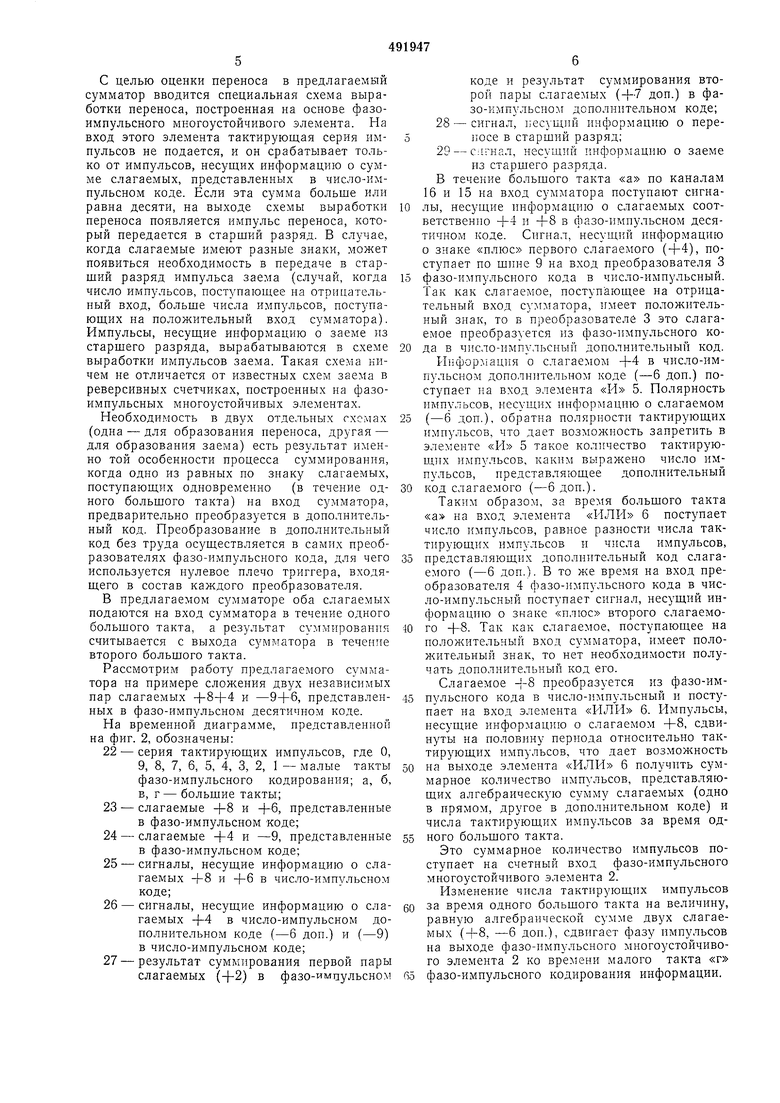

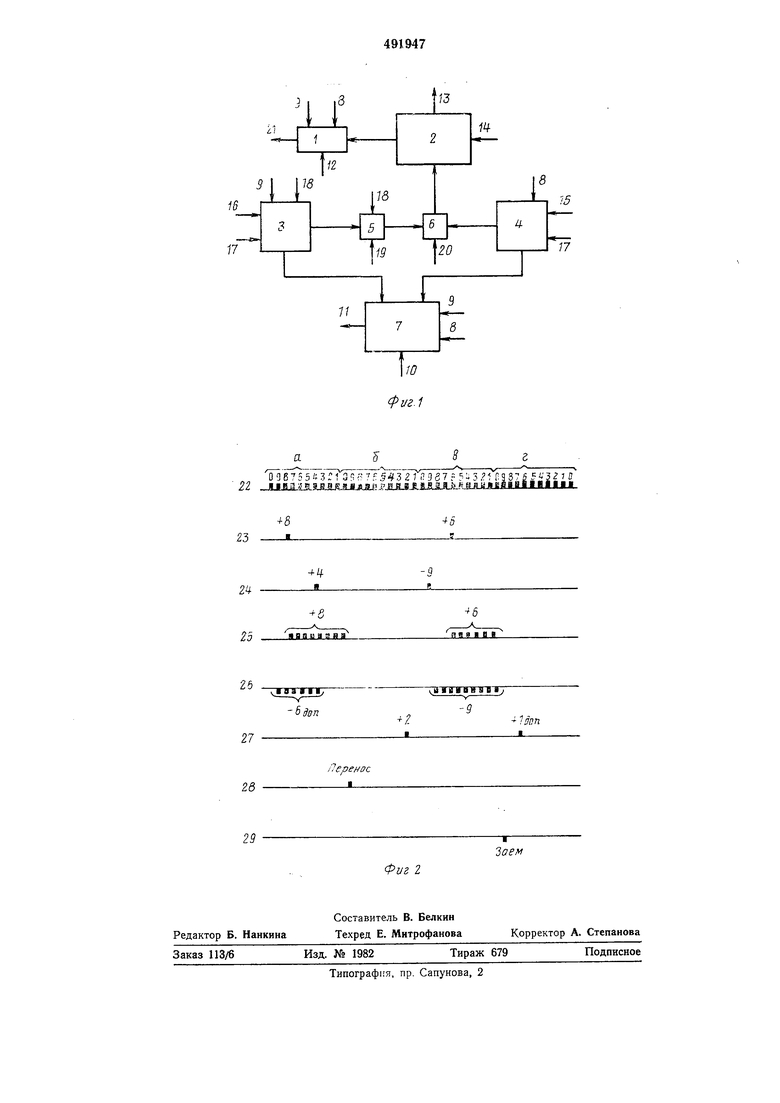

На фиг. 1 представлена блок-схема десятичного сумматора; на фиг. 2 - диаграмма его работы.

Десятичный сумматор содержит узел выработки импульсов заема, фазо-импульсный многоустойчивый элемент 2, преобразователи 3, 4 фазо-импульсного кода в число-импульсный, элемент «И 5, элемент «ИЛИ 6, узел 7 выработки импульсов переноса, шину 8 знака второго слагаемого, шину 9 знака первого слагаемого, шину 10 опроса переноса, шину 11 импульсов переноса в старший разряд, шину 12 опроса заема, шину суммы 13, шину 14 установки в «О, шину 15 первого слагаемого, шину 16 второго слагаемого, шину 17 импульсов опорной частоты, шину 18 тактовых импульсов, шину 19 импульсов заема, шину 20 импульсов переноса, шину 21 импульсов заема в старший разряд.

Предложенный десятичный сумматор работает следуюш,им образом.

В начальный момент на вход сумматора поступают первое и второе слагаемое в фазоимпульсном десятичном коде. В преобразователях 3, 4 фазо-импульсного кода в число-импульсный импульсный код десятичных цифр преобразуется в число-импульсный (прямой или дополнительный).

Преобразователи фазо-импульсного кода в число-импульсный могут быть построены на основе, например, триггера и схемы совпадения, причем единичное плечо триггера используется для преобразования в число-импульсный прямой код, а нулевое - в числоимпульсный дополнительный код.

Информация о слагаемых поступает через элемент «И 5 на вход элемента «ИЛИ б. Одновременно слагаемые передаются на узел 7 выработки сигналов переноса, который будет работать, если знаки слагаезгых на шипах 8, 9 одинаковы, а по шине 10 на вход узла 7 выработки сигналов переноса поступают импульсы опорной частоты. Если сумма больше или равнл десяти, появляется импульс переноса, который передается в старший разряд по шине 11.

Узел выработки сигналов переноса может быть построен на основе, например, фазо-импульсного мпогоустойчивого элемента и триггера опроса.

В случае, если слагаемые имеют разные знаки, информация о которых поступает по шинам 8 и 9, то появление сигнала заема на выходной шине 11 указывает на знак «минус результата.

Такая схема не отличается от известных схем заема в реверсивных счетчиках, построенных на фазо-имнульсных элементах.

С выхода элемента «ИЛИ 6 суммарное количество импульсов, представляющее алгебраическую сумму слагаемых и тактируюш,их

импульсов, поступает на счетный вход фазоимпульсного многоустойчивого элемента 2.

По прошествии двух больших тактов фазоимпульсный элемент 2 устанавливается в нулевое ноложение импульсами, поступаюш,ими по шине 12.

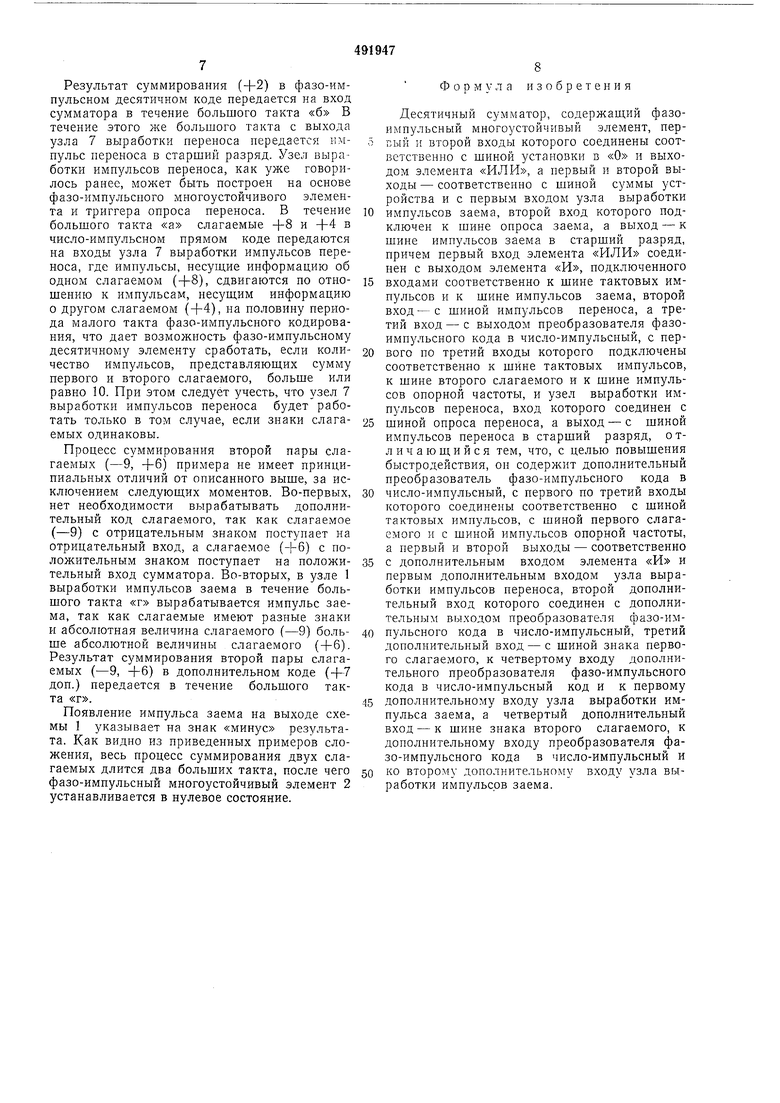

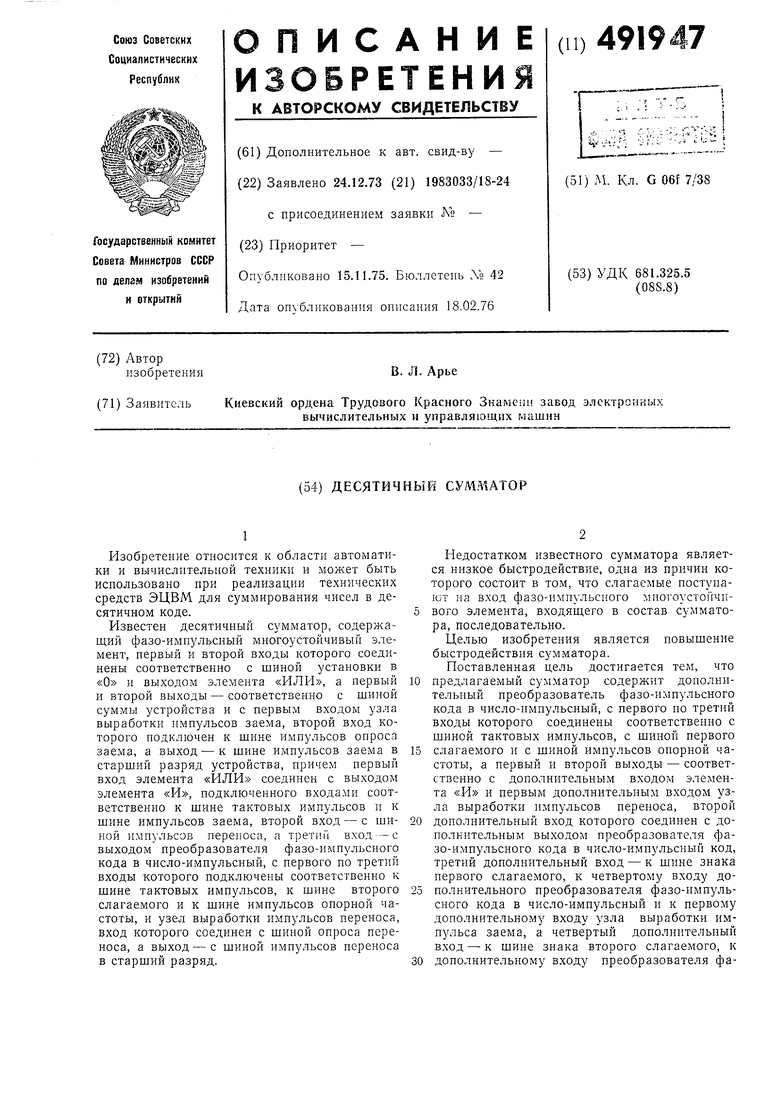

Работа устройства поясняется диаграммой, приведенной на фиг. 2. Специфика работы фазо-импульсного многоустойчивого элемента состоит в том, что одновременно на его счетный вход могут подаваться два слагаемых в число-импульсном коде только в том случае, если одно из них имеет отрицательный знак, а другое - положительный. При этом следует учесть, что слагаемое с отрицательным знаком подается на отрицательный вход сумматора и процесс суммирования этого слагаемого заключается в запрете такого числа тактируюпдих импультов, каким выражено это слагаемое, в то время как слагаемое с положительным знаком подается на положительный вход сумматора и процесс суммирования его заключается в увеличении числа тактирующих импульсов,

поступающих на счетный вход фазо-импульсного многоустойчивого элемента за время большого такта фазо-импульсного кодирования информации. Следовательно, если оба слагаемых имеют

(Г1рип,атслы11)1А знак, .то из них, которое ;ioступило па положительный вход сумматора, должно быть предварительно преобразовано в дополнительный код. Если же оба слагаел;ых ил;еют 1юло 1 ителы1ый знак, то кз них,

которое поступило на отрицательный вход сумматора, должно быть преобразовано в дополнительный код. Такое преобразование может исказить информацию о переносе в старший разряд. Известно, что перенос в старший разряд от сложения двух десятичных цифр получается только в том случае, если сумма слагаемых одного и того же знака равна или больше десяти. Как было указано выше, одно из слагаемых, равных по зна«у, преобразуется в дополнительный код. Слагаемые (одно в прямом, другое в дополнительном коде) преобразуются из фазо-импульсного кода в число-импульсный и поступают на счетпый вход фазо-импульсного многоустойчивого элемента. Действие одного из слагаемых, представленного в число-импульсном коде и поступающего на отрицательный вход сумматора, выражается в запрете определенного числа тактирующих импульсов, а

действие другого - в увеличении общего числа импульсов, ноступающих на счетный вход многоустойчивого элемента.

Таким образом, число импульсов, представляющих алгебраическую сумму слагаемых

одного и того же знака, одно из которых выражено в дополнительном коде, никогда не будет равно или больше десяти, что, в свою очередь, не даст возможности с помощью фазо-импульспой декады оценить наличие переноса.

С целью оценки переноса в предлагаемБш сумматор вводится сцециальная схема выработки переноса, построенная на основе фазоимпульсного многоустойчивого элемента. На вход этого элемента тактирующая серия импульсов не подается, и он срабатывает только от импульсов, несущих информацию о сумме слагаемых, представленных в число-импульсном коде. Если эта сумма больше или равна десяти, на выходе схемы выработки переноса появляется импульс переноса, который передается в старший разряд. В случае, когда слагаемые имеют разные знаки, может появиться необходимость в передаче в старший разряд импульса заема (случай, когда число импульсов, поступающее на отрицательный вход, больше числа импульсов, поступаюших на положительный вход сумматора). Импульсы, несущие информацию о заеме из старшего разряда, вырабатываются в схеме выработки импульсов заема. Такая схема ничем не отличается от известных схем заема в реверсивных счетчиках, построенных на фазоимпульсных многоустойчивых элементах.

Необходимость в двух отдельных схемах (одна - для образования переноса, другая - для образования заема) есть результат именно той особенности процесса суммирования, когда одно из равных по знаку слагаемых, поступающих одновременно (в течение одного большого такта) на вход сумматора, предварительно преобразуется в дополнительный код. Преобразование в дополнительный код без труда осуществляется в самих преобразователях фазо-импульсного кода, для чего используется нулевое плечо триггера, входящего в состав каждого преобразователя.

В предлагаемом сумматоре оба слагаемых подаются на вход сумматора в течение одного большого такта, а результат суммирования считывается с выхода сумматора в течение второго большого такта.

Рассмотрим работу предлагаемого сумматора на примере сложения двух независимых пар слагаемых -|-8+4 и -9+6, представленных в фазо-импульсном десятичном коде.

На временной диаграмме, представленной на фиг. 2, обозначены:

22- серия тактирующих импульсов, где О,

9, 8, 7, 6, 5, 4, 3, 2, 1 - малые такты фазо-импульсного кодирования; а, б, в, г - большие такты;

23- слагаемые +8 и +6, представленные

в фазо-импульсном коде;

24- слагаемые +4 и -9, представленные

в фазо-импульсном коде;

25- сигналы, несущие информацию о слагаемых -Ь8 и -|-6 в число-импульсном коде;

26- сигналы, несущие информацию о слагаемых -f-4 в число-импульсном дополнительном коде (-6 доп.) и (-9) в число-импульсном коде;

27- результат суммирования нервой пары

слагаемых (+2) в фазо-имцульсном

коде и результат суммирования второй пары слагаемых доп.) в фазо-импульсном дополнительном коде;

28- сигнал, несущий информацию о пере1юсе в старший разряд;

29- С:1гнал, несущий информацию о заеме

из старшего разряда.

В течение большого такта «а по каналам 16 и 15 на вход сумматора поступают сигналы, несущие информацию о слагаемых соответственно -J-4 и +8 в фазо-импульсном десятичном коде. Сигнал, несущий информацию о знаке «плюс первого слагаемого (Н-4), поступает по шине 9 на вход преобразователя 3

фазо-импульсного кода в число-импульсный. Так как слагаемое, поступающее на отрицательный вход слмматора, имеет положительный знак, то в преобразователе 3 это слагаемое преобразуется из фазо-импульсного кода в число-импульсный дополнительный код. Р1нфор:,1ация о слагаемом -}-4 в число-импульсном дополнительном коде (-6 доп.) поступает на вход элемента «И 5. Полярность нмпульсов, несущих информацию о слагаемом

(-6 доп.), обратна полярности тактирующих импульсов, что дает возможность запретить в элементе «И 5 такое количество тактпрующих импульсов, каким выражепо число импульсов, представляющее дополнительный

код слагаемого (-6 доп.).

Таким образом, за время большого такта «а на вход элемента «ИЛИ 6 поступает число импульсов, равное разности числа тактирующих импульсов и числа импульсов,

представляющих дополнительный код слагаемого (-6 доп.). В то же время на вход преобразователя 4 фазо-импульсного кода в число-импульсный поступает сигнал, несущий информацию о знаке «плюс второго слагаемого +8. Так как слагаемое, поступающее на полон нтельный вход сумматора, имеет положительный знак, то нет необходимости получать дополнительный код его. Слагаемое +8 преобразуется из фазо-импульсного кода в число-импульсный и поступает на вход элемента «ИЛИ 6. Импульсы, несущие информацию о слагаемом , сдвинуты на половину периода относительно тактирующих импульсов, что дает возможность

на выходе элемепта «ИЛИ 6 получить суммарное количество импульсов, представляющих алгебраическую сумму слагаемых (одно в прямом, другое в дополнптельном коде) и числа тактирующих импульсов за время одного большого такта.

Это суммарное количество импульсов поступает на счетпый вход фазо-импульсного многоустойчивого элемента 2. Изменение числа тактирующих импульсов

за время одного большого такта на величину, равную алгебраической сумме двух слагаемых (+8, -6 доп.), сдвигает фазу импульсов на выходе фазо-импульсного многоустойчивого элемента 2 ко времени малого такта «г

фазо-импульсного кодирования информации.

Результат суммирования (+2) в фазо-импульсном десятичном коде передается на вход сумматора в течение большого такта «б В течение этого же большого такта с выхода узла 7 выработки переноса нередается кмпульс иереноса в старший разряд. Узел выработки импульсов переноса, как уже говорилось ранее, может быть построен на основе фазо-импульспого многоустойчивого элемента и триггера опроса переноса. В течение большого такта «а слагаемые -f8 и +4 в число-импульсном прямом коде передаются на входы узла 7 выработки импульсов переноса, где импульсы, несуш,ие информацию об одном слагаемом (+8), сдвигаются по отношению к импульсам, несуш,им информацию о другом слагаемом (+4), на половину периода малого такта фазо-импульсного кодирования, что дает возможность фазо-импульсному десятичному элементу сработать, если количество импульсов, представляюших сумму первого и второго слагаемого, больше или равно 10. При этом следует учесть, что узел 7 выработки импульсов переноса будет работать только в том случае, если знаки слагаемых одинаковы.

Процесс суммирования второй пары слагаемых (--9, +6) примера не имеет принципиальных отличий от описанного выше, за исключением следующих моментов. Во-первых, нет необходимости вырабатывать дополнительный код слагаемого, так как слагаемое (-9) с отрицательным знаком поступает на отрицательный вход, а слагаемое (+6) с положительным знаком поступает на положительный вход сумматора. Во-вторых, в узле 1 выработки импульсов заема в течение большого такта «г вырабатывается импульс заема, так как слагаемые имеют разные знаки и абсолютная величина слагаемого (-9) больше абсолютной величины слагаемого (+6). Результат суммирования второй пары слагаемых (-9, +6) в дополнительном коде (+7 доп.) передается в течение большого такта «г.

Появление импульса заема на выходе схемы 1 указывает на знак «минус результата. Как видно из приведенных примеров сложения, весь процесс суммирования двух слагаемых длится два больших такта, после чего фазо-импульсный многоустойчивый элемент 2 устанавливается в нулевое состояние.

Формула изобретения

Десятичный сумматор, содержащий фазоимпульсный многоустойчивый элемент, первый и второй входы которого соединены соответственно с шиной установки в «О и выходом элемента «ИЛИ, а первый и второй выходы - соответственно с шиной суммы устройства и с первым входом узла выработки

импульсов заема, второй вход которого подключен к шине опроса заема, а выход - к шине импульсов заема в старший разряд, причем первый вход элемента «ИЛИ соединен с выходом элемента «И, подключенного

входами соответственно к шине тактовых импульсов и к шине импульсов заема, второй вход-с шиной импульсов переноса, а третий вход - с выходом преобразователя фазоимпульсного кода в число-импульсный, с первого по третий входы которого подключены соответственно к шине тактовых импульсов, к шине второго слагаемого и к шине импульсов опорной частоты, и узел выработки импульсов переноса, вход которого соединен с

шиной опроса переноса, а выход - с шиной импульсов переноса в старший разряд, отличающийся тем, что, с целью повышения быстродействия, он содержит дополнительный преобразователь фазо-имнульсного кода в

число-импульсный, с первого по третий входы которого соединены соответственно с шиной тактовых импульсов, с шиной первого слагаемого и с шиной импульсов опорной частоты, а первый и второй выходы - соответственно

с дополнительным входом элемента «И и первым дополнительным входом узла выработки импульсов переноса, второй дополнительный вход которого соединен с дополнительным выходом преобразователя фазо-импульсного кода в число-импульсный, третий дополнительный вход - с шиной знака первого слагаемого, к четвертому входу дополнительного преобразователя фазо-импульсного кода в число-импульсный код и к первому

дополнительному входу узла выработки импульса заема, а четвертый дополнительный вход - к шине знака второго слагаемого, к дополнительному входу преобразователя фазо-импульсного кода в число-импульсный и

ко второму дополнительному входу узла выработки импульсов заема.

1S 17

15

17

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1965 |

|

SU169891A1 |

| Фазо-импульсный сумматор | 1977 |

|

SU651343A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| Оптоэлектронный десятичный сумматор | 1978 |

|

SU840895A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Устройство для суммирования | 1976 |

|

SU674018A1 |

| МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1969 |

|

SU244713A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

00675543:1 3S --755 3 2 П367 . 1 :9S7S в

22 -jjLELai a.fiLajt3JiJLaLirp-aJL8.J.iuaaA ifLSJLiuiBfigBiinim

+ &

,23

+ Ч9

2

-g

r

26

B3 i ly

i/еренас

Авторы

Даты

1975-11-15—Публикация

1973-12-24—Подача