го селектора-мультиплексора образует информационный вход устройства, а выходы триггеров группы образуют второй информационный выход устройства ; первая группа выходов выходного регистра соединена соответственно с группой разрешающих входов первого и второго селекторов-мультиплексоров, информационными входами первого, второго и третьего селекторов, адресным входом одноразрядного оперативного- запоминающего узла и группой управляющих входов выходного дешифратора, выходы которого соединены соответственно с установочными входами триггеров группы, группа выходов первого селектора-мультиплексора соединена с третьим информационным входом мультиплексора данных, у вторьм информационным входом канальных приемопередатчиков и информационным входом второго селекторамультиплексора, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с информационным входом блока вычисления булевых функций, выход которого соединен соответственно с первым входом первого элемента И, четвертым информационным входом мультиплексора данных и информационным входом одноразрядного оперативного запомивакщег узла, выход которого соединен с вторым входом первого элемента ИЛИ, третий вход .которого соединен с выходом второго элемента И и первым входом второго элемента ИЛИ, выход которого соединен с входом выборки младших разрядов данных выходного дешифратора, вход выборки старших разрядов данных которого соединен соответственно с первым управляющим входом второго селектора-мультиплексора, стробирующим входом одноразрядного оперативного запоминающего узла, выходом первого элемента задержки и входом второго элемента задержки, выход которого соединен с запускающим входом блока вычисления булевых функций, разрешакяций вход которого . соединен с выходом шифратора, вход которого соединен с второй группой выходов выходного регистра, третья группа выходов которого соединена с входом выборки типа операции одноразрядного оперативного запоминакяцего узла, разрешанхций вход которого соединен с выходом первого селектора

выход второго селектора соединен с вторым управляющим входом второго селектора-мультиплексора, выход третьего селектора соединен с разрешающим входом выходного дешифратора, второй вход первого элемента И и первый вход второго элемента И соединеныс первым выходом регистра состояний, второй выход которого соединен с вторым входом второго элемента И, выход первого элемента И соединен с вторым входом второго элемента ИЛИ, вход первого элемента задержки соединен с выходом третьего элемента (И, первьй вход которого соединен с выходом Вывод 2 дешифратора управляющих сигналов,выхЬд вывода данных которого соединен с вТорым входом третьего элемента И.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок вычисления булевых функций содержит дешифратор, триггер, элемент НЕ, десять элементов И и три элемента ИЛИ, , вход дешифратора образует разрешающий вход блока, синхронный вход триггера образует запускающий вход блока, первьй вход первого элемента И соединен с входом элемента -НЕ, первыми входами второго и третьего элементов И, первого элемента ИЛИ и образует информационный вход блока, пергъш выход триггера соединен с вторым входом третьего элемента И, первыми входами второго элемента ИЛИ и четвертого элемента И и образует выход блока, при этом в блоке вычисления булевых функций первый, второй третий, четвертый, пятий, шестой, седьмой и восьмой выходы дешифратора соединены с вторым входом первого элемента И, первыми входами пятого, шестого, седьмого, восьмого,.девятого и десятого элементов И, вторым входом четвертого элемента И соответственно, первьй, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы третьего элемента ИЛИ соединены с выходами первого, четвертого, пятого, шестого, седьмого, восьмого, девятого и десятого элементов И соответственно, выход третьего элемента ИЛИ соединен с информационным входом триггера, второй выход которого соединен с вторыми входами второго, десятого элементов И н первого элемента ИЛИ, выход элемента НЕ соединен с

вторыми входами пятого элемента И и седьмого и восьмого элементов И соевторого элемента ИЛИ, выход которого динены с выходами второго, третьего соединен с вторьм входом девятого элементен И и первого элемента ИЛИ элемента И, 1зторые входы шестого, соответственно.

1164688

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1462341A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1985 |

|

SU1315988A1 |

| Устройство для подключения абонентов к магистрали ЭВМ | 1988 |

|

SU1608681A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1411760A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1401470A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1640702A1 |

1. УСТРОЙСТВО ДЛЯ ПАРАГЙЕЛЬНОГО ОБМЕНА ИНФОРМАЦИЕЙ, содержащее блок канальных передатчиков, блок канальных приемопередатчиков,выходной регистр,регистр состояния,мультиплексор данных,дешифратор адреса и дешифраг тор управлякяцих сигналов, причем группа вькодов блока канальных передатчиков образует первьй информационный выход устройства, группа входов-выходов блока канальных приемопередатчиков образует информационный вход-выход устройства, первая группа информационных входов дешифратора адреса является адресным входом устройства, группа входов-выходов дешифратора управляющих сигналов образует управляю1цие входы-выходы устройства, группа выходов блока канальных приемопередатчиков соединена с группой информационных входов выход- ного регистра, группой информационных входов регистра состояния, второй группой информационных входов дешифратора адреса и группой адресных входов дешифратора управлякицих сигналов соответственно, выход дешифратора адреса соединен с входом выборки устройства дешифратора управляющих сигналов, выход ввода которого соединен с разрешающими входами блока канальных передатчиков и блока канальных приемопередатчиков, первая . группа информационных входов которого соединена с вьпсодом мультиплексора данных, управляющий вход которого соединен с адресным выходом дешифратора управляющих сигналов, выход Вывод 2 которого соединен с входом выборки выходного регистра, первая группа ииходов которого соединена с первым информационгалм входом блока канальных передатчиков и группой адресных входов мультиплексора данных, первый информационный (Л вход которого соединен с первьм выходом регистра состояний, второй выход которого соединен с вторым информационным входом мультиплексора данных, вход выборки регистра состояний соединен с выходом Вывод О дешифратора управлякяцих сиг-налов , вторая группа выходов выход Од 4 ного регистра соединена с вторым информационным входом блока канальОд 00 00 ных передатчиков, третий информационный вход которого соединен с третьей группой выходов выходного регистра,о тличающееся .тем, что, с целью уменьшения времени обработки вводимой в процессор информации, в него введены два входных селектора-мультиплексора, три селектора, одноразрядный. оперативш 1й запоминающий узел, блок вычисления булевых функций, три элемента И, два элемента ИЛИ, два элемента задержки, выходной дешифратор, шифратор и группа триггеров, причем группа информационных входов перво

1

Изобретение относится к цифровым вычислительным машинам и может бытьиспользовано в качестве устройств ввода и обработки информации, отличающихся заданием програм обработки одновременно с вводом подлежащих обработке данных.

Известно устройство параллельного обмена, предназначенное для подсоединения к каналу ЭВМ Электроника 60 внешних устройств, включающее в себя ячейку коммутации и развязки, ячейку выходного регистра данных и канальных усилителей, ячейку регистра состояния, ячейку регистра адреса и дешифрации управляющих сигналов, соединенные соответствующим образом с каналом ЭВМ и внешними устройствами l .

Однако в случае использования указанного устройства в составе микроЭВМ при решении задач логического управления оно требует значительных затрат времени на обмен данными, а также большой объем программ, хранящих управляющую информацию для обмена данными.

: Известно устройство параллельного обмена, входящее в состав ЭВМ Электроника-60, предназначенное для подсоединения к каналу ,ЭВМ внешних устройств, обменивающихся с ЙВМ даннымив параллельном коде, и содержащее блок канальных передатчиков, блок канальных приемопередатчиков, выходной регистр, регистр состояния, мультиплексор данных, дешифратор адреса и дешифратор управлякицих сигналов, причем группа выходов блока канальных передатчиков образует первый инфор- мационный выход устройства, группа входов-выходов блока канальных приемопередатчиков образует адресноинформационный вход-выход устройства, вход дешифратора адреса является управляихцим входом устройства группа

входов-выходов дешифратора управляющих сигналов образует управляюпше входы-выходы устройства, группа выходов блока канальных приемопередатчиков соединена с группой информа- . ционных входов выходного регистра, группой информационных вxdдoв регистра состояния, группой адресных входов дешифратора адреса и группой адресных входов дешифратора управляющих сигналов соответственно, выход дешифратора адреса соединен с входом выборки устройства дешифратора управляющих сигналов, выход ввода которого соединен с управляющим входом блока канальных передатчиков и управляющим входом блока канальных приемопередатчиков, выход Вывод-2 дешифратора управляющих сигналов соединен с входом выборки выходного регистра, выход Вывод О дешифратора управлякицих сигналов соединен с управлякмцим входом регистра состояния, адресный выход дешифратора управляющих сигналов соединен с управляющим входом мультиплексора , первый выход выходного регистра соединен с первым входом блока канальных передатчиков и первым вхог дом мультиплексора данных, второй выход выходного регистра соединен с вторым входом блока канальных передатчиков, третий выход выходного регистра соединен с третьим входом блока канальных передатчиков, {выход мультиплексора данных соединен с пер вым информационным входом блока какальных приемопередатчиков, выходы выходного регистра являются выходами устройства, второй вход блока канальных приемопередатчиков и третий групповой вход мультиплексора данных являются входами устройстг. ва 2.

Однако в случае использования известного устройства в составе микро-ЭВМ при:решении задач логичес кого управления оно требует значительных затрат времени на обмен данными, а также большой объем программ, хранящих управляющую информацию для обмена данными. Задача логического управления для микро-ЭВМ формируется следующим образом: реализовать средствами, входящими в микро-ЭВМ, управлякяций автомат, комбинационная часть которого реализует некоторую систему булевый функций. Использование микро-ЭВМ при обмене через устройство параллельного обмена (по 16 разрядов) показало, что затраты времени на вычисление значения одного выходного сигнала по описыванлцей его булевой функции составляют i 200-300 МКС. При числе функций в системе булевых функций 128256 производительность управляющего автомата недостаточна для целого ряг да задач управления. В настоящее время общее количество входов и выходов таких автоматов колеблется в пределах от ста до тысячи реализация этих автоматов с применением УПО приводит к значительным зат ратам времени центрального процессеpa на подготовку и обмен данных. Цель изобретения - уменьшение вре мени обработки вводимой в процессор информации путем обеспечения предобработки входного потока данных в соответствии с булевыми функциями непосредственно в устройстве. Поставленная цель достигается тем что в устройство, содержащее блок канальных пере датчиков, блок канап ьны приемопередатчиков, выходной регистр регистр состояния, мультиплексор дан ных, дешифратор адреса и дешифратор управляющих сигналов, причем группа выходов блока канальных передатчиков образует первый информационный выход устройства, группа входов-выходов блока канальных приемопередатчиков образует информационный вход-выход устройства, первая группа информационных входов дешифратора адреса явля ет.ся адресным входом устройства, . группа входов-выходов дешифратора управляющих сигналов образует управ ляющие входы-выходы устройства, груп па выходов блока канальных приемопередатчиков соединена с ;группой инфо мационных входов выходного регистра. группой информационных входов регистра состояния, второй группой информационных входов дешифратора адреса и группой адресных входов дешифратора управляющих сигналов соответственно, выход дешифратора адреса соединен с входом выборки устройства дешифратора управляющих сигналов, выход ввода которого соединен с разрешающими входами блока канальных передатчиков и блока канальных приемопередатчиков, первая группа информационных входов которого соединена с выходом мультиплексора данных, управляющий вход которого соединен с адресным выходом дешифратора управляюпщх сигналов, выход Вывод 2 которого соединен с входом выборки выходного регистра, первая группа выходов которого соединена с первым информационным входом блока канальных передатчиков и группой адресных входов мультиплексора данных, первый информационный вход которого соединен с первым выходом регистра состояний, второй выход которого соединен с вторым информационным входом мультиплексора данных, вход выборки регистра состояний соединен с выходом Вывод О дешифратора управляющих сигналов, вторая группа выходов выходного регистра соединена с вторым информационным входом блока канaл ныx передатчиков, третий информационный вход которого соединен с третьей группой выходов выходного регистра, введены два входных селектора-мультиплексора, три селектора, одноразрядный оперативный sanoiejнакщий узел СОЗУ), блок вычисления булевых функций, три элемента И, два элемента ИЛИ, два элемента задержки, выходной дешифратор, шифратор и группа триггеров, причем группа информационных входов первого селектора-мультиплексора образует информационньй вход устройства, а выходы триггеров группы образуют второй информационный выход устройства, первая группа выходов выходного регистра соединена соответственно с группой разрешающих входов первого и второго селекторов-мультиплексо-. ров,. информационными входами первого, второго и третьего селекторов, адресным вхоДом одноразрядного ОЗУ и группой управлякяцих входов выходного дешифратора, выходы которого

соединены соответственно с устйно- вочными входами триггеров группы, группа выходов первого селекторамультиплексора соединена с третьим информационным входом мультиплексора данных, вторым.информационным входом канальных приемопередатчиков и информационным входом второго селектора-мультиплексора, I выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с информационным входом блока вычисления булевых функций, выход которого соединен соответственно с первым входом первого элемента И, четвертым информационным входом мультиплексора данных и информационным входом одноразрядного ОЗУ, выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом второго элемента И и первым входом второго элемента ИЛИ, выход которого соединен с входом выборки младших разрядов данных выходного дешифратора, вход выборки старших разрядов данных которого соединен

соответственно с первым уПравляняцим I

входом второго селектора-мультиплексора, стробирующим входом одноразрядного ОЗУ, выходом первого элемент задержки и входом второго элемента задержки, выход которого соединен с запускающим входом блока вычисления булевых функций, разрешающий вход которого соединен с выходом шифратора, ВХОД которого соединен с второй группой выходов выходного регистра, третья группа выходов которого соединена с входом выборки типа операции одноразрядного ОЗУ, разрешающий вход которого соединен с выходом первого селектора, выход второго селектора соединен с вторым управляющим входом второго селектора-мультиплексора, вы хЬд третьего селектора соединен с разрешакицим входом выходного дешифратора, второй вход первого элемента И и первый вход второго элемента И соединены с первым выходом регистра сое- тояний, второй выход которого соединен с вторым входом второго элемента И, выход первого элемента И соединен с вторым входом второго элемента ИЛИ, вход первого элемента задержки соединен с выходом третьего элемета И, первый вход которого соединен с выходом Вывод 2 дешифратора управляющих сигналов, выход вывода данных которого соединен с вторым входо третьего элемента И.

Кроме того, блок вычисления булевых функций содержит дешифратор, триггер, элемент НЕ, десять элементов И и три элемента ИЛИ, причем вход дешифратора образует разрешающий вход блока, синхронный вход триггера образует запускающий вход блока, первый вход первого элемента И соединен с входом элемента НЕ, первыми входами второго и третьего элементов И, первого элемента ИЛИ и образует информационный вход блока, первый выход триггера соединен с вторым входом третьего элемента И, первыми входами второго элемента ИЛИ и четвертого элемента И и -образует вь1ход блока, при этом в блоке вычисления булевых функций первый, второй, третий, четвертый, пятьй, шестой, седьмой и восьмой выходы дешифратора -соединены с вторым входом первого элемента И, первыми входами пятого, шестого, седьмого, восьмого, девятого и десятого элементов И, вторым входом четвертого элемента И соот- ветственно,первый, второй, третий, четвертьй, пятьй, шестой, седьмой и восьмой входы третьего элемента ИЛИ соединены с выходами первого, четвертого, пятого, шестого, седьмого, восьмого, девятого и десятого элементов И соответственно, выход третьего элемента ИЛИ соединен с информационным входом триггера, второй выход которого соединен с вторыми входами второго, десятого элементов И и первого- элемента ИЛИ, выход элемента НЕ соединен с вторыми входами пятого элемента И и второго элемента ИЛИ, выход которого соединен с вторым входом девятого элемента И, вторые входы шестого, седьмого и восьмого элементов И соединены с выходами второго, третьего элементов И и первого элемента ИЛИ соответственно., .1

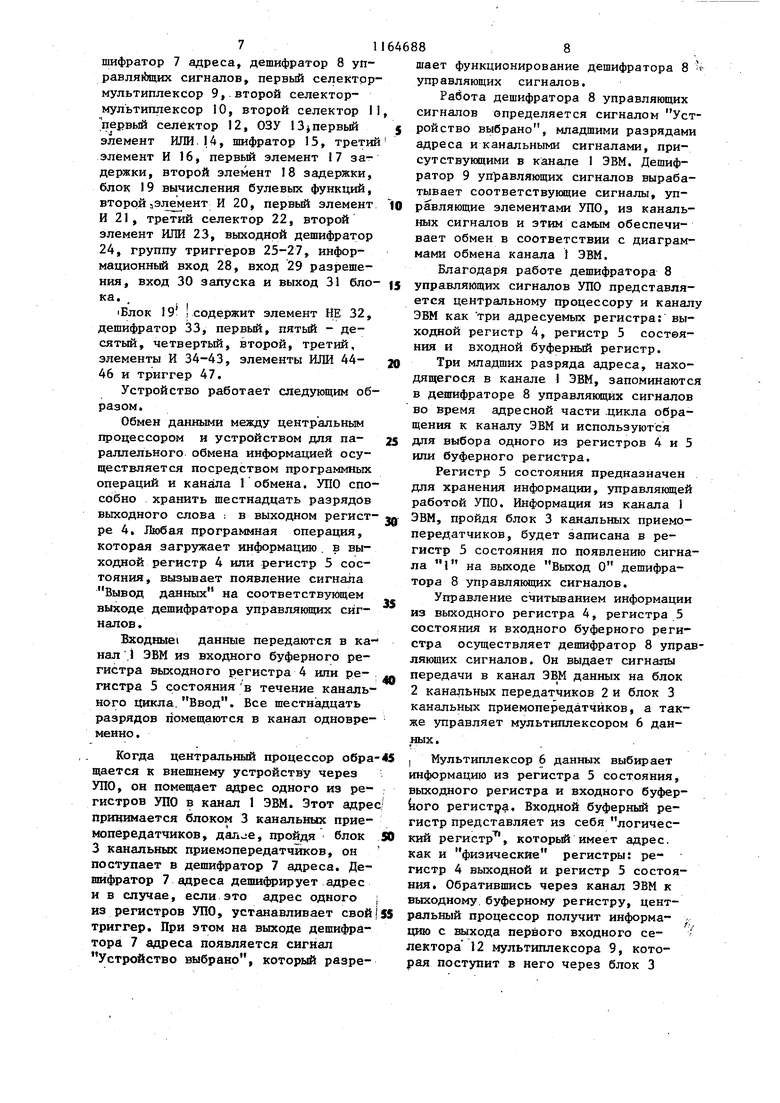

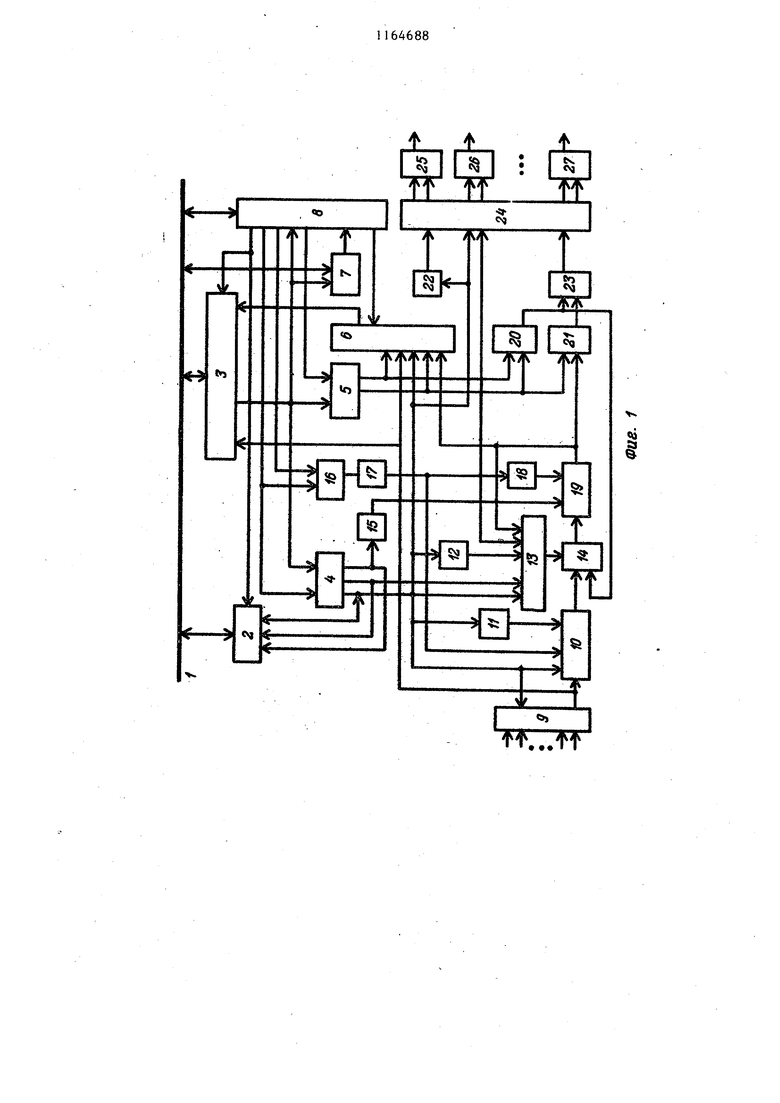

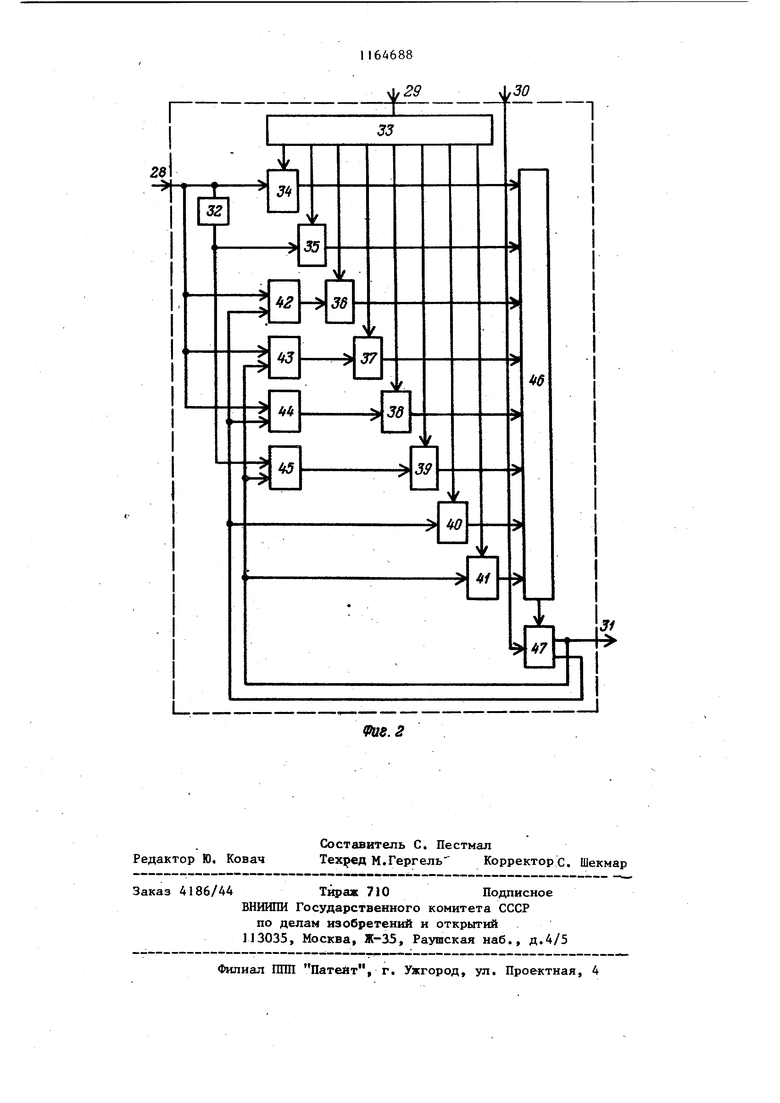

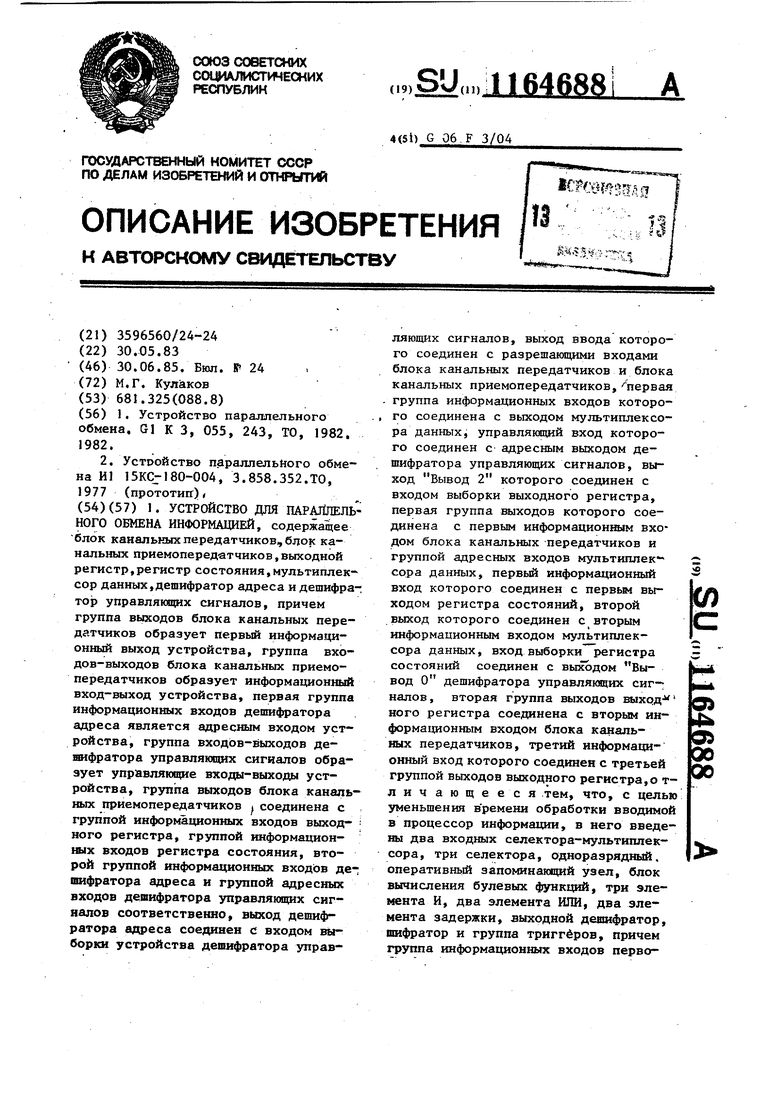

На фиг. 1 изображена структурная

схема предлагаемого устройства; на фиг. 2 - блок вычисления булевых

.функций,

Устройство содержит (фиг. 1} шину 1 ЭВМ, блок 2 канальных передатчиков,

.блок 3 канальных приемопередатчиков, выходной регистр А, регистр 5 состояния, мультиплексор 6 данных, дешифратор 7 BfSfeca, дешифратор 8 ytiравляйлцих сигналов, первый селектррмультиплексор 9, второй селектормультгашексор 10, второй селектор И Ъервый селектор 12, ОЗУ 13 первьй элемент ИЛИ.14, шифратор 15, третий элемент И 16, первьй элемент 17 задержки, второй элемент 18 задержки, блок 19 вычисления булевых функций. вторрйзэлемент И 20, первый элемент И 21, третий селектор 22, второй элемент ИЛИ 23, выходной дешифратор 24, группу триггеров 25-27, информационньй вход 28, вход 29 разрешения, вход 30 запуска и выход 31 блоБлок 19 содержит элемент НЕ 32, дешифратор 33, первьй, пятьй - десятый, четвертьй, второй, третий, элементы И 34-43, элементы ИЛИ 4446 и триггер 47. Устройство работает следующим образом. Обмен данными между центральным процессором и устройством для параллельного обмена информацией осуществляется посредством программных операций и канала 1 обмена. УПО способно хранить шестнадцать разрядов выходного слова : в выходном регистре 4. Любая программная операция, которая загружает информацию . в выходной регистр 4 или регистр 5 состояния, вызывает появление сигнала Вывод данных на соответствующем выходе дешифратора управляющих сигналов. Входные данные передаются в канал ,1 ЭВМ из входного буферного регистра выходного регистра 4 или регистра 5 С.ОСТОЯНИЯ в течение канального Цикла.Ввод. Все шестнадцать разрядов помещаются в канал одновременно. Когда центральный процессор обра щается к внешнему устройству через УПО, он помещает адрес одного из регистров УПО в канал 1 ЭВМ. Этот адре принимается блоком 3 канальных приемопередатчиков, , пройдя блок 3 канальных приемопередатчиков, он поступает в дешифратор 7 адреса. Дешифратор 7 адреса дешифрирует адрес и в случае, если это адрес одного из регистров УПО, устанавливает свой триггер. При этом на выходе дешифратора 7 адреса появляется сигнал Устройство выбрано, который разрешает функционирование дешифратора 8 4 управляющих сигналов. Работа дешифратора 8 управляющих сигналов определяется сигналом Устройство выбрано, младшими разрядами адреса и канальными сигналами, присутствующими в канале I ЭВМ. Дешифратор 9 управляющих сигналов вырабатывает соответствующие сигналы, управляющие элементами УПО, из канальных сигналов и этим самым обеспечивает обмен в соответствии с диаграмнами обмена канала 1 ЭВМ. Благодаря работе дешифратора 8 управляющих сигналов УПО представляется центральному процессору и каналу ЭВМ как три адресуемых регистра: выходной регистр 4, регистр 5 соствяния и входной буферный регистр. Три младших разряда адреса, находящегося в канале 1 ЭВМ, запоминаются в дешифраторе 8 управлякицих сигналов во время адресной части .цикла обращения к каналу ЭВМ и используются для выбора одного из регистров 4 и 5 ипи буферного регистра. Регистр 5 состояния предназначен для хранения информации, управляющей работой УПО. Информация из канала 1 ЭВМ, пройдя блок 3 канальных приемопередатчиков, будет записана в регистр 5 состояния по появлению сигнала 1 на выходе Выход О дешифратора 8 управляющих сигналов. Управление считыванием информации из выходного регистра 4, регистра 5 состояния и входного буферного регистра осуществляет дешифратор 8 управляющих сигналов. Он выдает сигналы передачи в канал ЭВМ данных на блок 2 канальных передатчиков 2 и блок 3 канальных приемопередатчиков, а также управляет мультиплексором 6 данных. I Мультиплексор 6 данных выбирает информацию из регистра 5 состояния, выходного регистра и входного буфер ого регистра. Входной буферный регистр представляет из себя логический регистр, которьй имеет адрес, как и физические регистры: регистр 4 выходной и регистр 5 состояния. Обратившись через канал ЭВМ к выходному, буферному регистру, центральный процессор получит информа- цию с выхода первого входного селектора 12 мультиплексора 9, которая поступит в него через блок 3 канальных приемопередатчиков и чере мультиплексор 6 данных и блок 3 канальных приемопередатчиков. Через мультиплексор 6 данных в канал ЭВМ передается содержимое мпадшего байта того регистра,код которого присутствует на выходе Адрес дешифратора 8 управляющих сигналов. Содержимое старшего байт выходного регистра 4 поступает через блок 2 канальных передатчиков, содержимое старшего байта входного бу фера регистра поступает через блок 3 канальных приемопередатчиков. Информация из канала ЭВМ, пройдя блок 3 канальных приемопередатчиков будет записана в выходной регистр 4 по появлению сигнала 1 на выходе Выход 2 дешифратора 8 управлякядих сигналов. Таким образом, блок 2 канальных передатчиков, блок 3 канальных мопередатчикой, выходной регистр 4 регистр 5 состояния, мультиплексор 6 данных, дешифратор 7 адреса, дешиф ратор 8 управлякщих сигналов функционируют аналогично прототипу. После записи информации из канал ЭВМ в выходной регистр 4 он хранит следующие данные: адрес выборки входа, выхода или слова ОЗУ, призна записи в ОЗУ, код операции логического блока. Адрес выборки требует для хранения девяти-двенадцати разрядов в зависимости от количества входов, выходов и объема ОЗУ, щшзнак записи - один разряд, код операции логического блока - трех-пяти разрядов в зависимости от количества операций логического блока. Адрес выборки входа, выхода илиг слова ОЗУ с первого выхода выходного регистра 4 поступает на оба входных селектора-мультиплексора 9 и to, три селектора И, 12 и 22, мультиплексор 6 данных и выходной дешифратор 24. Признак записи с второго выхода выходного регистра 4 поступает на вход запись-чтение ОЗУ 13. Код операции процессора с третьег выхода выходного регистра 4 поступае на вход .шифратора 15. Первый входной селектор-мультяйяе i сор 9 выполняет коммутацию входного поиска данных в шестнадцати каналах в соответствии с адресом выборки по ступившим из (ВЫХОДНОГО регистра 4 .- Второй входной селектор-мультиплексор. 10 предназначен для выборки одного из выходных каналов первого входного селектора-мультиплексора 9 в соответствии с четырьмя разрядами адреса выборки, поступившими из выходного регистра 4. Второй селектор 11 дешифрирует адрес выборки и в случае, если это адрес входного сигнала, вырабатывает сигнал разрешения, поступающий на строби15ующий вход второго входного селектора- . мультиплексора 10, разрешая тем самым появление информации на его выходе. Второй селектор И реализуется в обще случае на ПЗУ с организацией N сюв разряд, при этом обеспечивается гибкая система адресации входов, выходов и ОЗУ. Поскольку адрес выборки хранится в выходном регистре 4, то данные на выходе первого входного селекторамультиплексора 9 будут сохранять фик- срфованное значение до перезаписи информации в выходном регистре 4, Информация на выходе второго вход-но го селектора-мультиплексора 10 присутствует лишь в течение канального цикла Вывод, когда производится обращение к выходному регистру 4, поскольку на первый стробирукмций вход второго входного селектора-мультиплексора 10 подан сигнал с выхода первого элемента 17 задержки. Этим достигается простая коммутация информации через первьй элемент ИЛИ 14 на вход логического блока. Совместной работой первого и второго входных селекторов мультиплексоров и второго селектора 11 обеспечивается считывание значения одного из входных сигналов и появление этого значения на выходе второго селектора-мультиплексора Ш. Это значение сигнала, пройдя через первый элемент ИЛИ 14, поступит на вход логического блока 19. Совместной работой первого.входного Селектора-мультиплексора 9, вто- .. ого селектора 11 и выходного региг тра 4 обеспечивается прием, хранеие и передача в канал ЭВМ значений естнадцати входных сигналов, выбанных первым селектором-мультиплекором 9 в соответствии с адресом вы- ; орки, поступившим из выходного регистра 4. II Центральный процессор, запасав выходной регистр 4 адрес выборки в течение канального цикла Вывод, считает значение шестнадцати входны сигналов в канальном цикле Ввод, обратившись к входному буферному регистру данных УПО и П. ОЗУ 13 имеет организацию М-слов X 1 разрядов и предназначено для хранения сигналов, характеризующих состояние запоминающей части автом та. Адрес слова ОЗУ 13, в которое ведется запись информации или из которого информация считывается, определяется адресом выборки, посту пившим из выходного регистра 4. Тип операции ОЗУ 13, т.е. запись или чтение, определяется признаком вы вода, поступившим из выходного регистра 4, Данные в ОЗУ 13 поступают с выхода логического блока 19. Первый селектор 12 дешифрирует а рее выборки и в случае, если это адрес ОЗУ 13, вырабатывает сигнал разрешения, который поступает на вход выбор,ки ОЗУ 13. Этим разрешается запись или чтение информации в ОЗУ 13. Первый селектор 12 реализован на ПЗУ с организацией N слов X 1 разряд. Данные на выходе ОЗУ присутствуют только в течение канал ного цикла Вывод, поскольку он стробируется сигналом с выхода первого элемента задержки. Данные с вы хода ОЗУ 13, пройдя через первую схему ИЛИ 14, поступают на вход бло ка 19. Логический блок предназначен для выполнения булевых операций типа И, ИЛИ, НЕ, ЗАПОМНИТЬ и т.д. Эти опера ции выполняются между данными (один разряд), присутствующими на.его вхо де, и Содержимым,регистра-аккумулятора (один /разряд). Результат опера ции присутствует на выходе логического блока до появления результата следующей по порядку операции, В качестве примера рассмотрена реализация следующих логических опе раций : Л А .I-А, X А , X л , X V , TV А -А, , , 8 где X - данные на входе 28; А - содержимое регистра-аккумулятора (D-триггер 47); -- операция записи в А), Элементы 32, 42 и 45 обеспечивают выполнение упомянутых логических операций между входными данными и содержимым регистра-аккумулятора (D -триггер 47). Дешифратор 33,группа элементов И 34-41 и третий элемент ИЛИ 46 обгразуют селектор-мультиплексор 8 каналов в 1, который коммутирует требуемый результат операции на информационный вход D -триггера 47. Тип логической операции задается кодом на входе дешифратора, На синхровход D -триггера 47 TIOдается строб с выхода второго элемента 18 задержки. В качестве выхода логического блока используется единичный выход D триггера 47, нулевой выход используется при выполнении логических операций. Обычно число логических операций равно 16 - 64, причем широко- используется подмножество операций, для чего приходится использовать шифратор 15. Данные с выхода блока 19 поступают на один из каналов мультиплексора 6 данных, на вход ОЗУ 13 или на вход первого элемента И 21. Регистр 5 состояния управляет выводом значений выходных сигналов. Он имеет два разряда, состояния этих разрядов могут быть считаны через мультиплексор 6 данных в канал ЭВМ. Первый разряд регистра состояния с его первого выхода поступает на вход второго элемента И 20. Он предназначен для передачи значения выходного сигнала или сигнала на вход логического блока 19 через канал ЭВМ I и регистр 5 состояния логическому блоку 19 или выходному дешифратору 24. Второй разряд регистра 5 состояния с его второго выхода управляет передачей значения сигнала в выходной дешифратор 24 либо из регистра 5 состояния либо с выхода логического блока 19, Если этот разряд имеет состояние 1, то в выходной дешифратор 24 на его младший управляюпц й вход поступают данные из первого разряда регистра 5 состояния через второй элемент И 20 и второй элемент ИЛИ 23. Эти же данные поступают на вход блока 19 через второй элемент И 20 и первый элемент ИЛИ 14. Если второй разряд регистра 5 состояния имеет со тояние О то в выходной Дешифратор 24 на его младший управлягаций вход поступит разряд данных с выхода логи ческого блока 19 через первый элемен И 21 и второй элемент ИЛИ 23. Третий селектор 22 дешифрирует адрее выборкии,в случае,если это адрес выходного сигнала, вырабатывает Сигнал разрешения, который поступает на вход выборки выходного дешифратора 24, разрешая его работу. Третий селектор 22 реализован на ПЗУ с организацией N слов х 1 .разряд. Выходной дешифратор 24 предназначен для управления состояниями группы триггеров 25 - 27. В случае, если на младшем управляющем -входе выходного дешифратора 24 сигнал имеет значение О, то при обращении к выходному дешифратору 24 выбирается нечетный выход, а если 1 то четный. Какой из триггеров при этом меняет или подтверждает свое состояние определяет адрес выборки, поступивший из выходного регистра 4 на старш ие управляющие .входы дешифратора 24. Совместная работа узлов УПО синхронизируется сигналом Вывод данных, который последовательно проходит третий элемент И 16, первый элемент 17 задержки и второй элемент 18 задержки. При появлении сигнала Вывод данных вместе с сигналом Вывод 2 на соответствующих выходах дешифратора 8 управляющих сигналов произойдет запись информации в выходной регистр 4, а также в зависимости от состояния выходов Делекторов 11,12 и 22 будет выполнена одна из операций: считывание значения одного из входов первым и вторым входными селекторами-мультиплексорами 9 и 10 либо обращение к ОЗУ 13, либо устаноь ка одного из триггеров выходным дешифратором 24. После появления сигнала Вывод данных на выходе второго элемента задержки блок 19 выполнит логическую операцию над данными. Таким образом, предлагаемым устройством обеспечивается гибкая предобработка, ввод и вывод данных, необходимая для реализации управлякяцего автомата в соответствии с системой булевых функций. При этом в качестве аргументов могут быть использованы данные на входе первого входного селектора-мультиплексора 9, данные из ОЗУ 13 или с выхода регистра 5 состояния. Вычисленные значения могут быть помещены ;в ОЗУ 13, переданы в канал ЭВМ через мультиплексор 6 данных либо использоваться для управления состоянием триггеров 25 - 27, т.е. изменения значений выходных сигналов УПО. Управление состоянием триггеров 25-27 обеспечивается также совмест ной работой выходного регистра 4 и регистра 5 состояния. УПО работает только под управлением центрального процессора ЭВМ, в состав которого оно входит. Использование изобретения позволяет расширить.функциональные возможности устройства путем обеспечения предобработки входного канала данных в соответствии с булевыми функциями непосредственно в устройстве параллельного обмена информацией, что при общем числе входных и выходных сигналов большем тридцати двух дает экономию памяти микро-ЭВМ и повьппает ее быстродействие, В одном из случаев конкретного применения производительность ЭВМ была повышена на порядок, объем памяти сокращен в пять раз,

ip «)

V.

«о

С

tT...tT

90S.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство параллельного обмена, G1 К 3, 055, 243, ТО, 1982 | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-06-30—Публикация

1983-05-30—Подача