. 11462341

Изобретение относится к вычислительной технике и может быть использовано для сопряжения двух элект-- ровных вычислительных машин в информационно-измерительных и автоматизированных системах управления..

Цель изобретения - повышение пропускной способности устройства за счет организации режима двунаправлен- Q него прямого доступа.

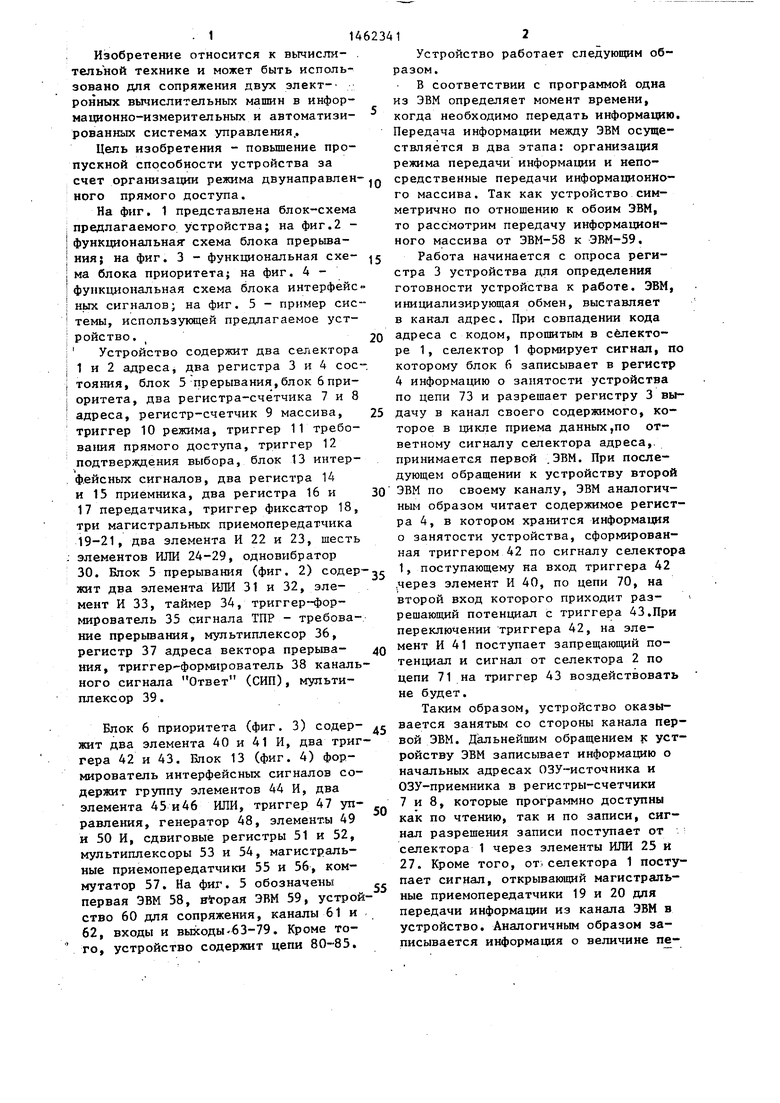

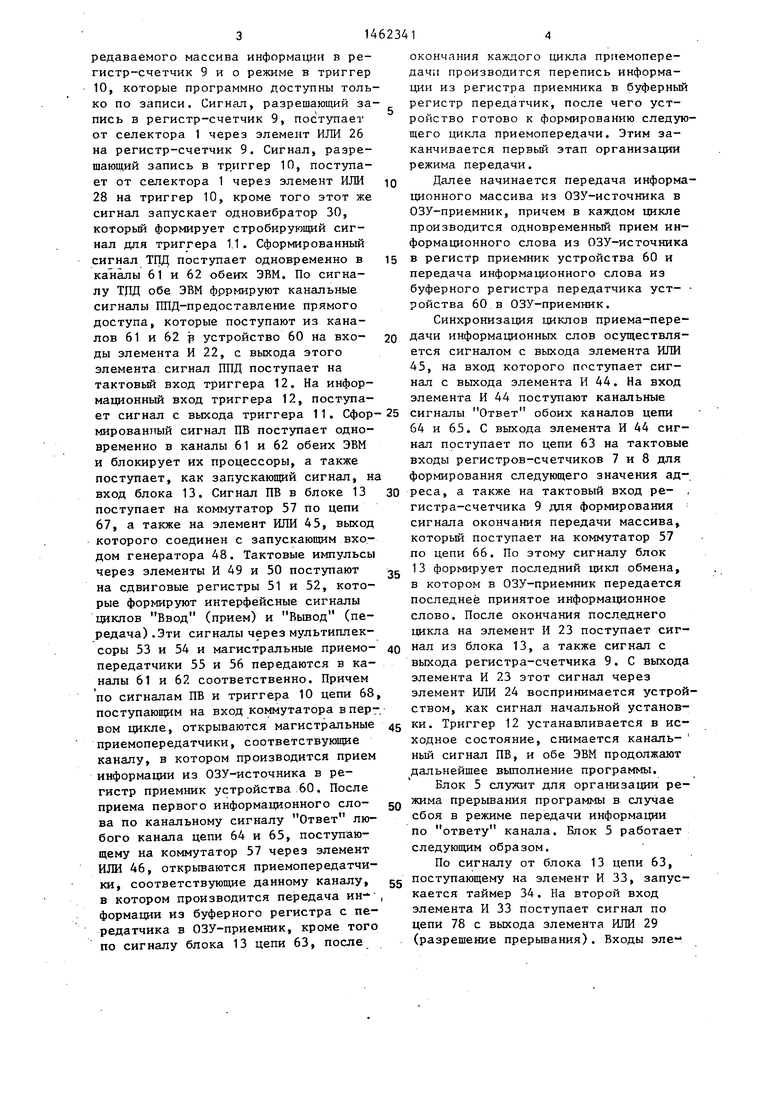

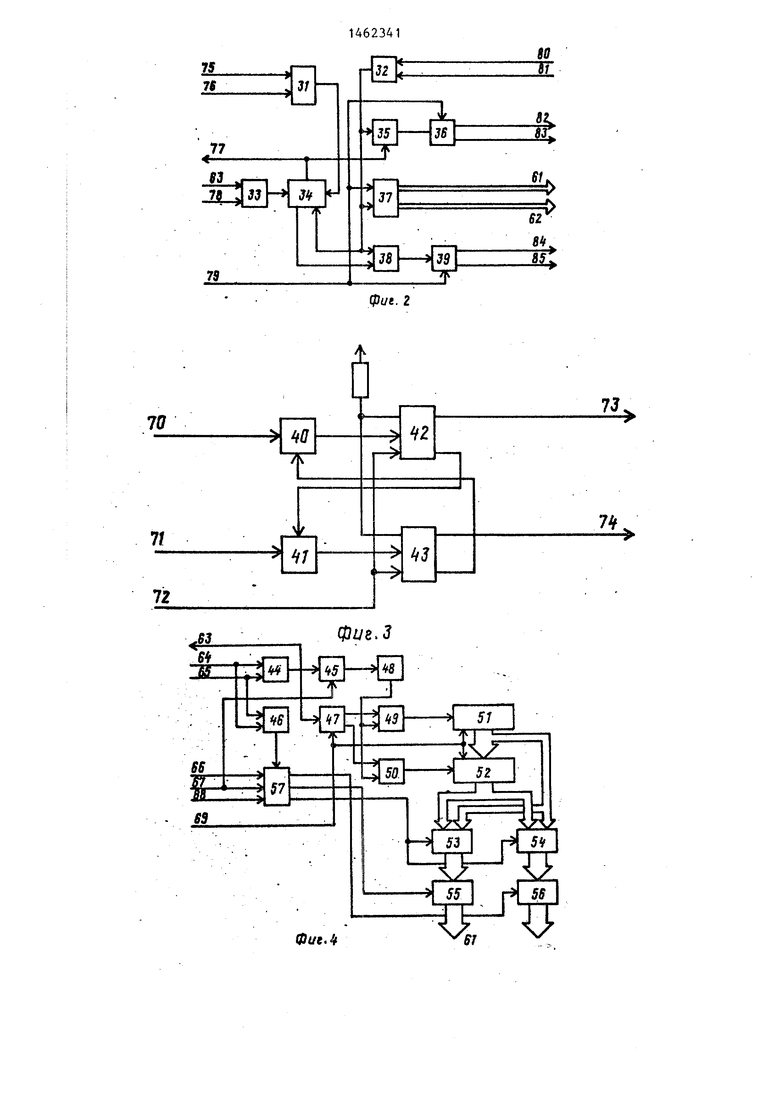

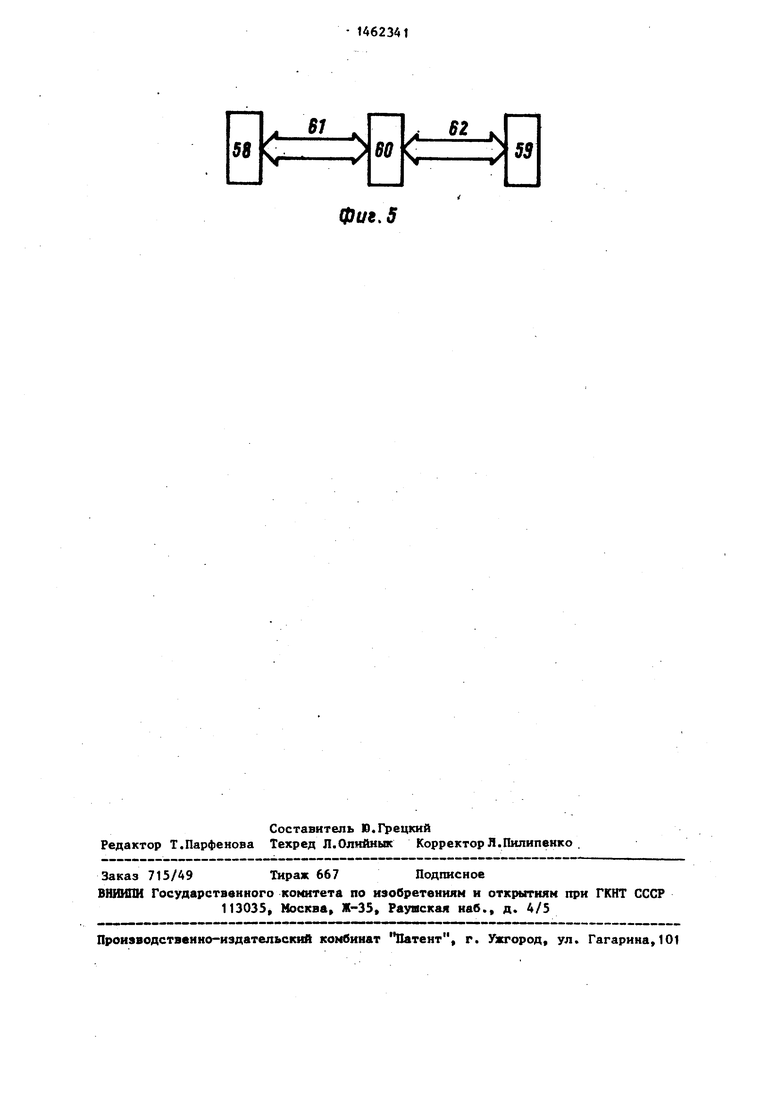

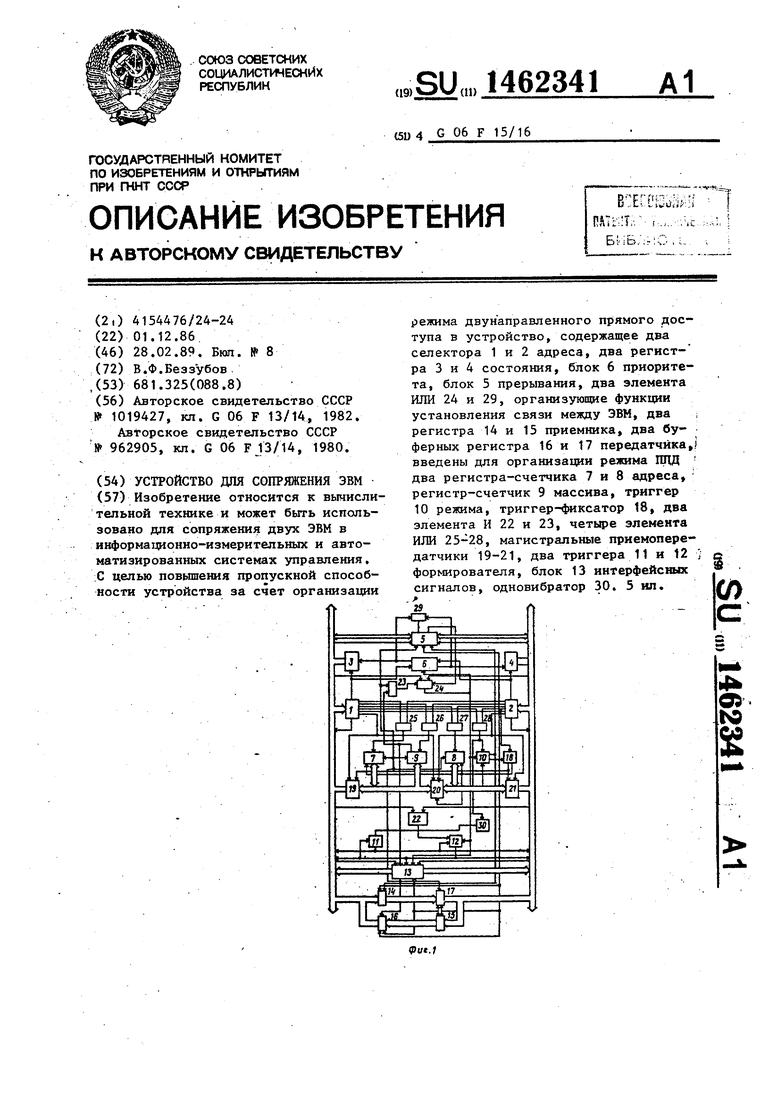

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 - функциональная- схема блока прерывания; на фиг. 3 - функциональная схе- j ма блока приоритета; на фиг. 4 - функциональная схема блока интерфейсных сигналов; на фиг. 5 - пример системы, использующей предлагаемое устройство. 20 Устройство содержит два селектора 1 и 2 адреса, два регистра 3 и 4 состояния, блок 5 прерывания,блок 6 приоритета, два регистра-счетчика 7 и 8 адреса, регистр-счетчик 9 массива, 25 триггер 10 режима, триггер 11 требования прямого доступа, триггер 12 подтверждения выбора, блок 13 интерфейсных сигналов, два регистра 14 и 15 приёмника, два регистра 16 и 30 17 передатчика, триггер фиксатор 18, три магистральных приемопередатчика 19-21, два элемента И 22 к 23, шесть элементов ИЛИ 24-29, одновибратор 30. Блок 5 прерывания (фиг. 2) содер- жит два элемента ИЛИ 31 и 32, элемент И 33, таймер 34, триггер-формирователь 35 сигнала ТПР - требование прерьшания, мультиплексор 36, регистр 37 адреса вектора прерьша- 40 ния, триггер-формирователь 38 канального сигнала Ответ (СИП), мультиплексор 39.

Устройство работает следующим образом.

В соответствии с программой одна из ЭВМ определяет момент времени, когда необходимо передать информацию. Передача информации между ЭВМ осуществляется в два этапа: организация режима передачи информации и непосредственные передачи информационного массива. Так как устройство симметрично по отношению к обоим ЭВМ, то рассмотрим передачу информационного массива от ЭВМ-58 к ЭВМ-59.

Работа начинается с опроса регистра 3 устройства для определения готовности устройства к работе. ЭВМ, инициализирующая обмен, выставляет в какал адрес. При совпадении кода адреса с кодом, прошитым в селекторе 1, селектор 1 формирует сигнал, по которому блок 6 записывает в регистр 4 информацию о занятости устройства по цепи 73 и разрешает регистру 3 выдачу в канал своего содержимого, которое в цикле приема данных ,по ответному сигналу селектора адреса,, принимается первой .ЭВМ. При последующем обращении к устройству второй ЭВМ по своему каналу, ЭВМ аналогичным образом читает содержимое регистра 4, в котором хранится информация о занятости устройства, сформированная триггером 42 по сигналу селектора 1, поступающему на вход триггера 42 .через элемент И 40, по цепи 70, на второй вход которого приходит разрешающий потендаал с триггера 43.При переключении триггера 42, на элемент И 41 поступает запрещающий потенциал и сигнал от селектора 2 по цепи 71 на триггер 43 воздействовать не будет.

Таким образом, устройство оказыБлок 6 приоритета (фиг. 3) содер- .5 вается занятым со стороны канала пер вой ЭВМ. Дальнейшим обращением к устройству ЭВМ записывает информацию о начальных адресах ОЗУ-источника и ОЗУ-приемника в регистры-счетчики 7 и 8, которые программно доступны как по чтению, так и по записи, сигнал разрешения записи поступает от селектора 1 через элементы ИЛИ 25 и 27. Кроме того, от. се:гектора 1 поступает сигнал, открывающий магистральные приемопередатчики 19 и 20 для передачи информации из канала ЭВМ в устройство. Аналогичным образом зажит два элемента 40 и 41 И, два триггера 42 и 43. Елок 13 (фиг. 4) формирователь интерфейсньк сигналов содержит группу элементов 44 И, два элемента 45 и46 ИЛИ, триггер 47 управления, генератор 48, элементы 49 и 50 И, сдвиговые регистры 51 и 52, мультиплексоры 53 и 54, магистральные приемопередатчики 55 и 56, коммутатор 57. На фиг. 5 обозначены первая ЭВМ 58, вторая ЭВМ 59, устрой ство 60 для сопряжения, каналы 61 и 62, входы и выходы-63-79. Кроме того, устройство содержит цепи 80-85.

50

55

писывается информация о величине п Устройство работает следующим образом.

В соответствии с программой одна из ЭВМ определяет момент времени, когда необходимо передать информацию Передача информации между ЭВМ осуществляется в два этапа: организация режима передачи информации и непосредственные передачи информационного массива. Так как устройство симметрично по отношению к обоим ЭВМ, то рассмотрим передачу информационного массива от ЭВМ-58 к ЭВМ-59.

Работа начинается с опроса регистра 3 устройства для определения готовности устройства к работе. ЭВМ, инициализирующая обмен, выставляет в какал адрес. При совпадении кода адреса с кодом, прошитым в селекторе 1, селектор 1 формирует сигнал, п которому блок 6 записывает в регистр 4 информацию о занятости устройства по цепи 73 и разрешает регистру 3 выдачу в канал своего содержимого, которое в цикле приема данных ,по ответному сигналу селектора адреса,, принимается первой .ЭВМ. При последующем обращении к устройству второй ЭВМ по своему каналу, ЭВМ аналогичным образом читает содержимое регистра 4, в котором хранится информация о занятости устройства, сформированная триггером 42 по сигналу селектор 1, поступающему на вход триггера 42 .через элемент И 40, по цепи 70, на второй вход которого приходит разрешающий потендаал с триггера 43.При переключении триггера 42, на элемент И 41 поступает запрещающий потенциал и сигнал от селектора 2 по цепи 71 на триггер 43 воздействовать не будет.

вой ЭВМ. Дальнейшим обращением к устройству ЭВМ записывает информацию о начальных адресах ОЗУ-источника и ОЗУ-приемника в регистры-счетчики 7 и 8, которые программно доступны как по чтению, так и по записи, сигнал разрешения записи поступает от селектора 1 через элементы ИЛИ 25 и 27. Кроме того, от. се:гектора 1 поступает сигнал, открывающий магистральные приемопередатчики 19 и 20 для передачи информации из канала ЭВМ в устройство. Аналогичным образом записывается информация о величине п редаваемого массива информации в регистр-счетчик 9 и о режиме в триггер 10, которые программно доступны только по записи. Сигнал, разрешающий запись в регистр-счетчик 9, поступает от селектора 1 через элемент ИЛИ 26 на регистр-счетчик 9. Сигнал, разрешающий запись в триггер 10, поступает от селектора 1 через элемент ИЛИ 28 на триггер 10, кроме того этот же сигнал запускает одновибратор 30, который формирует стробирующий сигнал для триггера 1.1 . Сформированный сигнал ТПД поступает одновременно в каналы 61 и 62 обеих ЭВМ. По сигналу ТДД обе ЭВМ фррмируют канальные сигналы ППД-предоставление прямого доступа, которые поступают из каналов 61 и 62 р устройство 60 на входы элемента И 22, с выхода этого элемента сигнал ППД поступает на тактовый вход триггера 12. На информационный вход триггера 12, поступаокончания каждого цикла пряемопере- дачи производится перепись информации из регистра приемника в буферный регистр передатчик, после чего устройство готово к формированию следующего цикла приемопередачи. Этим заканчивается первый этап организации режима передачи.

Далее начинается передача информационного массива из ОЗУ-источника в ОЗУ-приемник, причем в каждом цикле производится одновременный прием информационного слова из ОЗУ-источника

в регистр приемник устройства 60 и передача информационного слова из буферного регистра передатчика уст- ройства 60 в ОЗУ-приемник.

Синхронизация циклов приема-передачи информационных слов осуществляется сигналом с выхода элемента ИЛИ 45, на вход которого поступает сигнал с вькода элемента И 44. На вход элемента И 44 поступают канальные

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для сопряжения ЭВМ с магистралью ввода-вывода периферийных устройств | 1986 |

|

SU1397928A2 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1478222A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для сопряжения ЭВМ с магистралью ввода-вывода периферийных устройств | 1988 |

|

SU1672458A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1725223A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения двух ЭВМ в информационно-измерительных и автоматизированных системах управления. С целью повьппения пропускной способности устройства за счет организации режима двунаправленного прямого доступа в устройство, содержащее два селектора 1 и 2 адреса, два регистра 3 и 4 состояния, блок 6 приоритета, блок 5 прерывания, два элемента ИЛИ 24 и 29, организующие функции установления связи между ЭВМ, два ; регистра 14 и 15 приемника, два буферных регистра 16 и 17 передатчика,) введены для организации режима 1ЩД два регистра-счетчика 7 и 8 адреса, регистр-счетчик 9 массива, триггер 10 режима, триггер-фиксатор 18, два элемента И 22 и 23, четыре элемента ИЛИ 25-28, магистральные приемопередатчики 19-21, два триггера 11 и 12 J формирователя, блок 13 интерфейсных сигналов, одновибратор 30. 5 ил. (/) С й Од ю

ет сигнал с выхода триггера 11. Сфор- 25 сигналы Ответ обоих каналов цепи

мированпый сигнал ПВ поступает одновременно в каналы 61 и 62 обеих ЭВМ и блокирует их процессоры, а также поступает, как запускающий сигнал, на вход блока 13. Сигнал ПВ в блоке 13 поступает на коммутатор 57 по цепи 67, а также на элемент ИЛИ 45, выход которого соединен с запускающим входом генератора 48. Тактовые импульсы через элементы И 49 и 50 поступают на сдвиговые регистры 51 и 52, которые формируют интерфейсные сигналы циклов Ввод (прием) и Вьшод (передача) .Эти сигналы через мультиплексоры 53 и 54 и магистральные приемопередатчики 55 и 56 передаются в каналы 61 и 62 соответственно. Причем по сигналам ПВ и триггера 10 цепи 68 поступающим на вход коммутатора в первом цикле, открываются магистральные приемопередатчики, соответствующие каналу, в котором производится прием информации из ОЗУ-источника в регистр приемник устройства 60. После приема первого информационного слова по канальному сигналу Ответ любого канала цепи 64 и 65, поступающему на коммутатор 57 через элемент ИЛИ 46, открьшаются приемопередатчики, соответствующие данному каналу, в котором производится передача информации из буферного регистра с передатчика в ОЗУ-приемник, кроме того по сигналу блока 13 цепи 63, после

0

5

0

64 и 65. С выхода элемента И 44 сигнал поступает по цепи 63 на тактовые входы регистров-счетчиков 7 и 8 для формирования следующего значения адреса, а также на тактовый вход ре- , гистра-счетчика 9 для формирования сигнала окончания передачи массива, который поступает на коммутатор 57 по цепи 66. По этому сигналу блок 13 формирует последний цикл обмена, в котором в ОЗУ-приемник передается последнее принятое информационное слово. После окончания последнего цикла на элемент И 23 поступает сигнал из блока 13, а также сигнал с выхода регистра-счетчика 9. С выхода элемента И 23 этот сигнал через элемент ИЛИ 24 воспринимается устройством, как сигнал начальной установки. Триггер 12 устанавливается в исходное состояние, снимается каналь- ный сигнал ПВ, и обе ЭВМ продолжают дальнейшее выполнение программы.

Блок 5 служит для организации режима прерывания программы в случае сбоя в режиме передачи информации по ответу канала. Блок 5 работает следующим образом.

По сигналу от блока 13 цепи 63, е поступающему на элемент И 33, запускается таймер 34. На второй вход элемента И 33 поступает сигнал по цепи 78 с выхода элемента ИЛИ 29 . (разрешение прерьшания). Входы эле5

0

мента ИЛИ 29 соединены соответственно с выходами блока 6 по цепям 73 и 74 На входы элемента И 31 блока 5 поступают канальные сигналы Ответ (СИП) обоих каналов,по цепям 75 и 76. Сигнал с выхода элемента И 31 устанавливает таймер 34 в исходное сос- iTOHHHe. В случае отсутствия сигнала : 0твет (СИП) одного из каналов, сигнал с выхода таймера 34 через за- ;данный интервал времени после запус- ;ка поступает ца вход триггера-формирователя 35 сигнала требование прерывания ТИР, который через мультиплексор 36 поступает в канал ЭВМ, инициализирующий обмен (цепи 82 и 83). Кро- ;ме того, с выхода таймера 34 сигнал :по цепи 77 поступает на вход элеменстров передатчиков соответственно, информационные выходы которых являются вторым и первым информационными входами-выходами устройства и соеди - нены с входами второго и первого регистров приемников соответственно, адресные входы первого и второго селекторов адреса являются первым и

10 вторым адресными входами устройства соответственно, информационные выходы первого и второго регистров состояния соединены с первым и вторым информационными выходами устройства,

15 а информационные входы соединены соответственно с разрядами первого и второго выходов разрешения прерьгаания блока приоритета и с входами первого элемента ИЛИ; выход которого.соедине

та ИЛИ 24 и возвращает устройство из 20 с входом разрешения прерывания блока

режима обмена в исходное состояние. :Разблокированный процессор принимает сигнал ТПР и формирует сигнал предоставление прерывания ПИР и цикл Ввод. Блок 5 принимает сигнал ППР по цепям 80 и 81 на входы элемента ИЛИ 32, снимает сигнал ТПР, устанавливая триггер 35 в исходное состояние .. выставляет в канал адрес векпрерывания, первый и второй информационные входы блока приоритета соеди нены с первыми выходами первого и второго селекторов адреса и с управ- 25 ляющими входами записи первого и вто рого регистров состояния соответственно, первый и второй входы Ответ блока прерывания соединены с одноименными входами устройства, первый

J. . у .. л. С1..Ъ л 4.. f-M, ч- .

тора прерьшания (цепи 61 и 62) из ре- 30 и второй управляющие входы-выходы

гистра 37 и сигнал Ответ, сформированный триггером 38. Кроме того, сигнал ППР устанавливает таймер 34 в исходное состояние.

Сигнал Ответ поступает в канал ЭВМ через мультиплексор 39 по цепям 84 и 85. Управления мультиплексорами 36 и 39, а также регистрами 37 осуществляется от триггера 10 по цепи 79.

блока:прерывания образуют одноименны входы-выходы устройства, первый и второй входы начальной установки которого соединены с соответствующими 35 входами второго элемента ИЛИ, третий вход которого соединен с выходом бло ка прерывания, выход второго элемента ИЛИ соединен с входом начальной установки блока приоритета, о т л и

Процессор ЭВМ, инициализирующий обмен 40 ч а ю щ е

е с я

тем, что, с целью

принимает адрес вектора прерьгаания, .снимает сигнал ППР и переходит на подпрограмму обслуживания, в которой, читая содержимое регистров-счетчиков 7 и 8, определяет адрес ячейки памяти, при обращении к которой произошел сбой.

Формула изобретения

Устройство для сопряжения ЭВМ, содержащее два селектора адреса, два регистра состояния, блок приоритета, блок прерьгоания, два элемента ИЛИ, два регистра приемника, два регистра передатчика, причем информационные выходы первого и второго регистров приемников соединены с информационными входами второго и первого региуменьшения затрат машинного времени на передачу информации за счет организации режима двунаправленного прямого доступа, в него введены два ре45 гистра-счетчика адреса, регистр-счет

чик массива, триггер режима, триггер фиксатор, два элемента И, с третьего по шестой элементы ИЛИ, три магистральных приемопередатчика, триггер

50 требования прямого доступа, триггер подтверждения выбора, блок интерфейс ных сигналов, одновибратор, причем первый и второй управляющие выходы блока интерфейсных сигналов являются

55 соответственно первым и вторым упра ляющими выходами устройства, а первый и второй входы соединены соотве ственно с первым и вторым входами Ответ устройства, третий вход бло

тров передатчиков соответственно, нформационные выходы которых являются вторым и первым информационными входами-выходами устройства и соеди - нены с входами второго и первого регистров приемников соответственно, адресные входы первого и второго селекторов адреса являются первым и

вторым адресными входами устройства соответственно, информационные выходы первого и второго регистров состояния соединены с первым и вторым информационными выходами устройства,

а информационные входы соединены соответственно с разрядами первого и второго выходов разрешения прерьгаания блока приоритета и с входами первого элемента ИЛИ; выход которого.соединен

с входом разрешения прерывания блока

с входом разрешения прерывания блока

прерывания, первый и второй информационные входы блока приоритета соединены с первыми выходами первого и второго селекторов адреса и с управ- ляющими входами записи первого и второго регистров состояния соответственно, первый и второй входы Ответ блока прерывания соединены с одноименными входами устройства, первый

30 и второй управляющие входы-выходы

блока:прерывания образуют одноименные входы-выходы устройства, первый и второй входы начальной установки которого соединены с соответствующими 35 входами второго элемента ИЛИ, третий вход которого соединен с выходом блока прерывания, выход второго элемента ИЛИ соединен с входом начальной установки блока приоритета, о т л и 40 ч а ю щ е

е с я

тем, что, с целью

а ю щ е

уменьшения затрат машинного времени на передачу информации за счет организации режима двунаправленного прямого доступа, в него введены два регистра-счетчика адреса, регистр-счетчик массива, триггер режима, триггер- фиксатор, два элемента И, с третьего по шестой элементы ИЛИ, три магистральных приемопередатчика, триггер

требования прямого доступа, триггер подтверждения выбора, блок интерфейсных сигналов, одновибратор, причем первый и второй управляющие выходы блока интерфейсных сигналов являются

соответственно первым и вторым управляющими выходами устройства, а первый и второй входы соединены соответственно с первым и вторым входами Ответ устройства, третий вход блока интерфейсных сигналов соединен с выходом триггера подтверждения выбора, четвертый вход соединен с выходом регистра счетчика массива, пятый вход соединен с выходом триггера режима, шестой вход соединен с входом установки триггера подтверждения выбора, входом установки триггера режима и с выходом второго элемента ИЛИ, четвертый вход которого соединен с выходом первого элемента И, первый вход которого соединен с тактовым выходом блока интерфейсных сигналов, второй вход соединен с выходом переполнения регистра-счетчика массива, тактовый выход блока интерфейсных сигналов соединен с входами управления записью первого и второго регистров передатчиков, входы управления режимом первых и вторых регистров передатчиков и регистров приемников соединены соответственно с выходами триггера режима, тактовый вход триггера требования прямого доступа соединен с выходом одновибратора, вход которого соединен с выходом третьего элемента ИЛИ и с входом установки триггера режима, вход установки триггера требования прямого доступа соединен с выходом триггера подтверждения выбора и являются первым и вторым выходами подтверяздения выбора устройства, выход триггера требования прямого доступа соединен с первым и вторым выходами требования прямого доступа устройства,.такто- вход триггера подтверждения выбора соединен с выходом второго элемента И, первый и второй входы которого являются соответственно первым и вторым вьпсодами предоставления прямого доступа устройства, информационные

информационные входы-выходы второго регистра-счетчика адреса соединены с вторым информационным входом-выходом второго магистрального приемопередатчика и с первым информагдаонным входом-выходом третьего магистрального приемопередатчикаiвторой информационный вход-выход которого соединен с 10 одноименным входом-выходом устройства, второй информационный вход-выход первого магистрального приемопередатчика соединен с первым информаци онным входом-выходом устройства, пер15 вые входы управления режимом первого и второго регистров-счетчиков адреса соединены с выходом триггера фиксатора и с первыми управляющими входами магистральных приемопередатчиков,,

20 вход установки в О триггера-фиксатора соединен с выходом триггера режима, вход установки в 1 - с вторыми выходами селекторов адреса, тактовые входы первого и второго реги25 стров-счетчиков адреса и регистра счетчика массива соединены с тактовым выходом блока интерфейсных сигналов, стробирующие входы регистров- счетчиков адреса и массива соединены

30 с выходами с четвертого по шестой соответственно элементов ИЛИ, первые входы которых соединены с соответствующими выходами с третьего по пя- тый первого селектора адреса, а вто35 рыв входы - с соответствующими выходами второго селектора адреса, шестой выход первого селектора адреса соединен с вторыми управляющими входами первого и второго магистральных

40 приемопередатчиков, шестой выход второго селектора адреса соединен с третьим и вторым управляннчими входа ми второго и третьего магистральных приемопередатчиков соответственно.

входы-выходы первого регистра счетчика адреса и регистра-счетчика масси- 45 седьмые выходы первого и второго сева соединены с первыми информацион- лекторов адреса являются первым и ными входами-выходами первого и второго магистральных приемопередатчиков,

вторым ответными выходами устройства.

623418

информационные входы-выходы второго регистра-счетчика адреса соединены с вторым информационным входом-выходом второго магистрального приемопередатчика и с первым информагдаонным входом-выходом третьего магистрального приемопередатчикаiвторой информационный вход-выход которого соединен с 10 одноименным входом-выходом устройства, второй информационный вход-выход первого магистрального приемопередатчика соединен с первым информаци онным входом-выходом устройства, пер15 вые входы управления режимом первого и второго регистров-счетчиков адреса соединены с выходом триггера фиксатора и с первыми управляющими входами магистральных приемопередатчиков,,

20 вход установки в О триггера-фиксатора соединен с выходом триггера режима, вход установки в 1 - с вторыми выходами селекторов адреса, тактовые входы первого и второго реги25 стров-счетчиков адреса и регистра счетчика массива соединены с тактовым выходом блока интерфейсных сигналов, стробирующие входы регистров- счетчиков адреса и массива соединены

30 с выходами с четвертого по шестой соответственно элементов ИЛИ, первые входы которых соединены с соответствующими выходами с третьего по пя- , тый первого селектора адреса, а вто35 рыв входы - с соответствующими выходами второго селектора адреса, шестой выход первого селектора адреса соединен с вторыми управляющими входами первого и второго магистральных

40 приемопередатчиков, шестой выход второго селектора адреса соединен с третьим и вторым управляннчими входа ми второго и третьего магистральных приемопередатчиков соответственно.

45 седьмые выходы первого и второго селекторов адреса являются первым и

седьмые выходы первого и второго селекторов адреса являются первым и

вторым ответными выходами устройства.

75

7

j;

77

93

7S

фиг.З

Qfft/e. tt

80

32

di

IL

IT

ff/.

w e«.

ж

фиг.5

| Устройство для сопряжения цифровых вычислительных машин | 1981 |

|

SU1019427A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1986-12-01—Подача