упрощении устройства, повышении быст родействия и эффективности использования многоблочной памяти. Устройство содержит узел канальных приемопередатчиков 7, дешифратор 8 адреса, регистр 9 управления и состояния, содержащий триггер 15 режима и триггер 16 ошибки, блок 11 оперативной памяти, регистр 12 номера блока, дешифратор 14 номера блока, два элемента ИЛИ 18 и 23, два элемента И 19 и 25. После включения питания системы (или при начальной установке в процессе работы) по командам процессора в блок 11 заносится информация об управлении работой разделов 4 (устройств) памяти. В режиме Пользовательский, т.е. когда установлен триггер 15, сигнал с инверсного выИзобретение относится к вь1числи- тельной технике, в частности к устройствам управления памятью, и может быть использовано для увеличения объема оперативной памяти при построении цифровых систем на базе миниСмик- ро)ЭВМ, в том числе с многопользовательским, мультипрограммным режимом работы.

Целью изобретения является повышение быстродействия и сокращение аппаратурных затрат устройства.

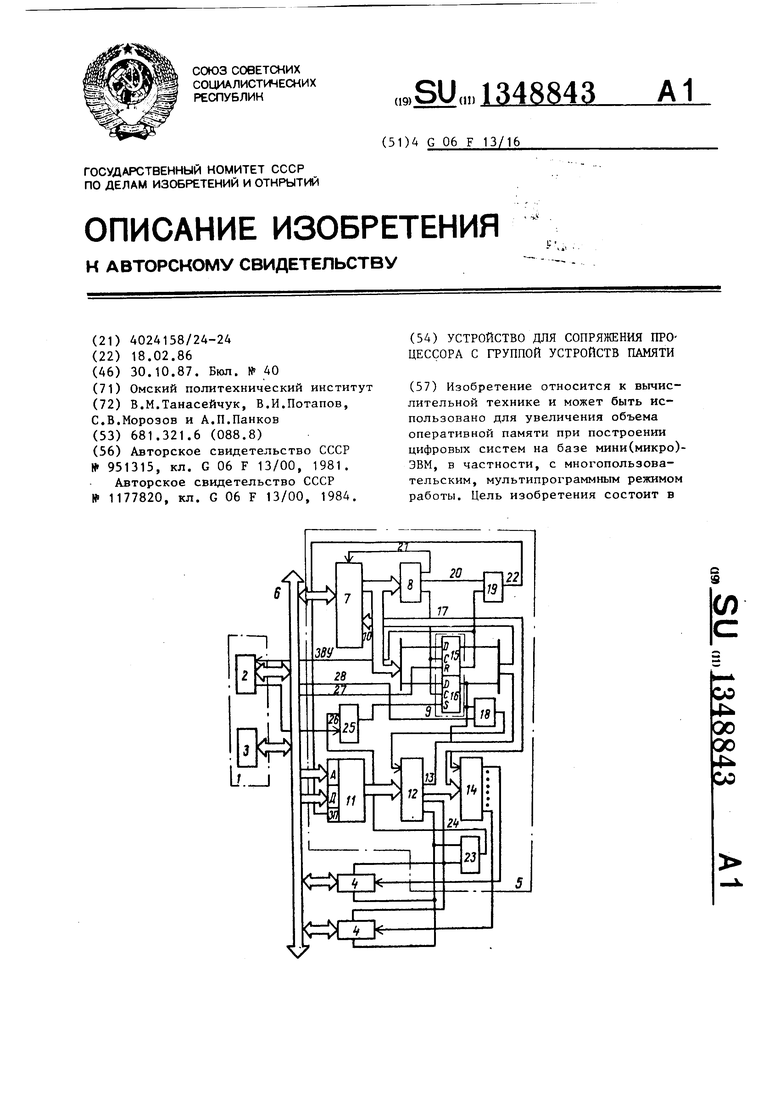

На чертеже изображена схема предлагаемого устройства.

На чертеже показаны микроЭВМ 1, содержащая центральный процессор 2, блок 3 постоянной памяти (ПЗУ), группа устройств 4 памяти (разделы), связанные с устройством 5 для сопряжения посредством магистрали 6.

Устройство 5 содержит узел 7 канальных приемопередатчиков, дешифратор 8 адреса, регистр 9 управления и состояния, управляющую мах истраль 10, блок 11 оперативной памяти (ОЗУ), регистр 12 номера блока, адресную магистраль 13, дешифратор 14 номера блока. Регистр 9 состоит из триггеров режима 15 и ошибки 16, синхровхо- ды которых соединены шиной 17 с первым выходом дешифратора 8. На черте48843

хода этого тригтера блокирует прохождение канального сигнала Выбор устройства, что позволяет более эффективно использовать многоблочные устройства памяти. После записи управляющей информации в блок 11 в адресной части цикла при обращении к памяти производится выборка соответствующего кода из блока 11, содержимое которого определяет выбираемый дешифратором 14 раздел памяти и разрешенный вид доступа к этому разделу;запись и/или чтение. При ощибке обращения на регистр 12 фиксируется адрес раздела, к которому производилось обращение, и устанавливается триггер 16, что позволяет управляющей программе определить причину возникновения ошибки. 1 ил.

5

же также показаны элемент ИЛИ 18, элемент И 19, щины 20 и 21 третьего и второго выходов дешифратора 8, шина 22 входа записи ОЗУ 11, элемент ИЛИ 23, шиной 24 подключенный к входу элемента И 25, шины сигналов ошибки 26, сброса 27 и синхронизации 28.

Пространство ячеек памяти, адресуемое всеми разрядами процессорного слова, определено как блок памяти, который состоит из совокупности банков памяти. Виртуальный адрес, т.е. адрес, формируемый командами процессора, содержит два поля: поле номера банка в данном блоке памяти и адрес ячейки (смещение) в данном банке памяти.

Физический (исполнительный) адрес содержит поля: номер раздела (устройства), номер блока памяти в разделе, номер банка и смещение адреса .

Устройство 5 при помощи ОЗУ 11 формирует физический адрес памяти, причем в ОЗУ 11 заносятся поля физического адреса, определяющие действительный физический адрес банка памяти. Например, для 16-разрядного

слова процессора старшие три разря- п

да 13-15 виртуального адреса интерпретируются как номер одной из вось5

ми ячеек ОЗУ 1 1 . (;одержимое ячейки ОЗУ 11 пристыковывается к виртуальному адресу, определяя физический номер блока в разделе, в котором находится нужный банк, и физический номе разде:та, к которому производится обращение. Доступность данного банка обеспечивается соответствующей установкой двухразрядного кода, который интерпретируется как разрешение банка для чтения и записи, только для чтения и чтение и запись запрещены. Последнее обозначает, что поле адресов, соответствующее этому банку памяти, не может быть использовано при решении задач. Это позволяет обеспечить защиту памяти от влияния одной задачи на другие.

Каждый раздел 4 памяти имеет уп7 равляющие входы Выборка, Разрешение ввода

Разрешение вывода

помощью которых данному разделу памяти либо разрешается, либо запрещается работа с маг истралью Общая щина

Устройство работает следующим образом.

Под все адреса ячеек ОЗУ 11 реализуются адреса внешних устройств, на которые реагирует дешифратор 8. В адресной части цикла при обращении к памяти производится выборка соответствующего кода из ОЗУ 11, содержимое которого определяет выбираемый дешифратором 14 раздел 4 памяти и разрешенный вид доступа запись и/или чтение к этому разделу. В случае, если произошел запрещенный для данного раздела 4 памяти вид обращения, то на регистре 12 фиксируется номер раздела памяти, к которому производилось ошибочное обращение, а также устанавливается триггер 16, что позволяет Программе обслуживания ошибки обращения к каналу определить, вызван ли этот сбой аппаратурой либо ошибкой программирования.

При включении питания системы ми- ни(микро)ЭВМ или при канальной установке в процессе работы процессор 2 вырабатывает сигнал Сброс, устанавливающий триггер 15 в нулевое состояние, что соответствует режиму работы устройства Системный. В этом режиме производится запись информации в ОЗУ 11. Сигнал с инверсного выхода триггера 15 через элемент И 19 по сиг

35

зо

налу с дешифратора 8 производит запись информации в ОЗУ 11.

В адресных частях процессор 2 последовательно выставляет зарезервированные адреса внешних устройств. В информационной части цикла магистрали 6, когда на шинах выставлены данные, старшие п разрядов адресуют

0 ячейку памяти ОЗУ 11, младшие m разрядов являются- информацией для этой ячейки,

В режиме Пользовательский, т.е. когда установлен триггер 15 в единич15 ное состояние, сигнал с инверсного выхода триггера 15 блокирует прохождение канального сигнала Выбор устройства из процессора 2. Таким образом, в режиме Пользовательский по0 является возможность использования банка памяти, отводимого под адреса внешних устройств.

При обращении к памяти старшие разряды адреса (номер банка) посту2Ь пают на вход ОЗУ 11, на выходе которого появляется информация соответствующей ячейки ОЗУ 11. В отсутствие сигнала синхронизации адреса регистр 12 работает в режиме прозрачности, т.е. информация с выхода ОЗУ 11 поступает на вход дешифратора 14, который дает разрешение на подключение заданного раздела 4 памяти. По переднему фронту в шине 28 информация с выхода ОЗУ 11 запоминается в регистре 12, в результате запрещается прохождение информации с выхода ОЗУ 11 на вход дешифратора 14 в информационной части цикла магистрали 6.

д Если производится запрещенный для данного раздела 4 вид обращения, то процессор 2 вырабатывает сигнал Ошибка обращения к магистрали 6, который по совпадению с сигналом с выхода элемента ИЛИ 23 устанавливает триггер 16 в единичное состояние. Сигнал с выхода триггера 16 запрещает работу дешифратора 14 и запрещает изменение информации в регистре 12. Обрабатывая прерывание по ошибке обращения к каналу, процессор 2 выраII

45

50

батывает канальный сиг нал Сброс и обращается к регистру 9 устройства, анализирует его, и если триггер 16 установлен, считывает информацию из регистра 12 и выполняет необходимые действия для выявления причины возникновения ошибки обращения к каналу. В случае выявления причин, вызванных аппаратурными сбоями, осуществляется повторный запуск команды либо участка программы, на котором произошел сбой. В случае ошибки программирования производится выдача сообщения об этом на терминал.

Формула изобретения

Устройство для сопряжения процессора с группой устройств памяти, содержащее узел канальных приемопередатчиков, выходом соединенный с информационным входом регистра управ- |Ления и состояния и входом дешифратора адреса, первым и вторым выходам подключенного соответственно к синх- ровходу регистра управления и состояния и управляющему входу узла канальных приемопередатчиков, вход-выход которого является входом-выходом устройства для подключения к шине адреса данных процессора, два элемента И, первый элемент ИЛИ и регистр номера блока, подключенный группой выходов к группе информационных входов дешифратора номера блока, группа выходов которох-о является группой выходов устройства для подключения к входам выборки устройств памяти 1 руппы, первый выход регистра управления и состояния соединен с первым входом первого элемента И и является выходом устройства для подключения к входу запрета выбора внешнего устройства процессора, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок оперативной паСоставитель В.Вертлиб Редактор Е.Копча Техред А. Кравчук Корректор В.Бутяга

Заказ 4803/49 Тираж 670Подписное

ВНИИПИ Государственного комитета.СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5

0

5

0

5

мяти и второй элемент. ИЛИ, причем входы адреса и данных блока оперативной памяти являются входами устройства для соединения с шиной адреса данных процессора, вход записи и выход блока оперативной памяти соединены соответственно с выходом первого элемента И и информационным входом регистра номера блока, управляющий вход которого соединен с выходом первого элемента ИЛИ, первым входом подключенного к второму выходу регистра управления и состояния и управляющему входу дешифратора номера блока, выход и первый вход установки регистра управления и состояния соединены с выходом второго элемента И, подключенного первым входом к выходу второго элемента ИЛИ, первый и вто- рой входы которого соединены соответственно с первым и вторым выходами регистра номера блока, информационный вход узла канальных приемопередатчиков соединен с вторым и третьим выходами регистра управления и состояния и группой выходов регистра номера блока, первый и второй выходы которого являются соответствующими выходами устройства для подключения к входам запрета ввода и вывода устройств памяти группы, второй вход установки регистра управления и состо- яния, вторые входы первого элемента ИЛИ и второго элемента И являются соответствующими входами устройства для подключения к шинам сброса, синхронизации и ошибки процессора,третий выход дешифратора адреса соединен с вторым входом первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Устройство сопряжения процессора с многоблочной памятью | 1989 |

|

SU1702383A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1986 |

|

SU1319039A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1501071A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1401470A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1345203A1 |

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

| Динамическое оперативное запоминающее устройство | 1987 |

|

SU1499401A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

Изобретение относится к вычислительной технике и может быть использовано для увеличения объема оперативной памяти при построении цифровых систем на базе мини(микро)- ЭВМ, в частности, с многопользовательским, мультипрограммным режимом работы. Цель изобретения состоит в (Л со 00 00 4 00

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1177820, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-02-18—Подача