торого являются соответственно выходами и входами устройства,

2.Устройство по п. I, отличающееся тен, что блок управления и синхронизации содержит четвертый и пятый коммутаторы, первый и второй счетчики, первый триггер, элемент коммутации, первый элемент И и узел формирования импульсов, к первому входу которого подключен первый выход четвертого коммутатора, второй выход которого подключен к первому входу первого элемента И, выход которого подключен к второму входу уэла формирования импульсов, первый вход элемента коммутации подключен к шине логической единицы, а его выход подключен к первому входу первого триггера, второму входу первого элемент И и третьему входу узла формирования импульсов, выход первого счетчика подключен к его первому входу, второму входу пятого коммутатора, второму входу первого триггера, выходы которого подключены к группе входов пятого коммутатора и являются второй группой выходов блока, третий выход четвертого коммутатора подключен к первому входу пятого коммутатора, выходы которого являются первой группой выходов блока, второй вход элемента коммутации подключен к шине логического нуля выход узла формирования импульсов подключен к второму входу первого счетчика, третьему входу пятого коммутатора и является выходом блока, выход второго счетчика подключен к его второму входу и пятому входу пятого коммутатора, четвертый вход которого объединен с первым входом второго счетчика, первый, второй, третий и четвертый входы четвертого коммутатора являются входами первой и второй групп блока соответственно четвертый вход узла -формирования импульсов и первый вход второго счетчика .являются вxoдa a{ третьей группы блока, выходы перйого и вторЬго счетчиков, элемента коммутации первого элемента И, третий выход четвертого коммутатора являются выходами третьей группы блока.

3.Устройство по п. 1, о тличаю цееся тем, что блок генерации команд обмена содержит генератор импульсов, со второго

по шестнадцатый злеме)яты И, с первого по пятый элементы ИЛИ, со второго по шестой триггеры, первый и второй дешифраторы, третий счетчик, первый, второй и третий формирователи, выход второго элемента И подключен к второк у входу второго триггера, первому входу, третьего счетчика, первому входу первого элемента ИЛИ, первому входу первого формирователя, первом входу третьего триггера, выход второго триггера подключен к nepBOMj входу третьего элемента И, к второму входу которого подключен вькод генератора импульсов, к третьему входу третьего элемента И подключ€ Н выход второго элемента ИЛИ, выход третьего элемента И подключен к второму входу третьего счетчика, выходы которого подключены к входам первого депшфратора, первый выхсд которого подключен к первому входу второго элемента ШШ, второй вход, которого и первый вход четвертого триггера подключены к второму выходу первого дешифратора, второй вход четвертого триггера объединен с вторым входом первого фор№1рователя, третий выход первого дешифратора подключен к третьему входу второго элемента ИЛИ и первому входу пятого триггера, к второму входу которого и четвертому входу второго элемента ИЛИ подключен выход четвертого элемента И, выход пятого триг.гера подключен к входу пятого элемента И, четвертый выход первого дешифратора подключен к первому входу шестого триггера и первому вхо-. ду четвертого элемента И, пятый выход первого дешифратора подключен к первому входу шестого элемента И, второй вход которого и первый вход седьмого элемента И объединены, выход шестого элемента И подключен к второму входу шестого триггера и пятому входу второго элемента ИЛИ,шестой выход neipBoro дешифратора подключен к второму входу седьмого элемента И и первому входу восьмого элемента И, Выход седьмого элемента И подключен к первому входу третьего элемента ИЛИ и входа девятого и десятого элементов И, к второму входу третьего элемента ИЛИ подключен первый выход третьего тригера, второй выход которого подключён к первому входу одиннадцатого элемента И, седьмой выход первого дешифратора подключен к второму входу одиннадцатого и первому входу двенадцатого элементов И первые входы.тринадцатого и четырнадцатого и третий вход одиннадцатого элементов И объединены, выход одиннадцатого элемента И подключен к второму входу первого элемента ИЛИ, к третьему входу которого подключен выход двенадцатого элемента И, второй вход которого объединен с первыми входаьм второго и пятнадцатого элементов И и вторым :входом восьмого элемента И, выход первого элемента ИЛИ подключен к второму входу тринадцатого элемента И, выход которого подключен к входу шестнадцатого элемента И, входы группы которого являются входа второй группы блока, а выходы подключены к входам первой группы четвертого элемента ИЛИ, выходы группы первого формирователя подключены к входам группы девятого элемента И, выходы которого подключены к входам второй группы четвертого элемента ИЛИ, выход первого формирователя подключен к второму входу второго формирователя, выходы которого подключены к входам группы десятого элемента И, выхбдь( которого подключены к входам треттьей группы четвертого элемента ИЛИ, выходы третьего формирователя подключены к входам группы пятого элемента И, выходы которого подключены к входам четвертой группы четвертого элемента ИЛИ, с первого по восьмой входы второго дешифратора и со второго по девятый входы четырнадцатого элемента И соответственно объединены, выходы четьфнадцатого элемента И являются выходами второй группы блока, первый выход второго дешифратора подключен к второму входу второго элемента И, второй выход второго дешифратора подключен к третьему входу восьмого элемента И, третий выход второго дешифратора подключен к второму входу пятнадцатого элемента И, выход Koropioro подключен к первому входу пятого элмента ИЛИ, выход которого подключен к второму входу третьего триггера, выходы восьмого элемента И подключены к таестоыу входу второго элемента ИЛИ, третий вход одиннадцатого элемента И и первый вход пятого элемента ИЛИ являются первой группой выходов блока, первый вход второго и второй вход четвертого триггеров, третий вход первого формирователя, второй вход пятого элемента ИЛИ и первый вход второго формирователя являются в ход акв первой группы блока, вторые входы четвертого, шестого и двенадцатого элементов И, третий вход одиннадцатого элемента И, с первого по восьмой входы второго дешифратора являются входами тре|тьей группы блока, выходы четвертого элемента ИЛИ, четвертого, пятого, шестого триггеров, первого и третьего элементов ИШ являются выходами третьей групгы блока.

4, Устройство по п. 1, отличающееся тем, что блок буферной памяти содержит .первый и второй узлы памяти, входы первых групп которых являются входаьи первой группы блока, входы вторых групп узлов памяти являются входаьо второй группы блока, выходы узлов памяти являются выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Устройство для распознавания изображений | 1985 |

|

SU1339601A1 |

| Устройство для центрирования изображений объектов | 1990 |

|

SU1836697A3 |

| Устройство для селекции изображений объектов | 1989 |

|

SU1777651A3 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ | 1990 |

|

RU2022346C1 |

| СИСТЕМА АСТРООРИЕНТАЦИИ КОСМИЧЕСКОГО АППАРАТА | 1989 |

|

SU1795708A1 |

| Устройство для определения отношения двух напряжений | 1989 |

|

SU1702397A1 |

| Устройство для исследования графов | 1985 |

|

SU1305720A1 |

1 . УСТРОЙСТВО ДЛЯ ВВОДА- . ВЫВОДА ПОЛУТОНОВОЙ ИНФОРМАЦИИ, содержащее блок сканирования, анало- , го-цифровой преобразователь, цифроанапоговый преобразователь, блок управления и синхронизации, выход которого подключен к первому входу аналого-цифрового преобразователя и входу цифроаналогового преобразователя, выход которого подключен к входу блока сканирования,выход которого подключен к второму входу аналого-цифрового преобразователя, выходы первой и второй групп блока сканирования подключены соответственно к входам первой и второй групп блока управления и. синхронизации, отличающееся тем, что, с целью повыщения быстродействия устройства, оно содержит блок буферной памяти, блок генерации команд обмена, первый, второй и третий коммутаторы, к выходам первой группы блока угфавпения и синхронизации подключены .входы первой группы блока буфернсЛ памяти , к входам второй группы которого прдключешл выходы первого коммутатора, к входам первой группы которого и входам первой группы второго коммутатора подключены выходы второй группы блока управления и синхронизации, к входам второй групгы второго коммутатора подключены выходы блока буферной памяти, выходы второго коммутатора подключены к входам первой группы третьего комел мутатора, выходы первой группы которого подключены к входам второй группы первого коммутатора, выходы аналого-цифрового преобразователя подключены к входам второй группы третьего коммутатора, выходы второй группы которого подключены к входам группы цифро-анапогового 05 Преобразователя, выходы третьей 4:ik группы блока управления и синхронизации подключены к входам первой vj группы блока генерации команд обмена, выходы первой группы которого подключены к входам третьей группы блока управления и синхронизации, выходы второй группы блока управления и синхронизации, выходы второй группы блока генерации команд обмена подключены к входам третьей групга 1 третьего коммутатора, выходы которой подключены к входам второй группы блока генерации команд обмена, выходы и входы третьих групп . .-..,-. г, f,.I I I. . , . : , 1Й i - I НИЯ u-g.ijtSCva.-

Изобретение относится к автоматической и вычислительной технике и может найти применение при проведении исследований, связанных с автоматизированной обработкой информации, зарегистрированной на фотоносителё.,

Целью изобретения является повышение быстродействия устройства.

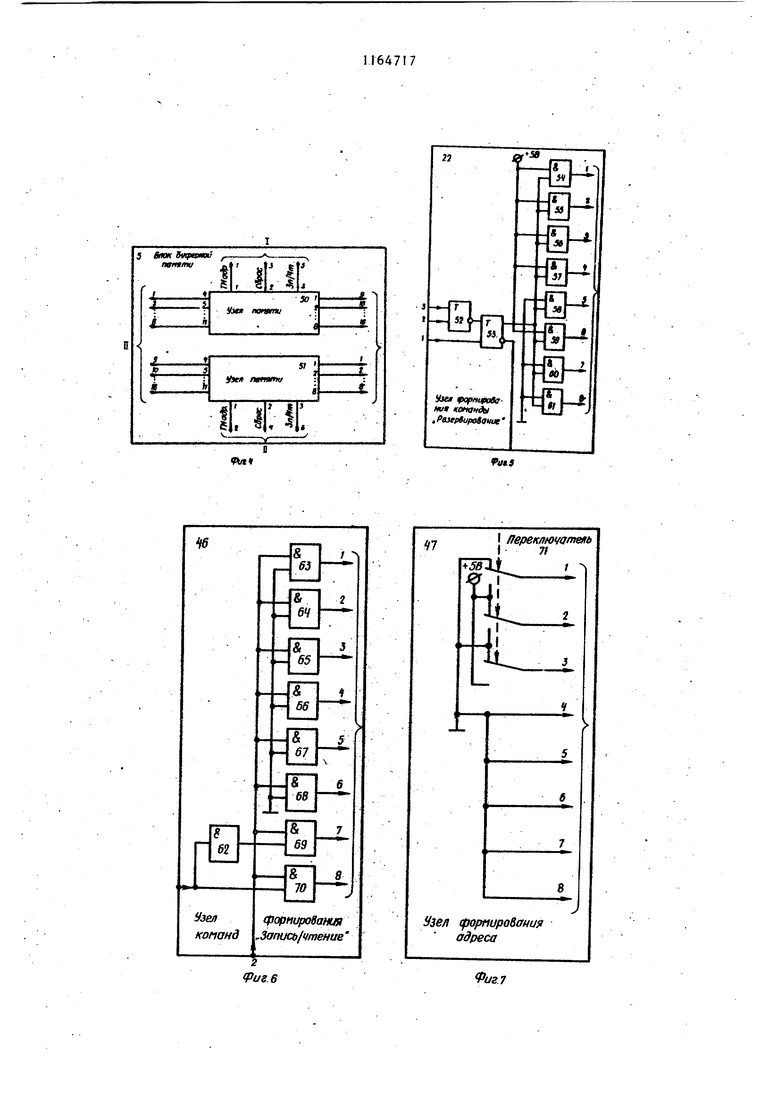

На фиг. 1 представлена структурная схема предлагаемого устройства-J на 4иг. 2 - блок-схема блока управления и синхронизации; на фиг. 3 блок-схема блока генерации команд обмена; на фиг. 4 - блок-схема блока буферной памяти-, на фиг. 5 - блоксхема узла формирования команды Ре:зервирование , на фиг. 6 - блок-схе5,

ма узла формирования команд Запись/ ;/Чтение ;на фиг. 7 - блок-схема уэла фop ffilp,oвaния адреса; на фиг, 8а,

6- диаграмма работы предлагаемого устройства в режиме на фиг. 9а, б, в - диаграмма работы предлагаемого устройства в режиме Вывод,.

Предлагаемое устройство ввода-вывода полутоновой информации (фиг. t) содержит блок 1 сканирования, аналого-хщфрсвой преобразователь, (АЦП) 2, цифро-аналоговый преобразователь (ЦАП 3, блок 4 управления и синхронизации (ВУ), блок 5 буферной памяти,, первьм, второй н третий коммутаторы 6-8. и блок 9 генерации команд обмена (ГКО); выход БУ 4 г подключен к njspaoMy. входу АЦП 2 н входу ЦАП 3, выход которого подключен к входу блока сканирования выход которого подключен к второму .входу АЦП 2, выходы первой и второй групп блока подключены к входам соответственно nepBCrfi и второй групп БУ 4, к выходам первой группы которого подключены входы первой группы блока 5 буферной памяти, к входам второй группы которого подключены выходы групгай первого коммутатора 6,, к входам первой группы которого и входам первой группы второго коммутатора 7 подключены выходы второй группы БУ 4, к входам второй группы коммутатора 7 подключены выходы группы блока S буферной памяти, выходы группы коммутатора .7подключены к входам первой группы третьего коммутатора 8, выходы первой группы которого подключены к входам второй группы коммутатора 6, выходы группы АЦП 2 подключены к входам второй группь коммутатора 8, Ешходы второй группы которого подключены к входам группы ЦАП 3, выходы третьей группы БУ 4 подключены к входам первой группы блока 9 ГКО, выходы первой группы которого подключены к входам третьей группы БУ4 выходы второй группы блока 9 ГКО подключеш к входам третьей группы ком татора 8, выходы третьей группы которого подключены к входам второй группы блока 9 ,ГКО , в ходы и входы третьих групп которого являются соответственно .

выходами и входами групп устройства.

Блок 4 управления и синхронизации (4иг. 2) содержит четвертый и пятый коммутаторы, первый и второй счетчики, первый триггер, элемент 5 коммутации, первый элемент И и узел 10 формнрования импульсов, к первому входу которого подключен первый выход четвертого комм татора 1, второй выход которого подключен к

О первому входу первого элемента И 12, выход которого подклюгген к второму входу узла 10 форьотроиання импульсов, первый вход элемента коммутации 13 подклю.чен к шине логической

15 единицы, а его выход подключен к первому входу первого триггера 14, второму входу элемента И 12 и тре.тьему входу узла 10 формирования импульсов, выход первого счет1шка

20 15 подключен к его первому входу, второму входу пятого коммутатора 16, второму входу триггера 14, выходь которого подключены к группе входов коммутатора 16 и являются

25 второй группой выходов БУ 4, третий выход коммутатора 11 подключен к первому входу коммутатора 16, выходы которого являются первой группой выходов БУ 4, второй вход

30 элемента 13 коммутации подключен к ши)е логического нуля, выход узла 10 формирования импульсов подключен к второму входу счетчика 15, третьему входу коммутатора 16 и

35 является выходом БУ 4, выход второго счетчика 17 подключен к его второму входу и пятому входу коммутатора 16, четвертый в;1сод которого объединен с первым входом счет40 чика 17, первый, второй и третий, четвертый входы коммутатора 11 являются входами первой и второй групп БУ 4 соответственно., четвертый вход .узла 10 формирования импульсов и

45 первый вход счетчика If являются входа№1 третьей группы блока БУ 4, выходы счетчиков 15 и 17, элемента. 13 коммутации, элемента И 12, третий выход коммутатора 11 являются

50 выходами третьей группы БУ 4. .

Блок 9 генерации команд обмена (фиг. 3) содержит генератор импульсов, со второго по шестнадцатый зле-, менты И, с первого по пятый эле мен- .

55 ты ИЛИ, со второго по шестой триггеры, первый и второй дешифраторы, третий счетчик, первый ;и второй и третий формирователи, В1ыход второ5To элемента И 18 подключен к второму входу второго триггера 19, первому входу третьего счетчика 20 первому входу, первого элемента ИЛИ первому входу первого формирователя 22,первому входу третьего триггера 23,выход триггера 19 подключен к первому входу третьего элемента И 24, к. второму входу которого подключен выход генератора импульсов 25, к третьему входу элемента. И 24 подключен выход второго элемен та ИЛИ 26, выход элемента И 24 подключен к второму входу счетчика 20, выходы которого подключены к входам первого дешифратора 27, первый выход которого подключен к первому входу элемента ИЛИ 26, второй вход которого и первый входчетвертого триггера 28 подключены к второму вы ходу дешифратора 27, второй вход триггера 28 объединен с вторым входом формирователя 22, третий выход дешифратора 27 подключен к третьему входу элемента ИЛИ 26 и первому входу пятого триггера 29, к второму входу которого и четвертому входу элемента ИЛИ 26 подключен выход чет вертого элемента И 30, выход триггера 29 подключен к входу пятого элемента И 3, четвертый выход дешифратора 27 подключен к первому входу шестого триггера 32 и первому входу элемента И 30, пятый выход дешифратора 27 подключен к первому входу шестого элемента И 33, второй вход которого и первый вход седьмого элемента И 34 объединены, выход элемента И 33 подключен к вто рому входу триггера 32 и пятому входу элемента ИЛИ 26, шестой выход дешифратора 27 подключен к второму входу элемент а И 34 и первому входу восьмого элемента И 35, выход эле.мента И 34 подключен к первому вхо,ду третьего элемента ИЛИ 36, входам девятого и десятого элементов- И 37 и 38, к второму входу третьего элемента ИЛИ 36 подключен первый выход триггера23, второй выход которого подключен к первому входу одиннад цатого элемента И 39, седьмой выход дешифратора 27 подключен к второму входу элемента И 39 и первому входу двенадцатого элемента И 40, первые входы тринадцатого и четырнадцатог элементов И 41, 42 и третий вход элемента И 39 объединены. 176. выход элемента И 39 подключен к второму входу элемента ИЛИ 21, . к третьему входу которого подключен выход элемента И 40, второй вход которого объединен с первыми входами элемента И 18 и пятнадцатого элемента И 43 и вторым входоь элемента И 35,выход элемента ИЛИ 21 подключен к второму входу элемента И 41, выход которого подключен к входу шестнадцатого элемента И 44, входы группы которого являются входами второй группы блока 9 ГКО, а выходы подключены к входам первой группы четвертого элемента ИЛИ 45, выходы группы формирователя 22 подключены к входам группы элемента И 37, выходы которого подключены к входам второй группы элемента ИЛИ 45, выход формирователя 22 подключен к второму входу второго формирователя 46, выходы которого подключены к входам группы элемента И 38, выходы которого подключены к входам третьей группы элемента ИЛИ 45, выходы третьего форм11ровагеля 47 подкпючень к входам группы элемента И 31, выходы которого подключены к входам четвертой группы элемента ИЛИ 45, с первого по восьмой входы второго дешифратора 48 и со второго по девятый входь элемента И 42 соответственно объеда)нены, выходы элемента И 42 являются выходами второй группы блоке 9 ГКО, П0РВЫЙ выход дешифратора 48 подключен к второму входу элемента И 18, второй выход дешифратора 48 подключен к третьему входу элемента И 35, третий выход дешифратора 48 подключен к третьему входу элемента И 35, третий выход дешифратора 48 подключен к второму входу элемента И 43, выход которого подключен к первому входу пятого элемента ИЛИ 49, выход которого подключен к второму входу триггера 23, выход элемента И 35 подключен к шестому входу элемента ИЛИ 26, третий вход элуемента И 39 и первый вход элемента ИЛИ 49 являются группой выходов блока 9 ГКО, первый вход и второй вход триггеров 19 и 28 соответственно третий вход первого формирователя 22, второй вход элемента ИЛИ 49 и первый вход фсчэмирователя 46 являются вхо- даьи первой группы блока 9 ГКО, вторые входы элементов И 30, 33 и 40,

третий вход элемента И 39, с первого по восьмой входы дешифратора 48 являются входами третьей группы блока 9 ГКО, выходы элемента ИШ 45 триггеров 28, 29 и 32, элементов

ИЛИ 21, 36 являются выходами третьей группы блока 9 ГКО, .

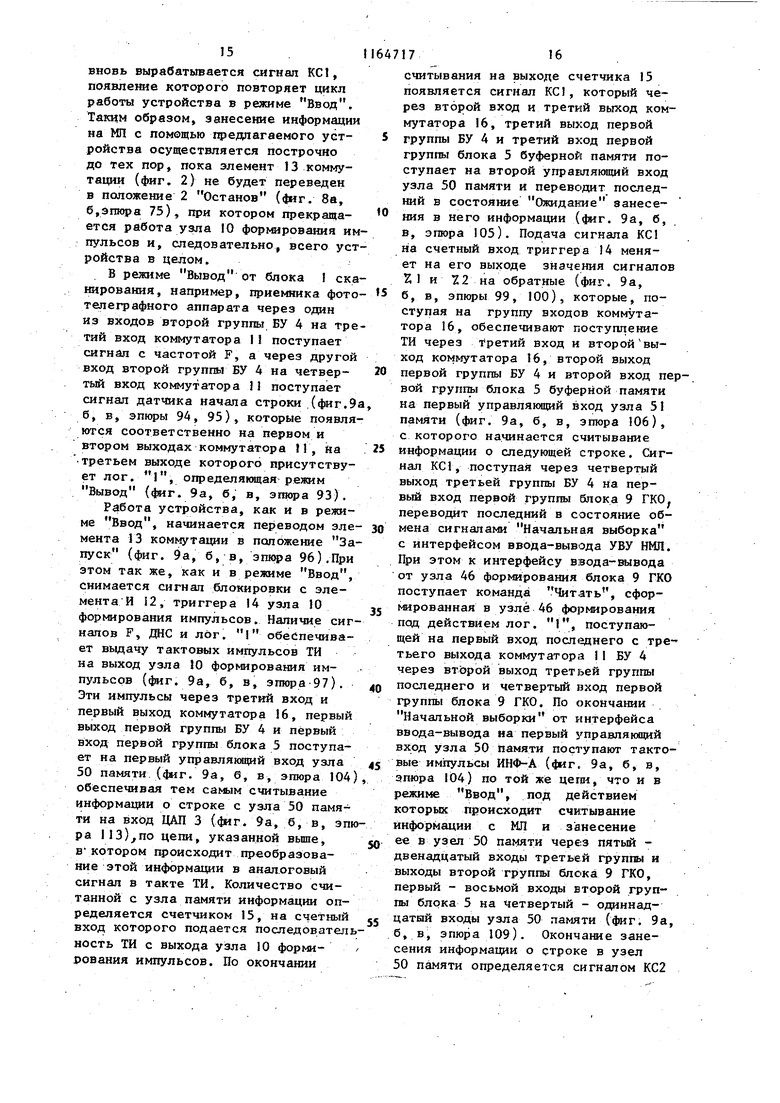

Блок 5 буферной памяти (фиг. 4) содержит первый и второй узлы памяти 50 и 51 соответственно, входы первых групп которых являются входами rtepвой группы блока 5, входы вторых групп узлов 50 и 5I памяти являются вxoдa м второй группы блока 5f выходы узлов 50 и 51 памяти являются выходами блока 5.

В качестве узлов 50 и 51 могут быть использованы любые стандартныеузлы памяти.

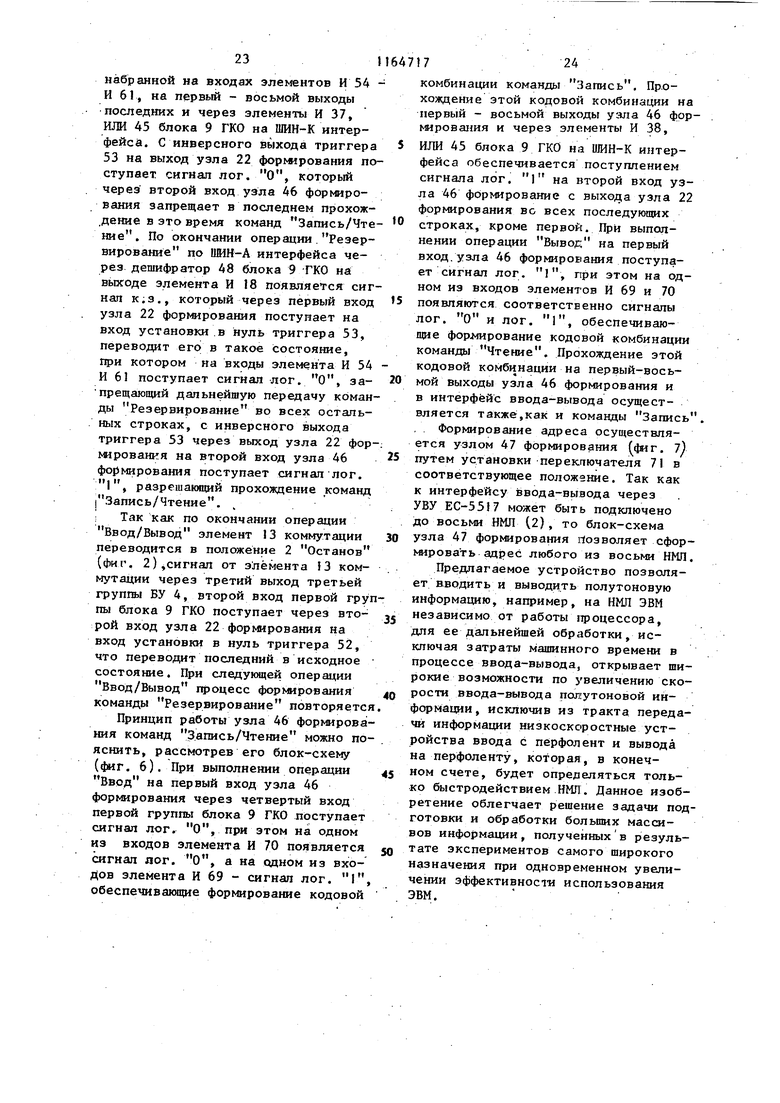

Узел 22 формирования (фяг. 5)

предназначен для формирования команды Резервирование, необходимой для резервирования, например УВУ НМЛ при работе последнего с предлагаеьым устройством, и содержит

триггеры 52, 53 и элементы И 54 И 61, третий вход узла 22 формирования подключен к счетному входу триггера 52, к входу установки в нуль которого подключен второй вход узла 22 формированияj первый вход последнего подключен к входу установки в нуль триггера 53, к счетному входу которого подключен инверсный выход триггера 52, прямой выход триг гера 53 подключен, : одному из входов элементов И 54 - И 6I, выходы которых подключены соответственно к первому - восьмому выходам группы узла 22 формирования, к выходу которого подключен инверсный выход триггера 53, к другому взсоду элементов И 54 - 57,- 59 подключена шина логической единицы, к другому входу элементов И 58, 60, 61 подключена шина логического нуля. Узел 46 формирования (фиг. б) предназначен для формирования команд Зачтись/Чтение, поступающих в интерфейс ввода-вывода УВУ НМЛ, и содержит элементы И 62 -. 70, к входу элемента И 62 подключен пёрвыА вход узла 46 формирования, с которым соединен один из входов .элемента И 70j выход элемента И 62 подключен к одному из входов элемен.та И 69, к одному из входов элементов И 63-68 подключена шина логического нуля f второй вход узла 46 формирования подключен к другому входу элементов И 63 - 70, выходы которых подключены соответственно к первомувосьмому выходам группы узла 46 формирования. Узел 47 формирования (фиг. 7) предназначен для формирования адреса НМП и содержит переключатель 71 с тремя контактными груп.пами, к одним входам которых подключена шина логической единицы, а к другим - тина логического нуля, а выходы подключены соотве;тственно к первому - третьему выходам группы узла 47 формирования, к четвертому восьмому выходам групгы которого подключена шина логического нуля.

Предлагаемое устройство может работать в двух режимах Ввод и Вывод.

В режиме Ввод видеосигиап с выхода блока 1 сканирования, наприме датчика фототелеграфного аппарата, поступает на. второй .вход АЦП 2, где под действием тактовых импульсов (ТИ) от БУ 4 на первом входе АЦП 2 преобразуется в цифровой код с частотой ТИ, кратной частоте сигнала управления, поступающего в БУ 4 чере входы первой группы из блока I сканирования . Цифровой код через выходы группы АЦП 2, входы второй группы и выходы первой группы коммутатора 8, входы второй и выходы групп коммутатора 6 под действием управляющих сигналов Z 1 и Z 2, сформированных в БУ 4 и поступающих на входы первой группы коммутатора 6, поступает на входы второй группы блока 5 буферной памяти. Поступление цифровой информации в блок 5 буферной памяти осуществляется побайтно под действием ТИ БУ 4, поступакицих в блок 5 буферной памяти через входы первой группы последнего.

Таким образом, данный режим харак теризуется тем, что меясду преобразованием видеосигнала ,U 2 в цифровой код и занесением его в блок 5 буферной памяти существует жесткая синхронизирующая связь, осуществляемая посредством применения единой тактовой последовательности БУ 4. Количество занесенных в блок 5 буферной памяти кодовых комбинаций определяется размерами строки фотоносителя блока 1 сканирования.

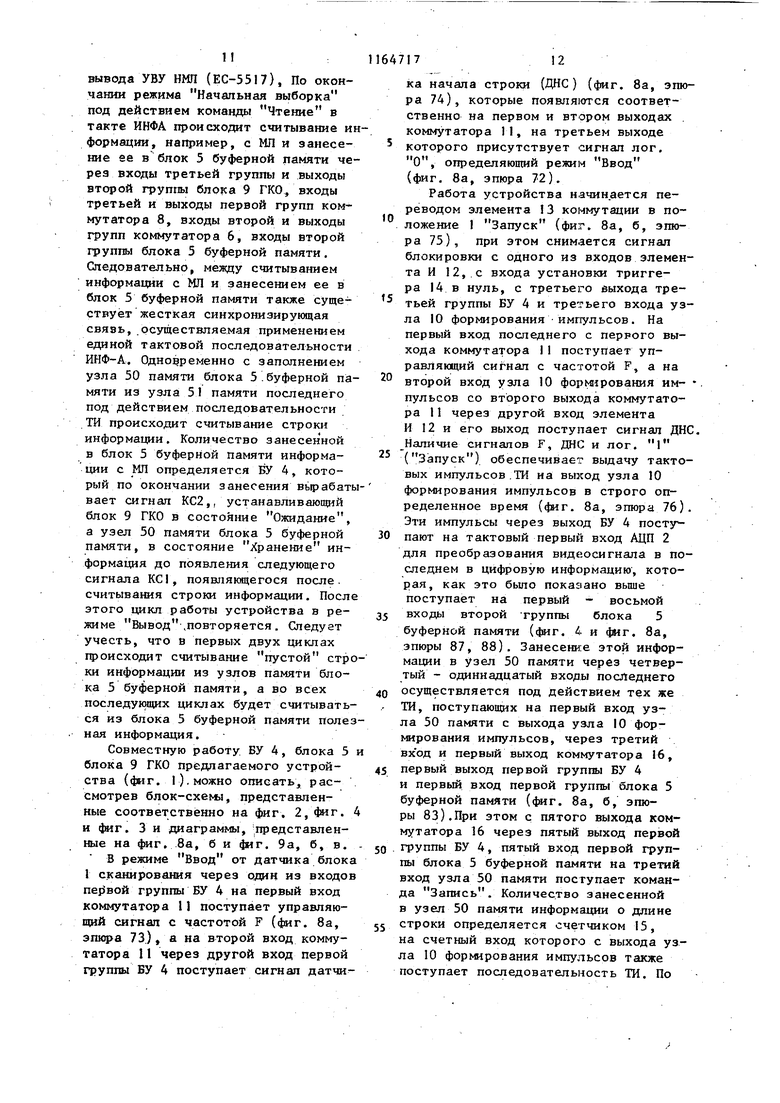

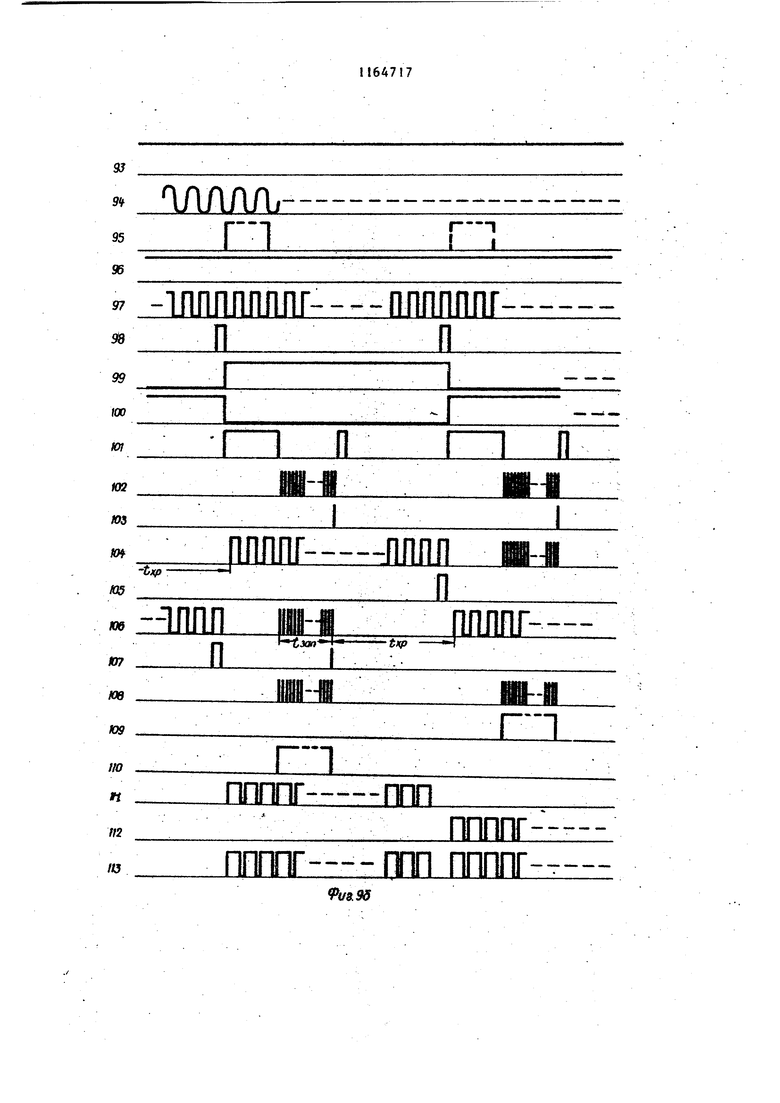

На фиг. 8-9 изображены зпюры 72-113 напряжений устройства. После занесения всей строки информации в блок 5 буферной памяти в БУ 4 .вырабатывается управляющий сигнал Конец строки КС, обеспечивающий смену значений сигналов Z. и Z, в результате чего на входы первой группы блока 5 буферной памяти поступ.ают управляющие сигналы из ВУ 4, позволяющие установить в блоке 5 буферной памяти узел 50 памяти в состояние Чтение, а узел 51 памяти - Запись информации. Кроме того, под действием сигнала КС1 БУ 4, поступающего через входы первой группы в блок 9 ГКО, последний устанавливается в режим Началь ная выборка, во время которого в блоке 9 ГКО вырабатывается команда Запись, поступающая через выходы третьей группы последнего на входы группы устройства, например, интерфейс ввода-вывода УВУ НМЛ (EC-55I7) По окончании режима Начальная выборка под действием команды Запис в такте ИНФ-А от УВУ НМЛ через входы третьей группы и выходы первой группы как блока 9 ГКО, так и БУ 4, поступаюищх на входы первой группы блока 5 буферной памяти , в последнем происходит считывание информа1и из ранее заполненного узла памяти и передача ее через выходы группы блока 5 буферной памяти, входы вто рой группы и выходы группы коммутатора 7, входы первой группы и выходы третьей группы коммутатора 8 входьг второй группы и выходы третье группы блока 9 ГКО на вход интерфей са УВУ НМЛ с последующим занесением информации на МП, Таким образом, между считыванием информации с блока 5 буферной памяти и занесением ее на МЛ также существует жесткая синхронизирующая связь, осуществляемая посредством применения единой тактовой последовательности ИНФ-А УВУ НМЛ. Одновременно со считыванием информации из заполненного узла памяти блока 5 буферной памяти,в свободный узел памяти последнего происходит занесение информации из блока 1 сканирования через АЦП 2. Количество считанной из блока 5 буферной памяти информации равно количеству занесенной в него информации и контролируется БУ 4, которы по окончании считывания информации 1710 вырабатывает сигнал КС2, обеспечивающий установку узла 50 памяти блока 5 и блок 9 ГКО в состояние Ожидание (j-ак как T Т|, по вления следующего сигнала КС1, появляющегося по мере заполнения узла 51 памяти блока 5 следующей строкой информации. После этого цикл работы устройства в режиме Ввод повторяется . В режиме Вывод от блока 1 сканирования, например, щтемняка фототелеграфного аппарата, через входы второй группы в БУ 4 поступают управляющие сигналы, обеспечивающие формирование ТИ в БУ 4, под действием которых из блока 5 буферной памяти происходит побайтное считывание информации о строке через выходы группы блока 5 буферной памяти, вхо-. ды второй и выходы групп коммутатора 7, входы первой и выходы второй групп коммутатора 8 на входы группы ЦАП 3, с выхода котсчого в такте ТИ БУ 4 в виде аналогового сигнала информация поступает, на вход блока i сканирования, например ycиJв тeля записи приемника фототелеграфного аппарата. Таким образом, Мевду считыванием информации из блока 5 буферной памяти и преобразованием ее в аналоговый сигнал ЦАП 3 существует жесткая синхронизирующая связь, осуществляемая посредством применения единой тактовой последовательности ТИ БУ 4. Количество считанной из блока 5 буферной памяти информации, ощ)еделя- . емое длиной строки фотоносителя, также контролируется БУ 4, который, по окончании считывания одной строки, вырабатывает сигнал КС 1,обеспечивающий смену значений сигналов Z 1 и Z 2, в результате чего на входы перпервой группы блока 5 буферной памяти поступают управляющие сигналы из БУ 4, позволяющие установить в блоке 5 узел 50 памяти в состояние Запись, а узел 51 памяти - Чтение информации. Кроме того, под дейдействием сигнала КС1 БУ 4, поступающего в блок 9 ГКО через входы первой группы,последний переходит в режим Начальная выборка, во время которого формируется команда Чтение, поступающая через выходы третьей группы блока 9 ГКО на входы труппы, например, интерфейса вводавывода УВУ НМЛ (ЕС-5517), По окончании режима Начальная выборка под действием команды Чтение в такте ИНФА происходит считывание информации, например, с МП и занесение ее в блок 5 буферной памяти через входы третьей группы и выходы второй группы блока 9 ГКО, входы третьей и выходы первой групп коммутатора 8, входы второй и выходы групп коммутатора 6, входы второй группы блока 5 буферной памяти, Следовательно, между считыванием информации с Ш и занесением ее в блок 5 буферной памяти также существует жесткая синхронизирующая связь, осуществляемая применением единой тактовой последовательности ИНФ-А. Одновременно с заполнением узла 50 памяти блока 5.буферной памяти из узла 51 памяти последнего под действием последовательности ТИ происходит считывание строки информации. Количество занесенной в блок 5 буферной памяти информации с МП определяется БУ 4, который по окончании занесения вь1рабатывает сигнал КС2,, устанавливаюпщй блок 9 ГКО в состояние Ожидание, а узел 50 памяти блока 5 буферной памяти, в состояние Хранение информация до появления следующего сигнала КС1, появляющегося после, считывания строки информации. После этого цикл работы устройства в режиме Вывод .повторяется. Следует учесть, что в первых двух циклах гфоисходит считывание пустой строки информации из узлов памяти блока 5 буферной памяти, а во всех последующих циклах будет считываться из блока 5 буферной памяти полезная информация.

Совместную работу. ВУ 4, блока 5 блока 9 ГКО предлагаемого устройства (фиг. I).можно описать, рассмотрев блок-схем 1, представленные соответственно на фиг. 2, Фиг. и 4иг. 3 и диаграммы, представленные на фиг. 8а, б и фиг. 9а, б, в. В режиме Ввод от датчика блока i сканирования через один из входов пе15вой группы БУ 4 на первый вход коммутатора I1 поступает управляющий сигнал с частотой F (фиг. За, эпюра 73), а на второй вход коммутатора 11 через другой вход первой группы БУ 4 поступает сигнал датчика начала строки (ДНС) (фиг. За, эпюра 74), которые появляются соответственно на первом и втором выходах коммутатора М, на третьем выходе которого присутствует сигнал лог. О, определяющий режим Ввод (фиг. За, эпюра 72).

Работа устройства начинается переводом элемента 13 коммутации в положение 1 Запуск (фиг. За, б, эпюра 73), при этом снимается сигнал блокировки с одного из входов элемента И 12, с входа установки триггера 14 в нуль, с третьего выхода третьей группы БУ 4 и третьего входа узла 10 формирования импульсов. На первый вход последнего с первого выхода коммутатора I1 поступает управляющий сигнал с частотой Р, а на

второй вход узла 10 формирования им- пульсов со второго выхода коммутатора 11 через другой вход элемента И 12 и его выход поступает сигнал ДНС. Наличие сигналов F, ДНС и лог. 1

(Запуск) обеспечивает выдачу тактовых импульсов.ТИ на выход узла 10 формирования импульсов в строго определенное время (фиг. За, эпюра 76). Эти импульсы через выход БУ 4 посту

пают на тактовый первый вход АЦП 2 для преобразования видеосигнала в последнем в цифровую информацию, которая, как это было показано выше поступает на первый - восьмой

входы второй труппы блока 5 буферной памяти (фиг. 4 и фиг. За, эпюры 37, 33). Занесенн:е этой информации в узел 50 памяти через четвертый - одиннадцатый входы последнего

осуществляется под действием тех же ТИ, поступающих на первый вход узла 50 памяти с выхода узла 10 формирования импульсов, через третий вход и первый выход коммутатора 16,

первый выход первой группы БУ 4

и первый вход первой группы блока 5 буферной памяти (фаг. За, б, эпюры 33).При этом с пятого выхода коммутатора 16 через пятый выход первой

группы БУ 4, пятый вход первой группы блока 5 буферной памяти на третий вход узла 50 памяти поступает команда Запись. Количество занесенной в узел 50 памяти информации о длине

строки определяется счетчиком 15,

на счетный вход которого с выхода узла 10 формирования импульсов также поступает последовательность ТИ. По

окончаний занесения одной строки информации на выходе счетчика 15 появляется сигнал КС1 (фиг. 8а, б, эпюра 77),который через второй вход и третий выход коммутатора 16, третий выход первой группы БУ 4, третий вход первой группы блока 5 буферной памяти (фиг. 8а, б, эпюра 84) поступает на второй управляющий вход узла 50 памяти, переводя последний в сое тояние Хранение информации. Поступление КС1 на счетный, вход триггера 14 меняет на его выходе значения сигналов Z I и.г 2 (фиг. 8а, б, эпюры 78, 79) на обратные, которые в свою очередь, поступая на группу входов коммутатора 16, обеспечивают поступпение последовательности ТИ со второго выхода последнего через второй выход первой группы БУ 4, второй вход первой группы блока 5 буферной памяти на первый управляющий вход узла 51 памяти (фиг. 8а, б, эпюра 85), а также.поступление команды Запись с шестого выхода коммутатора 16 через шестой выход первой группы БУ 4, шестой вход- первой группы блока 5 буферной памяти на третий управляющий вход узла 5I памяти. При этом с пятого выхода коммутатора 16.через пятый выход первой группы БУ 4, пятый вход первой группы блока 5 на третий управляющий вход узла 50 памяти поступает команда Чтение. Поступление сигнала KCI через четвертый выход третьей группы БУ 4 на первый .вход первой группы блока 9 ГКО приводит последний в состояние обмена сигналами Начальная выборка с интерфейсом ввода-вывода УВУ НМЛ СЕС-5517 В процессе обмена сигналами Начальная выборка от блока 9 ГКО к интерфейсу ввода-вывода поступает команда Запись, сформированная в узле 46 формирования (фиг. 6) под действием лог. 0 поступающего на первый вход последнего с третьего выхода коммутатора 11 БУ 4 (фиг. 2) через второй выход третьей группы последнего и четвертый вход первой группы блока 9 ГКО. По окончании Начальной выборки от интерфейса ввода-вывода на первый управляющий вход узла 50 памяти (фиг. 4)через третий вход третьей группы и первый выход первой груп1В)1 блока 9 ГКО, второй вход третьей

группы БУ 4, четвертый вход, и первый выход коммутатора 16, первый выход первой группы БУ 4 и первыйвыход первой группы блока 5 буферной памяти поступают тактовые импульсы ИНФ-А, под действием которых начинается побайтное считывание информации с первого - восьмого выходов узла 50 памяти и через девятый - шестнадцатый выходы группы блока 5 буферной памяти (фиг. 8а,. б, эпюра 90), входы второй и выходы групп коммутатора 7 (фиг. 1), входы первой и.выходы третьей групп коммутатора 8, входы второй группы блока 9 ГКО, входы и выходы групп элемента И 44 (4иг. З) ,входы первой группы и первый - девятый выходы элемента ИЛИ 45, седьмой --пятнадцатый выходы третьей группы блока 9 ГКО по ШИН-К интерфейса вводавывода УВУ НМЛ занесение ее на МП (фиг. 8а, б, эпюра 92). Окончание считывания информации с узла 50 памяти на №1 определяется сигнапом КС2 с выхода счетчика 17 (фиг. За, б, эпюра 82), на счетный вход которого поступает ИНФ-А. Сигнал КС2 через пятый выход третьей групгы БУ 4 поступает на пятый вход первой группы блока 9 ГКО и переводит последний в состояние Окончание операции с последукнцим переводом его в исходное состояние. Поступление сигнала КС2 через пятый вход и третий выход коммутатора 16, третий выход первой группы БУ 4, третий вход первой группы блока 5 на второй управляющий вход узла 50 патмяти переводит последний в исходное состояние (фиг. 8а,-б, эпюра 84 Одновременно со считыванием информации из узла 50 памяти на МП происходит занесение второй строки информации в узел 51 памяти с выхода АЦП 2 (фиг. 8а, б, эпюры 87, 89) под действием ТИ, поступающих на .первый управляющий вход узла 51 памяти с выхода узла 10 фор1 1рования импульсов БУ 4 (фаг, 2), через третий вход и второй выход коммутатора 16, второй выход первой группы БУ 4 и второй вход первой группы блока 5 буферной памяти (фи,г. 8а, б, эпюра 85). Количество занесенной в узе 51 памяти информации определяется счетчиком 15, на выходе которого по окончании занесения второй строки

вновь вырабатывается сигнал КС1, появление которого повторяет цикл работы устройства в режиме Ввод, Таким образом, занесение информации на Ш с помощью предлагаемого устройства осуществляется построчно до тех пор, пока элемент 13 коммутации (фиг. 2) не будет переведен в положение 2 Останов (фиг. 8а, б,эпюра 75), при котором прекращается работа узла 10 формирования импульсов и, следовательно, всего устройства в целом.

В режиме Вывод от блока I сканирования, например, приемника фототелеграфного аппарата через один из входов второй группы БУ 4 иа третий вход коммутатора I поступает сигнал с частотой F, а через другой вход второй группы БУ 4 на четвертьй вход коммутатора I1 поступает сигнал датчика начала строки (фиг.9а б, в, эпюры 94, 95), которые появляются соответственно на первом и втором выходах коммутатора И, На третьем выходе которого присутствует лог. I, определяквцая режим Вывод (4иг. 9а, б, в, эпюра 93).

Работа устройства, как и в режиме Ввод, начинается переводом элемента 13 коммутации в положение Запуск (фиг. 9а, б, в, этаара 96),При этом так же, как и в режиме Ввод, снимается сигнал блокировки с элемента И 12, триггера 4 узла 10 формирования импульсов. Наличие сигналов F, дне и лог. I обеспечивает выдачу тактовых импульсов ТИ на выход узла 10 формирования импульсов (фиг. 9а, б, в, эпюра 97). Эти импульсы через третий вход и первый выход коммутатора 16, первый выход первой группы БУ 4 и первый вход первой группы блока 5 поступает на первый управлякнций вход узла 50 памяти (фиг. 9а, б, в, эпюра 104) обеспечивая тем самым считывание информации о строке с узла 50 памяти на вход ЦАП 3 (фиг. 9а, б, в, эпюра 113),по цепи, указанной вьппе, В котором происходит преобразование этой информации в аналоговый сигнал в такте ТИ. Количество считанной с узла памяти информации определяется счетчиком 15, на счеТный вход которого подается последовательность ТИ с выхода узла 10 формирования импульсов. По окончании

считывания на выходе счетчика 15 появляется сигнал KCI, который через второй вход и третий выход коммутатора 16, третий выход первой группы БУ 4 и третий вход первой группы блока 5 буферной памяти поступает на второй упра 1лякщий вход узла 50 памяти и переводит последний в состояние Ожидание занесения в него информации (г. 9а, б, в, эпюра 105). Подача сигнала КС1 на счетный вход триггера 14 меняет на его выходе значения сигналов %1 и 7,2 на обратные (фиг. 9а, б, в, эпюры 99, 100), которые, поступая на группу входов коммутатора 16, обеспечивают поступление ТИ через Третий вход и второйвыход коь{мутатора 16, второй выход первой группы БУ 4 и второй вход певой групшг блока 5 буферной памяти на первый управлякмций вход узла 51 памяти (фиг. 9а, б, в, эпюра 106), с которого начинается считывание информации о следующей строке. Сигнал КС1, поступая через четвертый выход третьей группы БУ 4 на первый вход первой группы блока 9 ГКО, переводит последний в состояние обмена сигналами Начальная выборка с интерфейсом ввода-вывода УВУ НМЛ. При этом к интерфейсу ввода-вывода от узла 46 формирования блока 9 ГКО поступает команда Читать, сфор1 «рованная в узле 46 формирования под действием лог. I, поступающей на первый вход последнего с третьего выхода коммутатора 1I ВУ 4 через второй выход третьей группы последнего и четвертый 1зход первой группы блока 9 ГКО. По окончании Начальной выборки от интерфейса ввода-вывода на первый 5праБЛЯюа(ий вход узла 50 памяти поступают тактовые импульсы ИНФ-А (фиг. 9а, б, в, эпюра 104) по той же цеги, что и в режиме Ввод, под действием которых происходит считывание информации с МЛ и занесение ее в узел 50 памяти чере;з пятый двенадцатый входы третьей груп1Ы и выходы второй группы блока 9 ГКО, первый - восьмой входы второй группы блока 5 на четвертый - одиннадцатый входы узла 50 памяти (фиг. 9а б, в, эпюра 109). Окончание занесения информации о строке в узел 50 памяти определяется сигналом КС2 (фиг. 9а, б, в, эпюра 103) с выхода счетчика 17, на счетный вход которого также поступают ИНФ-А. Сигнал КС2, поступая через пятый выход третьей группы БУ 4 на пятый вход первой группы блока 9 ГКО, переводит последний в состояние Окон чание операт.ши с последующим переводо г его в исходное положение, а поступпение КС2 на второй управляющий вход узла 50 памяти по той же цели, что и в режиме Ввод, подготайливает последний к хранений занесенной в него информации.Одновременно с занесением информации с МЛ в узел 50 памяти, происходит счи тывание информации о второй строке с узла 51 памяти, как было показано выше. Количество считанной информации и в этом случае определя ется счетчиком 15, на выходе которо го по окончании считывания вновь вы рабатывается сигнал КС1, появление которого повторяет цикл работы устройства в режиме Вывод. Следует учесть, что в первых двух циклах происходит считывание пустой стро ки из узлов памяти блока 5 буферной памяти, а во всех последующих циклах из блока 5 будет считываться полезная информация. Вывод всей информации с МЛ заканчивается тогда, когда, на очередной сигнал КС1 после начальной выборки, из интерфейса ввода - вывода УВУ НМЛ на пятый двенадцатый входы третьей группы блока 9 ГКО поступает кодовая комбинация Конец группы зон (строк), которая дешифрируется дешифратором 48 блока 9 ГКО (фиг. 3) ив виде сигнала Запрет со второго выхода первой группы последнего через первый, вход третх ей группы БУ 4 поступает на четвертый вход узла 10 формирования импульсов, прекращая тем самым работу последнего и всего уст ройства в целом. . Работа блока 9 ГКО (фиг. З) характеризуется тремя этапами 1. Начальная выборка, 2. Передача данных и 3. Окончание операций (фиг. 8а, б, эпюры 80, 81 и фиг. 9а б, в, эпюры 101, 102). Этап Начальная выборка, идентичный для режимов Ввод и Вывод начинается после запуска развертки в блоке I сканирования с появлением сигнала КС1 через первый вход 1718 первой группы блока 9 ГКО на счетном входе триггера 19, в результате чего устанавливается высокий потенциал на первом входе элемента И 24, на третьем входе последнего также присутствует высокий потенциал с первого выхода дешифратора 27 череэ элемент ИЛИ 26, так как счетчик 20 находится в исходном состоянии. Это обеспечивает прохождение ТИ с выхода генератора 25 через второй вход . элемента И 24 на счетт Й вход счетчика 20. Первый ТИ,.поступивпшй в счетчик 20, возбуждает сигнал на втором выходе дешифратора 27, который, пройдя элемент ИЛИ 26, обеспеI чиваетпоступпение второго ТИ на вход счетчика 20. Одновременно сиг-. нал со второго выхода дешифратора 27 воздействует на вход триггера 28, на другой вход которого подана лог. 1 с элемента 13 коммутации через третий выход третьей группы БУ 4 и второй вход первой группы блока 9 ГКО. На выходе триггера 28 появляется сигнал РАБ-К, поступающий через первый выхо;ч третьей группы блока 9 ГКО в интерфейс ввода вывода УВУ НМЛ. С приходом: второго ТИ в счетчик 20 на третьем выходе дешифратора 27 появляется сигнал, обеспечивающийчерез элемент ИЛИ 26 поступление третьего ТИ на вход счетчика 20 и воздействующий на вход триггера 29. На выходе последнего появляется сигнал АДР-К, поступающий в интерфейс ввода - вывода череэ второй выход третьей группы блока 9 ГКО и воздействующий также на вход элемента И 31, что разрешает прохождение адреса с выхода узла 47 формирования через элемент И 31, элемент ИЛИ 45 и седьмой - пятнадцатый выходе.1 третьей группы блока 9 ГКО по ШИН-К в интерфейс. С приходом третьего ТИ в счетчике 20 на четвертом выходе дешифратора 27 появляется сигнал, посредством которого на выходах триггера 32 появляются сигналы ВБР-К и РВБ-К, поступающие соответственно через третий и четвертый выходы третьей группы блока 9 ГКО в интерфейс ввода-вывода, и одновременно подготавливается элемент И 30 к приему сигнала РАБ-А, из интерфейса. В ответ на последовательность сигналов РАБ-К, АДР-К, ВБР-К и РВБ-К инт рфейс выдает сигнал РАВ-А, который

через первый вход третьей группы блока 9 ГКО и элемент И 30 обеспечивает прохождение четвертого ТИ на вход счетчика 20 и снимает сигнал АДР-К и адрес с интерфейса, В ответ на сня тие сигнала ДЦР-К на втором входе третьей группы блока 9 ГКО появляется сигнал АДР-А, совместно с сигналом пятого выхода дешифратора 27, воздействующим на вход элемента И 33 выходной сигнал последнего воздействует на триггер 32, снимая сигналы ВБР-К и РВБ-К/ а через пятый вход элемента ИЛИ 26 обеспечивает прохождение пятого ТИ на вход счетчика 20, С приходом пятого ТИ на шестом выходе дешифратора 27 появляется сигнал, который совместно с сигналом АЦР-А воздействует на элемент И 34, выходной которого, пройдя

через элемент ИЛИ 36, вырабатывает сигнал УПР-К через пятый выход третьей группы блока 9 ГКО к интерфейсу, а также сигнал к элементам И 37 и 38, р-азрешан щий прохождение на

ШИН-К команды Резервирование или Запись/Чтение, сформированных соответственно, узлами 22 и 46 формирования. Управление вьщачей команд Запись или Чтение осуп1ествляется подачей соответственно лог. О или лог. 1 с третьего выхода тре.Тьей группы БУ 4 через четвертый вход первой группы блока 9 ГКО на первый вход узла 46 формирования.

В.первой строке сигналом ДНС от блока 1 сканирования на ШИН-К выводится команда Резервирование, а во всех последующих строках в зависимости от режима Ввод или Выводсоответственно команда Запись или .Чтение. В ответ на УПР-К в интерфейсе снимается сигнал АДР-А, тем самым снимая сигнал УПР-К и команду, выставленную на 11МН-К. В результате этого интерфейс отвечает через четвертый вход третьей группы блока 9 ГКО сигналом УПР-А с байтом состояния Готово по ШИН-А (пятый двенадцатый входы третьей группы бло ка 9 ГКО), последний дешифруется дешифратором 48 Под воздействием сигналов со второго выхода дешифратора 48 ynP-Ai и шестого выхода девшфратора 27 элемент И 35 вырабатывает сигнал, обеспечивающий прохождение шестого ТИ на вход счетчика 20. С цриходом шестого ТИ на седьмом выходе дешифратора 27 появляется сигнап, воздействующий одновременно с сигналом УПР-К на элемент И 40, выходной сигнал которЧ)го через элемент ИЛИ 2, шестой выход третьей группы блока 9 ГКО в виде,ИНФ-К поступает в интерфейс. В ответ на ИНФ-К интерфейс снимает сигнал УПР-А и байт состояния с ШИН-А, что, в свою очередь, снимает сигнал ИНФ-К, На этом

прекращается этап Начальная выборка и блок 9 ГКО переходит к следующему этапу Передача данных, включающего в себя обмен данными между узлами 50 и 5I блока 5 буферной памяти и интерфейсом. Передача данных при вводе осуществляется по принципу

запрос-ответ. Интерфейс выставляет сигнал ИНФ-А, означаю11 1й запрос на передачу байта данных. Высокие потенциалы на первом и втором входах элемента И 39 обеспечивают состояние Ожидание. С приходом сигнала

ИНФ-А через третий вход третьей группы блока 9 ГКО на третий вход эле- мента И 39 последний вырабатывает сигнал, который через элемент ИЛИ 21, шестой выход третьей группы блока 9 ГКО в виде сигнала ИНФ-К поступает в интерфейс, а одновременно с сигналом воздействует на элемент И 41. Последний формирует строб, поступающий на вход элемента И 44, на входы группы которого в такте ИНФ-А поступает байт данных через входы второй группы блока9 ГКО из узлов 50 и 5 памяти. Простробированная информация с выходов группы элементов И 44 через элемент ИЛИ 45 выставляется на ШИН-К. Появление сигнала ИНФ-К ведет к прекращению сигнала ИНФ-А,, который, в свою очередь, прекращает ИНФ-К, После этого в интерфейсе вновь формируется ИНФ-А и процесс повторяется до полного освобождения узлов 50 и 51 памяти, которое; характеризуется появлением сигнгла КС2 на выходе счетчика 17 (фиг, 2), воздействующим через пятый вход первой группы блока 9 ГКО и элемент ИЛИ 49 на один из установочных входов триггера 23, изменяя состояние последнего таким образом, что его второй выход блокирует элемент И 39, прекращая посьшку сигнала ИНФ-К в ответ на ИКФ-А, закрывается схема формирования строба :к элементу И 44, прекращая передачу данныхСи гнал ом с первого выхода триггера 23 через элемент ИЛИ 36 и пятый выход третьей группы блока 9 ГКО в интерфейс посьшается сигнал УПР-К наличие которого означает, что переданный байт был последним. Н-а этом этап Передача данных в режиме Ввод прекращается. Передача данных при выводе осуществляется следующим образом. Интерфейс посыпает байт данных по 1IMH-A, сопровождая его сигналом , который после стробирования в элементе И 42, через выходы второй группы блока 9 ГКО заносится в узлы 50 и 51 памяти блока 5. Сигнал ИНФ-А, воздействуя одновременно на элемент И 39, находящийся в состоянии Ожидания, формирует ответный сигнал ИНФ-К, поступающий через элемент ИЛИ 21 в интерфейс сигнализируя о принятом байте даиных. Сигнал ИНФ-К снимает в интерфейсе сигнал ИНФ-А и байт данных с ШИН-А. Прекращение сигнала ИНФ-А, в свою очередь снимает сигнал ИНФ-К,После этого интерфейс посылает следующий байт данных, сопровождая его сигналом ИНФ-А, и процесс передачи .данных повторяется до тех пор, пока ;не закончится зона на МП и интер|фейс на прекратит.передачу данных. 1По окончании.этапа Передача даншлх начинается этап Окончание операции, идентичный для режимов Ввод и Вывод. Окончание операции начинается посылкой сигнала УПР-А интерфейсом, сопровождая его байтом состояния : Канал кончил по ШИН-А, который де ши(1ч ируется деши атором 48, сигнал с первого выхода которого совгместно с УПР-А воздействует на элемент И 18. На выходе последнего поя ляется сигнал Конец зоны (к.з.) , сбрасываюпдай триггеры 19, 23 и счетчик 20 в исходное состояние. Триггер 23 снимает, высокий потенциал с вход элемента ИЛИ 36, снимая тем самым . сигнал УПР-К fсформированного по око чании передачи данных в режиме Ввод Одновременно сигнал к.з., пройдя, элемент ИЛИ 21, выставляет сигнал ИНФ-К к интерфейсу, сигнализируя о гфинятии байта состояния Канал кончил. В ответ в интерфейсе снимаются сигналы РАБ-А и УПР-А, что вызывает прекращение сигнала ИНФ-К. На этом . этап Окончание операции и весь процесс ввода/вывода одной строки (зоны) заканчивается. Ввод/вывод последующих строк осуществляется по описанному эыше алгоритму с приходом сигнала КС1 . Количество вводимых и выводимых строк зависит от объема фотоинформации и прекращается при переводе элемента 13 коммутации в положение 2 Останов, в результате чего снимается сигнал РАБ-К, обеспечивая логическое отключение блока 9 ГКО от интерфейса н прекращение его работы. Кроме того, вывод зон с МП может происходить до тех пор, пока после очере.ного этапа Начальная /выборка по ШИН-А не поступит байт cocV тояния Особый случай - маркер групгы зон (м.г.з.) в сопровоящении сигнала УПР-А. Байт состояния дешифрируется дешифратором 48, сигнал с третьего выхода которого совместно с УПР-А воздействует на элемент И 43, выходной сигнал которого через элемент ИЛИ 49 воздействует на один иэ установочных входов,7РИггера 23. Последний сигналом с первого выхода устанавливает высокий потенциал на, входе элемента ИЛИ 36, на выходе которого формируется сигнал УПР-К к интерфейсу. Последний переходит к этапу Окончание операции по алгоритму, описанному выше, и блок 9 ГКО возвращается в исходное состояние. Сигнал с выхода элемента И 43 посылается также через второй выход первой группы блока 9 ГКО к узлу 10 формирования импульсов как и сигнал Запрет {см. фиг, 2), запрещая прохождение ТИ на выход последнего. На этом прекращается дальнейшая работа предлагаемого устройства. Принцип работы узла 22 формирова.ния можно пояснить, рассмотрев его блок-схеког (4иг. 5). Ери поступлении через третий вход узла 22 формирования на счетный вход триггера 52 первого импульса от ДНС, триггер 52 принимает такое состояние, при котором сигнал с его инверсного выхода воздействует на счетный вход триггера 53. При сигнале лог. 1 с прямого выхода триггера 53 происходит прохождение кодовой комбинации команды Резервирование, набранной на входах элементов И 54 И 61, на первый - восьмой выходы последних и через элементы И 37, ИЛИ 45 блока 9 ГКО на ШИН-К интерфейса. С инверсного выхода триггера 53 на выход узла 22 фор1«1рования по ступает сигнал лог. О, который через второй вход узла 46 формирования запрещает в последнем прохож.дение в это время команд Запись/Чте ние. По окончании операции.Резервирование по ШИН-А интерфейса через дешифратор 48 блока 9 ГКО на вьгходе элемента И 18 появляется сиг нал к;з,, который через первый вход узла 22 формирования поступает на вход установки в нуль триггера 53, переводит его в такое состояние. При котором на входы элемента И 54 И 61 поступает сигнал лог. О, запрещающий дальнейшую передачу коман ды Резервирование во всех остальных строках, с инверсного выхода триггера 53 через выход узла 22 фор ыирования на второй вход узла 46 формирования поступает сигнап лог. 1, разрешающий прохождение команд | Запись/Чтение. i Так как по окончании операции Ввод/Вывод элемент 13 коммутации переводится в положение 2 Останов (фиг. 2),сигнап от элемента 13 комнутации через третий выход третьей rpyniai БУ 4, второй вход первой гру пы блока 9 ГКО поступает через второй вход узла 22 формирования на вход установки в нуль триггера 52, что переводит последний в исходное состояние. При следующей операции Ввод/Вывод процесс формирования команды Резервирование повторяетс Принцип работы узла 46 формирова ния команд Запись/Чтение можно по яснить, рассмотрев его блок-схему (4мг. 6), При выполнении операции Ввод на первый вход узла 46 формирования через четвертый вход первой группы блока 9 ГКО поступает сигнал лог. О, при этом на одном из входов элемента И 70 появляется сигнал яог. о, а на одном из входов элемента И 69 - сигнал лог. I обеспечивающие формирование кодовой 724 комбинации команды Запись, Пр.охождение этой кодовой комбинации на первый - восьмой выходы узла 46 фор мровгатя и через элементы И 38, ИЛИ 45 блока 9 ГКО на UJHH-K интерфейса обеспечивается поступлением сигнала лог, 1 на второй вход узла 46 формирование с узла 22 формирования во всех последующих строках, кроме первой. При выполнении операции Вывод на первый вход.узла 46 формирования поступает сигнал лог. l, при этом на одном из входов элементов И 69 и 70 появляются соответственно сигналы лог, О и лог, Г обеспечивающие формирование кодовой комбинации команды Чтение. Прохождение этой кодовой комбинации на первый-восьмой выходы узла 46 формирования и в интерфейс ввода-вывода осуществляется также,как и команды Запись, Формирование адреса осуществляется узлом 47 формирования фиг, 7) путем установки перекггючателя 71 в соответствующее положение. Так как к интерфейсу ввода-вывода через УВУ ЕС-5517 может быть подключено до восьми НЮ (2), то блок-схема узла 47 формирования 11озволяет сфоркмровать адрес любого из восьми НМЛ, Предлагаемое устройство позволяет вводить и выводить полутоновую информацию, например, на НМЛ ЭВМ независимо от работы 1троце ссор а, для ее дальнейшей обработки, исключая затраты машинного времени в процессе ввода-вывода, открывает широкие возможности по увеличению скорости ввода-вывода пал утоновой информации, исключив из тракта передачи информации низкоскоростные устройства ввода с перфолент и вывода на перфоленту, которая, в конечном счете, будет определяться только быстродействием НИЛ. Данное изобретение облегчает решение задачи подготовки и обработки больших массивов информации , полученныхв результате экспериментов самого широкого назначения при одновременном увеличении эффективности использования ЭВМ,

//

I

КонмуЁmamof 2

.-о Э/1епент Jo коммутации , у

Г

fi/70/r управления и синхронизации

/ 2

/fo«wш

Ш г.

а

fnctmop

I

g

/ff

I 1

Ж iJ

I 1

ЛС2

Счетчиц 17

Риг.б

г/г/

ту выя.ЗкоНч УН

ЯЛЛАЛЛЛ 9.8а

Рие.9а

.95

| Космические исследования земных ресурсов | |||

| М.: Наука, 1975 | |||

| Устройство ввода-вывода полуто.новой информации в ЭВМ на базе серийного фототелеграфного оборудования (УБВИ) Инв | |||

| № Б | |||

| 814230 | |||

| Гос | |||

| per | |||

| № 79070374 ВНТИЦ. |

Авторы

Даты

1985-06-30—Публикация

1984-03-15—Подача