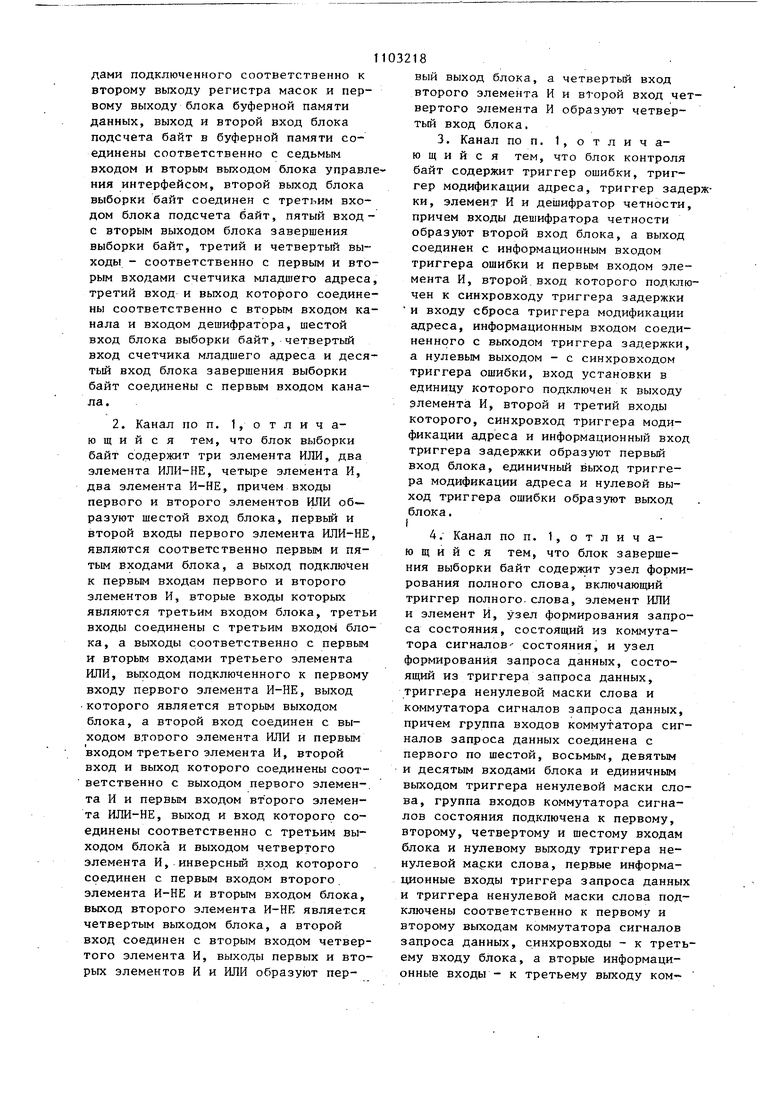

дами подключенного соответственно к второму выходу регистра масок и первому выходу блока буферной памяти данных, выход и второй вход блока подсчета байт в буферной памяти соединены соответственно с седьмым входом и вторым выходом блока управл ния интерфейсом, второй выход блока выборки байт соединен с третьим входом блока подсчета байт, пятый входс вторым выходом блока завершения выборки байт, третий и четвертый выходы - соответственно с первым и вто рым входами счетчика младшего адреса третий вход и выход которого соедине ны соответственно с вторым входом ка нала и входом дешифратора, шестой вход блока выборки байт, четвертый вход счетчика младшего адреса и деся тый вход блока завершения выборки байт соединены с первым входом канала. 2. Канал по п. 1, о т л и ч аю щ и и с я тем, что блок выборки байт содержит три элемента ИЛИ, два элемента ИЛИ-НЕ, четыре элемента И, два элемента И-НЕ, причем входы первого и второго элементов ИЛИ образуют шестой вход блока, первьй и второй входы первого элемента ИЛИ-НЕ являются соответственно первым и пятым входами блока, а выход подключен к первым входам первого и второго элементов И, вторые входы которых являются третьим входом блока, треть входы соединены с третьим входом бло ка, а выходы соответственно с первым и вторым входами третьего элемента ИЛИ, выходом подключенного к первому входу первого элемента И-НЕ, выход которого является вторым выходом блока, а второй вход соединен с выходом ВТОРОГО элемента ИЛИ и первым входом третьего элемента И, второй вход и выход которого соединены соответственно с выходом первого элемента И и первым входом второго элемента ИЛИ-НЕ, выход и вход которого соединены соответственно с третьим выходом блока и выходом четвертого элемента И, инверсньй вход которого соединен с первым входом второго элемента И-НЕ и вторым входом блока, выход второго элемента И-НЕ является четвертым выходом блока, а второй вход соединен с вторым входом четвер того элемента И, выходы первых и вто рых элементов И и ИЛИ образуют пер18вый выход блока, а четвертый вход второго элемента И и вТорой вход четвертого элемента И образуют четвертьй вход блока. 3. Канал по п. 1, о т л и ч аю щ и и с я тем, что блок контроля байт содержит триггер ошибки, триггер модификации адреса, триггер задержки, элемент И и дешифратор четности, причем входы дешифратора четности образуют второй вход блока, а выход соединен с информационным входом триггера ошибки и первым входом элемента И, второй вход которого подключен к синхровходу триггера задержки и входу сброса триггера модификации адреса, информационным входом соединенного с выходом триггера задержки, а нулевым выходом - с синхровходом триггера ошибки, вход установки в единицу которого подключен к выходу элемента И, второй и третий входы которого, синхровход триггера модификации адреса и информационный вход триггера задержки образуют первьй вход блока, единичный выход триггера модификации адреса и нулевой выход триггера ошибки образуют выход блока. ( 4. Канал по п. 1, отличающийся тем, что блок завершения выборки байт содержит узел формирования полного слова, включающий триггер полного.слова, элемент ИЛИ и элемент И, узел формирования запроса состояния, состоящий из коммутатора сигналов состояния, и узел формирования запроса данных, состоящий из триггера запроса данных, триггера ненулевой маски слова и коммутатора сигналов запроса данных, причем группа входов коммутатора сигналов запроса данных соединена с первого по шестой, восьмым, девятым и десятым входами блока и единичным выходом триггера ненулевой маски слова, группа входов коммутатора сигналов состояния подключена к первому, второму, четвертому и шестому входам блока и нулевому выходу триггера ненулевой марки слова, первые информационные входы триггера запроса данных и триггера ненулевой маски слова подключены соответственно к первому и второму выходам коммутатора сигналов запроса данных, синхровходы - к третьему входу блока, а вторые информационные входы - к третьему выходу ком

мутатора сигналов запроса данных, .четвертым выходом соединенного с входом установки единицы триггера запроса данных, выход которого является вторым выходом блока, инверсный и прямой входы элемента И подключены соответственно к второму и восьмому входам блока, а выход - к единичному входу триггера полного слова, нулевой вход и выход которого соединены соответственно с девятым входом блока и первым входом элемента ИЛИ, второй вход которого является седьмым входом блока, выходы элемента ИЛИ, коммутатора сигналов состояния и триггера запроса данных образуют первый выход блока.

5. Канал по п. 1, о т л и ч аю щ и и с я тем, что блок управления интерфейсом содержит семь триггеров, четыре элемента И, два элемента И-НЕ, элемент сравнения, элемент И-ИЛИ и элемент ИЛИ, причем вход сброса и выход первого триггера соединены соответственно с выходом первого элемента И и первым входом второго элемента И, выходом подключенного к информационному входу второго триггера-, вход сброса которого соединен с первым входом первого элемента И и нулевым выходом третьего триггера, выход с информационным входом третьего триггера, единичным выходом подключенного к первому входу элемента ИЛИ, выход которого является первым выходом блока, а второй вход соединен с единичным выходом четвертого триггера, информационный вход и вход сброса которого подключены соответственно к выходам третьего элемента И и первого элемента И-НЕ, а единичный и нулевой выходы - соответственно к прямому входу четвертого элемента И и первому входу второго элемента И-НЕ, выходы которых соеди3218

нены соответственнос информационным входом и входом сброса пятого триггера, единичным и нулевым выходами соответственно подключенного к первым входам первого элемента И-НЕ и третьего элемента И, второй вход которого соединен с вторым входом второго элемента И и выходом шестого триггера, информационным входом соединенного с выходом элемента И-ИЛИ, первый вход которого подключен к выходу элемента сравнения, первый и второй входы .элемента сравнения соединены соответственно с первым и седьмым входами блоки, выход седьмого триггера является третьим выходом блока, а выходы второго и пятого триг. геров образуют второй выход блока, информационные входы первого и седьмого триггеров подключены к второму входу первого элемента И, третьему входу третьего элемента И, инверсному входу четвертого элемента И, входу сброса третьего триггера итретьему входу блока, синхровходы первого, четвертого, пятого и седьмого триггеров подключены к второму входу второго элемента И-НЕ, синхровходы второго, третьего и шестого триггеров подключены к второму входу первого элемента И-НЕ, синхровходы первого и второго триггеров образуют пятый вход блока, второй и третий входы элемента И-ИЛИ, вход сброса шестого триггера, четвертый вход третьего элемента И и третий вход второго элемента И образуют второй вход блока, четвертые входы элемента И-ИЛИ и второго элемента И и пятый вход третьего элемента И образуют четвертый вход блока, пятый вход элемента И-ИЛИ соединен с первым входом блока, а вход установки в едийицу шестого трип ера подключен к шестому входу блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Селекторный канал | 1974 |

|

SU525081A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Селекторный канал | 1973 |

|

SU519703A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

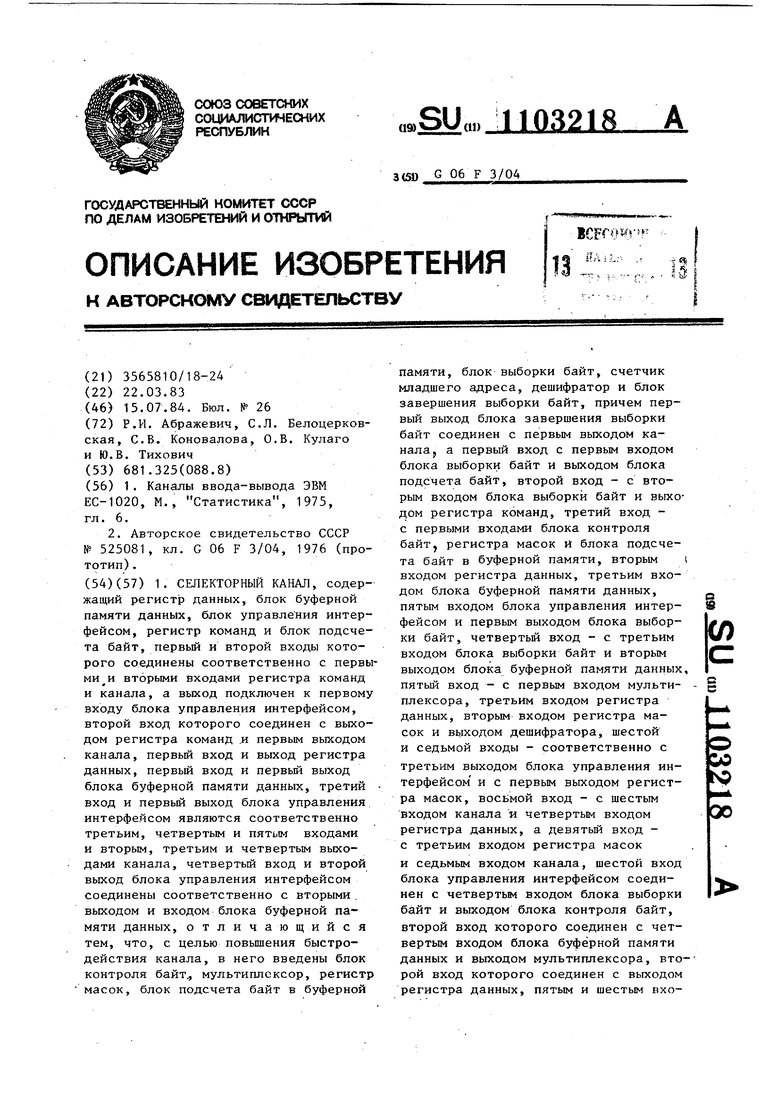

1. СЕЛЕКТОРНЫЙ КАНАЛ, содержащий регистр данных, блок буферной памяти данных, блок управления интерфейсом, регистр команд и блок подсчета байт, первый и второй входы которого соединены соответственно с первыми и вторыми входами регистра команд и канала, а выход подключен к первому входу блока управления интерфейсом, второй вход которого соединен с выходом регистра команд .и первым выходом канала, первый вход и выход регистра данных, первый вход и первый выход блока буферной памяти данных, третий вход и первый выход блока управления интерфейсом являются соответственно третьим, четвертым и пят)и1м входами и вторым, третьим и четвертым выходами канала, четвертый вход и второй выход блока управления интерфейсом соединены соответственно с вторыми выходом и входом блока буферной па мяти данных, отличающийся тем, что, с целью повышения быстродействия канала, в него введены блок контроля байт., мультиплексор, регистр масок, блок подсчета байт в буферной BCFfO r «AiL- , ig памяти, блок выборки байт, счетчик младшего адреса, дешифратор и блок завершения выборки байт, причем первый выход блока завершения выборки байт соединен с первым выходом канала, а первый вход с первым входом блока выборки байт и выходом блока подсчета байт, второй вход - с вторым входом блока выборки байт и выходом регистра команд, третий вход с первыми входами блока контроля байт регистра масок и блока подсчета байт в буферной памяти, вторым i входом регистра данных, третьим входом блока буферной памяти данных, § пятым входом блока управления интерфейсом и первым выходом блока выбор(Л ки байт, четвертьй вход - с третьим входом блока выборки байт и вторым выходом блока буферной памяти данных, с пятый вход - с первым входом мульти- с плексора, третьим входом регистра данных, вторым входом регистра масок и выходом дешифратора, шестой р и седьмой входы - соответственно с 00 NP третьим выходом блока управления интерфейсом и с первым выходом регистра масок, восьмой вход - с шестым эо входом канала и четвертым входом регистра данных, а девятый вход с третьим входом регистра масок и седьмым входом канала, шестой вход блока управления интерфейсом соединен с четвертьм входом блока выборки байт и выходом блока контроля байт, второй вход которого соединен с четвертым входом блока буферной памяти данных и выходом мультиплексора, вто-рой вход которого соединен с выходом регистра данных, пятым и шестым вхо

Изобретение относится к области вычислительной техники и может быть использовано для управления обменом информации между устройством вводавывода и процессором.

Известен селекторный канал, со.держащий буфер данных, регистр алреса данных, регистр счетчика байт, регистр команд, блок управления передачей данных, блок формирования

аппаратной и микропрограь1мной приос.тановок, регистр управления каналом Л .

Недостатком такого канала язпяется низкое быстродействие, сложность структуры и большой объем аппаратуры

Наиболее близким к данному по технической сущности является селекторный канал, содержа1ций регистр данных, блок буферной памяти данных, блок управления интерфейсом, регистр команд и блок подсчета байт, первый вход которого соединен с первыми входами регистра команд и канала, второй вход канала соединен с вторыми входами регистра команд и блока подсчета байт, выход которого подключен к первому входу блока управления интерфейсом, выход регистра команд соединен с вторым входом блока управления интерфейсом и первым выходом канала, третий вход которого и второй выход соединены соответственно с первым входом и выходом регисра данных, четвертый вход и третий выход - с первым входом и первым выходом блока буферной памяти данных а пятый вход и четвертьй выход - соответственно с третьим входом и первым выходом блока управления интерфей сом, четвертый вход которого и второй выход соединены соответственно с вторым выходом и вторым входом блока буферной памяти данных 2j .

Недостатком этого селективного канала является низкое быстродействие и сложная структура.

Цель изобретения - повьшение быстродействия и упрощение структуры селекторного канала.

Поставленная цель достигается тем, что в селекторный канал, содержащий регистр данных, блок буферной памяти данных, блок управления интерфейсом, регистр команд и блок подсчета байт, первьй и второй входы которого соединены соответственно с первыми и вторьии входами регистра команд и канала, а выход подключен к первому входу блока управления интерфейсом, второй вход которого соединен с выходом регистра команд и первым выходом канала, первый вход и выход регистра данных, первый вход и первый выход блока буферной памяти данных, третий вход и первьй выход блока управления.интерфейсом являются соответственно третьим, четвертым

и пятым входами и вторым, третьим и четвертым выходами канала, четвертый вход и второй выход блока управления интерфейсом соединены соответственно с вторыми выходом и входом блока буферной памяти данных, введены блок контроля байт, мультиплексор регистр масок, блок подсчета байт в буферной памяти, блок выборки байт счетчик младшего адреса, дешифратор и блок завершения выборки байт, причем первьй выход блока завершениявыборки байт .соединен с первым выходом канала, а первый вход - с первым входом блока выборки байт и выходом блока подсчета байт, второй вход с вторым входом блока выборки байт и выходом регистра команд, третий вход-с первыми входами блока контроля байт, регистра масок и блока подсчета байт в буферной памяти, вторым входом регистра данных, третьим входом блока буферной памяти данных, пятым входом блока управленияинтер фейсом и первым выходом блока выборки байт, четвертый вход - с третьим входом блока выборки байт и вторым выходом блока буферной памяти данных пятьгй вход - с первым входом мультиплексора, третьим входом регистра данных, вторым входом регистра масок и выходом дешифратора, шестой и седьмой входы - соответственно с третьим выходом блока управления интерфейсом и с первым выходом регистра масок, восьмой вход - с шестым входо канала и четвертым входом регистра данных, а девятый вход - с третьим .входом регистра масок и С(здьмым входом канала, шестой вход блока управлния Интерфейсом соединен с четвертым входом блока выборки байт и выходом блока контроля байт, второй вход которого соединен с четвертым входом блока буферной памяти данных и выходом мультиплексора, второй вход которого соединен с выходом регистра дан ных, пятым и шестым входами подключенного соответственно к второму выходу регистра масок и первому выходу блока буферной памяти данных, выход и второй вход блока подсчета байт в буферной памяти соединены соответственно с седьмым входом и вторым выходом блока управления интерфейсом, второй выход блока выборки байт соединен с третьим входом блока подсчета байт, пятый вход с вторым выходом блока завершения выборки байт, третий и четвертый выходы - соответственно с первым и вторым входами счетчика младшего адреса, третий вход и выход которого соединены соответственно.с вторым входом канала и входом дешифратора, шестой вход блока выборки байт, четвертый вход счетчика младшего гщреса и десятый вход блока завершения выборки байт соединены с первым входом канала. Блок выборки байт содержит три элемента ИЛИ, два элемента ИЛИ-НЕ, четыре элемента И, два элемента И-НЕ причем входы первого и второго элементов ИЛИ образуют шестой вход блока, первый и второй входы первого элемента ИЛИ-НЕ являются соответстве но первым и пятым входами блока, а выход подключен к первым входам первого и второго элементов И, вторые входы которых являются третьим входом блока, третьи входы - соединены с третьим входом блока, а выходы соответственно с первым и вторым вхо дами третьего элемента ИЛИ, выходом подключенного к первому входу первого элемента И-НЕ, выход которого является вторым выходом блока, а второ вход - соединен с выходом второго элемента ИЛИ и первым входом третьег элемента И, второй вход и выход кото рого соединены соответственно с выхо дом первого элемента И и первым входом второго элемента ИЛИ-НЕ, выход и вход которого соединены соответствен но с третьим выходом блока и выходом четвертого элемента И, инверсный вхо которого соединен с первым входом вт рого элемента И-НЕ и вторым входом блока, вь1ход второго элемента И-НЕ является четвертым выходом блока, а второй вход соединен с вторым входом четвертого элемента И, выходы первых и вторых элементов И и ИЛИ образуют первый выход блока, а четве тый вход второго элемента И и второй вход четвертого элемента И образуют четвертый вход блока. Блок контроля байт содержит триггер ошибки, триггер модификации адре са, триггер задержки, элемент И и де шифратор четности, причем входы дешифратора четности образуют второй вход блока, а выход соединен с инфор мационным входом триггера ошибки и первым входом элемента И, второй „вход которого подключен к синхровходу триггера задержки и входу сброса триггера модификации адреса, информационным входом соединенного с выходом триггера задержки, а нулевым выходом - с синхровходом триггера ошибки, вход установки в единицу которого подключен к выходу элемента И, второй и третий входы которого, синхровход триггера модификации адреса и информационный вход триггера, задержки образуют первый вход блока, единичный выход триггера модификации адреса и нулевой выход триггера ошибки образуют выход блока. Блок завершения выборки байт содержит узел формирования, полного слова, включающий триггер полного слова, элемент ИЛИ и элемент И, узел формирования запроса состояния, состоящий из коммутатора сигналов состояния, и узел формирования запроса данных, состоящий из триггера запроса данных триггера ненулевой маски слова и коммутатора сигналов запроса данных, причем группа входов коммутатора сигналов запроса данных соединена с первого по шестой, восьмым, девятым и десятым входами блока и единичным выходом триггера ненулевой маски слова, группа входов коммутатора сигналов состояния подключена к первому, второму, четвертому и шестому входам блока и нулевому выходу триггера ненулевой маски слова, первые информационные входы триггера запроса данных и триггера ненулевой маски слова подключены соответственно к первому и второму выходам коммутатора сигналов запроса данных, синхровходы - к третьему входу блока, а вторые информационные входы - к третьему выходу коммутатора сигналов запроса , четвертым выходом соединенного с входом установки единицы триггера запроса данных, выход которого является вторым выходом блока, инверсный и прямой входы элемента И подключены соответственно к вто-г рому и восьмому входам блока, а выход - к единичному входу триггера полного слова, нулевой вход и выход которого соединены соответственно с девятым входом блока и первым входом элемента ИЛИ, второй вход которого является седьмым входом блекл, выходы элемента ИЛИ, коммутатора сигналов состояния и триггера заироса данных образуют иервьш выход блока.

Блок управления интерфейсом содержит семь триггеров, четыре элемента И, два элемента И-ИЕ, элемент сравнения, элемент И-ИЛИ и элемент ИЛИ, причем вход сброса и выход первого триггера соединены соответственно с выходом первого элемента И и первым входом второго элемента И, выходом подключенного к информационному входу второго триггера вход сброса которого соединен с первым входом первого элемента И и нулевым выходом третьего триггера, выход с информационным входом третьего триггера, единичным выходом подключенного к первому входу элемента ИЛИ выход которого является первым выходом блока, а второй вход соединен с единичным выходом четвертого триггера, информационный вход и вход сброса которого подключены соответственно к выходам третьего элемента И и первого элемента И-НЕ, а единичный и нулевой выходы - соответственно к прямому входу четвертого элемента И и первому входу второго элемента И-НЕ, выходы которых соединены соответственно с информационным входом и входом сброса пятого триггера, единичным и нулевым выходами соответственно подключенного к первым входам первого элемента И-НЕ и третьего элемента И, второй вход которого -соединен с вторым входом второго элемента И и выходом шестого триггера, информационным входом соединенного с выходом элемента И-КПИ первый вход котрого подключен к выходу элемента сра нения первый и второй входы элемента сравнения соединены соответственно с первым и седьмым входами блока, выход седьмого триггера является третьим выходом, блока, а выходы второго и пятого триггеров образуют второй выход блока, информационные входы первого и седьмого триггеров подключены к второму входу первого элемента И, третьему входу третьего элемента И, инверсному входу четвертого элемента И, входу сброса третьего триггера и третьему входу блока, синхровходы первого, четвертого, пятого и седьмого триггеров подключены к второму входу второго элемента И-ЛЕ, синхровходы второго, трртьего Л шестого триггеров подключены

к второму входу первого элемента И-НЕ, синхровходы первого и второго триггеров образуют пятый вход блока, второй и третий входы элемента И-ИЛИ вход сброса шестого триггера, четвертый вход третьего элемента И и третий вход второго элемента И образуют второй вход блока, четвертые входы элемента И-ИЛИ и второго элемента И и пятьй вход третьего элемента И образуют четвертьпЧ вход блока, пятый вход элемента Й-ИЛИ соединен с первым входом блока, а вход установки в единицу шестого триггера подключен к шестому входу блока.

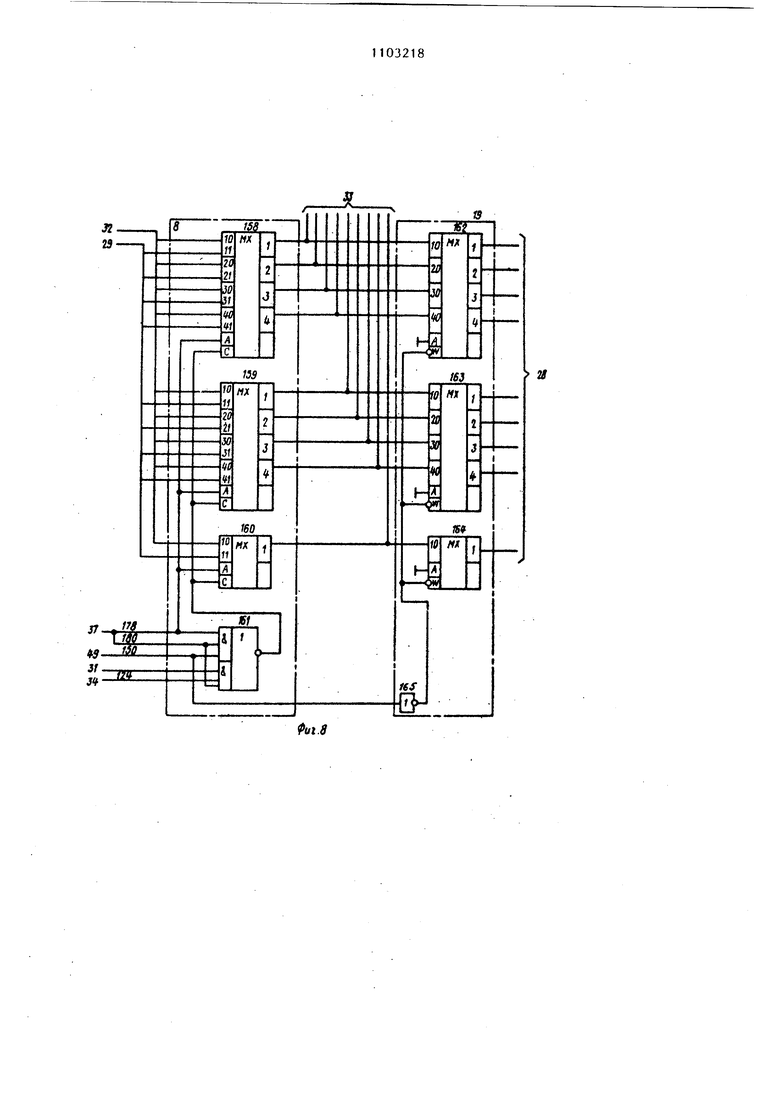

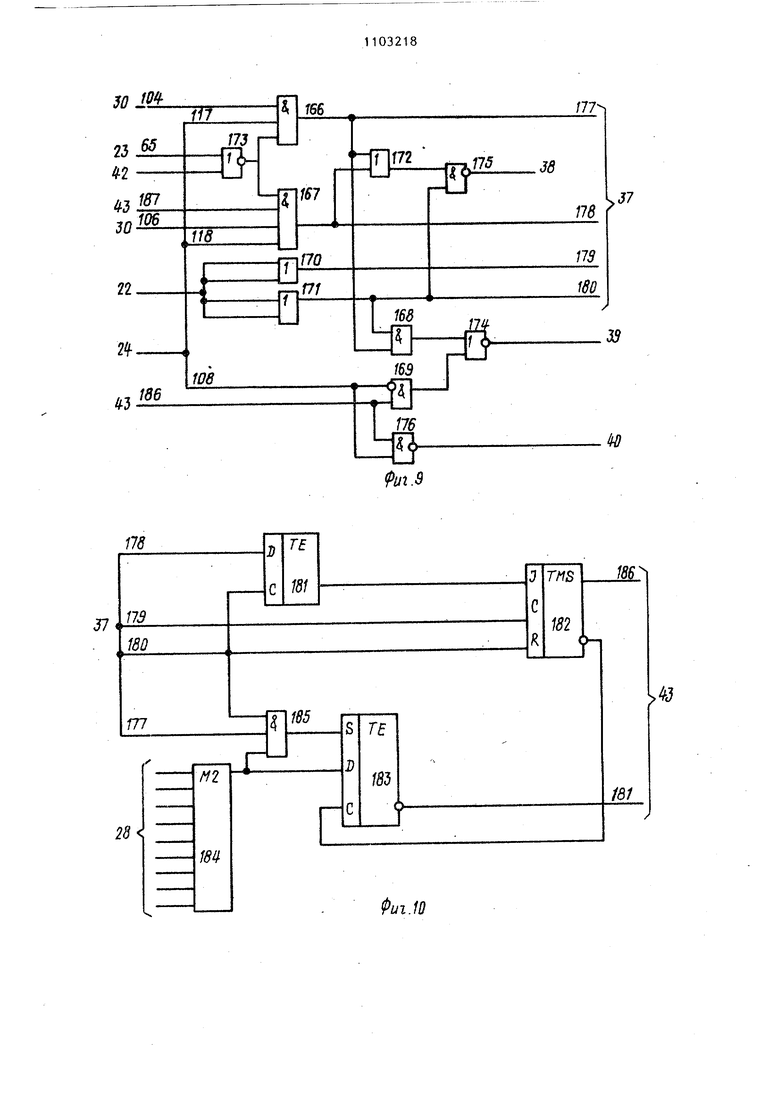

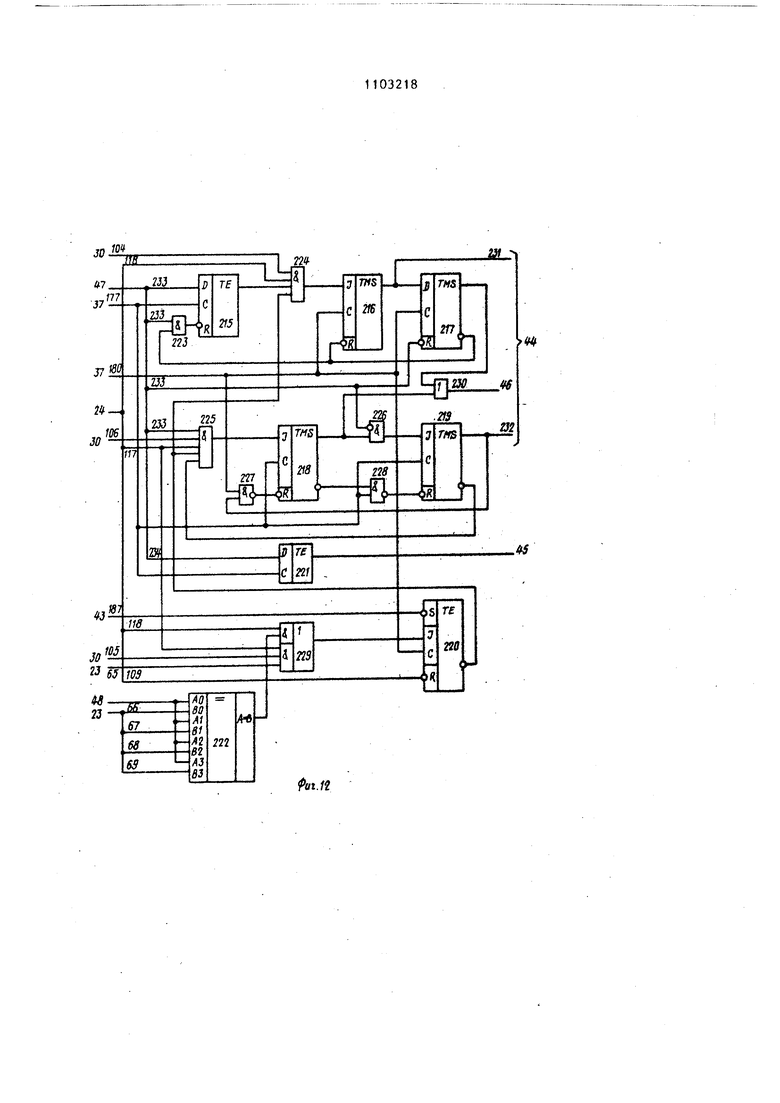

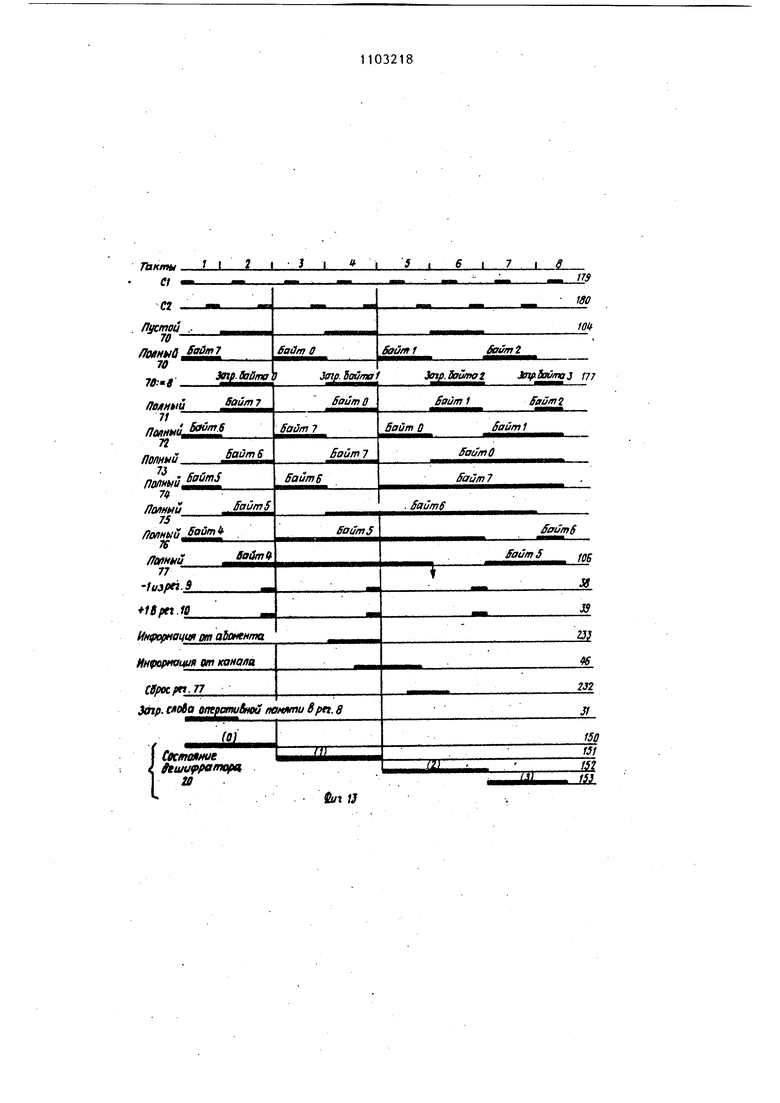

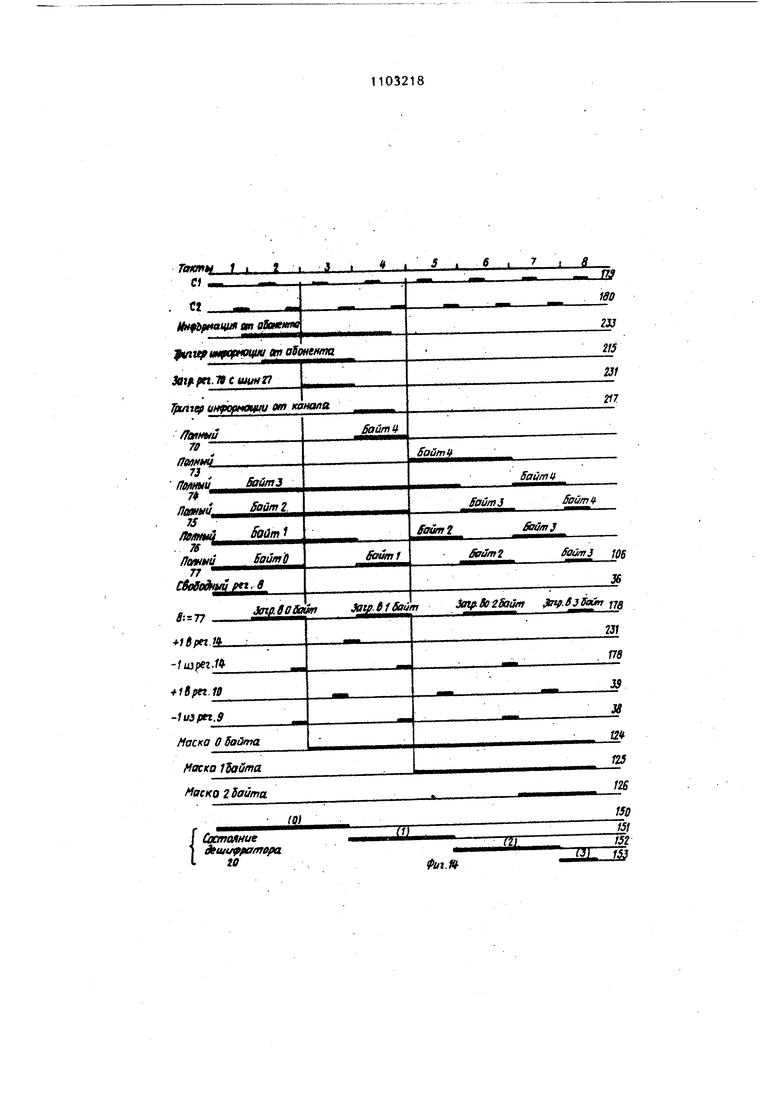

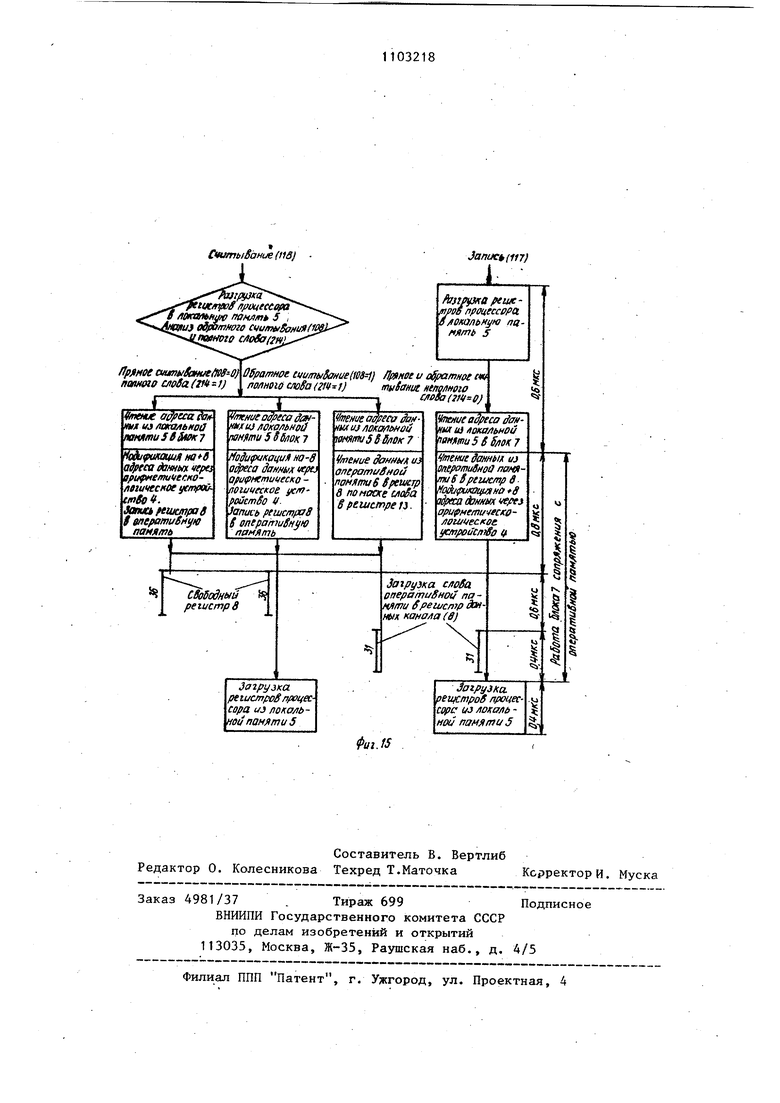

На фиг. 1 представлена блок-схема селекторного канала и процессора; на фиг. 2-12 - примеры функциональных схем блока подсчета байт, блока буферной памяти данных, регистракоманд блока подсчета байт в буферной памяти, регистра масок, счетчика младшего адреса, одного (нулевого) байта регистра данных и мультиплексора этого байта, блока выборки байт, блока контроля байт, блока завершения выборки байт, блока управления интерфейсом; на фиг. 13 - временная диаграмма работы канала для операций записи на устройство ввода-вывода; на фиг. 14 -.для операций считывания с устройства ввода-вывода; на фиг.15алгоритм выполнения микропрограммы передачи данных между каналом и оперативной памятью.

Селекторный канал 1 (фиг. 1) предназначен для подключения быстродействующих внешних устройств к процессору 2, который содержит блок 3 микропрограммного управления, арифметическо-логическое устройство 4, локальную память 5, оперативную память 6, блок 7 сопряжения с оперативной памятью. Селекторный канал 1 содержит (фиг. 1) регистр 8 данных, блок 9 подсчета байт, счетчик 10 младшего адреса, регистр 11 команд, блок 12 буферной памяти данных, регистр 13 масок, блок 14 подсчета байт в буферной памяти, блок 15 управления интерфейсом, блок 16 выборки байт, блок 17 завершения выборки байт, блок 18 контроля байт, мультиплексор 19, дешифратор 20, шины 21 и 22 второго и первого входов канала 1, шины 23 и 24 выходов блока 9 и регистра 11, шины 25 первого выхода канала 1, шины 26 счетчика, шины 27 четвертого

входа канала 1, шины 28 выхода мультиплексора 19, шины 29 третьего выхода канала 1 , шины 30 второго выхода блока 12, шины 31-33 шестого и третьего входов и второго выхода канала 1, шины 34 и 35 второго и первого выходов регистра 13, шины 36 седьмого входа канала 1, шины 37-40 первого четвертого выходов блока 16, шины 41 и 42 выходов блока 17, шины 43 выхода блока 18, шины 44 и 45 второго и третьего выходов блока 15, шины 46 и 47 четвертого выхода и пятого входа канала 1, шины 48 выхода блока 14, шины 49 выхода дешифратора 20.

Операция передачи данных в канале 1 начинается по специальной команде процессора 2, которая задает адрес селекторного канала 1 и устройства ввода-вывода, и при помощи специальных управляющих слов указывает код команды, начальный адрес оперативной памяти, количество передава-емых байт данных и другие управляющие признаки, которые располагаются в регистрах канала 1 и в локальной памяти 5, образуя в сопокупности упра)1лик)|цпс слова канала. В локальной памяти 5 размещается адрес следующего командного слона, адрес данных, ключи защиты, признаки и отметки, используемые н микропрограммах канала 1. Счетчик байт размещается в блоке 9, младший адрес в счетчике 10, команда - в регистре 11. Регистры загружаются по шинам 21 из локальной памяти 5 процессора 2 по управляющим сигналам на шинах 22 из блока 3.

Блок 12 буферной памяти данных выполнен в виде стековой памяти. Загружается по шинам 27 из устройства ввода-вывода, по шинам 28 с выхода мультиплексора 19 и разгружается по шинам 29 в регистр 8 или в устройство ввода-вывода.

Регистр 8 данных канала хранит 8-байтное слово, которым обменивается канал 1 с оперативной памятью 6 в процессе передачи данных.

Регистр 13 масок хранит 8-разрядную маску слова для операций считывапия с устройства ввода-вывода. Управ ляет приемом байт данных в регистр 8 с шин 32.

Блок 16 выборки байт управляет передачей бар1т из регистра 8 в блок

12 буферной памяти данных, через мультиплексор 19 для операций записи на устройство ввода-вывода и выборкой байт из блока 12 буферной памяти данных в регистр 8 для операций считывания из устройства ввода - вывода.

Блок 17 завершения выборки байт определяет момент выключения из работы блока 16, формирует признак (полное - неполное слово) завершения выборки байт из блока 12 буферной памяти данных в регистр 8, определяет момент выхода на микропрограммную приостановку для обслуживания данных

и состояния.

Блок 18 контроля осуществляет контроль выбираемых байт ,из регистра 8 или блока 12.

Блок 15 управления интерфейсом

осуществляет загрузку блока 12 в операциях считывания с устройства ввода - вывода и разгрузку блока 12 в операциях записи на устройство ввода вывода. Под управлением блока15 осуществляется начальная выборка устройства ввода - вывода, завершение операции ввода - вывода на интерфейсе и другие функции.

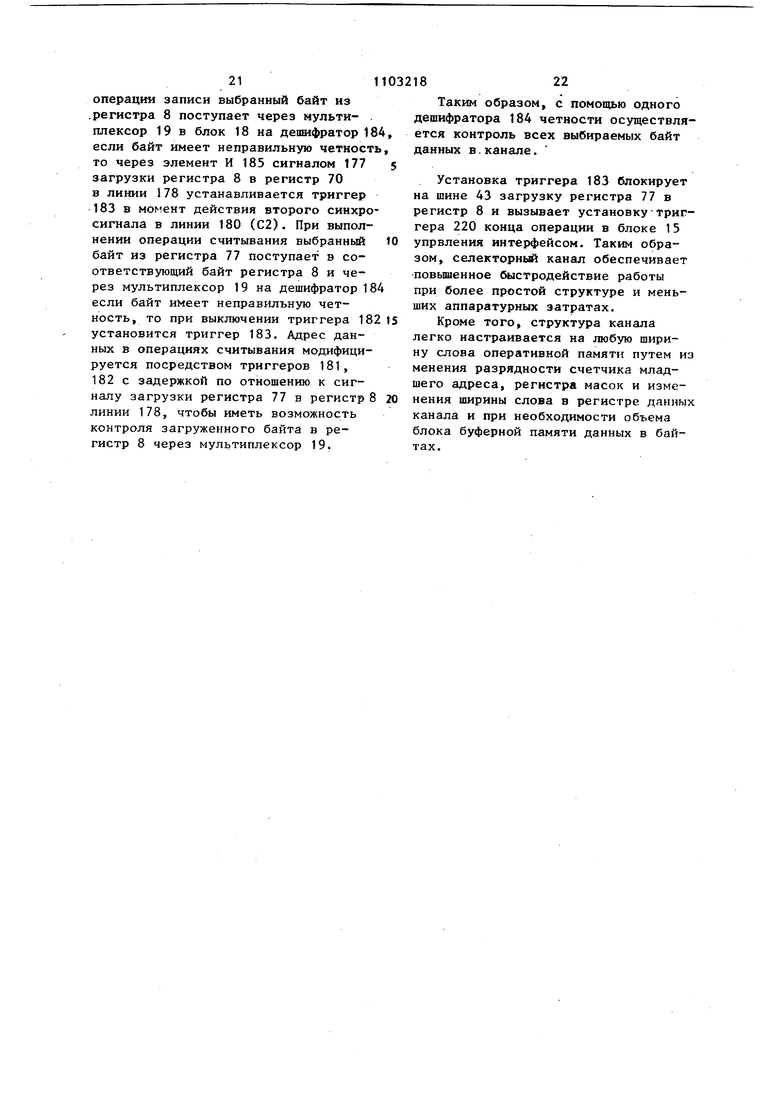

Блок 9 подсчета байт (фиг. 2) содержит счетчики 50-53 (синхронные реверсивные двоичные 4-разрядные) элементы ИЛИ 54-60, элементы И 61-62. Загружается по шинам 21 вторьгм третьим байтом слова локальной памяти 5,

по отрицательному управляющему сигналу в линии 63 на шинах 22. Вычитание из счетчика 50-53 производится отрицательным сигналом по шине 38. Блок 9 вырабатывает на шинах 23 сигналы равенства счетчика 1,0, 15

(сигналы в линиях 64-69 соответственно) .

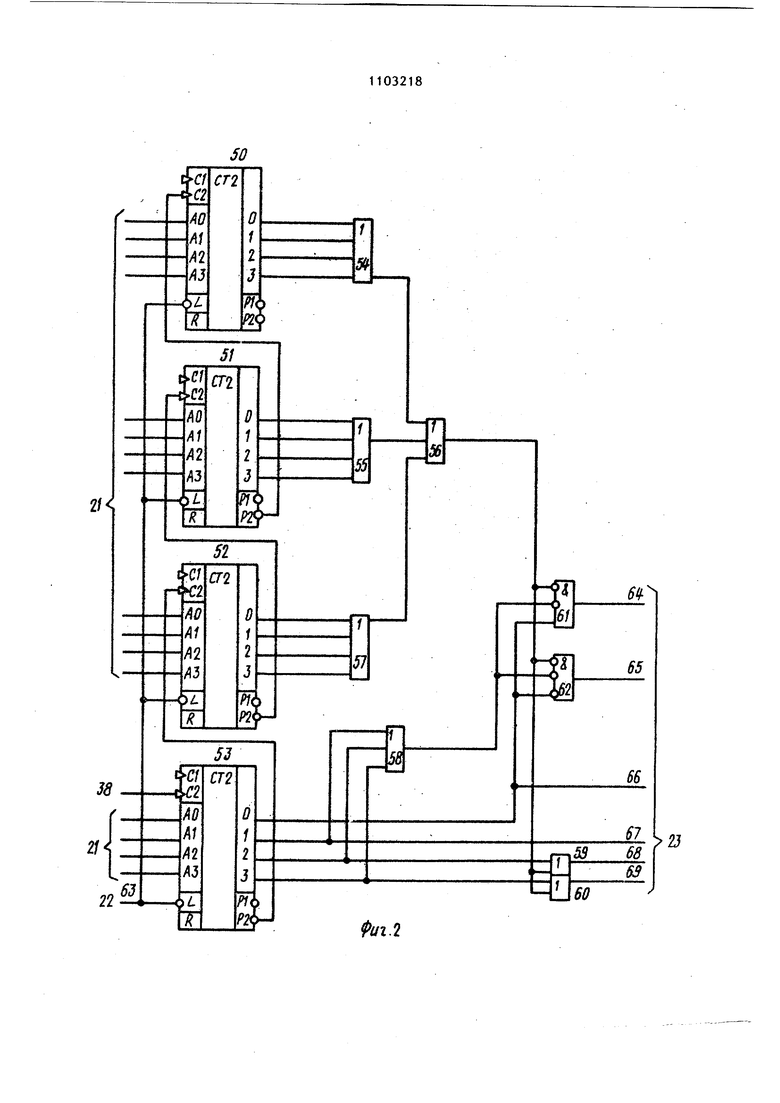

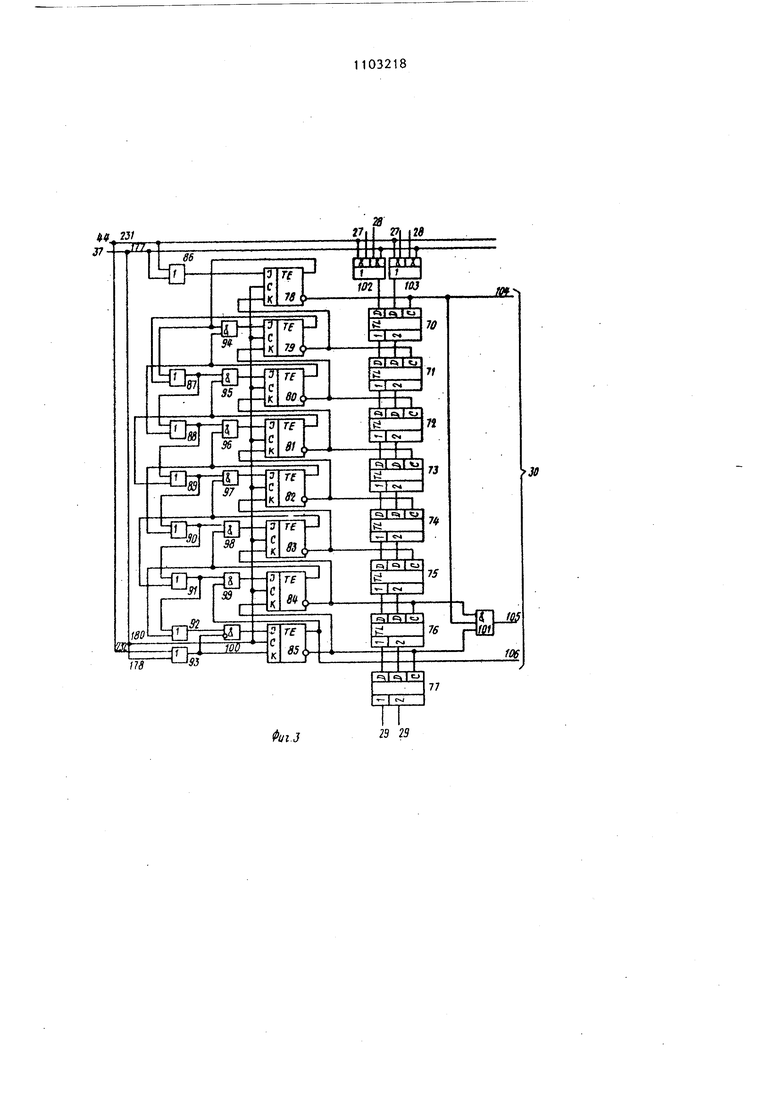

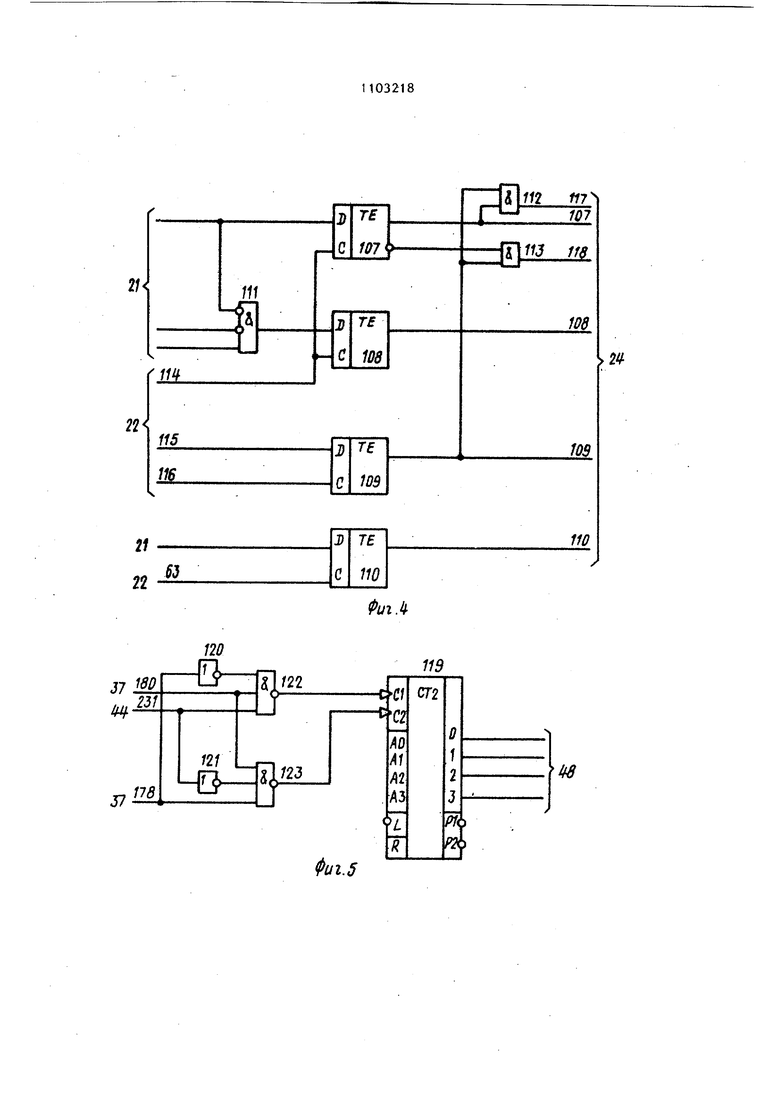

Блок 12 буферной памяти данных (фиг. 3) содержит триггеры (регистРы) 70-77, триггеры (флажки) 78-85, элементы ИЛИ 86-93, элементы И 94101, элементы И-ИЛИ 102, 103. Управляется вторым синхросигналом по ши-нам 37. Нулевые выходы триггеров 7885 соединены с С-входом соответствующих регистров 70-77 (на фиг. 3 представлены только 2 разряда каждого буферного регистра). Если блок 12 отключен, то все триггеры 78-85

сброшены и в регистрах 70-77 присут.«ствует нулевая информация, так как элементы 102-103 выключены, а сигиалы на С-входах регистров 70-77 пк.ючены. При загрузке блока 12, наприме из регистра 8 по шинам 28, когда включается сигнал загрузки на шинах 37 и загружаются 1, то включаются элементы 102-103, и байт данных поступает в регистр 70 и последующие регистры. В конец такта загрузки (см. фиг. 13, 14) по заднему фронту синхросигнала на шинах 37 устанавливается триггер 78 полного регистра 70 через элемент ИЛИ 86, включается синхросигнал на С-входе регистра 70 и байт данных записывается в регистр 70. В последующем такте канала через элементы ИЛИ 87-92, элемент И 100 устанавливается триггер 85 полного регистра 77 и сбрасывается триггер 78, так как триггер 79 выключен и байт данных из регистра 70 переписывается в регистр 77. В последующих тактах при загрузке через регистр 70 аналогичным образом байт данных запишется в регистр 76, установится триггер 84, так как включен триггер 85 и т.д. При разгрузке блока 12, например, на устройство ввода - вывода по шинам 29 по сигналу сброса регистра 77 на шинах 44 триггер 85 сбрасывается и байт данных из регист ра 76 передается в регистр 77, так как включается сигнал на С-входе регистра 77, а в следующем (третьем, включая такт сброса) такте устанавли вается триггер 85 и сбрасывается триггер 84. Через элемент И 101 формируется сигнал 105 пустого блока 12 поступающий по шинам 30 в блоке канала 1. Блок 12 буферной памяти вырабатывает сигнал 104 пустого регистра 70, сигнал 105 пустого блока 12 и сигнал 106 полного регистра 77. Регистр 11 команд (фиг. 4) содержит триггер 107 записи, триггер 108 обратного считывания, триггер 109 операции данных, триггер ПО блокиров ки записи в оперативную память, элементы И 111-113. Загружается по шина 21 канала нулевым байтом слова локал ной памяти 5 по управляющим сигналам в линиях 63, 114 на шинах 22 канала. Причем если включен седьмой разряд нулевого байта слова локальной памяти 5, то устанавливается триггер 107 а если седьмой, шестой разряды нулевого байта слова локальной памяти 5 выключены и включен четвертый разряд то через элемент Р1 1 11 устанавлива1812ется триггер 108. Триггер 109 устанавливается микропрограммой канала после успешной начальной выборки устройства ввода - вывода сигналом в линии 113 на шинах 22 канала, когда устройство ввода - вывода в ответ на команду от канала присыпает нулевой байт состояния и сбрасывается сигналом в линии 116 на шинах 22, когда завершена передача данных и устройство ввода - вывода, присьшает конечный байт состояния. Триггер 109 разрешает обмен данными между каналом 1 и устройством ввода - вывода посредством включения команды записи или считывания в линиях 117 или 118 через элементы И 112, 113. Триггер 110 загружается третьим разрядом нулевого байта слова локальной памяти 5 на шинах 21 по управляющему сигналу в линии 63 на шинах 22. Триггер 110 запрещает запись в оперативную память байт данных, считываемых из устройства ввода - вывода. Блок 14 подсчета байт в буферной памяти (фиг. 5) содержит счетчик 119 (синхронный реверсивный двоичный 4-разрядный) , элементы ИЛИ-НЕ 120, 121 элементы И-НЕ 122, 123. Используется только в командах считывания с устройства ввода - вывода. Добавлением 1 в счетчик 119 производится в момент действия второго синхросигнала на шинах 37 канала по управляющему сигналу на шинах 44 во время загрузки буферного регистра 70 с шин 27, а вычитание 1 - по управляющему сигналу на шинах 37 в конце передачи из регистра 77 по шинам 29 в регистр 8 данных канала. Если указанные и управляющие сигналы присутствуют одновременно, то счетчик 119 не считает. Регистр 13 масок (фиг. 6) содержит триггеры 124-131 масок соответственно нулевого - седьмого байт регистра 8, элементы И 132-148. Триггеры 124-131 масок устанавливаются по сигналу загрузки регистра 77 в регистр 8 на шинах 37 в момент действия второго синхросигнала на шинах 37, в зависимости от содержимого счетчика 10 младшего адреса через дешифратор 20 (выходы 150-157). Регистр 13 масок сбрасывается сигналом на шинах 36 из блока 7 после передачи данных из регистра 8 в оперативную память 6. В регистре 13 формируется через элемент И 1А8 на шину 35 сигнал полно.го слова в регистре 8. Счетчик 10 младшего адреса и дешифратор 20 (фиг. 7) выполнен как синхронньй двоичный реверсивный 4разрядный счетчик. Регистр 11 загружается по входу 21 младшими разрядами третьего байта слова локальной памяти 5 по управляющему сигналу в линии 149 нашинах22. Добавление 1 в счетчик 10 производится по отрицательному сигналу на шинах 39, а вычитание 1 - по отрицательному сигналу на шинах 40. Выходы 150-157 дешифратора 20 подаются на входы регистра 13. Регистр 8 данных (фиг. 8) может быть выполнен на селектор-мультиплек сорах 158-160 с запоминанием и элеме те И-ИЛИ-НЕ 161. Загружается по переднему фронту второго синхросигнала на шинах 37 из регистра 77 с шин 29 по управляющему сигналу на шинах 37, если включен сигнал в линии 150 на выходе дешифратора 20, из оперативно памяти 6 (нулевого байта слова) по шинам 32 по управляющему сигналу на шине 31, если триггер 124 нулевого байта регистра 8 сброшен. На фиг. 8 представлен только нулевой байт вось мибактного регистра 8. Остальные бай ты регистра 8 идентичны нулевому. Мультиплексор 19 (для нулевого байта) (фиг. 8) содержит, например, 4-разрядные селектор-мультиплексоры 162-164 с тремя устойчивыми состояни ями по выходу элемента НЕ 165. Мультиплексоры 162-164 переключаются из третьего (высокоимпедансного) состо яния сигналом в линии 150 на шинах 49 с выхода дешифратора 20 через элемент НЕ 165. Одноименные выходы мультиплексоров 19 всех байтов (например, вторые разряды мультиплексоров нулевого седьмого байта) объединены между собой. Таким образом при модификации счетчика 10 посредством дешифратора 20 выбирается через муль типлексоры 162-164 один из байтов регистра 8. Блок 16 выборки байт (фиг. 9) содержит элементы И 166-169, ИЛИ 170172, ИЛИ-НЕ 173, 174, И-НЕ 175/176, линии 177-1.80 шин 37 первого вьсхода блока 16. Блок 18 контроля байт (фиг. 10) содержит триггер 181 задержки сигнала в линии 178 загрузки регистра 77 в регистр 8, триггер 182 модификации регистра 11, триггер 183 ошибки данных в регистре 8 и дешифратор 184четности, элемент И 185, линии 186-187, шины 43 выхода блока. Блок 17 завершения выборки байт (фиг. 11) состоит из узла 188 формирования запроса данных, узла 189 формирования запроса состояния и узла 190 формирования признака полного слова. Узел 188 содержит триггер 191 запроса данных, триггер 192 ненулевой маски слова и коммутатор сигналов запроса данных, включающий элементы И-НЕ 193, 194, И 195-203, ИЛИ 204-205. Узел 189 представляет собой коммутатор сигналов состояния, выполненный на элементах И 206-208 и элементов ИЛИ 209. Узел 190 содержит триггер 210 полного слова: элемент И 211, ИЛИ 212, линии 213-214 входят в состав линий шины 41. Блок 15 управления интерфейсом (фиг. 12) содержит триггеры 215-221, элемент 222 сравнения двух чисел, элементы И 223-226, И-НЕ 227-228, И-ИЛИ 229, ИЛИ 230, линии 231, 232 . шины 44. Сигнал в линии 233 на шинах 47 устанавливает триггер 215, сигнал в линии 234 на шинах 47 устанавливает триггер 221. На фиг. 13 и 14 приняты следующие обозначения: С 1, С 2 - тактовые синхросигналы соответственно первой, второй серии канала. Справа на фиг. 13, 14 указаны позиции линий, шин и триггеров, взаимодействующих с сигналами, приведенными в левой стороне фиг. 13, 14. Селекторый канал 1 работает следующим образом, г Машинньй такт процессора, в который входит предлагаемый канал, состоит из .первого - четвертого тактовых синхросигналов (СИ1, СИ2, СИЗ, СИ4) длительностью каждый, например, 50нс. Длительность такта равна 400 не. Для увеличения быстродействия работы канала 1 на этапе передачи данных такт канала 1 выбран длительностью 200 НС, т.е. в 2 раза меньше длительности машинного такта процессора. С этой целью в блоке 16 по шинам 22 через элемент ИЛИ 170 из первого, третьего синхросигнала (СИ1 , СИЗ) формируется первый синхросигнал в линию 179 (С1), а через элемент 171 из второго, четвертого синхросигнала (СИ2, СИ4) - второй синхросигнал в линию 180 (С2), которые по шинам 37 поступают в блоки канала 1, Операция записи. После загрузки управляющей информации в канал 1 и успешной начальной выборки устройства ввода - вывода микропрограммой канала по сигналам в линии 115 на шинах 22 устанавливается триггер 10 и одновременно в блоке 17 через зле мент И-НЕ 194 устанавливается триггер 191. Запрос данных по шине 41 поступает в процессор 2, где вызывается микропрограмма передачи данных канала, которая выполняется за 3 микрокоманды процессора 2. Разгрузка регистров процессора 2 используемых в микропрограмме переда чи данных, в локальную память 5 (см фиг. 15). Чтение адреса данных из локальной памяти 5 в блок 7 и на вход арифмети ческо-логического устройства 4. Моди фикация адреса данных на + 8 через устройство 4 и запись его в локальну память 5. В зтом же такте запускается блок 7 для чтения данных из оперативной памяти 6 в регистр 8. Третья микрокоманда не выполняется до завершения чтения данных из оперативной памяти 6. Ко1да данные из оперативной памяти 6 прочитаны, то блок 7 выдает в канал сигнал загрузки слова оперативной памяти 6 в регистр 8, который по шине 31 поступает в канал 1. Последни принимает полное слово с шин 32 в регистр 8, так как регистр 13 в операциях записи выключен. Через злемент И 200 блока 17 сбрасывается триггер 191, тем самым включая в работу блок 16 по шине 42. Допускается на выполнение третья микрокоманда. Загрузка регистров процессора 2 и локальной памяти 5. В блоке 16, если регистр 70 пустой, через злемент И 166 вьщается сигнал в линию 177 на шину 37 загруз ки регистра 70 из регистра 8. Соответствующий байт регистра 8 через мультиплексор 19 передается в регистр 70. В конце передачи счетчика 53 в блоке 9 уменьшается по шине 38 на 1, а счетчик 10 увеличивается по шине 39 на +1. Через один такт канала 1, если регистр 70 освободится, предыдущие действия повторяются. Когда состояние счетчика 10 достигает границы слова (111), то в момент передачи последнего байта из регистра 8 (байта 7) через элемент И 198 блока 17 установится триггер 191 и вызывается микропрограмма передачи данных, после выполнения которой включается блок 16. Начало временной диаграммы на фиг. 13 соответствует моменту, когда в блоке 12 находятся байты 4-7 регистра 8, в регистрах 76, 74, 72, 70 и очередное слово данных читается в регистр 8 из оперативной памяти 6. Во втором такте канала производится загрузка прочитанного слова (байта 0) в блок 12. Если в момент передачи последнего байта регистра 8 (байта) содержимое счетчика 53 равно 1, то по шине 23 сигналом в линии 64 блокируется установка триггера 191 через элемент И 198 в блоке 17. Если счетчик 53 после очередной выборки байта из регистра 8 достигнет нуля, то сигналом в линии 65 по шине 23 через элемент ИЛИ-НЕ 173 блок 16 выключается из работы. Таким образом, байты данных считываются из оперативной памяти 6 в регистр 8, передаются в блок 12, где продвигаются к регистру 77, откуда выдаются на устройство ввода - вывода. Когда устройство ввода - вывода требует очередного байта данных, то оно устанавливает в линию 233 шины 47 сигнал информации от абонента поступающий в блок 15 (фиг. 12). Если регистр 77 загружен, то по сигналу в линии 106 на шине 30 через элемент И 225 по заднему фронту синхросигнала из линии 177 (М1) на шинах 37 установится триггер 218 информации от канала (фиг. 13) и через элемент ИЛИ 230 по шине 46 выдается сигнал информации от канала. Устройство ввода вывода принимает байт с шин 29 и снимает сигнал в линии 233, указывая каналу 1, что байт данных принят. В канале 1 через злемент И 226 по заднему фронту синхросигнала в линии 177 (С1) на шинах 37 установится триггер 219, по которому через щину 44 сбрасывается триггер 85 и очередной байт данных сдвигается в регистр 77. По установленному триггеру 219 через элемент И-НЕ 227 в момент действия второго синхросигнала в линии 180 (С2) по шине 37 сбросится триггер 218 информации от канала, что в свою оче редь приводит к сбросу триггера 219 Б момент действия первого синхросигнала в линии 177 (С1) через элемент И-НЕ 228, Если устройство запросит очередной байт данных, то все предыдущие действия повторяются. Операция передачи данных на интерфейс ввода - вывода обычно заканчивается, когда счетчик 53 достигает нуля и все байты данных из блока 12 переданы в устройство ввода - выво.да. Если это происходит, то по шинам 23, 30 через элемент И-ИЛИ 229 по заднему фронту второго синхросигнала в линии 180(С2) на шинах 37 устанавливается триггер 220 конца операции, который блокирует установку триггера 218 информации от канала через элемент И 225. В ответ на сигнал информации от абонента выдается сигнал управления от канала 1 (на фиг. 12 не показан), что является признаком останова для устройства ввода - вывода. Устройство ввода - вывода на этом заканчивает обмен данными и при сылает по линии 234 шин 47 сигнал управления от абонента, по которому в канале 1 устанавливается триггер 221, сигнал с выхода которого по шине 45 поступает в блок 17, где через элемент И 208 в линию 213 выбрасывается запрос обслуживания состояния, который вызывает в процессоре 2 выполнение микропрограммы обслуживания состояния устройства ввода вывода. Операция считывания. Операция счи тывания с устройства ввода - вывода начинается после загрузки управляющей информации в канал 1 и успешной начальной выборки устройства ввода вывода, когда микропрограммой канала по сигналу в линии 115 на шинах 22 устанавливается триггер 109 операции данных в регистре t1 команд. Устройство ввода - вывода помещает на шины 27 байт данных и устанавливает в линии 233 сигнал информации от або нента, что приводит к установке в блоке 15 триггера 215 информации от абонента по переднему фронту первого синхросигнала в линии 177 (С1) на шинах 37 (фиг. 12, 14). Если регистр 70 пуст, то через элемент И 224 установится по заднему фронту синхросигнала (С2) в линии i80 триггер 216, сигнал с выхода которого по шине 44 (линия 231) поступает в блок 12, Байт данных принимается в 70. Следующим синхросигналом в линии 180 установится триггер 217 информации от канала и через элемент ИЛИ 230 вьщается в интерфейс сигнал информации от канала, указывающий устройству ввода - вывода, что байт данных с шин 27 принят. Сбрасываются триггеры 215, 216. Устройство ввода - вывода снимает сигнал с линии 233, что приводит к сбросу триггера 217 информации от канала. Все последующие байты с шин 27 принимаются аналогичным образом. Отметим, что при каждом приеме байта данных с шин 27 производится добавление +1 в блок 14 сигналом в линии 231 на шине 44 через элемент И-НЕ 122, если выключен сигнал в линии 178. Как только первый байт данных достигает регистра 77, то включается в работу блок 16. Сигналом в линии 106 через элемент И 167 BbwaefcH сигнал в линии 178 для загрузки регистра 8 из регистра 77. Байт данных принимается в соответствующий байт регистра 8 (согласно состоянию счетчика 10 на выходе дешифратора 20), устанавливается в регистре 13 триггер маски соответствующего байта регистра 8. В конце такта загрузки по шине 38 производится вычитание У из блока 9, модификация на 1 счетчика 10 (на + для операций считывания через элемент ИЛИ-НЕ 174, по шине 39; на -1 для оп.ераций обратного считывания через элемент И-НЕ 176, по шине 40), производится вычитание 1 из блока 14 через элемент И-НЕ 123 по сигналу в линии 178 и сброс регистра 77 по сигналу в линии 178. При загрузке хотя бы одного байта в регистр 8 всегда устанавливается триггер 192 через элемент И 203 в блоке 17. При последующих загрузках байтов данных с шин 27 описанные действия повторяются. Блок 17 выключает блок 16 и формирует запрос данных для выполнения микропрограммы передачи данных в следующих случаях: когда в процессе выборки байт достигается граница слова в регистре 8, в этом случае.для команды считывания устанавливается триггер 191 через элемент И 196, а для команды обратного считывания - через элемент И 195; когда выбирается последний байт из блока 12, то по шине 23 через элемент И 197 устанавливается триггер 191; когда с устрой ства ввода считывается блок данных длиной меньшей, чем указано в счетчике 53, в этом случае устройство ввода вместо запроса на линии 233 присылает сигнал по линии 23А, который устанавливает триггер 221, сигна с единичного выхода которого По шине 45 поступает в блок 17. Если усло вия, описанные в первом случае не соблюдаются, то после выборки всех байтов данных из блока 12 s регистр 8 сигналом в линии 155 (пустой буфер

через элемент И 199 устанавливается триггер 191 запроса данных. Отметим, что сигнал запроса состояния в линии 213 блокируется по сигналу на шинах 45 на элементах И 206, 207 низ-20 КИМ уровнем сигнала с нулевого выхо да триггера 192. Запрос данных по шине 41 поступа ет в процессор 2, где вызывается микропрограмма передачи данных кана ла, которая выполняется за три микр команды (фиг. 15). Разгрузка регистров процессора 2 в локальную память 5 и ветвление по триггеру 108 и признаку в линии 214 полн о го ел ов а. Прямое или обратное считывание полного слова. Чтение адреса данных из локальной памяти 4 в блок 7 на вход арифметико-логического устройства 4. Модификация адреса данных соответственно на +8 или -8 через устройство 4 и запись его в локальную память 5. В этом же такте запускается блок для записи данных из регистра 8 по шинам 33 в оперативную память 6. Третья микрокоманда не выполняет ся до завершения передачи и записи переданных данных из регистра 8 в оперативную память 6. Когда данные из регистра 8 переданы, то блок 7 выдает в канал 1 сигнал свободного регистра 8, который по шине 36 пост пает в блок 17 и регистр 13. Регистр 13 сбрасьгоается и через элемент И 201 сбрасываются триггеры 191, 192 вторым синхросигналом по линии 180 (С2), тем самым включая в работу блок 16. Запускается после записи в оперативную память 6 данных третья микрокоманда.

третьей микрокоманды , как описано. Загрузка регистров процессора 2 из локальной памяти 5. Операция передачи данных на интерфейсе ввода 21820Прямое или обратное считывание неполного слова. Эта микрокоманда аналогична второй микрокоманде в операциях записи за исключением того, что адрес данных не модифицируется, данные с шин 32 принимаются в регистр 8 по маске слова в регистре 13, сигналом загрузки слова one- . ративной памяти 6 в регистр 8 на шинах 31 через элемент И 211 устанавливается триггер 210, триггеры 191, 192 не сбрасываются. Это дает возможность повторно войти в микропрограмму передачи данных, но уже для запи- си полного слова, после выполнения вывода обычно заканчивается, когда содержимое счетчика 119 в блоке 14 становится равным содержимому счетчика 50-53 в блоке 9. В этом случае через элемент 222 сравнения (фиг. 12) устанавливается триггер 220 конца операции, который через элемент И 224 блокирует установку триггера 216. Дальнейшие действия на интерфейсе аналогичны действиям в операциях записи. Сигнал запроса состояния в линии 213 вырабатывается по сигналу управления об абоненте на шине 45 в блоке 17 через элемент И 207, если имеется сигнал равенства нулю счетчика байт в линии 65 и выключен триггер 192 нулевой маски; через элемент И 206, если имеется сигнал пустого блока буферной памяти данных в линии 105 и выключен триггер 192 ненулевой маски. При считывании байт в данных с устройства ввода - вывода -с блокировкой записи в оперативную память 6 установлен триггер 110 в регистре 11. Это вызывает блокировку установки триггера 191 через элемент И-НЕ 193. Микропрограмма передачи данных не выполняется, а все описанные действия в канале выполняются. Начало временной диаграммы на фиг. 14 соответствует моменту, когда в микропрограмме передачи данных освобождается регистр 8 (в такте 1), в блоке 12 накоплены четыре байта (байты 0-3) , которые расположены в регистрах 11-1 f. Контроль выбираемых байт. Осуществляется в блоке 18. При выполнении операц№1 записи выбранный байт из .регистра 8 поступает через иульти- . плексор 19 в блок 18 на деошфратор 18 если байт имеет неправильную четност то через элемент И 185 сигналом 177 загрузки регистра 8 в регистр 70 в линии I78 устанавливается триггер 183 в момент действия второго синхро сигнала в линии 180 (С2). При выполнении операции считывания выбранный байт из регистра 77 поступает в соответствующий байт регистра 8 и через мультиплексор 19 на дешифратор 18 если байт имеет неправильную четность, то при выключении триггера 18 установится триггер 183. Адрес данных в операциях считывания модифицируется посредством триггеров 181, 182 с задержкой по отношению к сигналу загрузки регистра 77 в регистр линии 178, чтобы иметь возможность контроля загруженного байта в регистр 8 через мультиплексор 19. 1822 Таким образом, с помощью одного дешифратора 184 четности осуществляется контроль всех выбираемых байт данных в.канале. Установка триггера 183 блокирует на шине 43 загрузку регистра 77 в регистр 8 и вызывает установку-триггера 220 конца операции в блоке 15 упрвления интерфейсом. Таким образом, селекторн канал обеспечивает повьшенное быстродействие работы при более простой структуре и меньших аппаратурных затратах. Кроме того, структура канала легко настраивается на любую ширину слова оперативной памяти путем из менения разрядности счетчика младшего адреса, регистра масок и изменения ширины слова в регистре данных канала и при необходимости объема блока буферной памяти данных в байтах.

21 22

37 М.

Фиг.5

т

W

20

Фиг.1

кМ

27

Фи1.11

ТЬкты 1 I

аска ZSauma

(SL

I CjomUffue I dtuiu famopa. I to

{26

ISO

«/

.

fS2

iUL

(31 Ш

Фиг.

CwmbiSoHue (ilBj

tti/e/ryvf n/fomceiya flOKOfiMjM fiOMmt 5 I аз oHfiamwio cvuirwSoHuHfn wmno c/io&rffH

e cuunnSaHutf№SOMSpamHoe сыитыдание КЩ Л/янве и (фатное tuvо слаба ( I полною aioSa () тибанм имдлного

5%

свободный регистре

CflDK}()

Загрузка сдоба оперативной па fVimu fpewcmp Заннык канала (S)

Загрузка, oeufcmpoo прочееи с UJ лохалб ной памяти 5

Фи1.15

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ТЕЛЕФОННОЕ РЕЛЕ | 1923 |

|

SU1020A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Селекторный канал | 1974 |

|

SU525081A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-15—Публикация

1983-03-22—Подача