, г - .- , ггя к ар 0 1:г ке и

В1- 1 и П Г, , - с h lOHw i л -1 1 злогс х ens на

/ ч ) . ч кЗХ

И , 4 1 pi TifiЭС «11 ТЧОН -Й ДЬ п

«П- Ч ГГ..- i / . J г мПГ/Н

Ч- i i о( ло г4 npoj:1- , г,.- , , г. j- i( с cva f5/. г I „ г1

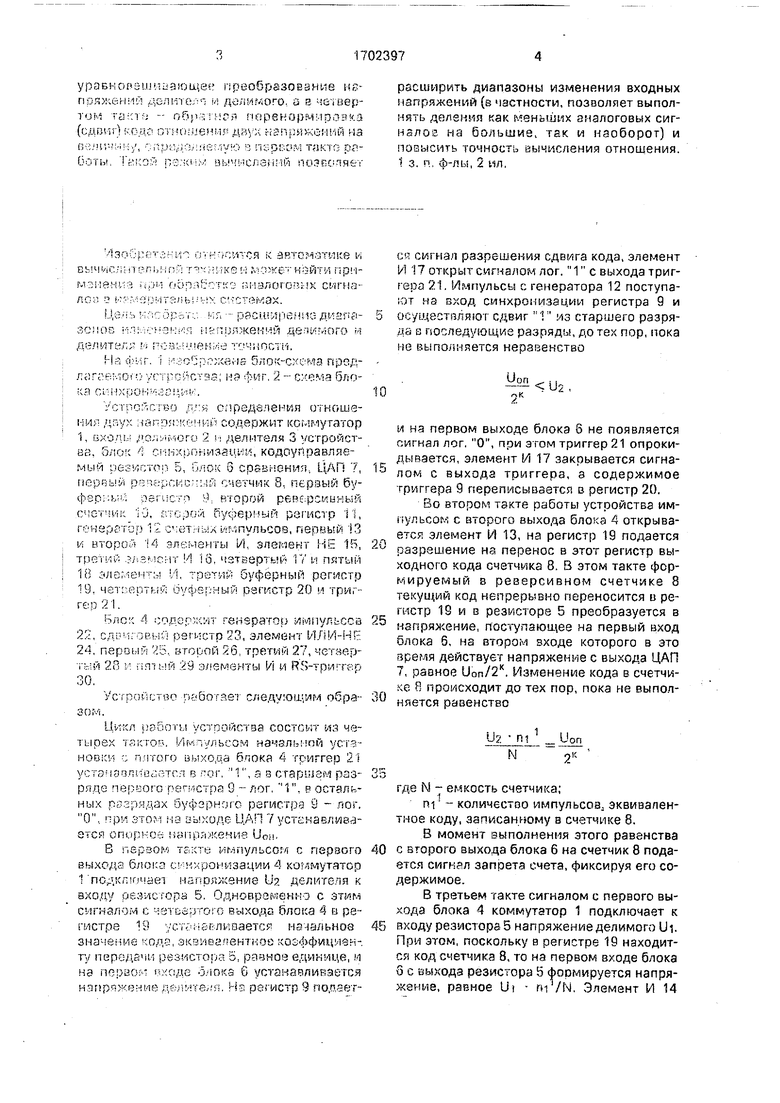

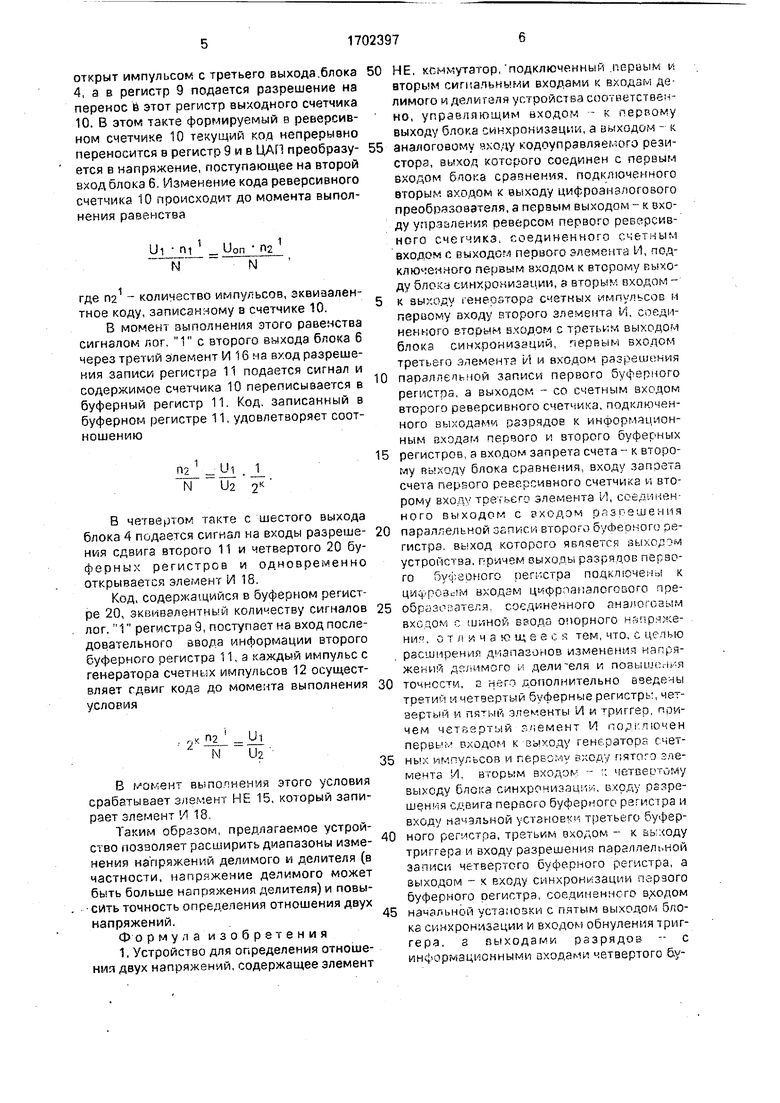

i Р s-fj - , с рэдепемия о.ноше- i и TVX ч1 сопержит KCi. Myraiop 1 ь ;, r io i I ic1 г 2 депптоля 3 vcrpofici- dc Ьло1; т ,i-.ynpui,-, кодоуправляе- ми 1 jL.. , i г . 3 cpSB. OHU i ЦлП 7,

flfpfiJH f - „ i J u /1C«4 U 8 ПсОЭЫЙ б уфзс ь -i с т i piopon pe«c pЈ U - bri г Ct ii i j, i л Р/оерчыГ рошстр ,, i не с i j 1 - 1зт i л г .пульсое, пеовыи З

riiOpP 4 inf-viGHiU 1/1 SnGiieh i il ц, j - Г i

lij j;i ,н i

19 ( -

re

0 liaTf8p t1H i f l ПЯТЫЙ

p SA « буферный регистр

f-ulG

:пл

пл/ рз( 1 стр 20 три, еперагоь yi./iiiyr cca

Р с- i ,/P i oer CiD 3, элемьнч ИП /i-Hf 2 перин1 ВТО1ОЙ/.6 гретой , -s T-

i И 2ПП1 1 rf ЛеМ згПЫ И И fv f

30

j c н степ i-.fibo ie; слецуоаим обра oor i

IV ел iv OIH vc i j Niaa coctCbt ил чч- it-ioex 1 | гоч Hf- /льч.ом начал -чой vyci нов п iioro ьь ond бпока 4 титер 2 G. т - в MI я з сгар -ом рзз- psin,e ippLO c pcir с Г р остяя -- ных г-.н ОА i vp2pH;rc регистра У - nor.

1 П Р-р « ,Э JoiNO/ T UAH / уСТ НйБЛИВ-Зетс° .nu} i о- яip i Hii0 Uoii

В чгрзом К ч1ульсо,ч п первого ВЧХСДР Ьл)| з с роиизааии & ко лмутатор ncr.T. r f li JT Mo.r Оллсение U делмгс )Я вхоцу u- Ltt ора 5 Одноврэг-тен э с счгьал JM i го о выхода гшоюэ 4 в ре- i метре U Се -rfniaaeTCP нэнэльнов зна е- ие ол л з/1Еагшнт os сас.Ьфицче--- т/ nepi ; гчп pejitctotj о рчвно з единице, i че и 5 dn Vic -j b стачаплир ьгся и jn r pesHC p4 попаегLr сигнач разрешения сдвига кода, элемент И 7 открыт сигналом лог. 1 с выхода триг- реоа 1 Импульсы с, генератора 12 поступает нз вход синхронизации регистра 9 и ск,/Щ80т1эляюг сдвиг 1 из старшего разря- иеа в последующие разряды, до тех пор, пока не выполняется неравенство

Ю

Uc

2K

U2

0

5

0

3

0 5

и на первом выходе блока 6 не появляется сигнал лог О, при этом триггер 21 опрокидывается, элемент l/i 17 закоывается сигналом с выхода триггера, з содержимое триггера 9 переписывается в регистр 20.

Во втором такте оаботы устройства им- к льсом с второго выхода блока Л открыва- ется элемент И 13, на регистр 19 подается разрешение ня перенос в этот регистр выходного кода счетчика 8 В этом такте формируемый в реверсивном счетчике 8 текущий код непрерывно переносится в регистр 19 и в резисторе 5 преобразуется в напряжение, поступающее на первый вход блока 6, на втором входе которого в это время действует напряжение с выхода ЦАП 7, оавное Uon/2K. Изменение кода в счетчи- е В происходит до тех пор, пока не выполняется равенство

irlUJll1 - Uon Ы 2к

где N - емкость счетчика;

гм - количество импульсов, эквивалентное коду, записанному в счетчике 8.

В момент выполнения этого равенства с второго выхода блока 6 на счетчик 8 подается запоета счета, фиксируя его содержимое.

В третьем гакте сигналом с первого выхода блока 4 коммутатор 1 подключает к входу резистора 5 напряжение делимого U1. При этом, поскольку в регистре 19 находится код счетчика 8, то на первом входе блока G с ьыхода резистора 5 формируется напряжение, равное Ui m /N Элемент И 14

открыт импульсом с третьего выхода.блока 4, а в регистр 9 подается разрешение на перенос 6 этот регистр выходного счетчика 10. В этом такте формируемый в реверсивном счетчике 10 текущий код непрерывно переносится в регистр 9 и в ЦАП преобразуется в напряжение, поступающее на второй вход блока 6. Изменение кода реверсивного счетчика 10 происходит до момента выполнения равенства

Uon 2 1 NN

где па - количество импульсов, эквивалентное коду, записанному в счетчике 10.

В момент выполнения этого равенства сигналом лог. 1 с второго выхода блока 6 через третий элемент И 16 на вход разрешения записи регистра 11 подается сигнал и содержимое счетчика 10 переписывается в буферный регистр 11. Код, записанный в буферном регистре 11, удовлетворяет соотношению

Ui

U2

J

оК

В четвертом такте с шестого выхода блока 4 подается сигнал на входы разрешения сдвига второго 11 и четвертого 20 бу- ферных регистров и одновременно открывается элемент И 18.

Код, содержащийся в буферном регистре 20, эквивалентный количеству сигналов лог. 1 регистра 9, поступает на вход последовательного ввода информации второго буферного регистра 11, а каждый импульс с генератора счетных импульсов 12 осуществляет гдвиг кода до момента выполнения условия

2 к 2 Ui

N

U2

В момент выполнения этого условия срабатывает элемент НЕ 15, который запирает элемент И 18.

Таким образом, предлагаемое устройство позволяет расширить диапазоны изменения напряжений делимого и делителя (в частности, напряжение делимого может быть больше напряжения делителя) и новы- сйть точность определения отношения двух напряжений.

Формула изобретения

1. Устройство для определения отношения двух напряжений, содержащее элемент

НЕ, кйммутатор, подключенный .первым и вторым сигнальными входами к входам делимого и дели геля устройства соответственно, управляющим входом - к первому выходу блока синхронизации, а выходом - к

аналоговому .«.ходу кодоуправняемого резистора, выход которого соединен с первым входом бпока сравнения, подключенного вторым входом к выходу цифроаналогового преобразователя, а первым выходом - к входу управления реверсом первого реверсивного счегчикз, соединенного счетным входом с выходом первого элемента И, подключенного первым входом к второму выходу блока синхронизации, а вторым входом к выходу генератора счетных импульсов и первому входу второго элемента И, соединенного вторым входом с третьим выходом блока синхронизации, первым входом третьего элемента И и входом разрешения

параллельной записи первого буферного регистра, а выходом - со счетным входом второго реверсивного счетчика, подключенного выходами разрядов к информационным входам первого и второго буферных

регистров, а входом запрета счета - к второму выходу блока сравнения, входу запоета счета первого реверсивного счетчика и второму входу третьего элемента И, соединенного выходом с входом рлзг.ешения

параллельной записи второго буФеоного регистра, выход которого является выходэм устройства, причем выходы разрядов первого буфеоного регистра подключены к цифровым входам цмфрпапалсгсвого прео5рйзо;:ателя. соединенного аналоговым входом с шиной ввода опорного напряжения, отличающееся тем, что, с целью расширения диапазонов изменения напряжений делимого и делителя и повышения

точности, Е него дополнительно введены третий и четвертый буферные регистры, четвертый и пятый элементы И и триггер, причем четвертый йпемент И подключен первые входом к выходу генератора счетных импульсов и первому входу пятого элемента И, вторым входом - ; четвертому выходу блока синхронизации, входу разрешения сдвига первого буферного регистра и входу начальной установки третьего буферного регистра, третьим входом - к выходу триггера и входу разрешения параллельной записи четвертого буферного регистра, а выходом - к входу синхронизации пгрзого буферного регистра, соединенного в,ходом

начальной установки с пятым выходом блока синхронизации и входом обнуления триггера, а выходами разрядов -- с информационными входами четвертого &уферного регистра, подключенного входом разрешения сдвига к шестому выходу блока синхронизации, входу разрешения сдвига второго буферного регистра и второму входу пятого элемента И, входом синхронизации - к выходу пятого элемента И и входу синхронизации второго буферного регистра, а выходом старшего разряда - к входу последовательного ввода данных второго буферного регистра и входу элемента НЕ, выход которого соединен с третьим входом пятого элемента И, причем первый блока сравнения подключен к входу установки о единицу триггера и входу управления реверсом второго реверсивного счетчика, а выходы разрядов первого реверсивного счетчика соединены с информационными входами третьего буферного регистра, подключенного входом разрешения параллельной записи к второму выходу блока синхронизации, а выходами разрядов - к управляющим входам кодоуправля- емого резистора.

0

5

0

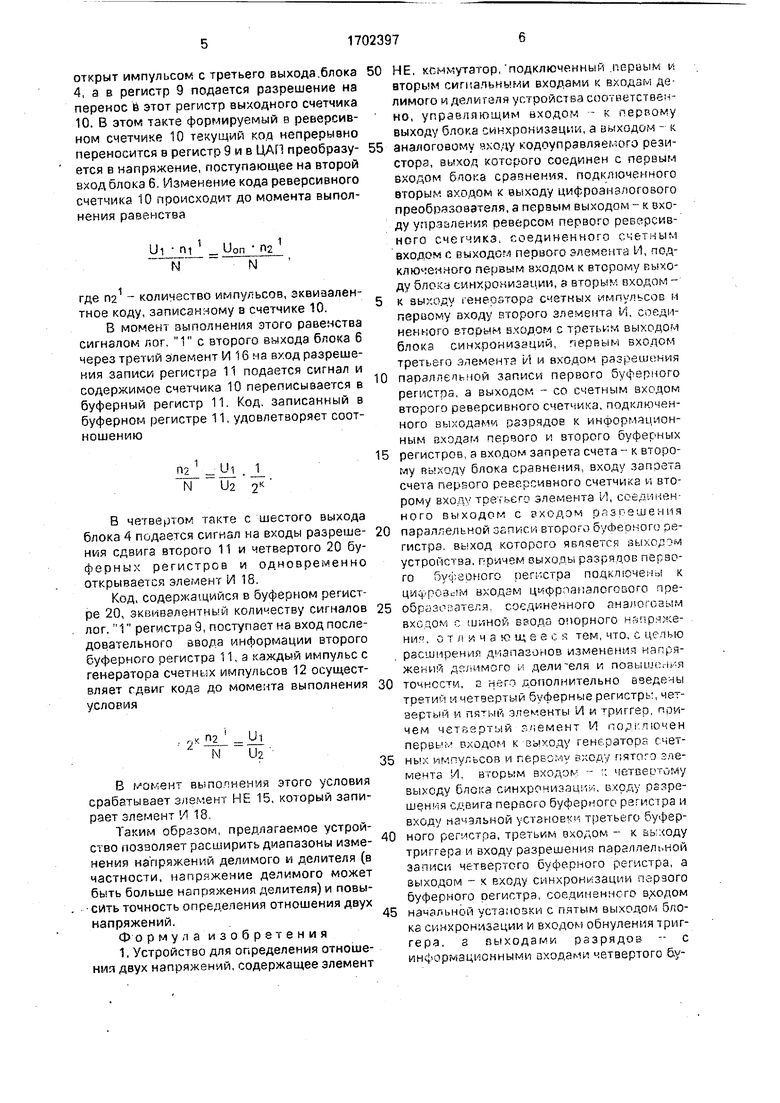

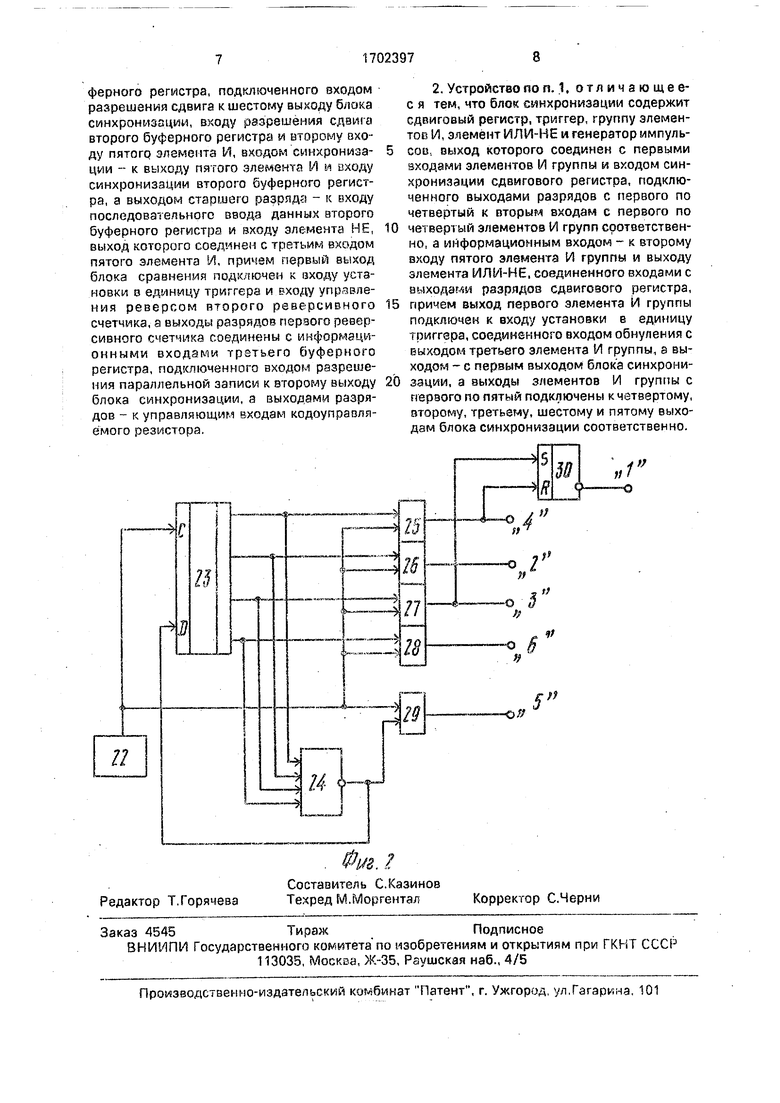

2. Устройство по п. 1, отличающее- с я тем, что блок синхронизации содержит сдвиговый регистр, триггер, группу элементов И, элемент ИЛИ-НЕ и генератор импульсов выход которого соединен с первыми входами элементов И группы и входом синхронизации сдвигового регистра, подключенного выходами разрядов с первого по четвертый к вторым входам с первого по четвертый элементов И групп соответственно, а информационным входом - к второму входу пятого элемента И группы и выходу элемента ИЛИ-НЕ, соединенного входами с выходами разрядов сдвигового регистра, причем выход первого элемента И группы подключен к входу установки в единицу тоиггера, соединенного входом обнуления с выходом третьего элемента И группы, а выходом - с первым выходом блока синхронизации, а выходы элементов И группы с первого по пятый подключены к четвертому, второму, третьему, шестому и пятому выходам блока синхронизации соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения отношения двух напряжений | 1983 |

|

SU1151994A1 |

| Вычислительное устройство для определения параметров пика | 1988 |

|

SU1562937A1 |

| Устройство сжатия информации | 1980 |

|

SU942109A2 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

| Устройство для последовательного деления | 1986 |

|

SU1304017A1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение при обработке аналоговых сигналов в измерительных системах. Цель изобретения - расширение диапазонов изменения напряжений делимого и делителя и повышение точности. Устройство для определения отношения двух напряжений содержит коммутатор 1, блок 4 синхронизации, кодоуправляемый резистор 5, блок 6 сравнения, цифроаналоговый преобразователь 7, два реверсивных счетчика 8 и 10, четыре буферных регистра 9, 11, 19 и 20, генератор 12 счетны импульсов, пять элементов И 13, 14, 16, 17 и 13. элемент НЕ 15 и триггер 21. Работа устройства выпопня ется в четыре такта: в первом такте осуществляются нормирован 0 (сдв«г) кода коэффициента деления опорного напряжения до срабатывания блока сравнения, во втором третьем тактах- соответствующре СП

15

-э

-Э

и

Фм. 2

Редактор Т.Горячева

Составитель С.Казинов Техред М.Моргентал

$

i

1 til

i

V

о S я

о 6 п

f}

It

Корректор С.Черни

| Аналого-цифровое делительное устройство | 1984 |

|

SU1256046A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Локомобиль | 1928 |

|

SU11519A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-30—Публикация

1989-09-29—Подача