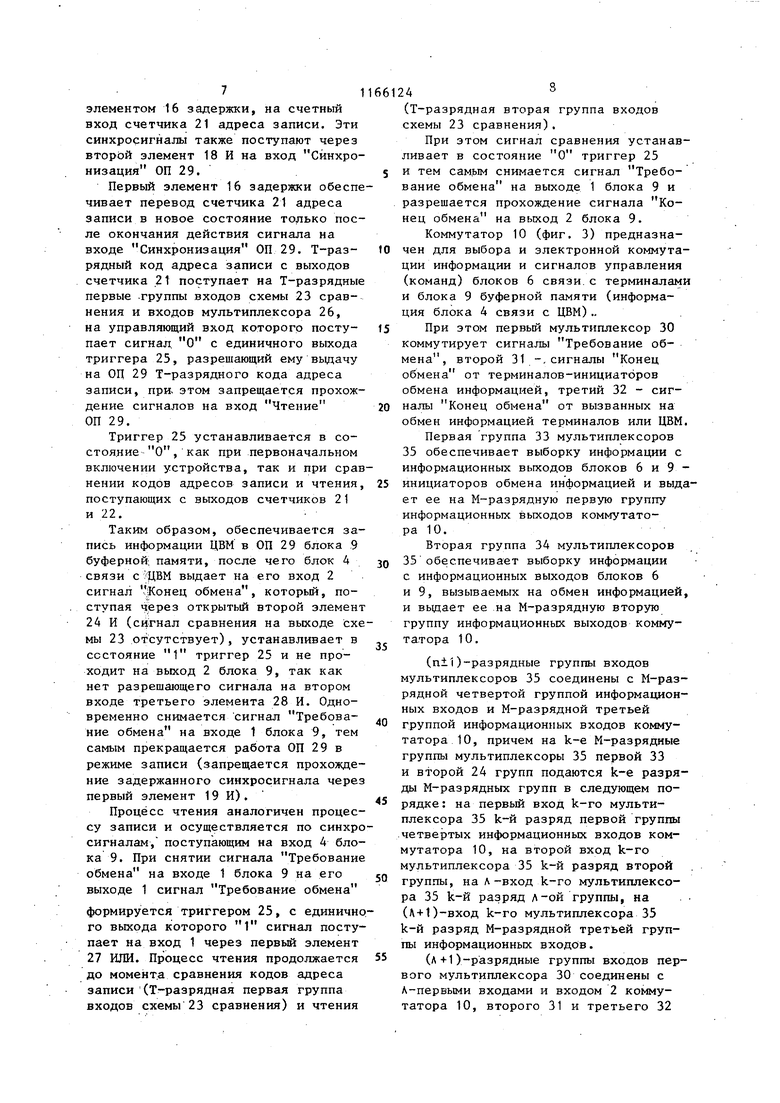

вход которого соединен с выходом требования обмена блока буферной памяти, выход конца обмена которого соединен с вторым управляющим входом коммутатора, выход требования обмена которого соединен с первым входом блока управления, второй и третий входа которого соединены с первым и вторым выходами конца обмена коммутатора соответственно, второй выход блока управления соединен с синхровходом блока буферной памяти и с первыми синхровходами блоков связи с терминалами группы, вторые синхровходы которых соединены с четвертым выходом блока управления, группы информационных входов блоков связи с терминалами группы соединены с соответствующими группами выходов блока элементов ИЛИ, выходы требования обмена блоков связи с терминалами группы соединены с первой группой управляющих входов коммутатора, вторая группа управляющих входов которого соединена с выходами конца обмена блоков связи с терминалами группы, группы информационных выходов которых соединены с второй группой информационных входов коммутатора, причем блок управления содержит два дешифратора, триггер, два элемента ИЛИ, элемент И, задающий генератор, делитель частоты, при этом группы входов первого и второго дешифраторов обра.зуют первую и вторую группы входов блока управления соответственно, группы выходов первого и второго дешифраторов образуют первую и вторую группы выходов блока управления соответственно, причем группа выходов первого дешифратора соединена также с группой входов первого элемента ИЛИ, выход которого является первым выходом блока управления, единичный вход триггера является первым входом блока управления, первый и второй входы второго элемента ИЛИ являются вторым и третьим входами блока управления , вькод делителя частоты является вторым выходом блока управления, выход элемента И является третьим выходом блока управления, первый выход задающего генератора соединен с первым входом элемента И и является четвертым выходом блока управления, выход второго элемента ИЛИ соединен с нулевым входом триггера, единичный выход которого сое6124

динен с разрешающими входами первого и второго дешифраторов, нулевой выход триггера соединен с вторым входом элемента И, второй выход задающего генератора соединен с входом делителя частоты.

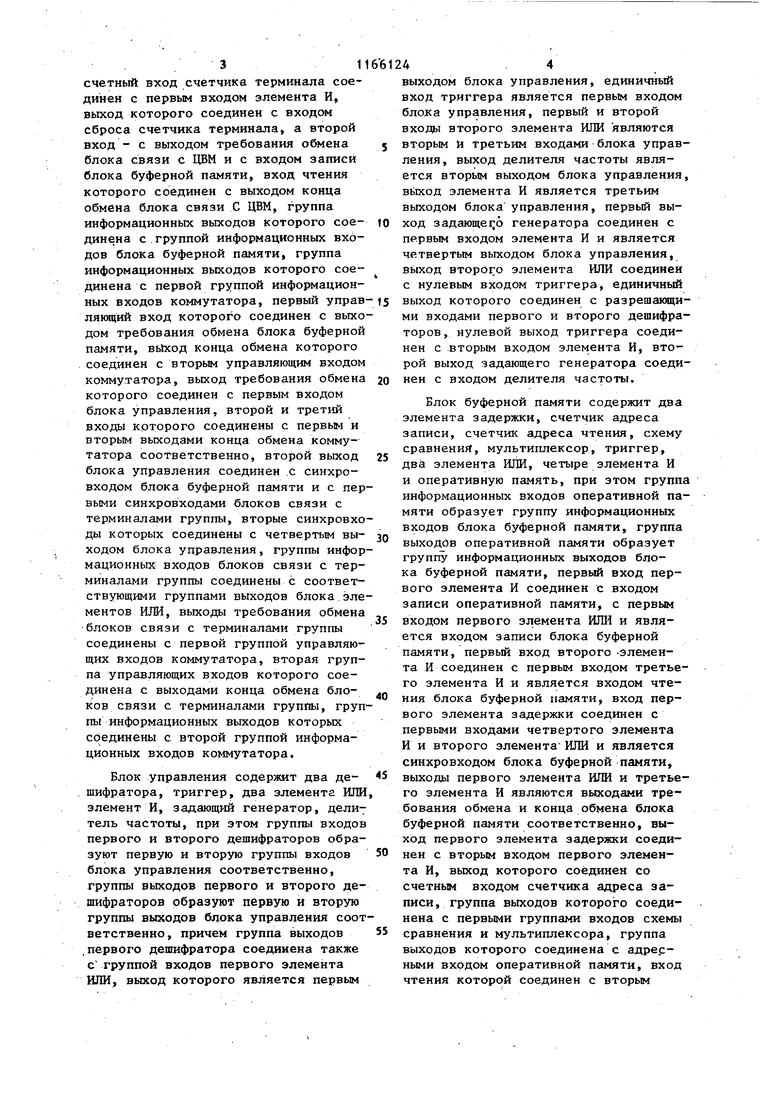

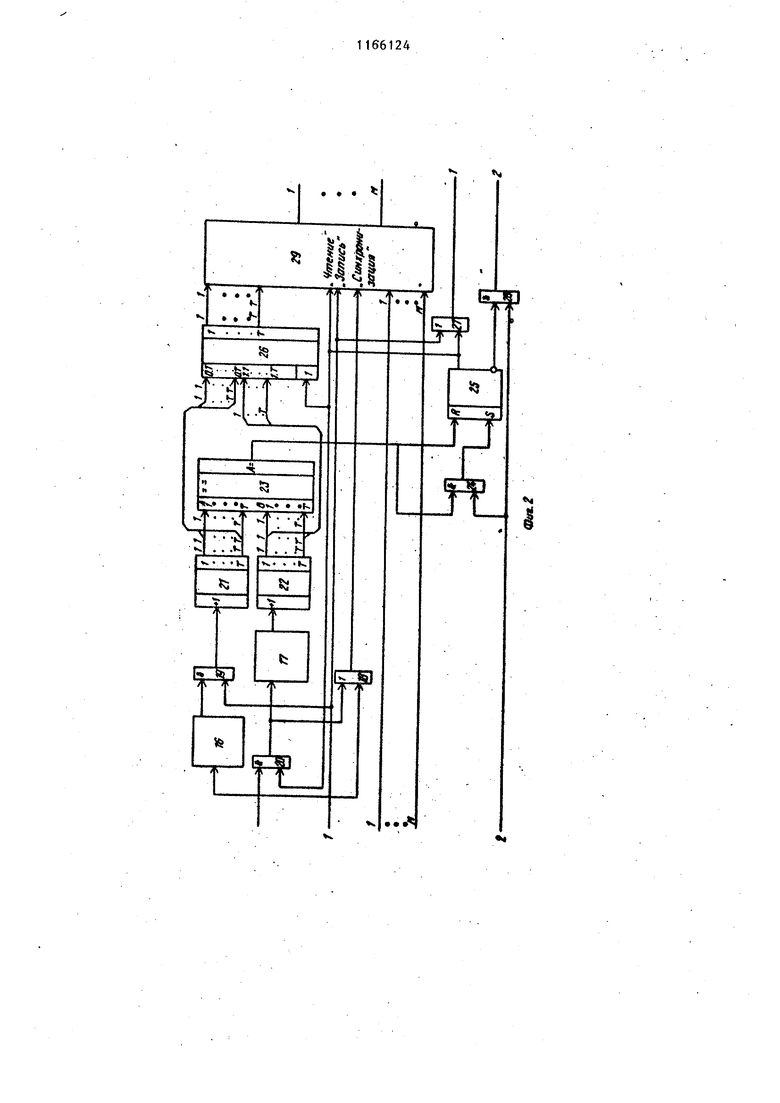

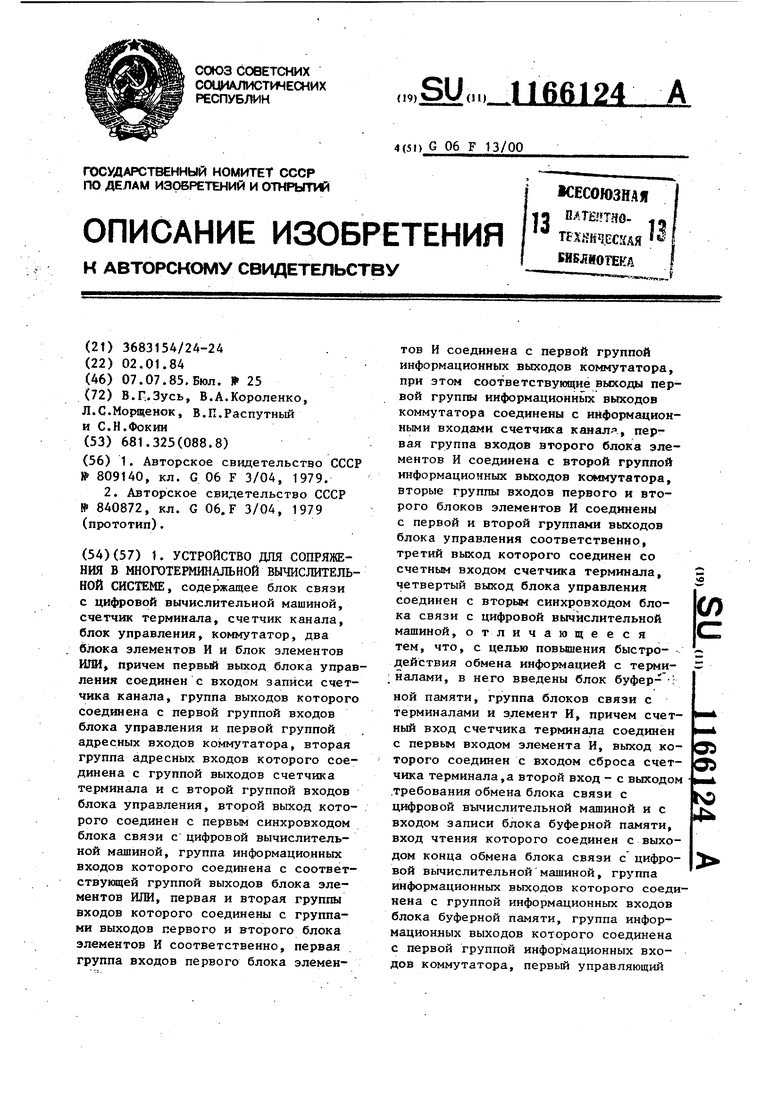

2. Устройство по п. 1, о т л ичающееся тем, что блок буферной памяти содержит два элемента задержки, счетчик адреса записи, счетчик адреса чтения, схему сравнения, мультиплексор, триггер, два элемента ИЛИ, четыре элемента И и оперативную память, при этом группа информационных входов оперативной памяти образует группу информационных входов блока буферной памяти, группа выходов оперативной памяти образует группу информационных выходов блока буферной памяти, первый вход первого элемента И соединен с , входом записи оперативной памяти, с первым входом первого элемента ИЛИ и является входом записи блока буферной памяти, первый вход второго элемента И соединен с первым входом третьего элемента И и является входом чтения блока буферной памяти, вход первого элемента задержки соединен с первыми входами четвертого элемента И и второго элемента ИЛИ и является синхровходом блока буферной памяти, выходы первого элемента ИЛИ и третьего элемента И являются выходами требования обмена и конца обмена блока буферной памяти соответственно, выход первого элемента задержки соединен с вторым входом первого элемента И, выход которого соединен со счетным входом счетчика адреса записи, группа выходов которого соединена с первьми группами входов схемы сравнения и мультиплексора, группа выходов которого соединена с адресными входом оперативной памяти, вход чтения которой соединен с вторым входом первого элемента ИЛИ, с единичным выходом триггера, с управляющим входом мультиплексора и с вторым входом четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и с входом второго элемента задержки, выход которого соединен со счетным входом счетчика адреса чтения, группа выходов которого соединена с вторыми группами входов мультиплексора и схемы сравнения, выход которой соединен

с вторым входом второго элемента И и с нулевым входом триггера, нулевой выход которого соединен с вторым третьего элемента И, единичный вход триггера соединен с выходом второго элемента И, выход второго элемента ИЛИ соединен с синхронизирующим входом оперативной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1977 |

|

SU703799A1 |

| Устройство для сопряжения абонетского пункта с цифровой вычислительной машиной | 1977 |

|

SU736085A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и терминалами | 1980 |

|

SU881726A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и терминалами | 1982 |

|

SU1034029A2 |

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

| Устройство для сопряжения цифровой вычис-лиТЕльНОй МАшиНы C ВидЕОТЕРМиНАлОМ | 1979 |

|

SU840872A1 |

| Устройство для обмена информацией | 1974 |

|

SU732848A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ В МНОГОТЕРМИНАЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ, содержащее блок связи с цифровой вычислительной машиной, счетчик терминала, счетчик канала, блок управления, коммутатор, два блока элементов И и блок элементов ШШ, причем первьА выход блока управления соединен с входом записи счетчика канала, группа выходов которого соединена с первой группой входов блока управления и первой группой адресных входов коммутатора, вторая группа адресных входов которого соединена с группой выходов счетчика терминала и с второй группой входов блока управления, второй выход которого соединен с первым синхровходом блока связи с цифровой вычислительной машиной, группа информационных входов которого соединена с соответствунлцей группой выходов блока элементов ИЛИ, первая и вторая группы входов которого соединены с группами выходов первого и второго блока элементов И соответственно, первая группа входов первого блока элементов И соединена с первой группой информационных выходов коммутатора, при этом соответствующие выходы первой группы информационных выходов коммутатора соединены с информационными входами счетчика канала, первая группа входов второго блока элементов И соединена с второй группой информационных выходов коммутатора, вторые группы входов первого и второго блоков элементов И соединены с первой и второй группами выходов блока управления соответственно, третий выход которого соединен со счетным входом счетчшса терминала, четвертый выход блока управления (Л соединен с вторьм синхровходом блока связи с цифровой вычислительной машиной, отличающееся тем, что, с целью повьвиения быстродействия обмена информацией с терми; налами, в него введены блок буфер- : ной памяти, группа блоков связи с терминалами и элемент И, причем счетный вход счетчика терминала соединен с первым входом элемента И, выход которого соединен с входом сброса счетчика терминала,а второй вход - с выходом .требования обмена блока связи с цифровой вычислительной машиной и с входом записи блока буферной памяти, вход чтения которого соединен с выходом конца обмена блока связи с цифровой вычислительной машиной, группа информационных выходов которого соединена с группой информационных входов блока буферной памяти, группа инфорнациониых выходов которого соединена с первой группой информационных входов коммутатора, первый управляющий

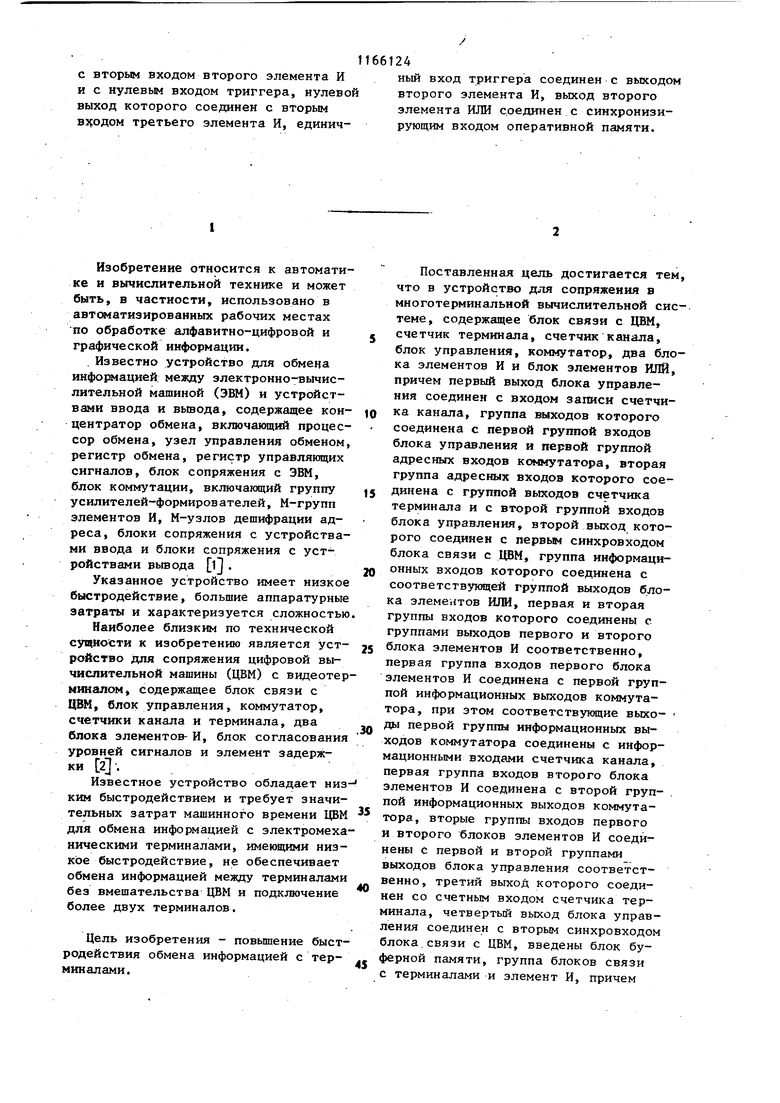

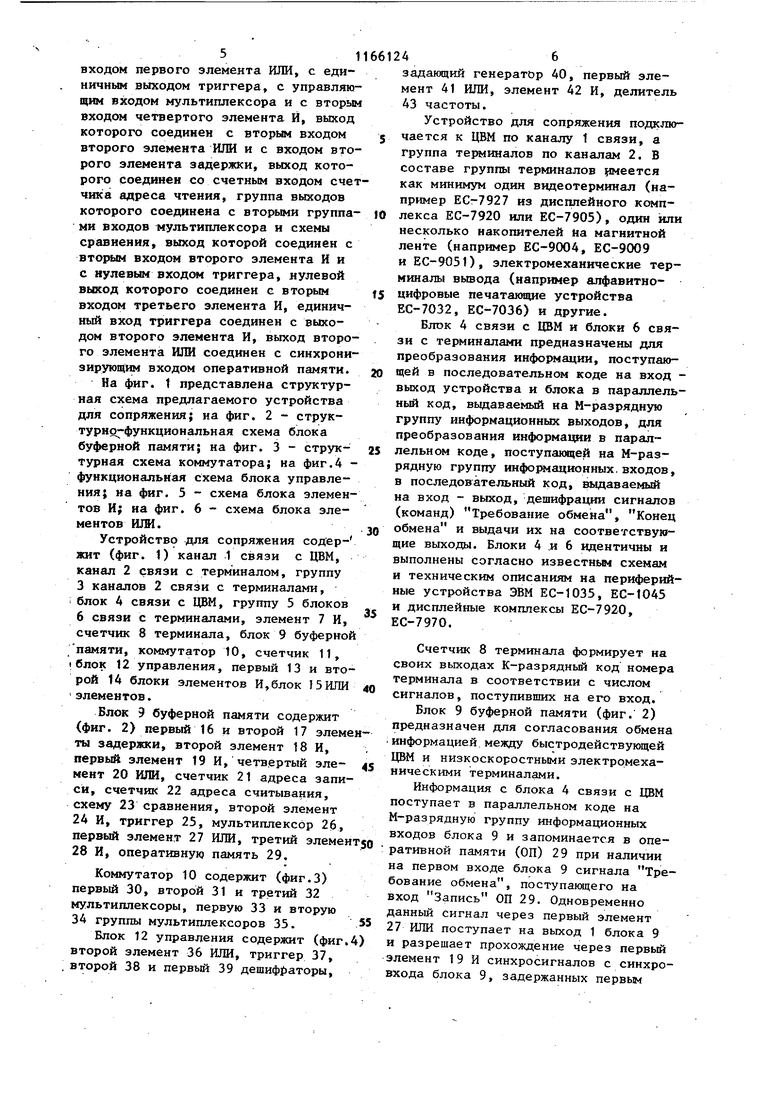

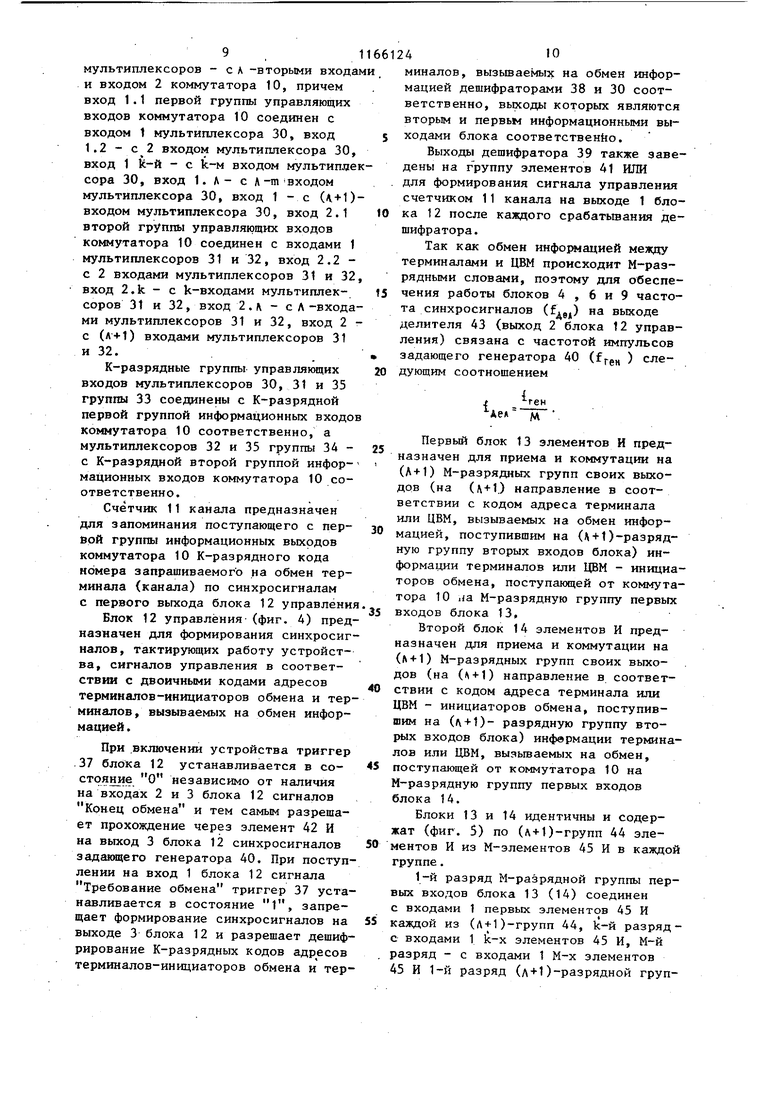

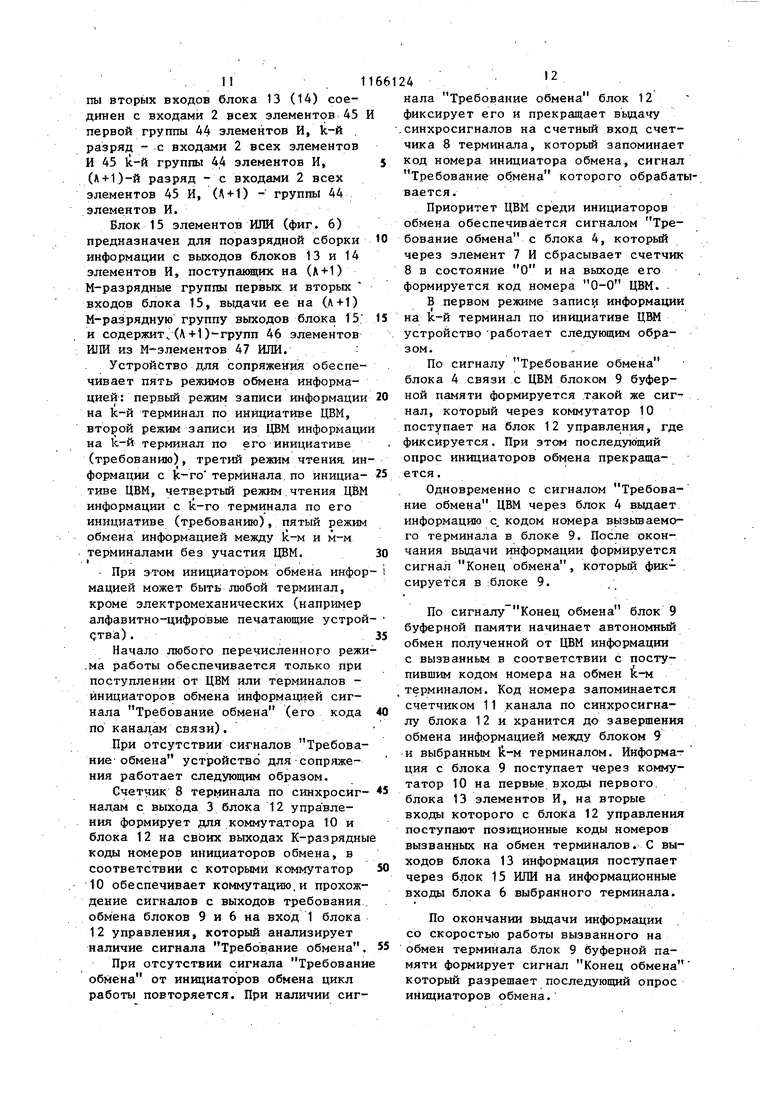

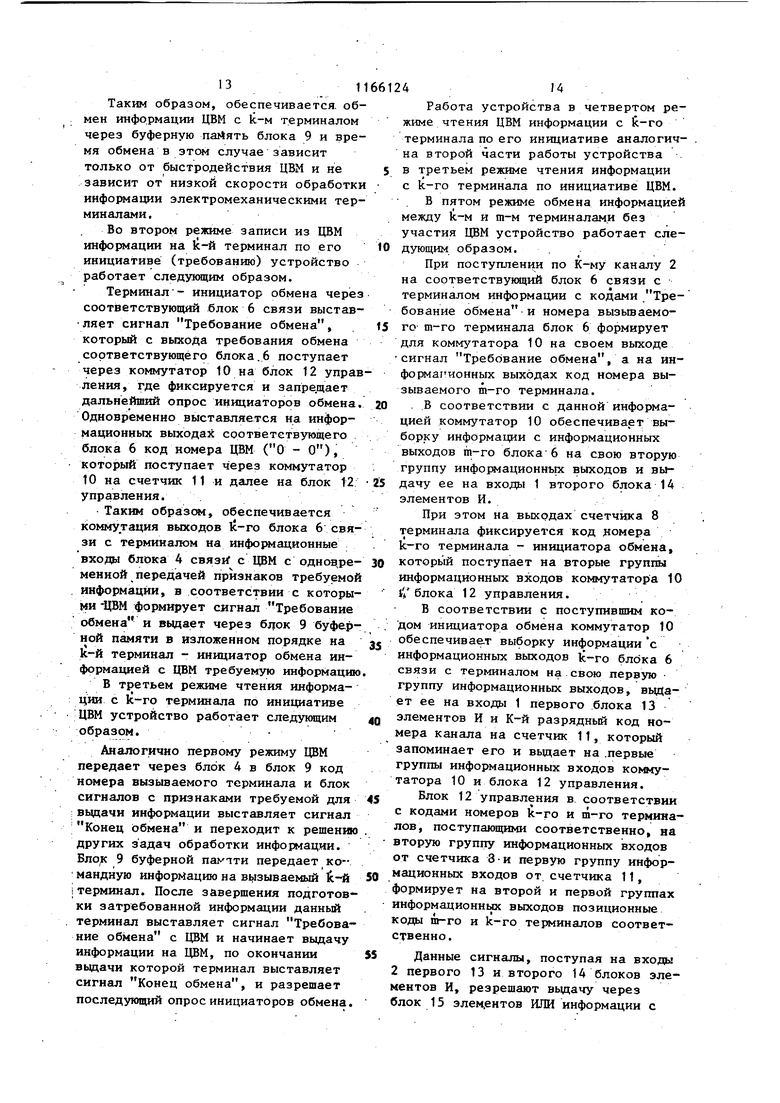

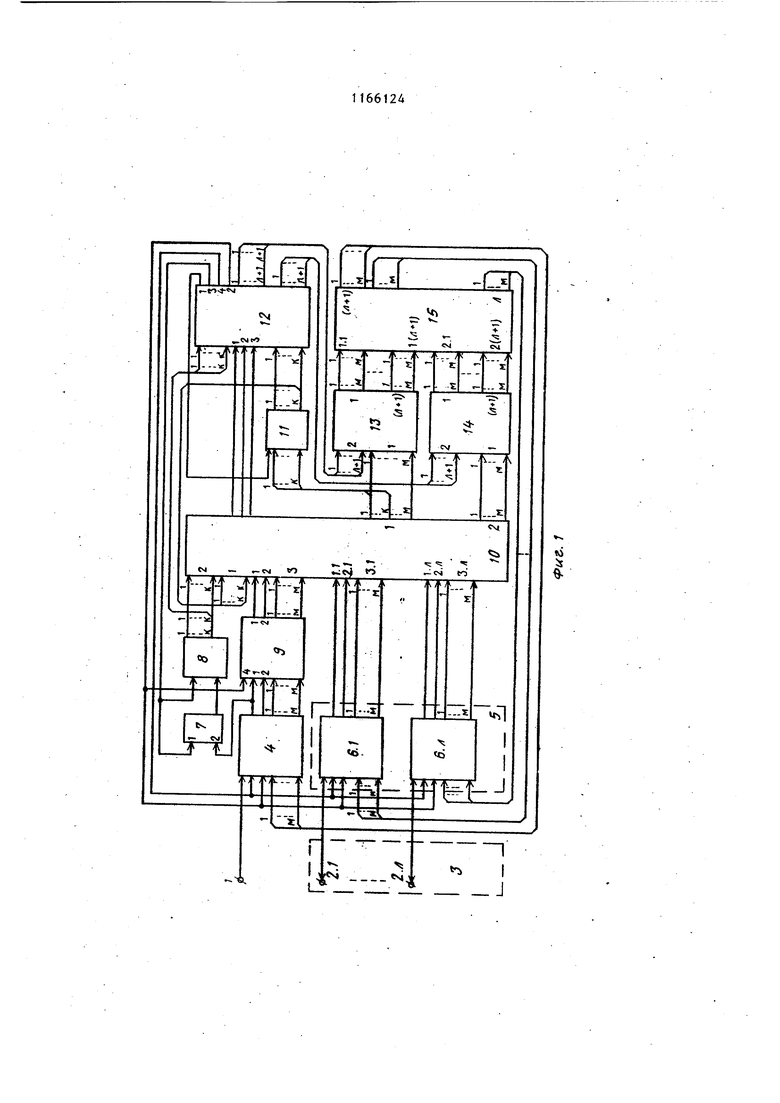

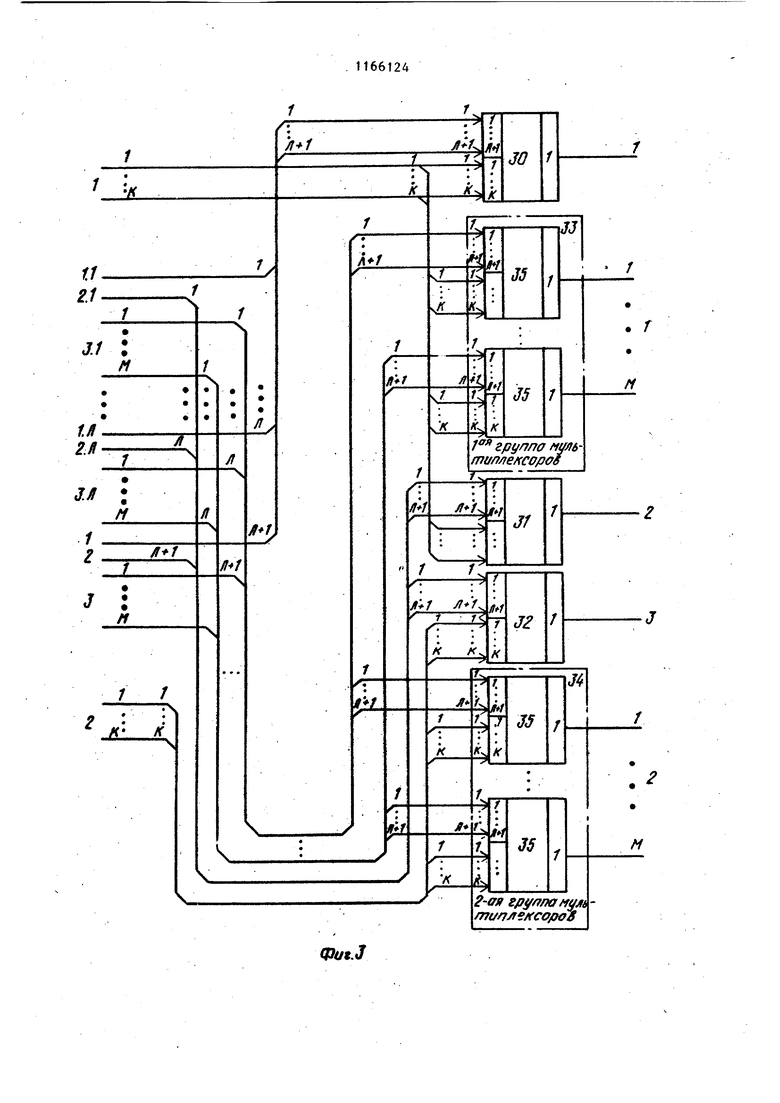

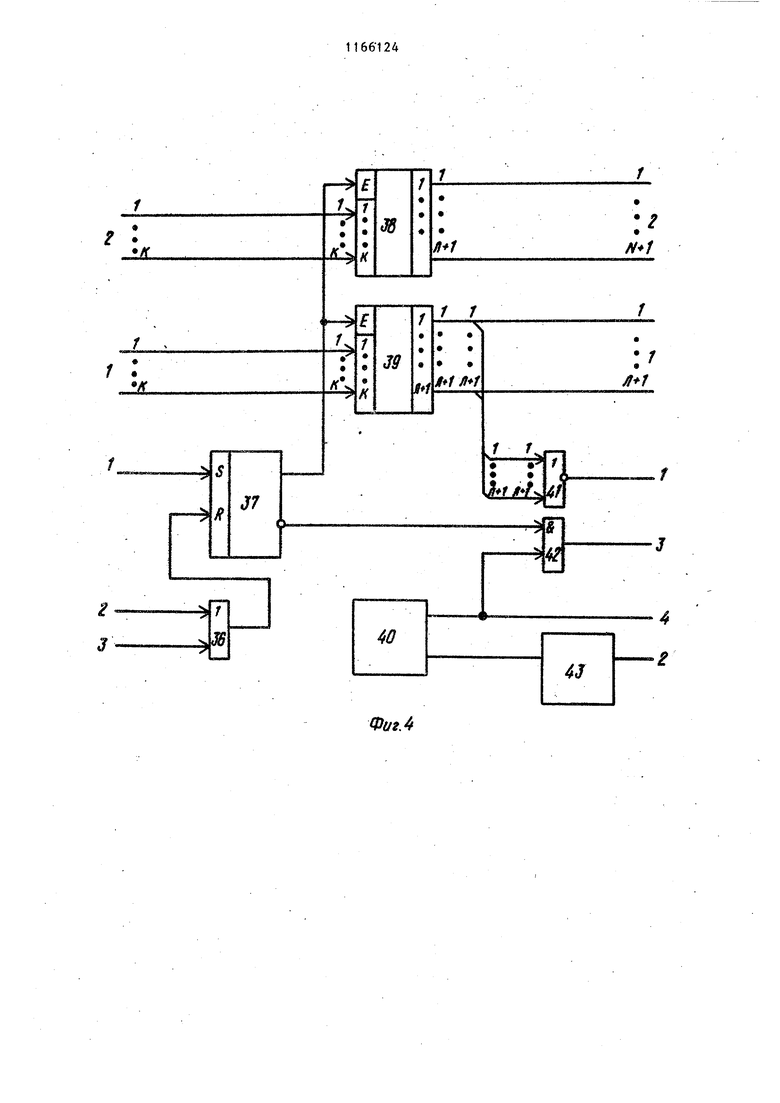

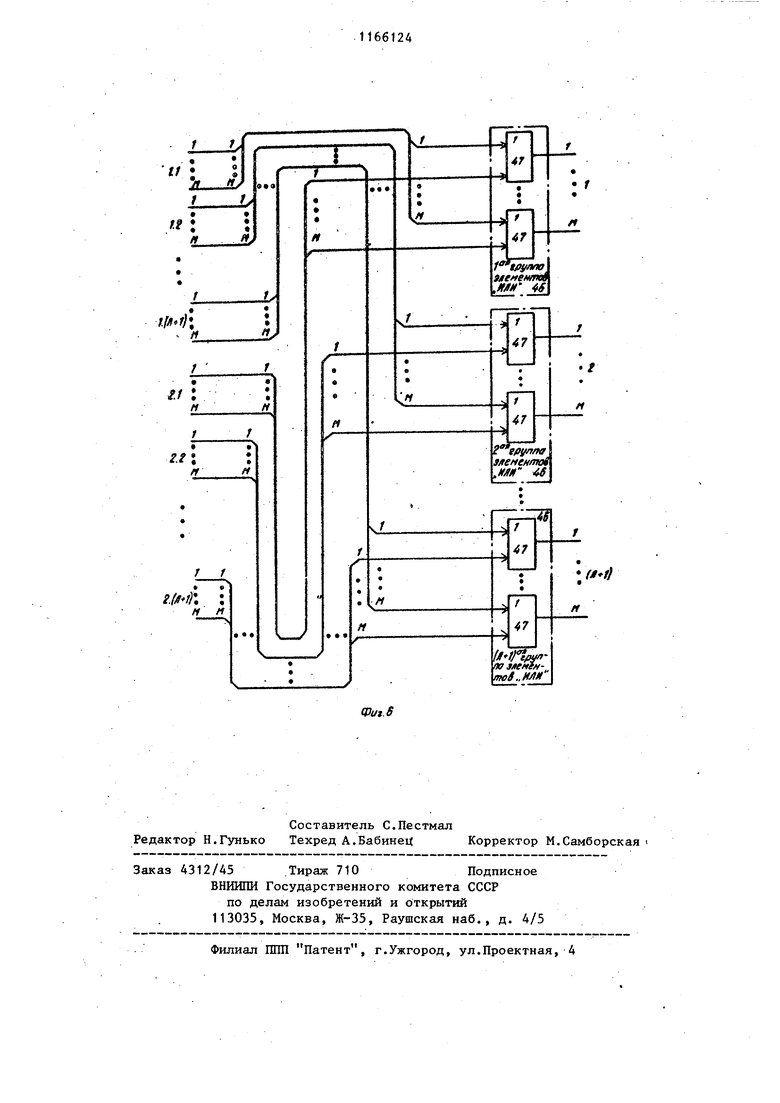

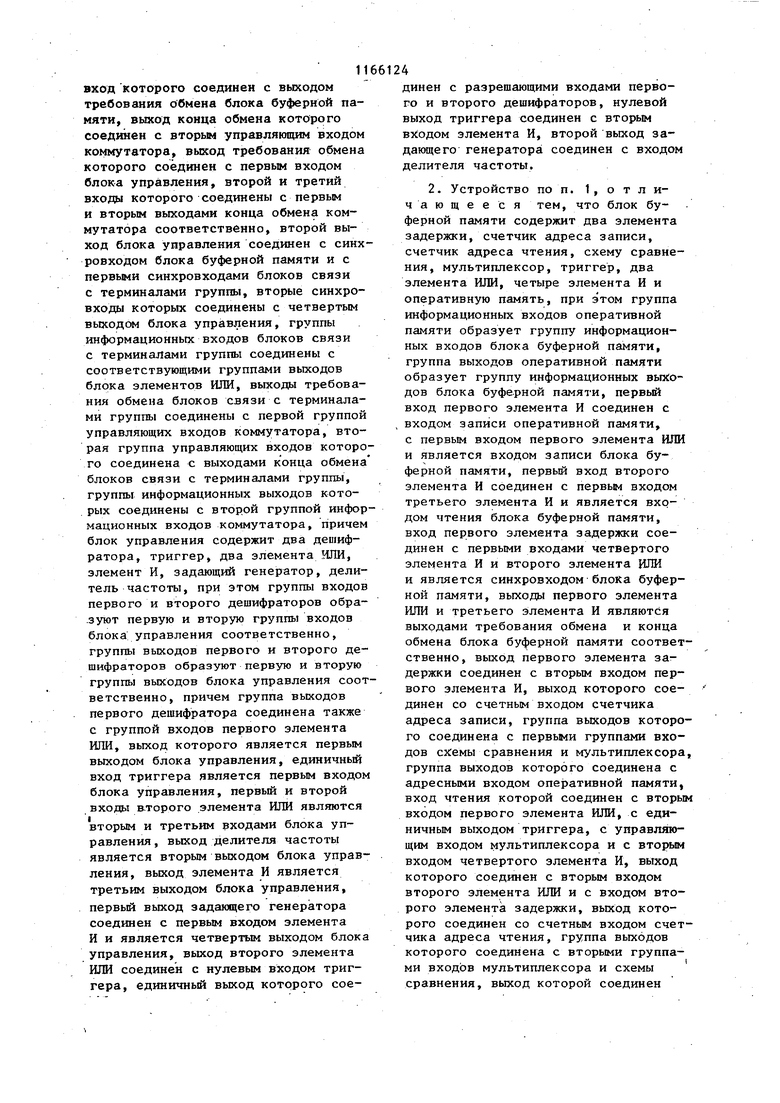

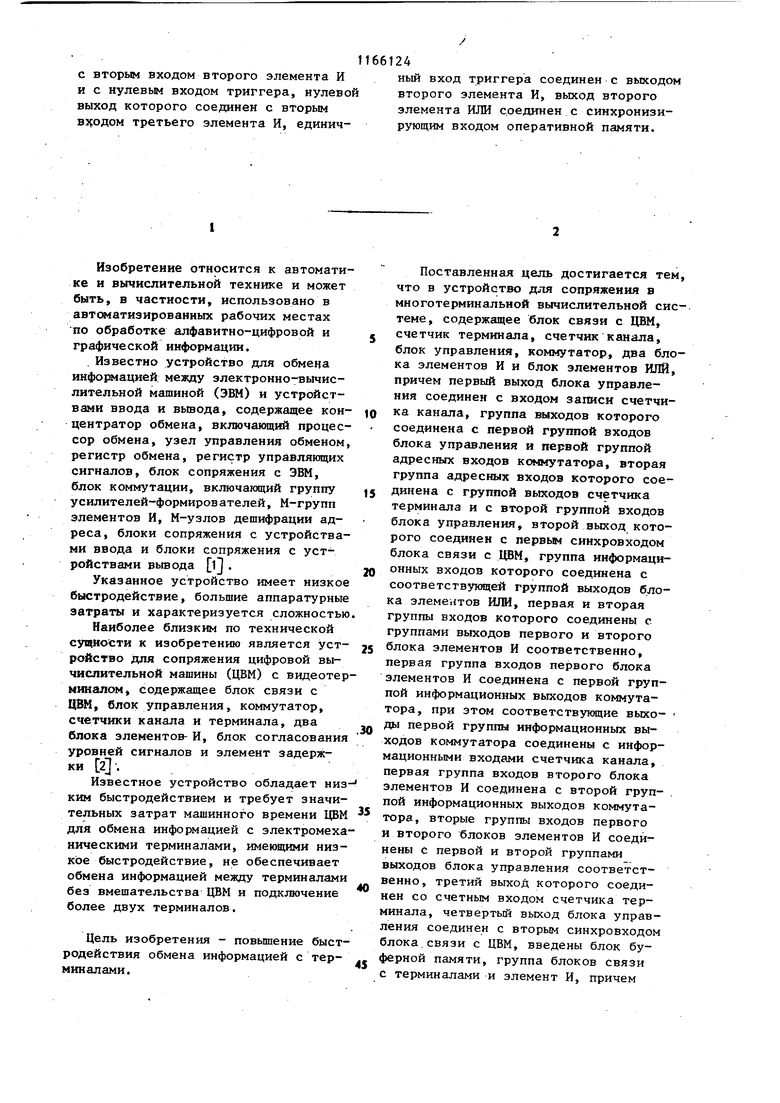

Изобретение относится к автоматике и вычислительной технике и может быть, в частности, использовано в автоматизированных рабочих местах по обработке алфавитно-цифровой и графической информации. Известно устройство для обмена информацией между электронно-вычислительной машиной (ЭВМ) и устройствами ввода и вьшода, содержащее концентратор обмена, включающий процессор обмена, узел управления обменом, регистр обмена, регистр управляющих сигналов, блок сопряжения с ЭВМ, блок коммутации, включающий группу усилителей-формиров ателей, М-групп элементов И, М-узлов дешифрации адреса, блоки сопряжения с устройствами ввода и блоки сопряжения с устройствами рьшода lj , Указанное устройство имеет низкое быстродействие, большие аппаратурные затраты и характеризуется сложностью Наиболее близким по технической сущности к изобретению является устройство для сопряжения цифровой вычислительной машины (ЦВМ) с видеотер миналом, содержащее блок связи с ЦВМ, блок управления, коммутатор, счетчики канала и терминала, два блока элементов- И, блок согласования уровней сигналов и элемент задержки . Известное устройство обладает низ КИМ быстродействием и требует значительных затрат машинного времени ЦВМ для обмена информацией с электромеха ническими терминалами, имеиицими низкое быстродействие, не обеспечивает обмена информацией между терминалами без вмешательства ЦВМ и подключение более двух терминалов. Цель изобретения - повьшение быст родействия обмена информацией с терминалами. Поставленная цель достигается тем, что в устройство для сопряжения в многотерминальной вычислительной сие-, теме, содержащее блок связи с ЦВМ, счетчик терминала, счетчик канала, блок управления, коммутатор, два блока элементов И и блок элементов ИЛИ, причем первый выход блока управления соединен с входом записи счетчика канала, группа выходов которого соединена с первой группой входов блока управления и первой группой адресных входов коммутатора, вторая группа адресных входов которого соединена с группой выходов счетчика терминала и с второй группой входов блока управления, второй выход которого соединен с первым синхровходом блока связи с ЦВМ, группа информационных входов которого соединена с соответствующей группой выходов блока элементов ИЛИ, первая и вторая группы входов которого соединены с группами выходов первого и второго блока элементов И соответственно, первая группа входов первого блока элементов И соединена с первой группой информационных выходов коммутатора, при этом соответствующие выходы первой группы информационных выходов коммутатора соединены с информационными входами счетчика канала, первая группа входов второго блока элементов И соединена с второй группой информационных выходов коммутатора, вторые группы входов первого и второго блоков элементов И соединены с первой и второй группами выходов блока управления соответственно, третий выход которого соединен со счетным входом счетчика терминала, четвертый выход блока управления соединен с вторым синхровходом блока,связи с ЦВМ, введены блок буферной памяти, группа блоков связи с терминалами и элемент И, причем счетный вход счетчика терминала соединен с первым входом элемента И, вькод которого соединен с входом сброса счетчика терминала, а второй вход - с выходом требования обмена блока связи с ЦВМ и с входом записи блока буферной памяти, вход чтения которого соединен с выходом конца обмена блока связи С ЦВМ, группа информационньк выходов которого соединена с группой информационных входов блока буферной памяти, группа информационных выходов которого соединена с первой группой информационных входов коммутатора, первый управ ляющйй вход которого соединен с выхо дом требования обмена блока буферной памяти, вьЬсод конца обмена которого соединен с вторым управляющим входом коммутатора, выход требования обмена которого соединен с первым входом блока управления, второй и третий входы которого соединены с первым и вторым выходами конца обмена коммутатора соответственно, второй выход блока управления соединен .с синхровходом блока буферной памяти и с пер выми синхровходами блоков связи с терминалами группы, вторые синхровхо ды которых соединены с четвертым выходом блока управления, группы инфор мационных входов блоков связи с терминалами группы соединены с соответствующими группами выходов блока.эле ментов ИЛИ, выходы требования обмена блоков связи с терминалами группы соединены с первой группой управляющих входов коммутатора, вторая группа управляющих входов которого соединена с выходами конца обмена блоков связи с терминалами группы, груп пы информационных выходов которых соединены с второй группой информационных входов коммутатора. Блок управления содержит два дешифратора, триггер, два элемента ИЛИ элемент И, задающий генератор, делитель частоты, при этом группы входов первого и второго дешифраторов образуют первую и вторую группы входов блока управления соответственно, группы выходов первого и второго дешифраторов образуют первую и вторую группы выходов блока управления соот ветственно, причем группа выходов первого дешифратора соединена также с группой входов первого элемента ШШ, выход которого является первым выходом блока управления, единичный вход триггера является первым входом блока управления, первый и второй входы второго элемента ИЛИ являются вторым И третьим входами блока управления, выход делителя частоты является вторым выходом блока управления, выход элемента И является третьим выходом блока управления, первый выход задающе1;6 генератора соединен с первым входом элемента И и является четвертым выходом блока управления, выход второго элемента ИЛИ соединен с нулевым входом триггера, единичный выход которого соединен с разрешакицими входами первого и второго дешифраторов, нулевой выход триггера соединен с .вторым входом элемента И, второй выход задающего генератора соединен с входом делителя частоты. Блок буферной памяти содержит два элемента задержки, счетчик адреса записи, счетчик адреса чтения, схему сравнения, мультиплексор, триггер, два элемента ИЛИ, четыре элемента И и оперативную память, при этом группа информационных входов оперативной памяти образует группу информационных входов блока буферной памяти, группа ВЫХОДИВ оперативной памяти образует группу информационных выходов блока буферной памяти, первый вход первого элемента И соединен с входом записи оперативной памяти, с первым входом первого элемента ИЛИ и является входом записи блока буферной памяти, первый вход второго -элемента И соединен с первым входом третьего элемента И и является входом чтения блока буферной памяти, вход первого элемента задержки соединен с первыми входами четвертого элемента И и второго элемента ШШ и является синхровходом блока буферной памяти, выходы первого элемента ИЛИ и третьего элемента И являются выходами требования обмена и конца обмена блока буферной памяти соответственно, выход первого элемента задержки соединен с вторым входом первого элемента И, выход которого соединен со счетным входом счетчика адреса записи, группа выходов которого соединена с первыми группами входов схемы сравнения и мультиплексора, группа выходов которого соединена с адрерными входом оперативной памяти, вход чтения которой соединен с вторым входом первого элемента ИЛИ, с единичным выходом триггера, с управляю щим входом мультиплексора и с вторы входом четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и с входом вто рого элемента задержки, выход которого соединен со счетным входом сче чика адреса чтения, группа выходов которого соединена с вторыми группа ми входов мультиплексора и схемы сравнения, выход которой соединен с вторым входом второго элемента И и с нулевым входом триггера, нулевой выход которого соединен с вторым входом третьего элемента И, единичный вход триггера соединен с выходом второго элемента И, выход второ го элемента ИЛИ соединен с синхрони зирующим входом оперативной памяти. На фиг. 1 представлена структурная схема предлагаемого устройства для сопряжения; на фиг. 2 - структурно функциональная схема блока буферной памяти; на фиг. 3 - структурная схема коммутатора; на фиг.4 функциональная схема блока управления; на фиг. 5 - схема блока элемен тов И; на фиг. 6 - схема блока элементов ИШ. Устройство для сопряжения содержит (фиг. 1) канал 1 связи с ЦВМ, канал 2 свяэи с терминалом, группу 3 каналов 2 связи с терминалами, i блок 4 связи с ЦВМ, группу 5 блоков 6 свяэи с терминалами, элемент 7 И, счетчик 8 терминала, блок 9 буферно памяти, коммутатор 10, счетчик 11, (блок 12 управления, первый 13 и вто рой 14 блоки элементов И,блок 15 ИЛИ элементов. Блок 9 буферной памяти содержит (фиг. 2) первый 16 и второй 17 элем ты задержки, второй элемент 18 И, первый элемент 19 И, четвертый элемент 20 ИЛИ, счетчик 21 адреса запи си, счетчик 22 адреса считывания, схему 23 сравнения, второй элемент 24 И, триггер 25, мультиплексор 26, первый элемент 27 ИЛИ, третий элеме 28 И, оперативную память 29. Коммутатор 10 содержит (фиг.З) первый 30, второй 31 и третий 32 мультиплексоры, первую 33 и вторую 34 группы мультиплексоров 35. Блок 12 управления содержит (фиг второй элемент 36 ИЛИ, триггер 37, , второй 38 и первьй 39 дешиф)аторы. задающий генератор 40, первый элемент 41 ИЛИ, элемент 42 И, делитель 43 частоты. Устройство для сопряжения подключается к ЦВМ по каналу 1 связи, а группа терминалов по каналам 2. В составе группы терминалов | меется как минимум один видеотерминал (например ЕС-7927 из дисплейного комплекса ЕС-7920 или ЕС-7905), один или несколько накопителей на магнитной ленте (например ЕС-9004, ЕС-9009 и ЕС-9051), электромеханические терминалы вывода (например алфавитноцифровые печатающие устройства ЕС-7032, ЕС-7036) и другие. Блок 4 связи с ЦВМ и блоки 6 связи с терминалами предназначены для преобразования информгщии, поступающей в последовательном коде на вход выход устройства и блока в параллельный код, выдаваемый на М-разрядную группу информационных выходов, для преобразования информащ1и в параллельном коде, поступающей на М-разрядную группу информационных,входов, в последовательный код, выдаваемый на вход - выход, дешифрации сигналов (команд) Требование обмена, Конец обмена и выдачи их на соответствующие выходы. Блоки 4 .и 6 идентичны и выполнены согласно известным схемам и техническим описаниям на периферийные устройства ЭВМ ЕС-1035, ЕС-1045 и дисплейные комплексы ЕС-7920, ЕС-7970. Счетчик 8 терминала формирует на своих выходах К-разрядный код номера терминала в соответствии с числом сигналов, поступивших на его вход. Блок 9 буферной памяти (фиг. 2) предназначен для согласования обмена информацией между быстродействующей ЦВМ и низкоскоростными электромеханическими терминалами. Информация с блока 4 связи с ЦВМ поступает в параллельном коде на М-разрядную группу информационных входов блока 9 и запоминается в оперативной памяти (СП) 29 при наличии на первом входе блока 9 сигнала Требование обмена, поступакяцего на вход Запись СП 29. Одновременно данный сигнал через первый элемент 27 ИЖ поступает на выход 1 блока 9 и разрешает прохождение через первый элемент 19 И синхросигналов с синхровхода блока 9, задержанных первым 7 элементом 16 задержки, на счетный вход счетчика 21 адреса записи. Эти синхросигналы также поступают через второй элемент 18 И на вход Синхронизация ОП 29. Первый элемент 16 задержки обеспе чивает перевод счетчика 21 адреса записи в новое состояние только после окончания действия сигнала на входе Синхронизация ОП 29. Т-разрядный код адреса записи с выходов счетчика 21 поступает на Т-разрядные первые .группы входов схемы 23 сравнения и входов мультиплексора 26, на управляющий вход которого поступает сигнал. О с единичного выхода триггера 25, разрешающий ему выдачу на ОЦ 29 Т-разрядного кода адреса записи, при- этом запрещается прохождение сигналов на вход Чтение ОП 29. Триггер 25 устанавливается в состоя,ние О, как при первоначальном включении устройства, так и при срав нении кодов адресов записи и чтения поступающих с выходов счетчиков 21 и 22. Таким образом, обеспечивается запись информации ЦВМ в ОП 29 блока 9 буферной: памяти, после чего блок 4 связи сЦВМ выдает на его вход 2 сигнал ЗКонец обмена, который, поступая через открытый второй элемент 24 И (сигнал сравнения на выходе схе мы 23 отсутствует), устанавливает в состояние 1 триггер 25 и не проходит на выход 2 блока 9, так как нет разрешающего сигнала на втором входе третьего элемента 28 И. Одновременно снимается сигнал Требование обмена на входе 1 блока 9, тем самым прекращается работа ОП 29 в режиме записи (запрещается прохождение задержанного синхросигнала через первый элемент 19 И). Процесс чтения аналогичен процессу записи и осуществляется по синхро сигналам, поступающим на вход 4 блока 9. При снятии сигнала Требование обмена на входе 1 блока 9 на его выходе 1 сигнал Требование обмена формируется триггером 25, с единично го выхода которого 1 сигнал поступает на вход 1 через первый элемент 27 ШШ. Процесс чтения продолжается до момента сравнения кодов адреса записи (Т-разрядная первая группа входов схемы 23 сравнения) и чтения 4 (Т-разрядная вторая группа входов схемы 23 сравнения). При этом сигнал сравнения устанавливает в состояние О триггер 25 и тем сам.ым снимается сигнал Требование обмена на выходе 1 блока 9 и разрешается прохождение сигнала Конец обмена на выход 2 блока 9. Коммутатор 10 (фиг. 3) предназначен для выбора и электронной коммутации информации и сигналов управления (команд) блоков 6 связи.с терминалами и блока 9 буферной памяти (информация блока 4 связи с ЦВМ) ., При этом первый мультиплексор 30 коммутирует сигналы Требование обмена, второй 31 -.сигналы Конец обмена от терминалов-инициаторов обмена информацией, третий 32 - сигналы Конец обмена от вызванных на обмен информацией терминалов или ЦВМ. Первая группа 33 мультиплексоров 35 обеспечивает выборку информации с информационных вьгходов блоков 6 и 9 - инициаторов обмена информацией и выдает ее на М-разрядную первую группу информационных выходов коммутатора 10. Вторая группа 34 мультиплексоров 35 обеспечивает выборку информации с информационных выходов блоков 6 и 9, вызываемых на обмен информацией, и выдает ее на М-разрядную вторую группу информационных выходов коммутатора 10. (п±1)-разрядные группы входов мультиплексоров 35 соединены с М-разрядной четвертой группой информационных входов и М-разрядной третьей группой информационных входов коммутатора 10, причем на k-e М-разрядные группы мультиплексоры 35 первой 33 и второй 24 групп подаются k-e разряды М-разрядных групп в следующем порядке: на первый вход k-ro мультиплексора 35 k-й разряд первой группы четвертых информационных входов коммутатора 10, на второй вход k-ro мультиплексора 35 k-й разряд второй группы, на Л-вход k-ro мультиплексора 35 k-й разряд л-ой группы, на (Л+1)-вход k-ro мультиплексора 35 k-й разряд М-разрядной третьей группы информационных входов. (л+1)-разрядные группы входов первого мультиплексора 30 соединены с А-первыми входами и входом 2 коммутатора 10, второго 31 и третьего 32

9 ,1

мультиплексоров - с А -вторыми входам и входом 2 коммутатора 10, причем вход 1.1 первой группы управляющих входов коммутатора 10 соединен с входом 1 мультиплексора 30, вход 1.2 - с 2 входом мультиплексора 30, вход 1 k-й - с k-M входом мультиплексора 30, вход 1. Л- с л-тВХОДОМ мультиплексора 30, вход 1 - с ()входом мультиплексора 30, вход 2.1 второй группы управляющих входов коммутатора 10 соединен с входами 1 мультиплексоров 31 и 32, вход 2.2 с 2 входами мультиплексоров 31 и 32, вход 2.k - с К-входами мультиплексоров 31 и 32, вход 2.л - с Л-входами мультиплексоров 31 и 32, вход 2 с (л+1) входами мультиплексоров 31 и 32.

К-разрядные группы управляющих входов мультиплексоров 30, 31 и 35 группы 33 соединены с К-разрядной первой группой информационных входов коммутатора 10 соответственно, а мультиплексоров 32 и 35 группы 34 с К-разрядной второй группой информационных входов коммутатора 10 соответственно.

Счетчик 11 канала предназначен для запоминания поступающего с первой группы информационных выходов коммутатора 10 К-разрядного кода номера запрашиваемого на обмен терминала (канала) по синхросигналам с первого выхода блока 12 управления

Блок 12 управления (фиг. 4) предназначен для формирования синхросигналов, тактирующих работу устройства, сигналов управления в соответствии с двоичными кодами адресов терминалов-инициаторов обмена и терминалов, вызываемых на обмен информацией .

При .включении устройства триггер .37 блока 12 устанавливается в состояние О независимо от наличия на входах 2 и 3 блока 12 сигналов Конец обмена и тем самым разрешает прохождение через элемент 42 И на выход 3 блока 12 синхросигналов задакяцего генератора 40. При поступлении на вход 1 блока 12 сигнала требование обмена триггер 37 устанавливается в состояние 1, запрещает формирование синхросигналов на выходе 3 блока 12 и разрешает дешифрирование К-разрядных кодов адресов терминалов-инициаторов обмена и тер410

миналов, вызьтаемых на обмен информацией дешифраторами 38 и 30 соответственно, выходы которых являются вторым и первьм информационными выходами блока соответственйо.

Выходы дешифратора 39 также заведены на группу элементов 41 ИЛИ для формирования сигнала управления счетчиком 11 канала на выходе 1 блока 12 после каждого срабатьшания дешифратора.

Так как обмен информацией между терминалами и ЦВМ происходит М-разрядными словами, поэтому для обеспечения работы блоков 4 , 6 и 9 частота синхросигналов () на выходе делителя 43 (выход 2 блока 12 управления) связана с частотой импульсов задающего генератора 40 (ffg ) слеующим соотношением

i

ген

Аел- W

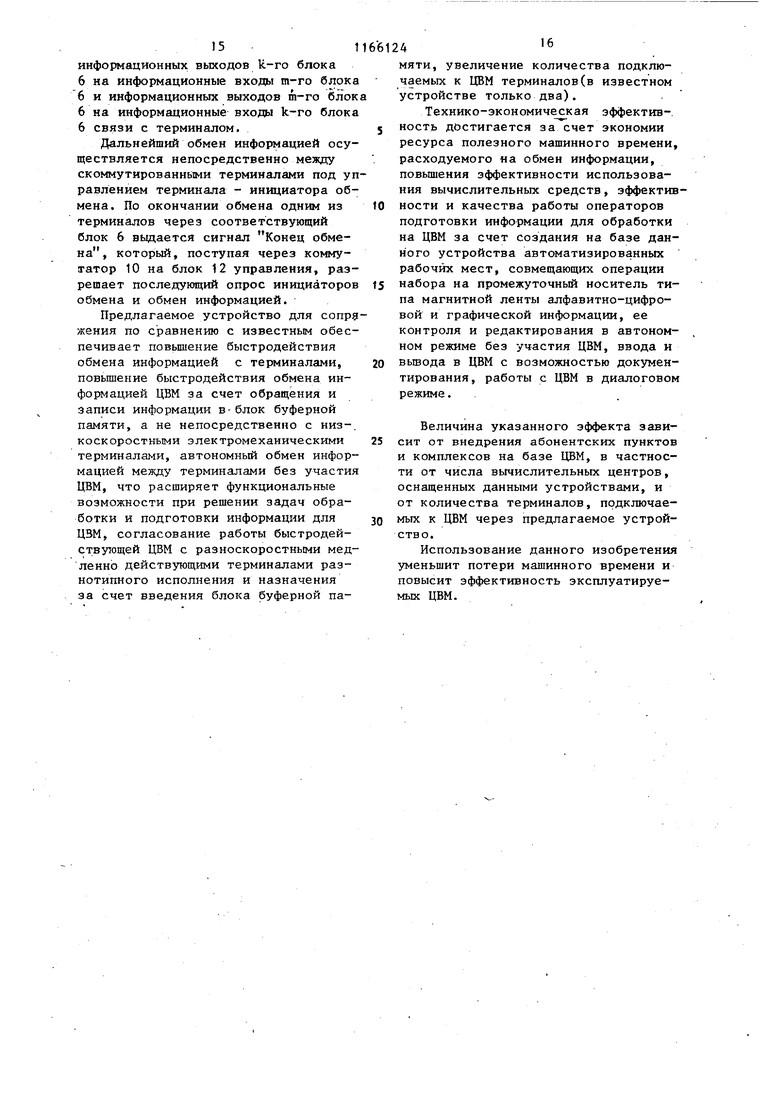

Первый блок 13 элементов И предназначен для приема и коммутации на (А+1) М-разрядных групп своих выходов (на (.) направление в соответствии с кодом адреса терминала или ЦВМ, вызываемых на обмен информацией, поступившим на (+1)-paзpядную группу вторых входов блока) информации терминалов или ЦВМ - инициаторов обмена, поступающей от коммутатора 10 ,ia М-разрядную группу первых входов блока 13,

Второй блок 14 элементов И предназначен для приема и коммутации на (А-«-1) М-разрядных групп своих выходов (на (+1) направление в соответствии с кодом адреса терминала или ЦВМ - инициаторов обмена, поступившим на (л+1)- разрядную группу вторых входов блока) инфврмации терминалов или ЦВМ, вызьгоаемых на обмен, поступающей от коммутатора 10 на М-разрядную группу первых входов блока 14.

Блоки 13 и 14 идентичны и содержат (фиг. 5) по (л+1)-групп 44 элементов И из М-элементов 45 И в каждо группе.

1-й разряд М-разрядной группы первых входов блока 13 (14) соединен с входами 1 первых элементов 45 И каждой из (л + 1)-групп 44, k-й разрядс входами 1 k-x элементов 45 И, М-й разряд - с входами 1 М-х элементов 45 И 1-й разряд (л-t-1)-разрядной груп11 1

пы вторых входов блока 13 (14) соединен с входами 2 всех элементов 45 первой группы 44 элементов И, k-й разряд - с входами 2 всех элементов И 45 lc-й группы 44 элементов И, (А 4-1)-и разряд - с входами 2 всех элементов 45 И, (А+1) - группы 44 элементов И.

Блок 15 элементов ИЛИ (фиг. 6) предназначен для поразрядной сборки информации с выходов блоков 13 и 14 элементов И, поступакндих на (А + 1) М-разрядные группы первых и вторых входов блока 15, выдачи ее на (Л+1) М-разрядную группу выходов блока 15 и содержит(+1)-групп 46 элементов из М-элементов 47 ИЛИ. :

Устройство для сопряжения обеспечивает пять режимов обмена информацией: первьй режим записи информации на k-й терминал по инициативе ЦВМ, второй режим записи из ЦВМ информаци на k-й терминал по его инициативе (требованию), третий режим чтения информации с k-готерминала, по инициативе ЦВМ, четвертый режим.чтения ЦВМ информации с k-ro терминала по его инициативе (требованию), пятый режим обмена информацией между 1с-м и м-м терминалами без участия ЦВМ.

При этом инициатором обмена инфор мацией может быть любой терминал, кроме электромеханических (например алфавитно-цифровые печатающие устрой дтва).

Начало любого перечисленного режи.ма работы обеспечивается только при поступлении от ЦВМ или терминалов инициаторов обмена информацией сигнала Требование обмена (его кода по каналам связи).При отсутствии сигналов Требование обмена устройство для сопряжения работает следующим образом.

Счетчик 8 терминала по синхросигналам с выхода 3 блока 12 управления формирует для коммутатора 10 и блока 12 на свйих выходах К-разрядны коды номеров инициаторов обмена, в соответствии с которыми коммутатор 10 обеспечивает коммутацию.и прохождение сигналов с выходов требования обмена блоков 9 и 6 на вход 1 блока 12 управления, который анализирует наличие сигнала Требование обмена.

При отсутствии сигнала Требовани обмена от инициаторов обмена цикл работы повторяется. При наличии сиг12

24

нала Требование обмена блок 12 фиксирует его и прекращает вьадачу синхросигналов на счетный вход счетчика 8 терминала, который запоминает код номера инициатора обмена, сигнал Требование обмена которого обрабатвается.

Приоритет ЦВМ среди инициаторов обмена обеспечивается сигналом Требование обмена с блока 4, который через элемент 7 И сбрасывает счетчик 8 в состояние О и на выходе его формируется код номера 0-0 ЦВМ. .

В первом режиме запис информации на k-й терминал по инициативе ЦВМ устройство работает следующим образом.

По сигналу Требование обмена блока 4 связи с ЦВМ блоком 9 буферной памяти формируется такой же сигнал, который через коммутатор 10 поступает на блок 12 управления, где фиксируется. При этом последутощий опрос инициаторов обмена прекращается.

Одновременно с сигналом Требование обмена ЦВМ через блок 4 вьщает. информацию с, кодом номера вызьшаемого терминала в блоке 9. После окончания выдачи информации формируется сигнал Конец обмена, который фиксируется в :блоке 9.

По сигналу Конец обмена блок 9 буферной памяти начинает автономный обмен полученной от ЦВМ информации с вызванным в соответствии с поступившим кодом номера на обмен к-м терминалом. Код номера запоминается счетчиком 11 канала по синхросигналу блока 12 и хранится до завершения обмена информацией между блоком 9 и выбранным k-M терминалом. Информация с блока 9 поступает через коммутатор 10 на первые входы первого, блока 13 элементов И, на вторые входы которого с блока 12 управления поступают позиционные коды номеров вызванных на обмен терминалов. С выходов блока 13 информация поступает через блок 15 ИЛИ на информационные входы блока 6 выбранного терминала.

По окончании выдачи информации со скоростью работы вызванного на обмен терминала блок 9 буферной памяти формирует сигнал Конец обмена который разрешает последующий опрос инициаторов обмена.

Таким образом, обеспечивается, обмен информации ЦВМ с k-м терминалом через буферную память блока 9 и время обмена в этом случае зависит только от быстродействия ЦВМ и не s зависит от низкой скорости обработки информации электромеханическими терминалами.

Во втором режиме записи из ЦВМ информации на 1с-й терминал по его 10 инициативе (требованию) устройство работает следующим образом.

Терминал- инициатор обмена через соответствующий блок 6 связи выстав ляет сигнал Требование обмена, 15 который с выхода требования обмена соответствующего блока.6 поступает через коммутатор 10 на блок 12 управления, где фиксируется и запре.щает дальнейший опрос инициаторов обмена. 20 Одновременно выставляется на информационных выходах соответствующего блока 6 код номера ЦВМ (О - О), который поступает через коммутатор 10 на счетчик 11 и далее на блок 12 25 управления.

Таким образсж, обеспечивается коммутация выходов U-ro блока 6 связи с терминалом на информационные входы блока 4 связ с ЦВМ с однодре- 30 менной передачей признаков требуемой информации, в соответствии с которыми -ЦВМ формирует сигнал Требование обмена и выдает через блок 9 буфер- . ной памяти в изложенном порядке на 35 k-й терминал - инициатор обмена информацией с ЦВМ требуемую информацию.

В третьем режиме чтения информации с U-ro терминала по инициативе ЦВМ устройство работает следующим 40 образом.

Аналогично первому режиму ЦВМ передает через блок 4 в блок 9 код номера вызываемого терминала и блок сигналов с признаками требуемой для 45 вьщачи информации выставляет сигнал Конец обмена и переходит к рещению . других задач обработки информации. Блок 9 буферной пам1ти передает командную информацию на вь1зываемый -й 50 терминал. Цосле заверщения подготовки затребованной информации данный терминал выставляет сигнал Требование обмена с ЦВМ и начинает выдачу информации на ЦВМ, по окончании 55 вьщачи которой терминал выставляет сигнал Конец обмена, и разрешает последующий опрос инициаторов обмена.

Работа устройства в четвертом режиме чтения ЦВМ информации с -го терминала по его инициативе аналогична второй части работы устройства в третьем режиме чтения информации с k-ro терминала по инициативе ЦВМ.

В пятом режиме обмена информацией между k-M и т-м терминалами без участия ЦВМ устройство работает следующим образом. . ,

При поступлении по К-му каналу 2 на соответствующий блок 6 связи с терминалом информации с кодами Требование обмена и номера вызьшаемого т-го терминала блок 6 формирует для коммутатора 10 на своем выходе сигнал Требование обмена, а на информагионных выходах код номера вызываемого т-го терминала.

. В соответствии с данной информацией коммутатор 10 обеспечивает выборку информации с информационных выходов т-го блока 6 на свою вторую группу инфор ационнък выходов и выдачу ее на входы 1 второго блока 14 элементов И.

При этом на выходах счетчика 8 терминала фиксируется код ломера k-ro терминала - инициатора обмена, который поступает на вторые группы информационных входов коммутатора 10 1 блока 12 управления.

В соответствии с поступивщим кодом инициатора обмена коммутатор 10 обеспечивает выборку информациис информационных выходов k-ro блока 6 связи с терминалом на свою лервую группу информационных выходов, вьщает ее на входы 1 первого блока 13 элементов И и К-й разрядный код номера канала на счетчик 11, который запоминает его и вьщает на .первые группы информационных входов коммутатора 10 и блока 12 управления.

Блок 12 управления в. соответствии с кодами номеров k-ro и т-го терминалов, поступающими соответственно, на вторую групцу информационных входов от счетчика 3-й первую группу информационных входов от счетчика 11, формирует на второй и первой группах информационных выходов позиционные ко/цл т-го и k-ro терминалов соответственно .

Данные сигналы, поступая на входы 2 первого 13 и второго 14 блоков элементов И, резрешают вьщачу через блок 15 элементов ИЛИ информации с

15П

информационных выходов k-ro блока 6 на информационные входы т-го блока 6 и информационных выходов т-го блок 6 на информационные входы k-ro блока 6 связи с терминалом.

Дальнейший обмен информацией осуществляется непосредственно между скоммутированньми терминалами под управлением терминала - инициатора обмена. По окончании обмена одним из терминалов через соответствующий блок 6 выдается сигнал Конец обмена, который, поступая через коммутатор 10 на блок 12 управления, разрешает последующий опрос инициаторов обмена и обмен информацией.

Предлагаемое устройство для сопрджения по сравнению с известным обеспечивает повышение быстродействия обмена информацией с терминалами, повышение быстродействия обмена информацией ЦВМ за счет обращения и записи информации в-блок буферной памяти, а не непосредственно с низ-, коскоростными электромеханическими терминалами, автономный обмен информацией между терминалами без участия ЦВМ, что расширяет функциональные возможности при решении задач обработки и подготовки информации для ЦЗМ, согласование работы быстродействугощей ЦВМ с разноскоростными медленно действующими терминалами разнотипного исполнения и назначения за счет введения блока буферной па16

мяти, увеличение количества подключаемых к ЦВМ терминалов(в известном устройстве только два).

Технико-экономическая эффективность достигается за счет экономии ресурса полезного машинного времени, расходуемого на обмен информации, повьш1ения эффективности использования вычислительных средств, эффективности и качества работы операторов подготовки информации для обработки на ЦВМ за счет создания на базе данного устройства автоматизированных рабочих мест, совмещающих операции набора на промежуточный носитель типа магнитной ленты алфавитно-цифровой и графической информации, ее контроля и редактирования в автономном режиме без участия ЦВМ, ввода и вьюода в ЦВМ с возможностью документирования, работы с ЦВМ в диалоговом режиме.

Величина указанного эффекта зависит от внедрения абонентских пунктов и комплексов на базе ЦВМ, в частности от числа вычислительных центров, оснащенных данными устройствами, и от количества терминалов, подключаемых к ЦВМ через предлагаемое устройство.

Использование данного изобретения уменьшит потери машинного времени и повысит эффективность эксплуатируемых ЦВМ.

w

55

(pat.J

Фиг.4

uz.S

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения цифровой вычис-лиТЕльНОй МАшиНы C ВидЕОТЕРМиНАлОМ | 1979 |

|

SU840872A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-07-07—Публикация

1984-01-02—Подача