2. Корректор по п.1, отличающийся тем, что блок управления содержит последовательно соединенные генератор, вход которог является первым входом блока управления, первый счетчик адресов, второй счетчик адресов, первый коммутатор, блок памяти номера цикла и элемент И, а также последовательно соединенные второй коммутатор, элемент памяти, блок вычитания и интегратор, выход которого подключен к объединенным первому входу второго (коммутатора и второму входу первого коммутатора, кроме того первый вы66318

ход второго счетчика адресов подключен к второму входу элемента И, третий вход которого соединен с вторым входом блока памяти цикла и вторым выходом второго счетчика адресов, при этом объединенные входы блока вычитания и второго коммутатора являются вторым входом блока управлени5 первым выходом которого является третий выход второго адресов, вторым выходом блока управления является выход первого счетчика адресов, а третьим выходом блока управления - выход элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Адаптивный корректор | 1989 |

|

SU1688418A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Адаптивный корректор | 1987 |

|

SU1417197A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1988 |

|

SU1619414A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1989 |

|

SU1741274A2 |

| ЦИФРОВОЙ АДАПТИВНЫЙ ПРИЕМНИК ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2039416C1 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| Цифровой фильтр | 1988 |

|

SU1569957A1 |

| Способ компенсации фазовых искажений в многоканальных системах аналого-цифрового преобразования сигналов и устройство для его реализации | 2019 |

|

RU2723566C1 |

1. АДАПТИВНЫЙ КОРРЕКТОР КАНАЛА СВЯЗИ, содержащий коммутатор и решающий блок, отличающий.с я тем, что, с целью повышения точности коррекции, в него введены блок памяти выборок, вход которого является входом устройства, блок умножения, блок памяти, сумматор, блок промеж точной памяти, блок памяти сумм и блок управления, первый вход которого является входом для подачи сигнала тактовой частоты, при этом выход блока, памяти выборок через последовательно соединенные коммутатор, блок умножения, сумматор и блок памяти сумм подключен к другому входу коммутатора, управляющий вход которого соединен с первым выходом блока управления, второй выход которого подключен к обг единенным вторым входам блока памяти, выборок, блока памяти сумм, блока памяти и сумматора, выход которого подключен к первому входу блока промежуточной памяти и входу решающего блока, выход которого подключен к другому входу блоха (Л управления, третий выход которого подключен к второму входу блока промежуточной памяти, выход которого является выходом корректора, кроме того выход блока памяти подключен к второму входу блока умножения. о о:) со 00

1

Изобретение относится к области электросвязи и другим областям, связанным с передачей сигналов данных по каналам связи, и предназначено для коррекции частотных характеристик каналов связи.

Целью изобретения является повышение точности коррекции частотных характеристик каналов связи.

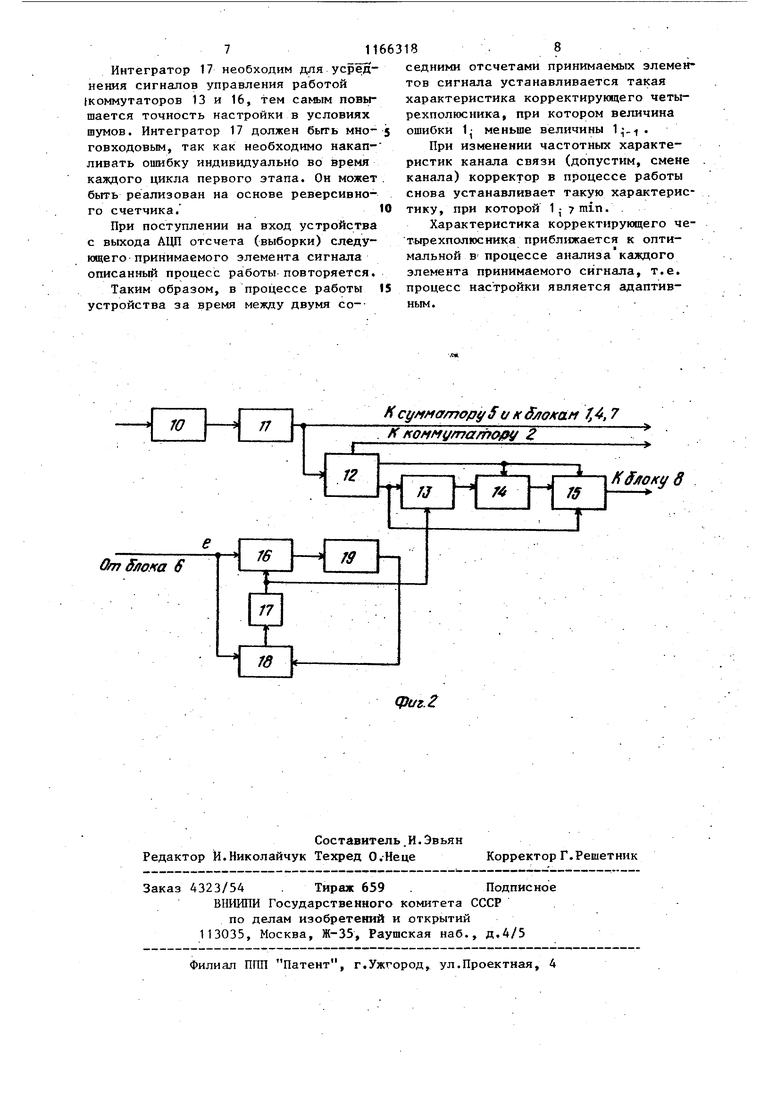

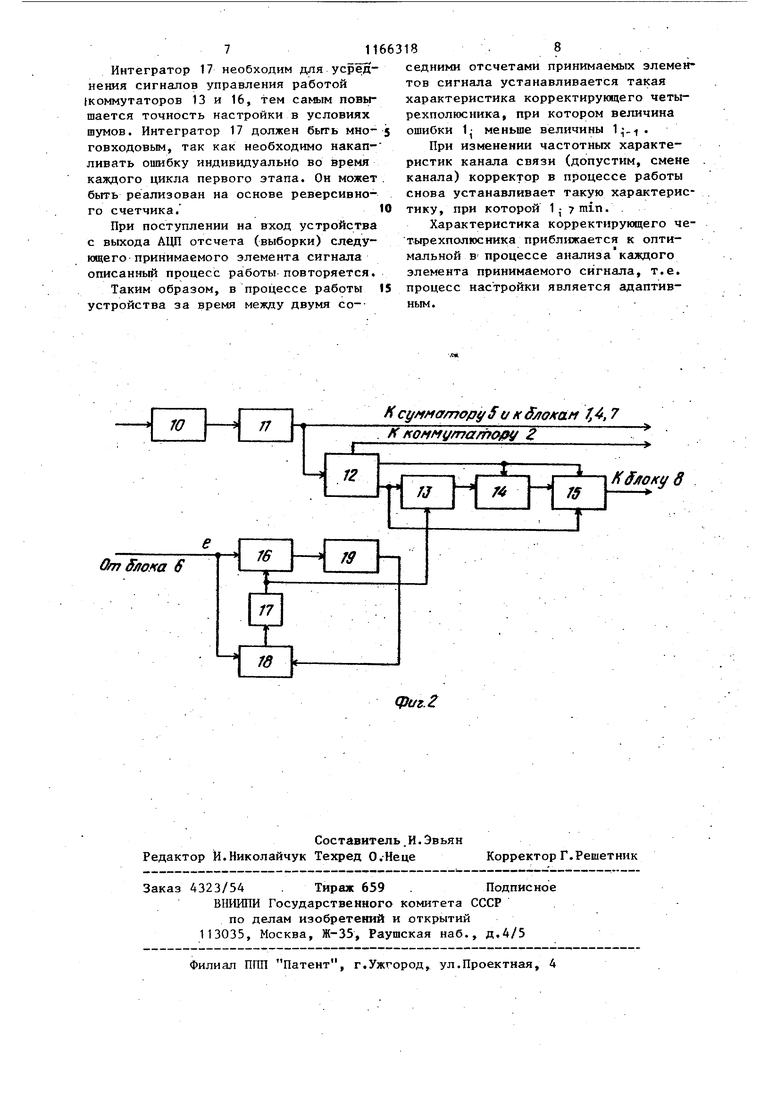

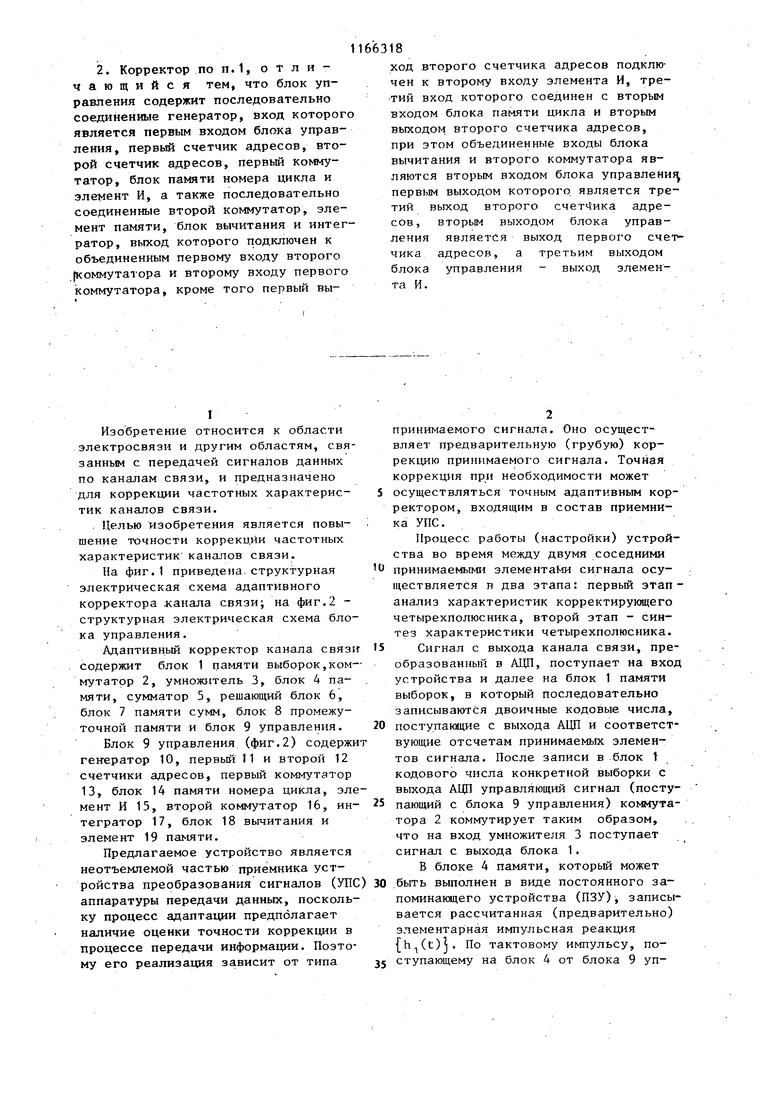

На фиг.1 приведена, структурная электрическая схема адаптивного корректора .канала связи; на фиг.2 структурная электрическая схема блока управления.

Адаптивный корректор канала связи содержит блок 1 памяти выборок,коммутатор 2, умножитель 3, блок 4 памяти, сумматор 5, решающий блок 6, блок 7 памяти сумм, блок 8 промежуточной памяти и блок 9 управления.

Блок 9 управления (фиг.2) содержи генератор 10, первый 11 и второй 12 счетчики адресов, первый коммутатор 13, блок 14 памяти номера цикла, элемент И 15, второй коммутатор 16, интегратор 17, блок 18 вычитания и элемент 19 памяти.

Предлагаемое устройство является неотъемлемой частью приемника устройства преобразования сигналов (УПС аппаратуры передачи данных, поскольку процесс адаптахщи предполагает наличие оценки точности коррекции в процессе передачи информации. Поэтому его реализация зависит от типа

принимаемого сигнала. Оно осуществляет предварительную (грубую) коррекцию принимаемого сигнала. Точная коррекция при необходимости может осуществляться точным адаптивным корректором, входящим в состав приемника УПС.

Процесс работы (настройки) устройства во время между двумя соседними принимаемыми элементайи сигнала осуществляется в два этапа: первый этапанализ характеристик корректирующего четырехполюсника, второй этап - синтез характеристики четырехполюсника.

Сигнал с выхода канала связи, преобразованный в АЦП, поступает на вход устройства и далее на блок 1 памяти выборок, в который последовательно записываются двоичные кодовые числа, поступающие с выхода АЦП и соответствующие отсчетам принимаемых элементов сигнала. После записи в блок t кодового числа конкретной выборки с выхода АЦП управляющий сигнал (поступающий с блока 9 управления) коьмутатора 2 коммутирует таким образом, что на вход умножителя 3 поступает сигнал с выхода блока 1.

В блоке 4 памяти, который может быть выполнен в виде постоянного запоминакщего устройства (ПЗУ), записывается рассчитанная (предварительно) элементарная импульсная реакция {h(t)J. По тактовому импульсу, поступающему на блок 4 от блока 9 управления, на второй вход умножителя 3 подается кодовое число, соответствующее одному отсчету элементарной импульсной реакции, которое в блоке 3 перемножается с двоичным кодовым числом, соответствующим выборке входного сигнала, записанной в блоке 1. Полученное произведение записывается в сумматор 5. В следующем такте работы блока 9 на вход умножителя 3 от блока 4 поступает сигнал, соответствующий второму отсчету элементарной импульсной реакции, а от блока 1 сигнал, соответствующий следующей выборке. Полученное проиэведение с выхода умножителя 3 поступает на сумматор 5, где алгебраически суммируется с результатом, записанным в сумматоре 5 в предьщущем такте работы блока 9. Этот процесс продолжается до тех пор, пока в сзгмматоре 5 не будет записана сумма произведений всех отсчетов элементарной импульсной реакции на выборки входного сигнала, соответствующая реализации выражения

g(t)X S(t-n)h(n),

где {h:,{n) - дискретное представленив (отсчеты) элементарной импульсной реакции (длина импульсной реакци равна МТ, Т - период дискретизации), S(t) - сигнал на входе четьфехполюсника.

Описанный процесс вычисления свертки (умножение с последующим суммированием) в дальнейшем назьгоается циклом.

Таким образом, после проведения рассмотренного цикла на выходе сум атора 5 формируется сигнал, соответствующий входному сигналу, откорректированному корректирукнцим четырехполюсником с элементарной импульсной характеристикой. Этот сигнал записывается в блок 7 и анализируется в решакяцем блоке 6, в котором осуществляется оценка сигнала на выходе сумматорй 5 и вычисляется отклонение этого сигнала от его оценки (эталона) т.е. сигнал ошибки 1 . Сигнал ошибки поступает на вход блока 9, где на основании анализа величины 1 может выработаться сигнал управления, по которому коммутатор 2 подключает на вход умножителя 3 сигнал с выхода блока 7.

Затем повторяется описанный цикл последовательного перемножения и суммирования всех отсчетов элементарной импульсной реакции (такое же. число отсчетов) предварительно откорректированного сигнала, поступающего с выхода блока 7.

В результате последовательного повторения описанных циклов настройки в блоке 9 запоминается номер цикла при котором вычисленная величина сигнала ошибки t, усредненная в блоке 9, минимальна. В качестве критерия настройки (11) можно использовать как среднеквадратичное, так и абсолютное отклонение откорректированного сигнала от эталона. Интеграция (усреднение) необходима для обеспечения устойчивости формирования сигналов управления работой корректора и оптимального выбора числа циклов на основании анализа совокупности последовательности {l{} , вырабатываемой по результатам каждого цикла работы. На этом первый этап работы заканчивается.

Во время второго этапа работы цик-лы последовательного перемножения и су(Ф1ировання повторяются, начиная с первого. После проведения цикла настройки, номер которого соответствует запомненному в блоке 9 (при котором величина ошибки 1,- минимальна) процесс коррекции заканчивается. В блоке 9 вьфабатывается сигнал, по которому двоичное кодовое число, соответствующее оптимально откорректированному сигналу, переписывается с выхода cytotaTopa 5 в блок 8, с выхода которого этот сигнал поступает на выход устройства и далее в приемник УПС.

Формирование сигналов управления в блоке 9 осуществляется следующим образом.

Высокочастотная импульсная последовательность, вырабатываемая генератором 10 (г.2), входяпщм в состав блока 9, поступает на первый счетчик 11 адресов. Причем на вход счетчика 11 поступает и myльcнaя последовательность только после прихода от АЦП на первый вход блока 9 импульса, соответствующего концу процесса преобразования в АЦП принимаемого элемента сигнала. Этот сигнал обычно вы-рабат.ывается в АЦП. 51 На выходе первого счетчика 11 последовательно фop вipyютcя двоичные кодовые числа, соответствующие адресам, по которым в блоке 4 записаны отсчеты элементарной импульсной реакции, а в блоке 1 записано также количество выборок принимаемых элементов сигнала. Эти же сигналы используются для записи промежуточных сумм в сумматоре 5 в соответствии с описанным алгоритмом работы устройст ва. Результирукщая сумма после .первого цикла настройки записывается с выхода сз мматора 5 в блок 8 по адресу, формируемому на выходе первого счетчика 11. Первый 11 и второй 12 счетчики включены последовательно. После анализа сигнала, сформированного в результате первого цикла настройки, на выходе решающего блока 6 Бырабатьгоается сигнал ошибки , который поступает на второй вход блока 9 управления и далее на блок 18 и второй коммутатор 16. Последний во время первого цикла включен таким образом, что сигнал t с второго входа блока управления записывается непосредственно в элемент 19 памяти. После проведения первого цикла на стройки начинается второй цикл. При этом на третьем выходе второго счетчика 12 формируется сигнал управления, по которому коммутатор 2 подклю чает на вход умножителя 3 сигнал с выхода блока 7. Затем проводится вто рой цикл настройки аналогично первому, за исключением того, что отсчеты элементарной импульсной реакции, записанные в блоке 4, последовательно умножаются на результат операции пер вого цикла, записанный, в блоке 7. В результате анализа откорректированно го во втором дакле сигнала на выходе решающего блока 6 сформировано новое значение ошибки 1 1л, которое поступае на второй коммутатор 16 и блок 18 В последнем осуществляетс вычитания, 1. и 1 -Т.е. вычисление сравнение . их разности. При этом величина 1 по ступает на блок 18 вычитания с выход элемента 19 памяти. В случае 1-71 на вход интегратора 17 с выхода блок 18поступает сигнал, соответствующий условию,при которомна вход элементаir; 19памяти величину 1, не следует записывать. В случае 1, на вход интегратора 17.с выхода блока 18 по8ступает сигнал, соответствующий условию, при котором на вход элемента 19 памяти следует записать величину j, поскольку при этом принимаемый сигнал лучше откорректирован. С выхода интегратора 17 сигнал управления поступает на первый коммутатор 16, на второй коммутатор 13, который подключен на вход блока 14, поступает сигнал от счетчика 12. Таким образом, в элементе 19 памяти записывается сигнал ошибки 1, а в блоке 14 номер цикла, при котором 1; 1Затем проводится третий цикл настройки. После него осуществляется формирование сигналов управления работой первого 13 и второго 16 коммутаторов, но при этом проводится сравнение величин 1- и 1j, если после второго цикла выполнялось условие 1.j7l,j, или величин 1 и 1, если после второго цикла выполнялось условие Описанный процесс повторяется для всех циклов первого этапа. После окончания первого этапа в блоке 14 записано кодовое число, соответствующее номеру цикла, прк котором 1. min. Во все время первого этапа от счетчика 12 на первый вход элемента И 15 поступает запрещакидий сигнал. Затем начинается второй этап настройки. Он осуществляется аналогично первому этапу, однако в блок 14 новые номера цикла не записываются. В случае совпадения адреса, при котором на первом этапе выполняется условие 1.min, коды номера цикла на выходах счетчика 12 и блока 14 совпадают. При этом на выходе элемента И 15 появляется сигнал, соответствукиций этому совпадению, поскольку во время этого этапа с выхода счетчика 12 на первый вход элемента И 15 поступает сигнал, разрешающий Сравнение. Управлянодий сигнал, соответствующий минимальной ошибке 1.; , поступает с выхода блока 9 управления на блок 8. По этому сигналу в блок 8 с выхода сумматора 5 записывается сигнал, соответствуклций условию . Откорректированный сигнал поступает на выход устройства. Осуществление описанного итеративного процесса обеспечивает синтез оптимальной характеристики корректирующего четырехполюсника.

Интегратор 17 необходим для усреднения сигналов управления работой (коммутаторов 13 и 16, тем самым повышается точность настройки в условиях шумов. Интегратор 17 должен быть мнеговходовым, так как необходимо накапливать ошибку индивидуально во время каждого цикла первого этапа. Он может быть реализован на основе реверсивного счетчика.

При поступлении на вход устройства с выхода АЦП отсчета (выборки) следующего принимаемого элемента сигнала описанный процесс работы повторяется.

Таким образом, в процессе работы устройства за время между двумя соседними отсчетами принимаемых элементов сигнала устанавливается такая характеристика корректирующего четырехполюсника, при котором величина ошибки 1 меньше величины .

При изменении частотных характеристик канала связи (допустим, смене канала) корректор в процессе работы снова устанавливает такую характеристику, при которой 1- 7niin.

Характеристика корректирующего четырехполюсника приближается к оптимальной в процессе анализакаждого элемента принимаемого сигнала, т.е. процесс настройки является адаптивным.

| Данилов B.C | |||

| и др | |||

| Устройства преобразования сигналов передачи данных | |||

| М., Связь, 1979, с | |||

| Домовый номерной фонарь, служащий одновременно для указания названия улицы и номера дома и для освещения прилежащего участка улицы | 1917 |

|

SU93A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Беркович Д.А., Лев А.Ю | |||

| Система коррекции стандартных каналов локальной частоты с автоматической настройкой | |||

| М., Связь, 1972, с | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1985-07-07—Публикация

1983-12-21—Подача