(21)4258196/24-09

(22)08.06.87

(46) 15.08.88. Бюл. 30 (72) А.М.Боград, Б.С.Данилов, ;Л.Г.Израильсон и 0.И Сидорова ( 53) 621.395.662 (088.,8)

(56)Ahuja BfK, etal. А Sampled analog MOSLSI agaptive, Filtes IEEE Transactions on communications Vol Com 27 № 2, 1979, p. 406-412, figo3.

(54) АДАПТИВНЫЙ КОРРЕКТОР

(57)Изобретение относится к электросвязи. Цель изобретения - повышение точности коррекции. Корректор содержит АЦП 1 и 6, ключ 3, блок памяти (БП) 4 выборок, перемножающий ЦАП 5,

сумматор 7, решающий блок 8, БП 10 коэффициентов5 ЦАП 11, формирователь 12 веса коэффициента, коммутатор 13 и блок 14 управленияо Корректор имеет два цикла работы. В первом цикле выполняется операция формирования откорректированного сигнала, а во втором цикле - операция измерения (подстройки) коэффициентов передачи регуляторов отводов корректора.В устройстве осзпцествляется адаптивная коррекция принимаемого сигнала с использованием среднеквадратичного алгоритма настройки. Цель достигается за счет учета величины регулируемого коэффициента передачи. I э.п. ф-лы, 5 ил.

5S

(Л

i Изобретение относится к электро связи и другим областям, связанным с приемом модулированных сигналов данных и предназначено для коррекции межсимвольной интерференции (МСЙ), принимаемого сигнала, обусловленной неидеальностью частотных характеристик каналов связи.

Целью изобретения является новы- шение точности коррекции.

На фиго изображена структурная электрическая схема адаптивного кор ;ректора| на фиг„2 - структурная схе- ма сумматора на фиг„3 « структурная jсхема блока управления; на фиг.А - диаграммы поясняющие работу блока iуправления; на фиг,5 - структурная I схема решакяцего блока Адаптивный корректор содержит i последовательно соединенные первый : аналого-цифровой преобразователь (АЦП) 1, вход которого является вхо дом 2 устройства, клмч 3, блок 4 па- мяти выборок, перемножающий цифре- аналоговый преобразователь (ДАЛ) 5 второй АЦП 6, сумматор 7, решающий блок 8, первый выход которого является выходом 9 устройства, блок 10 памяти коэффициентов, ДАЛ 11, форми- рователь 12 веса коэффициента, комму татор 13, блок 14 управления о

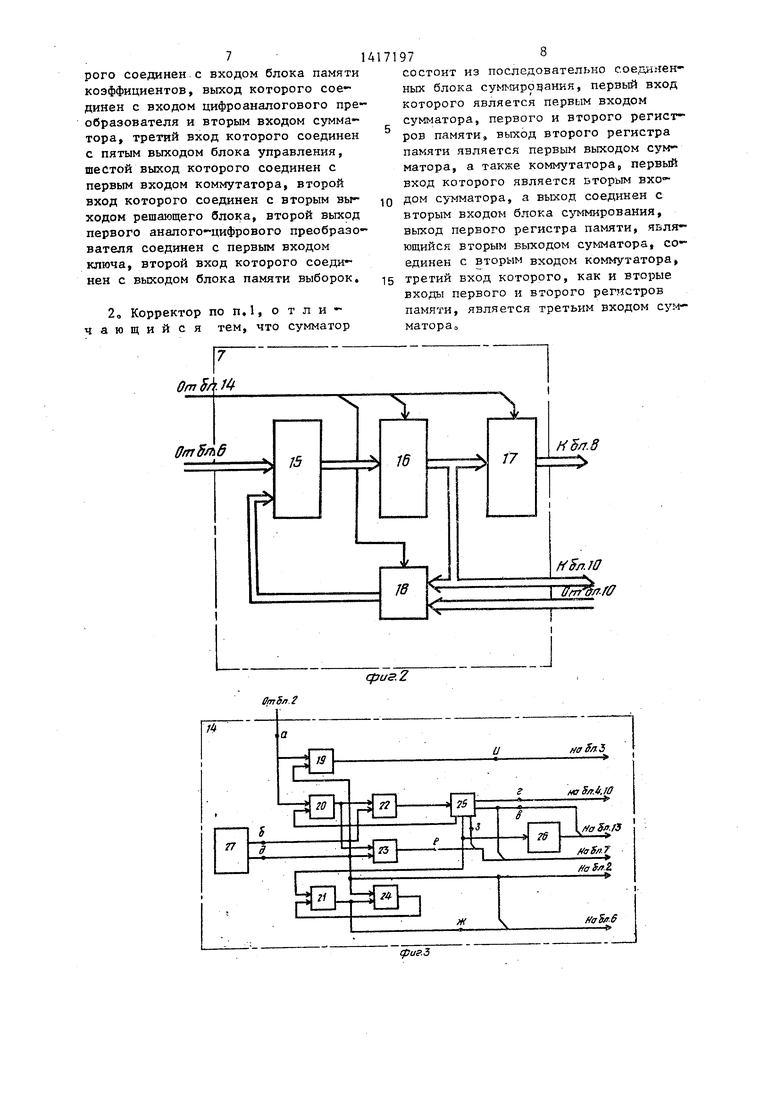

Сумматор 7 (фиг,2) содержит блок 15 сумътрования, первый 16 и второй 17 регистры памяти коммутатор 18о

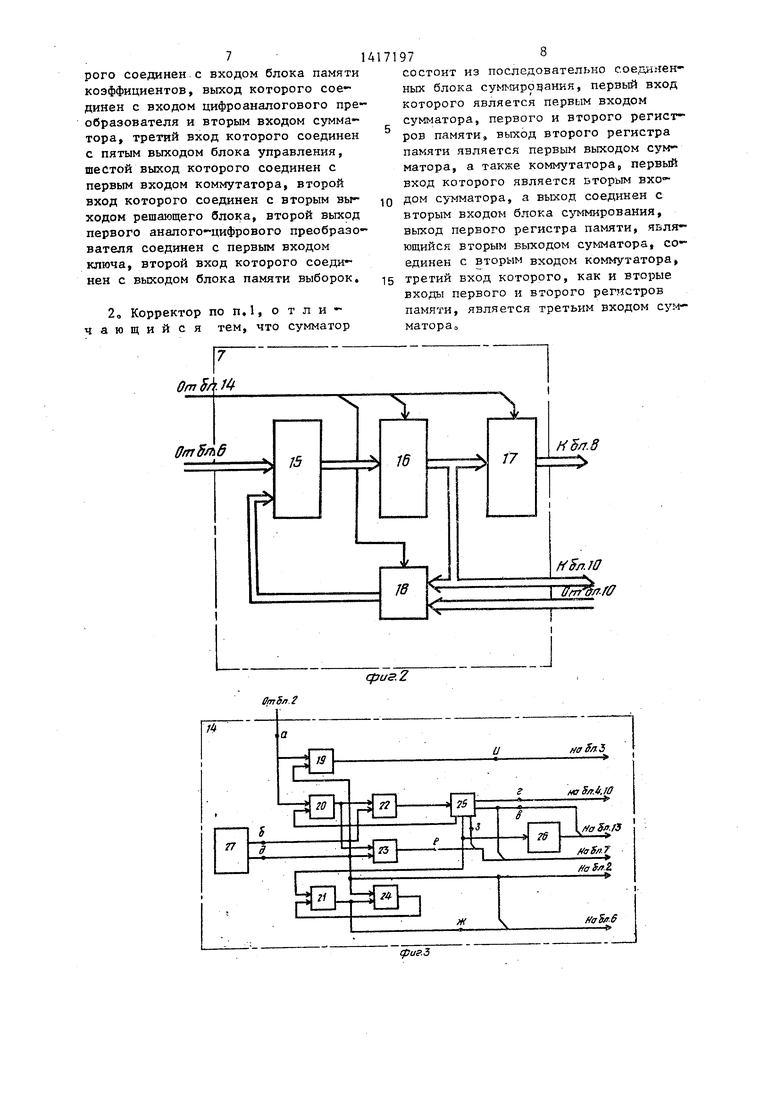

Блок 4 управления (фиГоЗ) содержит первый 19, второй 20 и третий 21 триггеры, первый 22, второй 23 и третий 24 элементы И, делитель 25, блок 26 элементов И и генератор 27,

Решающий блок 8 (фиг.5) содержит элемент ИЛИ 28 и блок 29 вычитания

Адаптивньш корректор работает следующим образом,

В течение времени равного перио- ду следования сигналов на входе 2, в адаптивном корректоре выполняются две операции: формирование откорректированного сигнала (первый цикл работы) и изменение (подстройка) коэффициентов передачи регуляторов отводов предлагаемого корректора (второй цикл работы).

В первом цикле работы аналоговый сигнал с выхода 2 устройства поступа ет на первый АЦП 1 о Сигнал выборки в виде п-разрядного кодового слова записьшается через открытый ключ 3 в блок 4 памяти выборок. После запи

Q

5 0 5 0

5

0

5

си выборки в блок 4 памяти выборок ключ 3 по сигналу, поступающему от блока 14 управления, отключает выход первого АЦЦ 1 от входа блока 4 памяти выборок и подключает выход блока 4 памяти выборок на его вход По сигналам, поступающим от блока 14 управления , с выходов блоков 4 и 10 памяти выборок и ко:; ффициентов выписываются выборки и коэффициенты соответствующих отводов предлагаемого корректора для их взаимного перемножения, которое осуществляется следующим образом.

В блоках 4 и 12 выборки и коэффици енты записаны в виде многоразрядных кодовых чисел в цифровой форме Однако при перемножении таких чисел трудно учесть вес каждого отвода, , его место по отношению к центральному отводу, что уменьшает точность настройкио Кроме того, перемножение выборок и коэффициентов, представленных в цифровой форме, при использовании умножителя существенно увеличива- ет мощность потребления, особенно в устройствах, осуществляющих адаптивную коррекцию сигналов при высокоскоростной передаче информации. Поэтому в предлагаемом устройстве осуществляется аналоговое перемножение выборок и коэффициентов. Для этого сигналы с выхода блока 4 памяти выборок поступают на первый вход которого поступают сигналы с выхода блока 10 памяти коэффициентов, преобразованные в аналоговую форму посредством ДАП П„ Таким образом, перемножение соответствующих вы- борок и коэффициентов осуществляется в перемножающем ЦАП 5. Изменение веса требуемых коэффициентов осуществляется посредством формирователя 12 веса коэффициента, представляющего собой регулируемый усилитель, коэффициент передачи которого изменя- . ется в зависимости от кодовой комбинации, подаваемой на его управляющий вход. По сигналу управления, поступающему от блока 14 управления в первом цикле работы на выход коммутатора 13 (на вход формирователя 12), поступают кодовые сигналы, соответствукхцие выбранным областям номеров коэффициентов передачи регуляторов корректора При этом изменяется вес коэффициента, т обо уменьшается динамический диапазон изменения (по мере удаления от

3,4

центрального), что эквивалентно повышению точности регулировки коэффициентов.

Аналоговый сигнал с выхода перемн жакицего ДАЛ 5 преобраэуется в цифровую форму во втором АЦП $ и далее поступает на сумматор 7, в котором осуществляется суммирование с накопле- /наем произведений выборок на коэффициенты передачи регуляторов корректора, т.е, формирование откорректированного сигнала. Откорректированный сигнал с выхода сумматора 7 поступает на решающий блок 8, в котором вырабатываются эталонные сигналы, поступающие на выход 9 устройства, а также сигналы ошибки

Предпагаемое устройство осуществляет адаптивную коррекцию принимаемого сигнала с использованием среднеквадратичного алгоритма настройкио Однако возможно применение и других алгоритмов настройки«

Во втором {досле работы по сигналу формируемому в блоке 14 управления, коммутатор 13 подключает на вход формирователя 12 веса коэффициента сигнал ошибки, формируемый в решающем блоке 8, В соответствии со среднеквадратичным алгоритмом наст ройки изменение коэффициентов пере дачи (с точностью до постоянной) равно произведению соответствунщей выборки на ошибку. Однако при этом не увеличивается величина подстраивав емого коэффициента передачи, что снижает точность настройки. В предлагаемом адаптивном корректоре во втором цикле работы (во время настройки коэффициентов) в формирователе 12 перемножаются сигналы, соответствующие - ошибке и подстраиваемому коэффициенту, т.е. при формировании сигналов подстройки коэффи1щентЬв учитгывает- ся величина подстраиваемого коэффициента. Перемножение сигнала выборки и сигнала с выхода формирователя 12 веса коэффициента осуществляется в перемножанщем ЦАП 5. Изменение величины коэффициента передачи подстраг иваемого отвода осуществляется пос- редством сумматора 7, на второй вход которого поступает сигнал с выхода блока 10 памяти коэффициентов.

Повышение точности коррекции эа счет учета величины регулируемого коэффициента передачи можно подтвердить следующим образом.

7197

Алгоритм подстройки коэффициента передачи С -в ш-й,тактовый момент описывается вьфажением

,

Cjm-H)C,(m) l-otC,(m)li.Y;., (О

где 1; - величина ошибки на i-м так-

те; .Q Yf - входной сигнал}

oi «- постоянная адаптация. Можно показать, что дисперсия D отклонения Сц от желаемого значения при алгоритме (1) определяется сле- g дуняцим образом

D.. S cJo PoCl-C..),

(2)

где EJJ - мощность полезного сигнала. При этом минимум дисперсии D обеспечивается при условии м

-Гвк Д -oi p zv

.

обГр;(1 -z:c:),

(3)

СсО

где N - число отводов корректора.

Традиционный среднеквадратичный алгоритм настройки описьшается выра- 30 жением

С(т+О C,(m)-oi.li -V .j. . (4)

, Дисперсия -в этом случае может 35 быть определена как

D «ob PoCl - С), (5)

а минимум дисперсии определяется из 40 условия

г

(б)

Сравнивая (3) и (6), видим, Что в первом случае (в предлагаемом устройстве) точность настройки коэффициентов увеличивается в N раз.

В процессе формирования откорректированного сигнала (в первом цик- . ле работыр на первый вход блока 16 суммирования поступает сигнал с выхода второго АЦП 6, а на второй вход блока 15 суммирования поступает сигнал с выхода первого регистра 16 памяти через коммутатор 18, Таким образом, реализуется суммирова- ние с накоплением. После окончания последовательного суммирования произведений соответствующих выборок и

коэффициентов результат переписыва- ется во второй регистр 17 памяти, В процессе изменения коэффициентов передачи отводов корректора (во втором цикле работы) посредством комму- татора 18 по сигналу, поступающему от блока 14 управления, на второй вход блока 15 суммирования поступают сигналы, соответствующие регулируемому коэффициенту передачи, а на пер вый вход блока 15 суммирования - сигналы, соответствуннцие произведению выборки и ошибки (изменение коэффициента) с учетом величины подстраиваемого коэффициента (см.), При этом на выходе первого регистра 16 памяти формируется сигнал, соответствующий величине изменения ко- эффиилента передачи подстраиваемого (Отвода без накопления результата,

С первого выхода первого АЦП 2 . (фиг,4а) поступает сигнал на входы триггеров 19 - 20 (фиГв4а) и уста навливает их в начальное состояниее С вьосода триггера 19 сигнал поступает на управляю1ций вход ключа 3 (фиг,4и)о Посредством триггера 20, элемента И 22 и делителя 25 формиру-

показано на фиг,5, где а,а - первый

(старший), второй разряды сигнала а,

Допустим, что сигнал а; на выходе сумматора 7 имеет вид п-разряд-Н него кодового слова и представлен в прямом коде. Предположим также, что сигналу с относительным значением 1 соответствует комбинация 001,

ас отнрсительным значением 3 - комбинация 011, В решающем блоке 4 необходимо изменять только значение второго разряда кодового числа , Первый, четвертый, п-й разряды имеют

вид логического О, а третий разряд, вид лог ической 1, На выходе блока 29 вычитания формируется- сигнал ошибки 1-по правилу 1, а - а|,

Форм У па изобретения

I, Адаптивный корректор, содержа- пвдй первый аналогово-цифровой преобразователь, первый вход которого яв- ляется входом адаптивного корректора, последовательно соединенные ключ, / блок памяти выборок и перемножающий цифроаналоговый преобразователь, второй аналого-цифровой преобразова

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Адаптивный корректор сигнала | 1978 |

|

SU794735A1 |

| Адаптивный корректор | 1989 |

|

SU1688418A1 |

| Цифровой адаптивный корректор меж-СиМВОльНыХ иСКАжЕНий B СигНАлАХ дАН-НыХ | 1978 |

|

SU801269A1 |

| Цифровой адаптивный корректорСигНАлА | 1978 |

|

SU832733A1 |

| Корректор межсимвольных искажений | 1984 |

|

SU1220130A1 |

| Цифровой адаптивный корректор межсимвольной интерференции | 1982 |

|

SU1083374A1 |

| Адаптивный корректор канала связи | 1983 |

|

SU1166318A1 |

| Цифровой адаптивный корректор межсимвольных искажений в сигналах данных | 1979 |

|

SU921099A2 |

| Устройство для адаптивной коррекции межсимвольной интерференции | 1981 |

|

SU951724A1 |

ется тактовый сигнал управления рабо- зо тель, последовательно соединенные

той блоков 4 и 10, а посредством .триггера 20 и элемента И 23 - сигнал управления первого регистра памяти .16 сумматора 7 ().

Посредством триггера 21, элемента И 24 и. делителя 25 формируется сигиал управления работой второго АЩ 6 (фиг«4х), который включен после перемножакядего ЦАП 5с,

С одного из выходов делителя 25 сигнал поступает на управляющие входы коммутаторов 13 и 18 (фиг.4в), С делителя 25 сигнал поступает на тактовый вход второго регистра 17

сумматор и решающий блок, первый выход которого является выходом адаптивного корректора, блок памяти коэффициентов и блок управления, вход

ос которого соединен с первым выходом первого аналого-цифрового преобразо вателя, второй вход которого соединен с первым выходом блока управления, второй выход которого соединен

40 управляющим входом ключа, третий выход блока управления соединен с первым входом второго аналого-цифрового преобразователя, четвертый выход блока управления соединен с такпамяти сумматора 7 (фиГо4з), Коэффи- 45 товыми входами блока памяти выборок

циент деления делителя 25 определяет- ся количеством отводов корректора. Блок 26 элементов И может быть реализован в виде набора элементов

и блока памяти коэффициентов, отличающийся тем, что, с целью повышения точности коррекции, в него введены коммутатор, последова

И, на выходе каждого из которых фор- go но соединенные цифроаналоговый мируется сигнал (например, в виде

п рёобразователь и формирователь веса коэффициента, а также коммутатор, выход которого соединен с вторым входом перемножакщего цифроаналого- вого преобразователя, выход которого соединен с другим входом второго аналого-цифрового преобразователя, выход которого соединен с первым входом сумматора, второй выход котологического О), соответствующий подстройке t требуемой группы отводов.

В случае, когда корректируются ., сигналы, сформированные посредством двухпозиционной амплитудно-фазовой модуляции, решающий блок 8 может быть реализован аналогично тому, как

сумматор и решающий блок, первый выход которого является выходом адаптивного корректора, блок памяти коэффициентов и блок управления, вход

которого соединен с первым выходом первого аналого-цифрового преобразо вателя, второй вход которого соединен с первым выходом блока управления, второй выход которого соединен

управляющим входом ключа, третий выход блока управления соединен с первым входом второго аналого-цифрового преобразователя, четвертый выход блока управления соединен с тактовыми входами блока памяти выборок

и блока памяти коэффициентов, отличающийся тем, что, с целью повышения точности коррекции, в него введены коммутатор, последова-

o но соединенные цифроаналоговый

п рёобразователь и формирователь веса коэффициента, а также коммутатор, выход которого соединен с вторым входом перемножакщего цифроаналого- вого преобразователя, выход которого соединен с другим входом второго аналого-цифрового преобразователя, выход которого соединен с первым входом сумматора, второй выход кото7рого соединение входом блока памяти коэффициентов, выход которого соединен с входом цифроаналогового преобразователя и вторым входом сумматора, третий вход которого соединен с пятым выходом блока управления, шестой выход которого соединен с первым входом коммутатора, второй вход которого соединен с вторым выходом решающего блока, второй выход первого аналого-цифрового преобразователя соединен с первым входом ключа, второй вход которого соединен с выходом блока памяти выборок.

2о Корректор по п,1, о т л и - чающийся тем, что сумматор

Г .1

Om5fh6

15

0

5

97а

состоит из последователько соединенных блока суммирования, первьй вход которого является первым входом cyм laтopa, первого и второго регистров памяти, выход второго регистра памяти является первым выходом сумматора, а также коммутатора, первый вход которого является вторым входом сумматора, а выход соединен с вторым входом блока с т мирования, выход первого регистра памяти, являющийся вторым выходом сумматора, соединен с вторым входом коммутатора, третий вход которого, как и вторые входы первого и второго регистров памяти, является третьим входом cyj-i- матора.

А

Л.

1д

/7

HbfJ.8

.W

W

.fff

cfjus.Z

I

J

а -JL-.--

S М I I I I I I I I II 1

LLL1 I I I IJ 1 I I I I I I I I I I I I I I I I I I I I

8 --л

г -j.

11111111111111II11i 111111111111111111111111111111 6IIIII

/vr

П

n

П

-Л

JL

JL

П

Авторы

Даты

1988-08-15—Публикация

1987-06-08—Подача