-го элемента ИЛИ группы, выходы триггеров являются инверсные , разности сравниваемых чисел устройвыходами1167603

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки чисел | 1981 |

|

SU1001083A1 |

| Устройство для сравнения п-разрядных двоичных чисел | 1975 |

|

SU561959A1 |

| Устройство для поиска данных | 1990 |

|

SU1795447A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для сравнения чисел | 1978 |

|

SU767753A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для сравнения чисел | 1981 |

|

SU993247A1 |

| Устройство для сравнения весов кодов | 1979 |

|

SU798810A1 |

| Устройство для сортировки двоичных чисел | 1990 |

|

SU1783511A1 |

| Устройство для сравнения двоичных чисел | 1978 |

|

SU748408A1 |

УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ, содержащее элементы И, ИЛИ, триггеры, первый и второй кольцевые сдвигающие регистры, выходы старших разрядов которых соединены с первыми входами первого и второго элементов И соответственно, вторые входы которых соединены с инверсными выходами старших разрядов соответственно второго и первого кольцевых сдвигающих регистров, выходы первого и второго элементов И подключены к первым входам третьего и четвертого, пятого и шестого элементов И соответственно, вторые входы третьего и пятого элементов И соединены с ивнерсными вькодами первого и второго триггеров соответственно, прямые входы которых подключены к вторым входам соответственно четвертого и шестого элементов И,, выходы третьего и пятого элементов И подключены к входам установки в единичное состояние соответственно второго и первого триггеров и к входам первого э-лемента ИЛИ, выходы четвертого и шестого триггеров соединены с входами второго элемента ИЛИ, входы сдвига регистров подключены к входу тактовых сигналов устройства. отличающееся тем, что, с целью расширения области применения за счет получения разности сравниваемых чисел для любых комбинаций сравниваемых чисел, в устройство введены элемент НЕ, счетчик, дешифратор, две группы входных элементов И по п элементов в каждой, группа П элементов задержки, группа п элементов ИЛИ, группа п триггеров и rpjrnna (я - 1) элементов И переноса, где П - число разрядов сравниваемых чисел, причем вход тактовых сигналов устройства подключен к первым входам входных элементов И первой и второй групп и счетному входу счетчика, выходы разрядов которого подключены к (Л входам дешифратора, выходы которого с соединены с вторыми входами соответствующих входных элементов И первой и второй групп, третьи входы входных элементов И первой группы соединены , через элементы НЕ с выходом первого элемента ИЛИ, выход второго элемента ИЛИ подключен к третьим входам входных элементов И второй группы, 05 выход i-го входного элемента И пер вой группы, где i 1, 2, ..., ц , 05 соединен с первым входом i-го элеО мента ИЛИ группы, второй вход котооо рого подключен через элемент задержки к выходу 1 -го входного элемента И второй группы, а выход соединен со счетным входом t-го триггера группы, выход (j + 1)-го триггера группы, где j 1, 2, ..., п- 1, соединен с первым входом j -го элемента И переноса группы, второй вход которого соединен с выходом (j + 1)-го элемента ИЛИ группы, а выход подключен к третьему входу

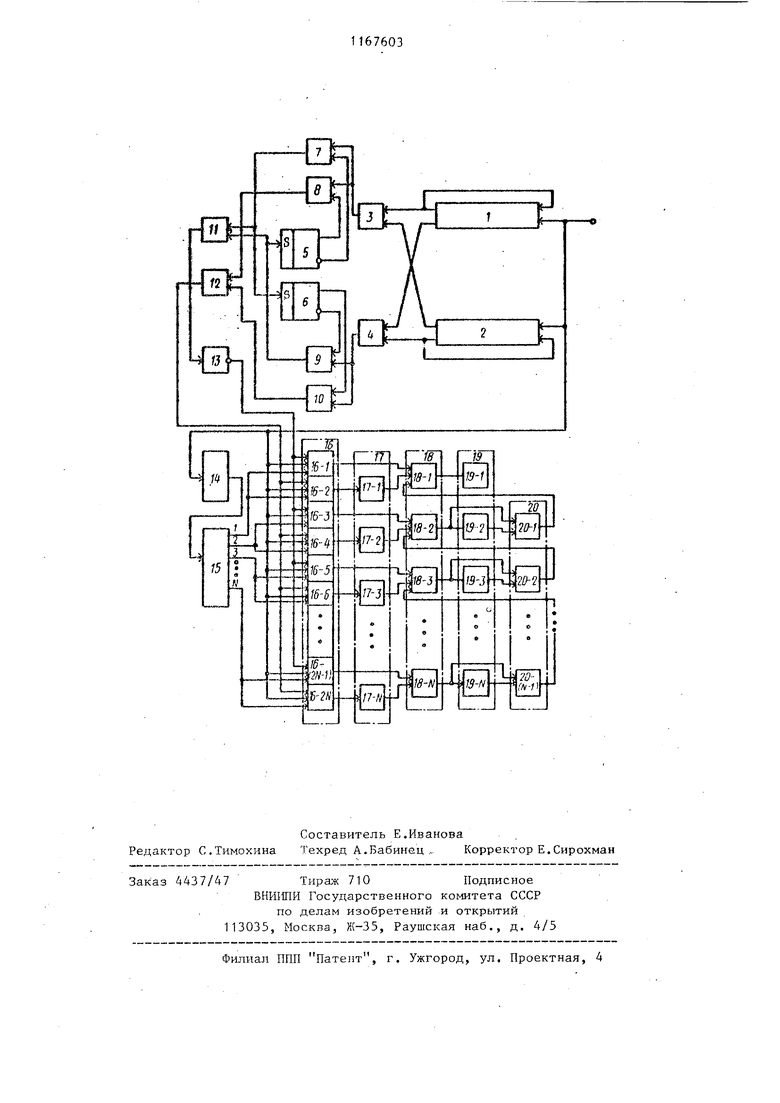

Изобретение относится в автомати ке и вычислительной технике и может быть использована при реализации технических средств дискретной авто матики и ЭВМ. Целью изобретения является расши рение области применения за счет получения разности сравниваемых чисел для любых комбинаций сравниваемых чисел за счет использования нового алгоритма формирования разности сра ниваемых чисел, реализуемого дополнительными элементам. На чертеже схематически показано предлагаемое устройство. Устройство содержит кольцевые сдвигающие регистры 1 и 2, элементы И 3 и 4, триггеры 5 и 6,.элементы 7-10, элементы ИЛИ 11 и 12, элемент НЕ 13, счетчик 14, дешифратор 15, группу входных элементов И 16, группу элементов задержки 17, группу элементов ИЛИ 18, группу триггеров 19, группу элементов И переноса 20. , Устройство работает следующим образом. Старшие разряды сравниваемых чисел поступают на элементы И 3 и 4. При равенстве старших разрядов на рыходах элементов И 3 и 4 сигнал ра вен ОЧ Если старший разряд числа, находящегося в регистре 1 больше, чем старший разряд числа в регистре 2, то срабатывает элемент И 3. Единичный сигнал с этого элемента, проходя через элемент И 7, ввиду того, что триггер 5 находится в сос тоянии О, поступает на вход S триггера 6 и переводит его в единич ное состояние. Б дальнейшем, при сравнении последующих разрядов чисе состояние триггеров 5 и 6 не меняет ся. Если же сказывается большим ста ший разряд числа, находящегося в регистре 2, то срабатывает элемент И 4, что, в свою очередь, приводит к установлению в единичное состояни триггера 5. Поэтому состояние триггеров несет информацию о том, какое число больше. Если триггер 6 находится в единичном состоянии, то больше число, находящееся в регистре 1,. если триггер 5 находится в единичном состоянии, то больше число, находящееся в регистре 2, Триггеры 5 и 6 совместно с элементами И 7-10 осуществляют коммутацию результата сравнения чисел таким образом, что на вход элемента ИЛИ 11 поступает единичный сигнал, если соответствующий разряд большего числа больше, чем тот же разряд меньшего числа, а на вход элемента ИЛИ 12 поступает единичный сигнал, если соответствующий разряд меньшего числа больше, чем тот же разряд большего числа. Сигналы с выходов элементов ИЛИ 11 и 12, с элемента ИЛИ 11 через инвертор 13, соответственно через элементы И 16-1 и И 16-2 поступают на общий вход триггера 19-1, состояние инверсного выхода которого отражает значение старшего разряда разности сравниваемых чисел Д . При этом сигнал с выхода элемента И 16-2 поступает на вход триггера через элемент задержки 17-1, с временем задержки на длительность импульса сдвига. Объединение сигналов на входе триггера 19-1 осуществляется элементом ИЛИ 18-1. После поступления 1-го импульса сдвига присутствует сигнал на 2-м выходе дешифратора 15, сигнал с выходов элементов ИЛИ 11 и 12, с элемента ИЛИ 11 через инвертор 13, поступают через соответствующие логические элементы 16-3 и 16-4, 17-2, 18-2 на общий вход триггера 19-2, состояние инверсного выхода которого отрал ает значение следующего разряда разности сравниваемых чисел. После поступления 2-го импульса сдвига сигнал появляется на 3-м выходе дешифратора, что при3водит к поступлению сигналов с выхо дов элементов ИЛИ 11 и 12, с элемен та ИЛИ 11 через инвертор 13, на общий вход триггера 19-3 и т.д. В про цессе формирования очередного знака разряда разности, если с обоих элементов ИЛИ 11 и 12, с элемента ИЛИ через инвертор 13, на общий вход соответствующего триггера поступают .единичные сигналы, происходит перенос 1 в старший разряд, через соответствующий злемент И группы 20. Для осуществления этой операции триггер должен срабатывать по заднему фронту импульса. Результат разности сравниваемых чисел формируется на инверсных выходах триггеров группы 19 после поступления (h -1)го импульса сдвига, где гг -разрядность сравниваемых двоичных чисел. Применение данного устройства позволяет получить результат сравнения двоичных чисел с фиксацией как качественного результата сравнения . ( , , ), так и количественного результата в виде модуля разности 4 для всевозможных комбинатдий сравниваемых чисел. Цель изобретения достигается за счет введения дополнительных элементов 13-15, группы элементов И 16, группы элементов задержки 17, группы элементов ИЛИ 18, группы триггеров 19 и группы элементов И 20. Эти элементы реализуют новый алгоритм получения разности сравниваемых чисел из сигналов, присутствующих на выходах 034 элементов ИЛИ 11 и 12. Алгоритм заключается в следующем: сигнал с выхода элемента ИЛИ 11 инвертируется и суммируется с сигналом, поступающим с элемента ИЛИ 12, результат разности сравниваемых чисел получается равным обратному коду, который получается в результате суммирования. Пример сравнения двоичных чисел: Af2j 101110 и 011011. В этом случае на выходе элемента ИЛИ 11 -присутствует следующая двоичная последовательность F. 100100, а на выходе элемента ИЛИ 12 - следующая Е,2 010001. Б соответствии с предлагаемым алгоритмом получаем: двоичная последовательность на выходе инвертора 13 F.,3 011011, результат cyм шpoвaния двоичных последовательностей дает результат 011011 010001 101100 обратный код результат сравнения010011, что соответствует правильному результату. Действительно (А - В)j равно 101110 011011 010011

| Устройство для сравнения двоичныхчиСЕл | 1979 |

|

SU830375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сравнения двоичных чисел | 1975 |

|

SU541166A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-15—Публикация

1984-02-15—Подача