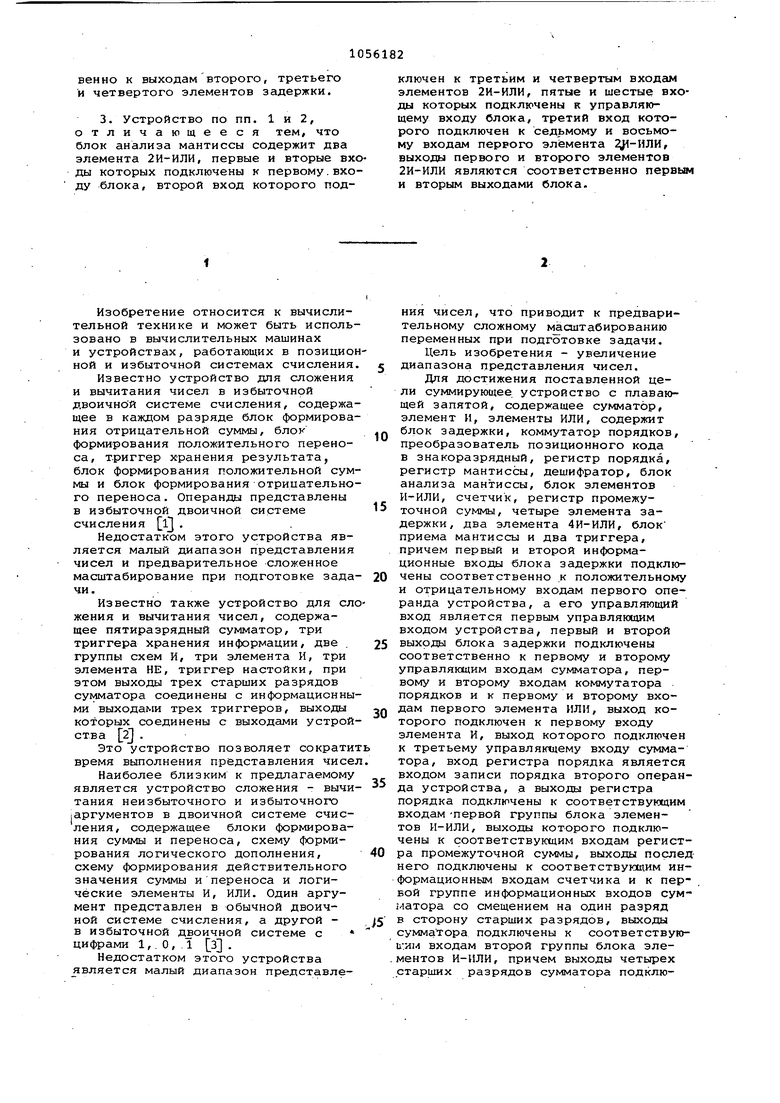

мактиссы подключены к шине записи. мантиссы второго операнда устройства, а его выходы соединены с соответствующими входами второй группы блока элементов И-ИЛИ, инверсный выход знака счетчика подключен к первому управляющему входу дешифратора и к первому входу блока приема мантиссы, выход которого подключен к второму управляющему входу блока элементов И-ИЛИ, управляющий вход блока анализа мантиссы, третий, четвертый и пятый управляющие входы блока элементов И-ИЛИ, первый управляющий вход счетчика и второй вход блока приема мантиссы являются управляющими входами с второго по седьмой устройства соответственно, прямой выход зыак.а счетчика подключен к второму управляющему входу счетчика и к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу старшего разряда дешифратора, входы которого подключены к соответствукщим информационным выходам счетчика, а остальные выходы дешифратора подключены к соответствующим входам второй группы информацион ных входов сумматора, первый вход которого соединен с выходом второго элемента ИЛИ, второй вход элемента И подключен к второму управляющему входу дешифратора, четвертому управляющему входу сумматора, первым управляющим входам элементов 4И-ИЛИ и к первому управляющему входу устройства, вход стробирования счетчика является входом стробирования устройства, входы сброса счетчика, регистра промежуточной суммы и коммутатора порядков подключены к входу сброса устройства, прямые выходы первого и второго триггеров подключены соответственно к первым и вторым группам входов элементов 4И-ИЛИ, входы третьей; группы первого элемента 4И-.ИЛИ под-. ключены соответственно к выходам .первого и третьего элементов задержки и первому выходу преобразователя позиционного кода в знакоразрядный, входы третьей группы второго

элемента 4И-ИЛИ подключены соо ветственно к выходам второго и четвертого элементов задержки и второму выходу преобразователя позиционного кода в . знакоразрядный., вторые управляющие входы первого и второго . элементов 4И-ИЛИ подключены соответственно к первому и второму выходам коммутатора порядков, а ВЕЛХОДЫ элементов 4И-ИЛИ являются выходами результата устройства.

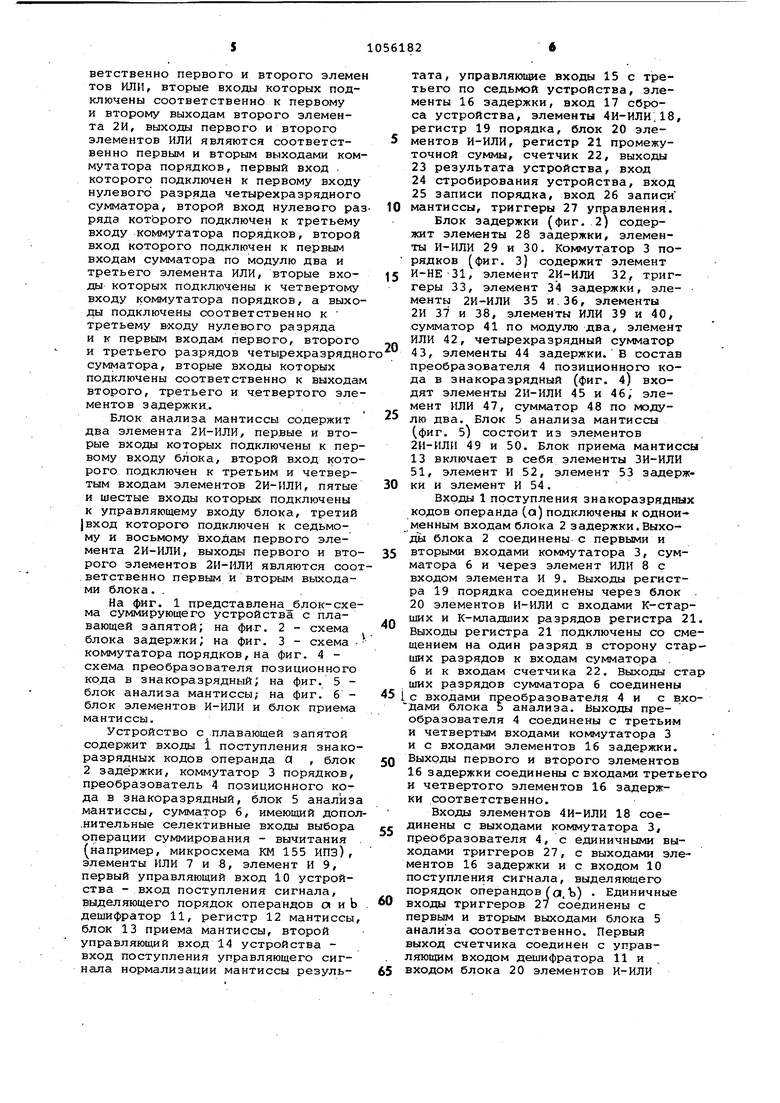

2. Устройство по п. 1, о т л ич. ающёеся тем, что коммутатор порядков содержит два триггера, сумматор по модулю два, четырехраз- рядный сумматор, четыре элемента задержки, три элемента ИЛИ, элемент

И-НЕ, три элемента 2И-ИЛИ, два элемента 2И, причем нулевые входы триггеров подключены к входу сброса коммутатора порядков, инверсный выход первого триггера подключен к входу первого элемента задержки, выход которого соединен с первыми и вторыми входами первого и второго элементов 2И-ИЛИ, третьи и четвертые входы которых подключены к старшему знаковому выходу четырехразрядного сум1иатора, пятые входы подключены к старшему значащему выходу четырехразрядного сумматора, входу второго элемента задержки и к первому входу элемента И-НЕ, второй и третий входы которого соединены соответственно с младшим и средним знаковыми выходами четырехразрядного сумматора, подключенными к входам соответствейно третьего и четвертого элементов задержки и соответственно к первому и второму входс1М третьего элемента 2И-ИЛИ, третий и четвертый входы которого подключены к выходу элемента И-НЕ, а выход третьего элемента 2И-ИЛИ соединен с единичным входом первого триггера и с шестыми входами первого и второго элементов 2И-ИЛИ, выходы которых подключены соответственно к нулевому и единичному входам второго, триггера, прямой выход которого подключен к первому и второму входам первого элемента 2И, а инверсный к первому и второму входам второго элемента 2И, третий и четвертый входы первого элемента 2И подключены соответственно к первому и второму входам коммутатора порядков, третий и четвертый входы которого подключены соответственно к третьему и четвертому входам второго элемента 2И, первый и второй выходы первого элемента 2И подключены к первым входам соответственно первого и второго элементов ИЛИ, вторые входы которых подключены соответственно к первому и второму выходам второго элемента 2И, выходы первого и второго элементов ИЛИ являются соответственно перBtoM и вторым выходами коммутатора порядков, первый вход которого подключен к первому входу нулевого рязряда четырехразрядного сумматора, второй вход нулевого разряда которого подключен к третьему входу коммутатора порядков, второй вход которого подключен к первым входам сумматора по модулю два и третьего элемента ИЛИ, вторые входы которых подключены к четвертому входу коммутатора порядков, а выходы подключены соответственно к третьему входу нулевогоразряда и к первым входам первого, второго и третьего разрядов четырехразрядного сумматора, вторые , входы которых подключены соответственно к выходам второго, третьего и четвертого элементов задержки.

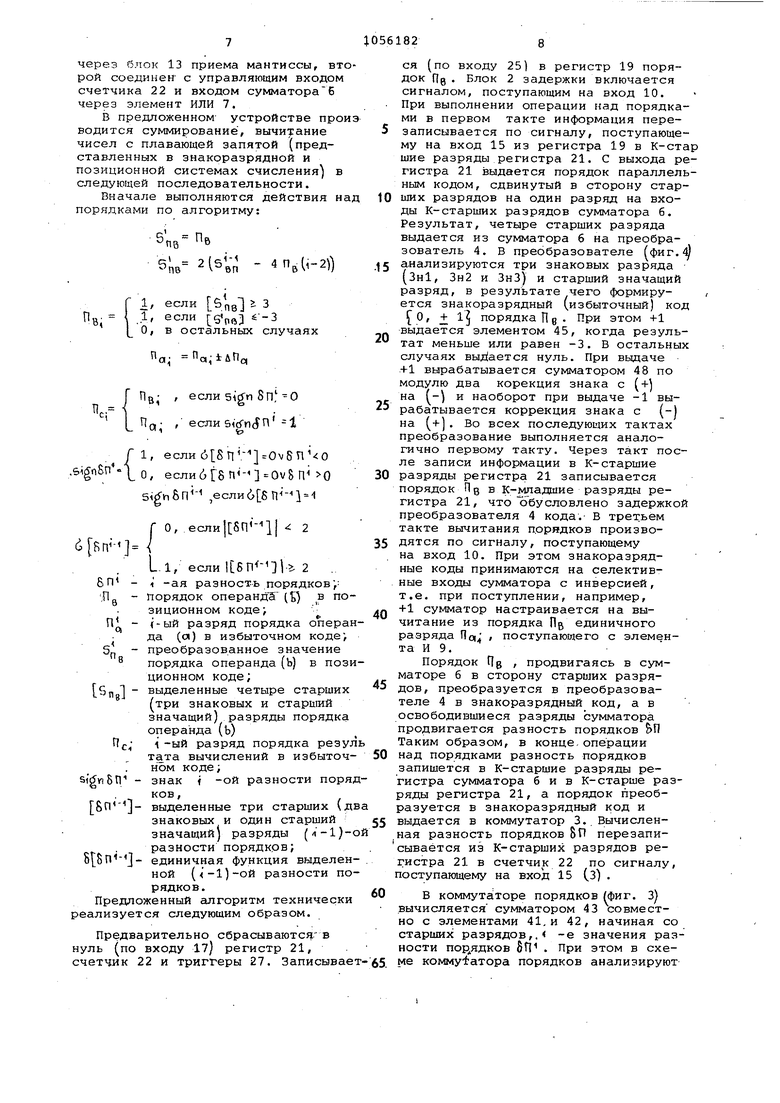

3. Устройство по пп. 1 и 2, отличающееся тем, что блок анализа мантиссы содержит два элемента 2И-ИЛИ, первые и вторые входы которых подключены к первому.входу блока, второй вход которого подключен к третьим и четвертым входам элементов 2И-ИЛИ, пятые и шестые входы которых подключены к управляющему входу блока, третий вход которого подключен к седьмому и восьмому входам первого элемента yi-ИЛИ, выходы первого и второго элементов 2И-ИЛИ являются соответственно первым и вторым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Устройство для деления с плавающей запятой | 1979 |

|

SU860063A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

1. СУМИРУЮИЕЕ УСТРОЙСТВО С ПЛАВАЮЩЕЙ ЗАПЯТОЙ, содержащее сумматор, элемент И, элементы ИЛИ, отличающееся тем, что, с целью увеличения диапазона представления чисел, устройство содер-, жит блок задержки, коммутатор порядков, преобразователь позиционного кода в знакоразрядный, регистр порядка, регистр мантиссы, дешифратор, блок анализа мантиссы, блок элементов И-ИЛИ, счетчик/ регистр промежуточной суммы, четыре элемента задержки, два элемента 4И-ИЛИ, блок приема мантиссы и два триггера, причем первый и второй информационные входы блока задержки подключены соответственно к положительному и отрицательному входам первого опера,нда устройства, а его управляющий вход является первым управляющим входом устройства, первый и второй выходы блока задержки подключены соответственно к и второму управляющим входам сумматора, первому и второму входам коммутатора порядков и к первому и второму входам первого элемента ИЛИ, выход которого подключен к первому входу элемента и, выход которого подключен к третьему управляющему входу сумматора, вход регистра порядка является входом записи порядка второго операнда устройства, а выходы регистра порядка подключены к соответствующим входам первой группы блока элементов И-ИЛИ, выходы которого подключены к соответствующим входам регистра промежуточной суммы, выходы последнего подключены к соответствующим информационным входам счетчика и к первой группе инфррмационных входов сумматора со смещением на один разряд в сторону старших разрядов, выходы сумматора подключены к соответствукедим (О входам второй группы блока элементов И-ИЛИ, причем выходы четырех старших разрядов сумматора подключены соответственно к первому, второму, третьему и четвертому входам преобразователя позиционного кода в знакоразрядный, второй, третий и четвертый входы которого сое- ; э :л динены соответственно с первым, ; вторым и третьим входами блока ана- лиза мантиссы, первый и второй выхоз: ды которого подключены к единичным входам соответственно первого и , второго триггеров, нулевые входы ; 30 которых подключены к входу сброса устройства, первый и второй выхоtsD ды преобразователя позиционного кода в знакоразрядный соединены соответственно с третьим и четвертым входами коммутатора порядкови с входами соответственно первого и второго элементов задержки, выходы которых соединены с входами третьего и четвертого элементов задержки соответственно, третий выход преобразователя позиционного кода в знакоразрядный подключен к первому управляк ему входу блока элементов И-ИЛИ, входы регистра

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и устройствах, работающих в позиционной и избыточной системах счисления.

Известно устройство для сложения и вычитания чисел в избыточной двоичной системе счисления, содержащее в каждом разряде блок формирования отрицательной суммы, блок формирования положительного переноса, триггер хранения результата, блок формирования положительной суммы и блок формирования отрицательного переноса. Операнды представлены в избыточной двоичной системе счисления i .

Недостатком этого устройства является малый диапазон представления чисел и предварительное сложенное масштабирование при подготовке задачи.

Известно также устройство для сложения и вычитания чисел, содержащее пятиразрядный сумматор, три триггера хранения информации, две . группы схем И, три элемента И, три элемента НЕ, триггер настойки, при этом выходы трех старших разрядов сумматора соединены с информационными выходами трех триггеров, выходы которых соединены с выходами устройства 2j .

Это устройство позволяет сократит время выполнения представления чисел

Наиболее близким к предлагаемому является устройство сложения - вычитания неизбыточного и избыточного аргументов в двоичной системе счисления, содержащее блоки формироваНИН суммы и переноса, схему формирования логического дополнения, схему формирования действительного значения суммы и переноса и логические элементы И, ИЛИ. Один аргумент представлен в обычной двоичной системе счисления, а другой в избыточной дJвoичнoй системе с цифрами 1,. О, . 1 З .

Недостатком этого устройства 1вляется малый диапазон представления чисел, что приводит к предварительному сложному масштабированию переменных при подготовке задачи.

Цель изобретения - увеличение диапазона представления чисел.

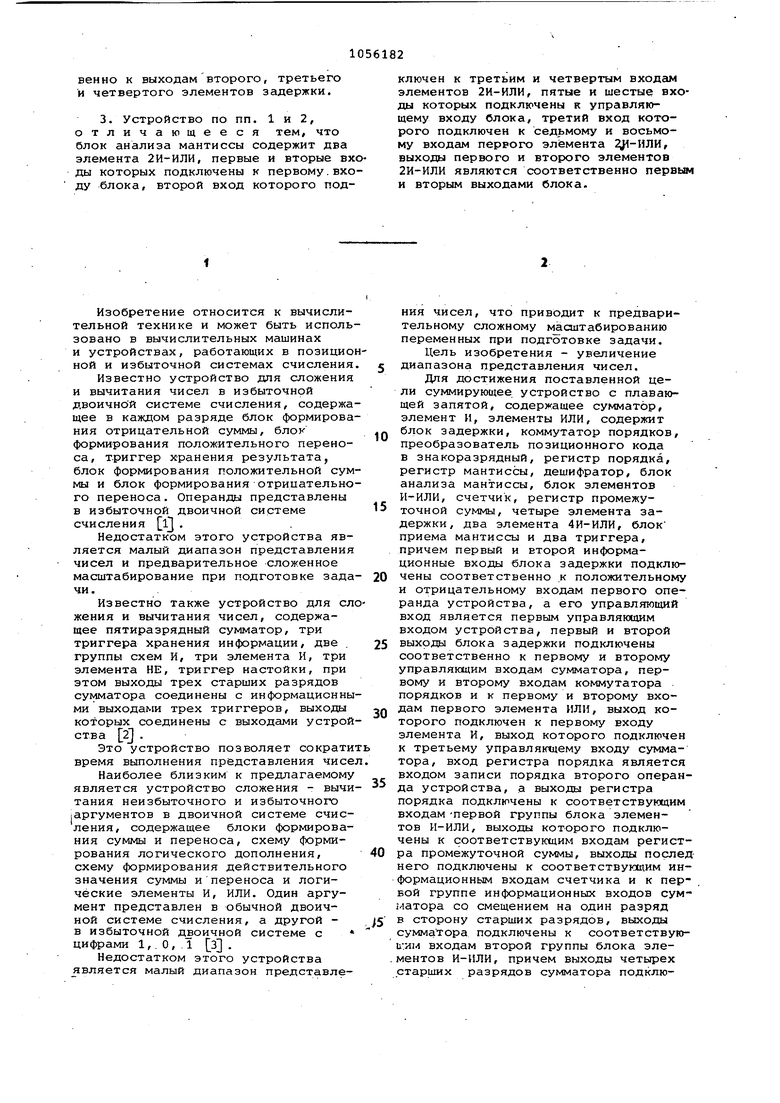

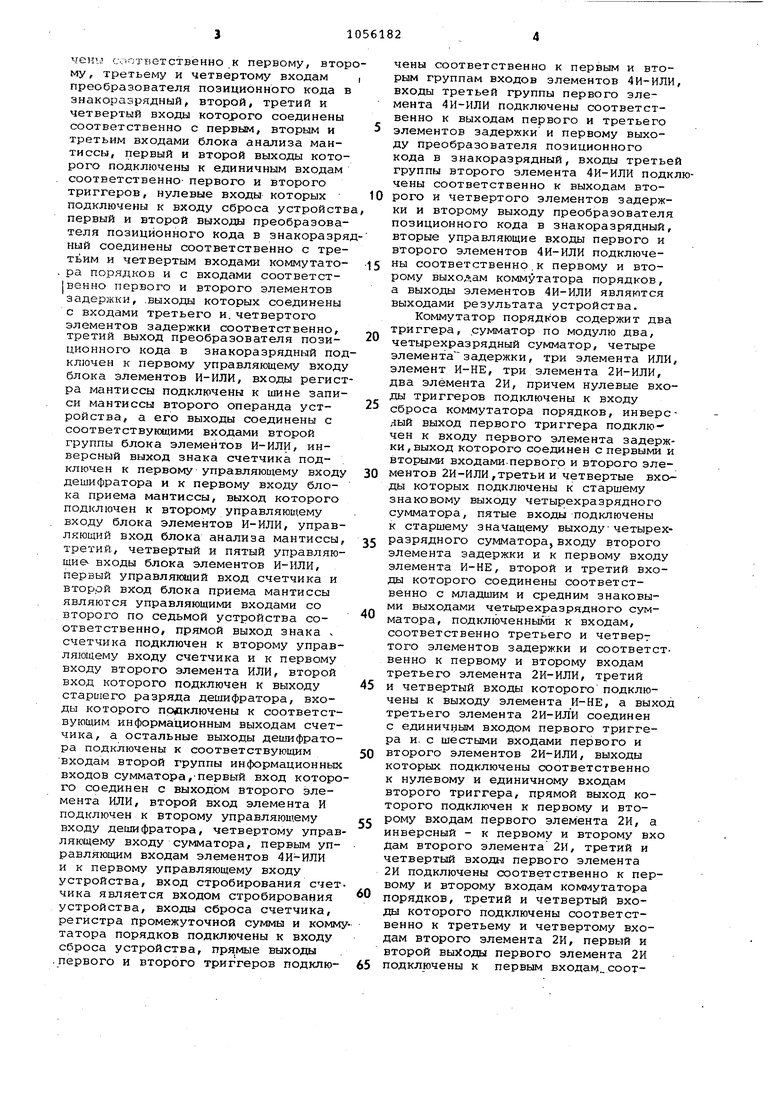

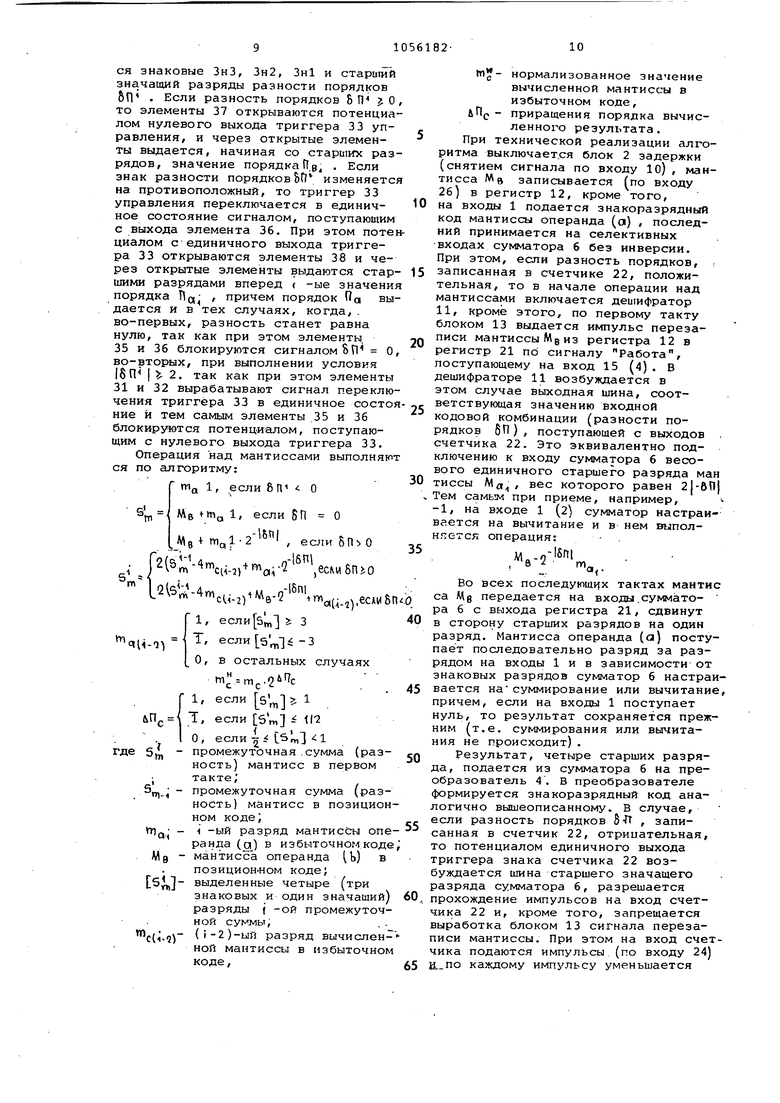

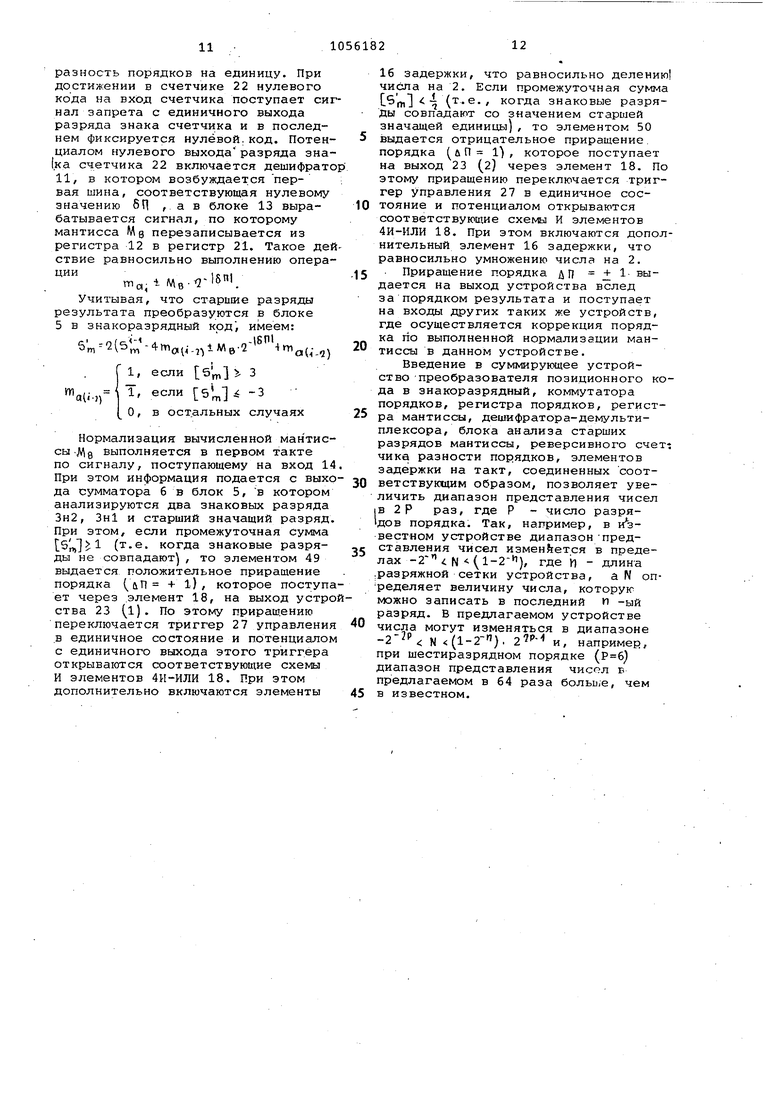

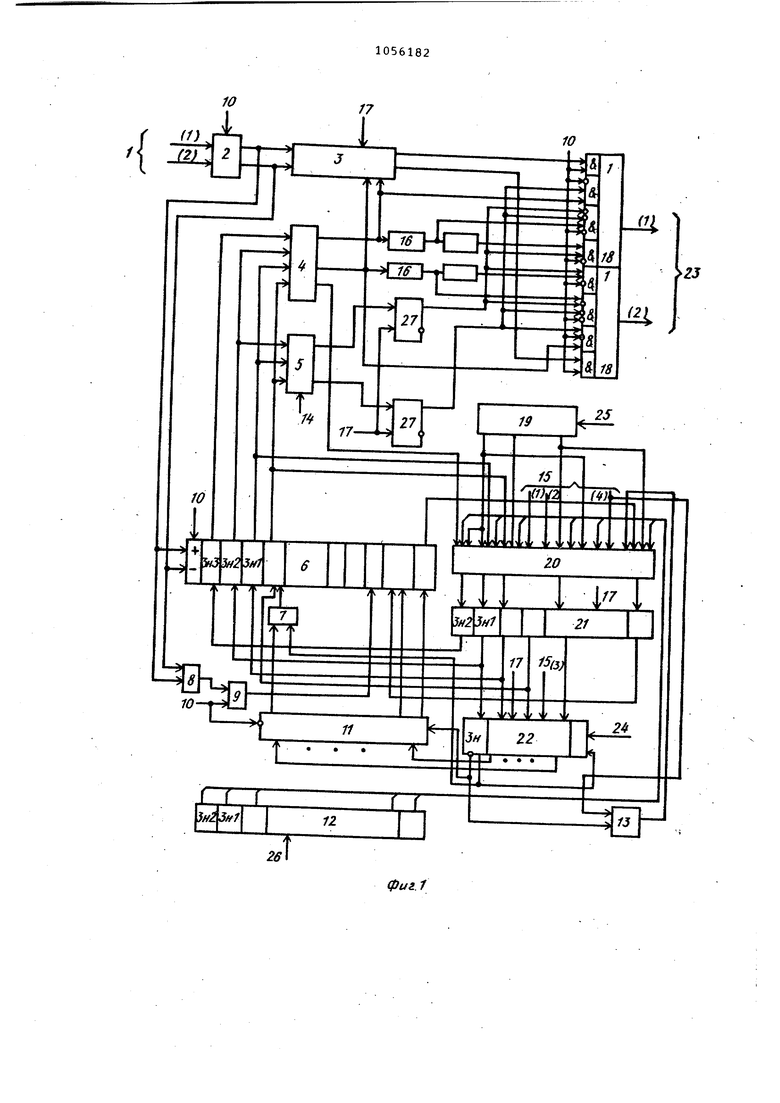

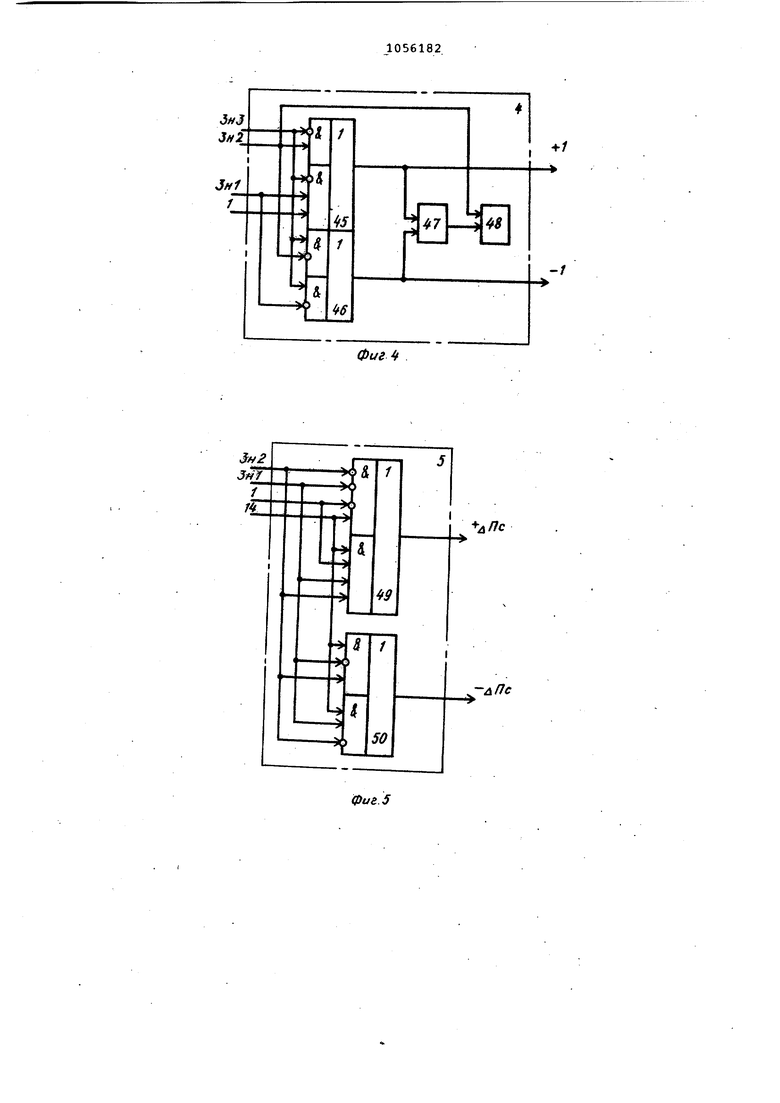

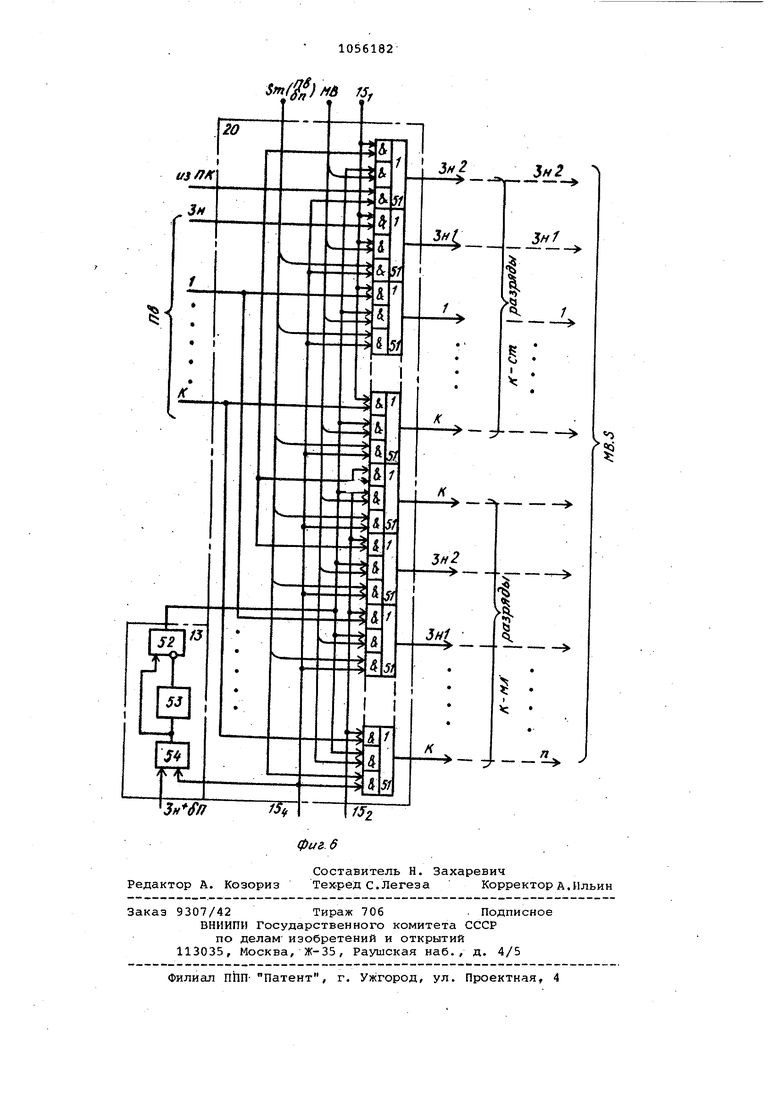

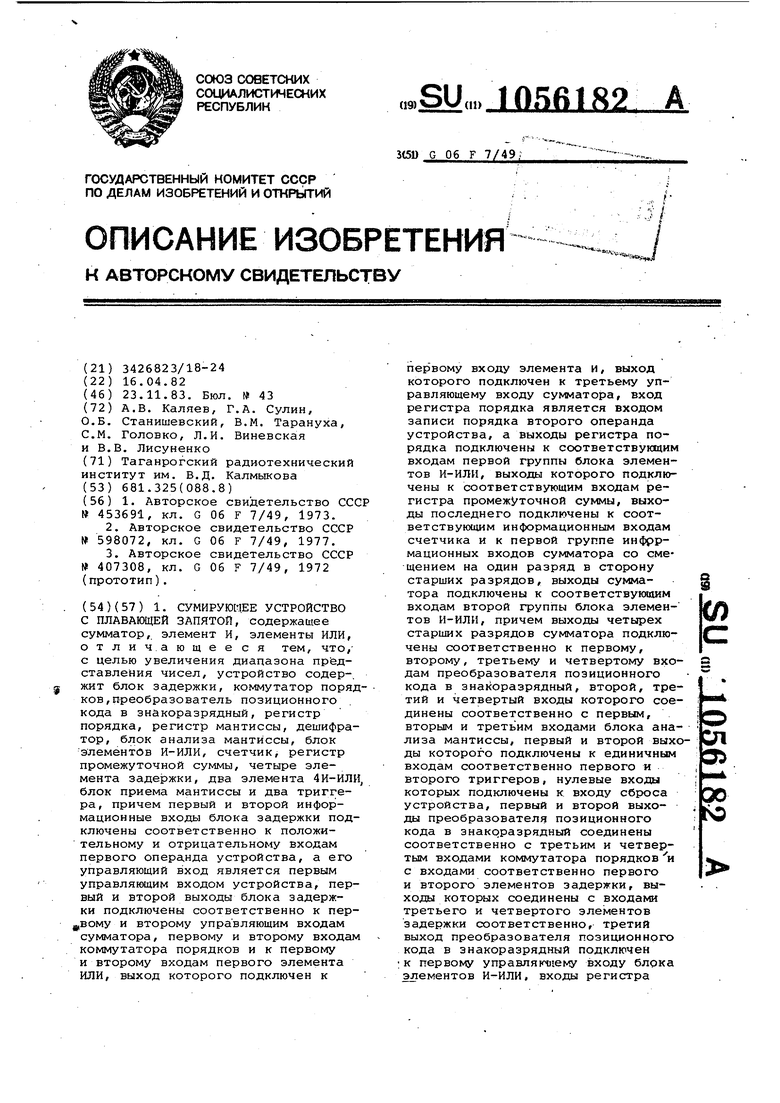

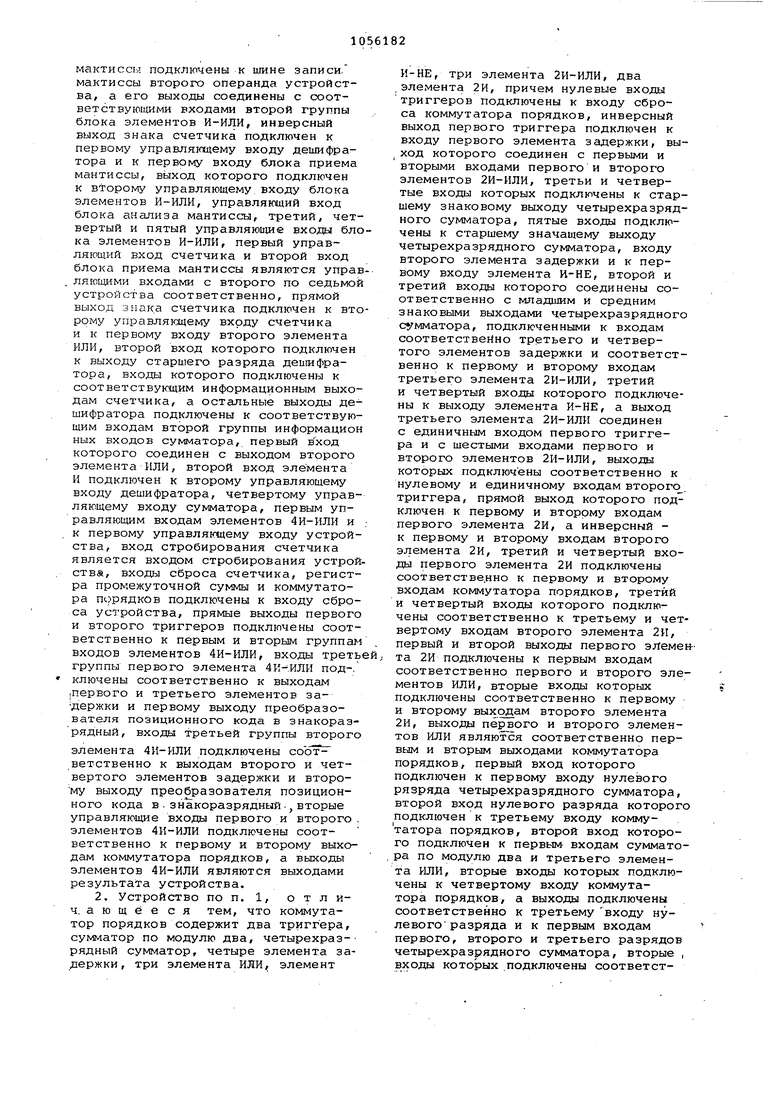

Для достижения поставленной цели суммирующее устройство с плавающей запятой, содержащее сумматор, элемент И, элементы ИЛИ, содержит блок задержки, коммутатор порядков, преобразователь позиционного кода в знакоразрядный, регистр порядка, регистр мантиссы, дешифратор, блок анализа мантиссы, блок элементов И-ИЛИ, счетчик, регистр промежуточной суммы, четыре элемента задержки, два элемента 4И-ИЛИ, блок приема мантиссы и два триггера, причем первый и второй информационные входы блока задержки подключены соответственно к положительному и отрицательному входам первого операнда устройства, а его управляющий вход является первым управляющим входом устройства, первый и второй выходы блока задержки подключены соответственно к первому и второму управляющим входам сумматора, первому и второму входам коммутатора . порядков и к первому и второму входам первого элемента ИЛИ, выход которого подключен к первому входу элемента И, выход которого подключен к третьему управляющему входу сумматора, вход регистра порядка является входом записи порядка второго операнда устройства, а выходы регистра порядка подключены к соответствующим входам -первой группы блока элементов И-ИЛИ, выходы которого подключены к соответствующим входам регистра промежуточной суммы, выходы посленего подключены к соответствующим информационным входам счетчика и к пер вой группе информационных входов сумматора со смещением на один разряд в сторону старших разрядов, выходы сумматора подключены к соответствуюи:им входам второй группы блока элементов И-ИЛИ, причем выходы четырех старших разрядов сумматора подключеиь Счюхветственно к первому, втор му , третьему и четвертому входам преобразователя позиционного кода в энакоразрядный, второй, третий и четвертый входы которого соединены соответственно с первым, вторым и третьим входами блока анализа мантиссы, первый и второй выходы которого подключены к единичным входам соответственно- первого и второго триггеров, нулевые входы которых подключены к входу сброса устройств первый и второй выходы преобразователя позиционного кода в знакоразря ный соединены соответственно с третьим и четвертым входами коммутатора порядков и с входами соответст|венно первого и второго элементов задержки, .выходы которых соединены с входами третьего и. четвертого элементов задержки соответственно, третий выход преобразователя позиционного кода в знакоразрядный под ключен к первому управляющему входу блока элементов И-ИЛИ, входы регист ра мантиссы подключены к шине записи мантиссы второго операнда устройства, а его выходы соединены с соответствующими входами второй группы блока элементов И-ИЛИ, инверсный выход знака счетчика подключен к первому управляющему входу дешифратора и к первому входу блока приема мантиссы, выход которого подключен к второму управляющему входу блока элементов И-ИЛИ, управляющий вход блока анализа мантиссы третий., четвертый и пятый управляющие входы блока элементов И-ИЛИ, первый управляющий вход счетчика и второй вход блока приема мантиссы являются управляющими входами со второго по седьмой устройства соответственно, прямой выход знака , счетчика подключен к второму управляющему входу счетчика и к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу старшего разряда дешифратора, входы которого подключены к соответствующим информационным выходам счетчика, а остальные выходы дешифратора подключены к соответствующим входам второй группы информационных входов сумматора,Первый вход которо го соединен с выходом второго элемента ИЛИ, второй вход элемента И подключен к второму управляющему входу дешифратора, четвертому управ ляющему входу сумматора, первым управляющим входам элементов 4И-ИЛИ и к первому управляющему входу устройства, вход стробирования счет чика является входом стробирования устройства, входы сброса счетчика, регистра промежуточной суммы и комм татора порядков подключены к входу сброса устройства, пря.мые выходы .первого и второго триггеров подключены соответственно к первым и вторым группам входов элементов 4И-ИЛИ, входы третьей группы первого элемента 4И-ИЛИ подключены соответственно к выходам первого и третьего элементов задержки и первому выходу преобразователя позиционного кода в знакоразрядный, входы третьей группы второго элемента 4И-ИЛИ подключены соответственно к выходам второго и четвертого элементов задержки и второму выходу преобразователя позиционного кода в знакоразрядный, вторые управляющие входы первого и второго элементов 4И-ИЛИ подключены соответственно.к первому и второму выходам коммутатора порядков, а выходы элементов 4И-ИЛИ являются выходами результата устройства. Коммутатор порядков содержит два триггера, сумматор по модулю два, четырехразрядный сумматор, четыре элемента задержки, три элемента ИЛИ, элемент И-НЕ, три элемента 2И-ИЛИ, два элемента 2И, причем нулевые входы триггеров подключены к входу сброса коммутатора порядков, инверсдый выход первого триггера подклю чен к входу первого элемента задержки, выход которого соединен с первыми и вторыми входами.первого и второго элементов 2И-ИЛИ,третьи и четвертые входы которых подключены к старшему знаковому выходу четырехразрядного сумматора, пятые входы подключены к старшему значащему выходу четырехразрядного сумматора, входу второго элемента задержки и к первому входу элемента И-НЕ, второй и третий входы которого соединены соответственно с младшим и средним знаковыми выходами четырехразрядного сумматора, подключенными к входам, соответственно третьего и четверг того элементов задержки и соответственно к первому и второму входам третьего элемента 2И-ИЛИ, третий и четвертый входы которого подключены к выходу элемента И-НЕ, а выход третьего элемента 2И-ИЛИ соединен с единичным входом первого триггера и. с шестыми входами первого и второго элементов 2И-ИЛИ, выходы которых подключены соответственно к нулевому и единичному входам второго триггера, прямой выход которого подключен к первому и второму входам первого элемента 2И, а инверсный - к первому и второму вхо Дам второго элемента 2И, третий и четвертый входы первого элемента 2И подключены соответственно к первому и второму входам коммутатора порядков, т-ретий и четвертый входы которого подключены соответственно к третьему и четвертому входам второго элемента 2И, первый и второй выходы первого элемента 2И подключены к первым входам соответственно первого и второго элемен тов ИЛИ, вторые входы которых подключены соответственно к первому и второму выходам второго элемента 2И, выходы первого и второго элементов ИЛИ являются соответственно первым и вторым выходами коммутатора порядков, первый вход . которого подключен к первому входу нулевого разряда четырехразрядного сумматора, второй вход нулевого раз ряда которого подключен к третьему входу коммутатора порядков, второй вход которого подключен к первым входам сумматора по модулю два и третьего элемента ИЛИ, вторые входы которых подключены к четвертому входу коммутатора порядков, а выходы подключены соответственно к третьему входу нулевого разряда и к первым входам первого, второго и третьего разрядов четырехразрядно сумматора, вторые входы которых подключены соответственно к выходам второго, третьего и четвертого элементов задержки.. Блок анализа мантиссы содержит два элемента 2И-ИЛИ, первые и вторые входы которых подключены к первому входу блока, второй вход которого подключен к третьим и четвертым входам элементов 2И-ИЛИ, пятые и шестые входы которых подключены к управляющему входу блока, третий )вход которого подключен к седьмому и восьмому входам первого элемента 2И-ИЛИ, выходы первого и второго элементов 2И-ИЛИ являются соот ветственно первым и вторым выходами блока. . На фиг. 1 представлена блок-схема суммирующего устройства с плавающей запятой; на фиг. 2 - схема блока задержки; на фиг. 3 - схема коммутатора порядков, на фиг. 4 схема преобразователя позиционного кода в знакоразрядный; на фиг. 5 блок анализа мантиссы; на фиг. 6 блок элементов И-ИЛИ и блок приема мантиссы. Устройство с плавающей запятой содержит входы i поступления знакоразрядных кодов операнда а , блок 2 задержки, коммутатор 3 порядков, преобразователь 4 позиционного кода в знакоразрядный, блок 5 анализа мантиссы, сумматор 6, имеющий допол .нительные селективные входы выбора операции суммирования - вычитания например, микросхема КМ 155 ИПЗ), элементы ИЛИ 7 и 8, элемент И 9, первый управляющий вход 10 устройства - вход поступления сигнала, выделяющего порядок операндов а и b дешифратор 11, регистр 12 мантиссы блок 13 приема мантиссы, второй управляющий вход 14 устройства вход поступления управляющего сигнала нормализации мантиссы результата, управляющие входы 15 с третьего по седьмой устройства, элементы 16 задержки, вход 17 сброса устройства, элементы 4И-ИЛИ.18, регистр 19 порядка, блок 20 элементов И-ИЛИ, регистр 21 промежуточной суммы, счетчик 22, выходы 23результата устройства, вход 24стробирования устройства, вход 25записи порядка, вход 26 записи мантиссы, триггеры 27 управления. Блок задержки (фиг. 2) содержит элементы 28 задержки, элементы И-ИЛИ 29 и 30. Коммутатор 3 порядков фиг. 3) содержит элемент И-НЕ 31, элемент 2И-ИЛИ 32, триггеры 33, элемент 34 задержки, элементы 2И-ИЛИ 35 и.36, элементы 2И 37 и 38, элементы ИЛИ 39 и 40, сумматор 41 по модулю два, элемент ИЛИ 42, четырехразрядный сумматор 43, элементы 44 задержки. В состав преобразователя 4 позиционного кода в знакоразрядный (фиг. 4) входят элементы 2И-ИЛИ 45 и 46, элемент ИЛИ 47, сумматор 48 по модулю два. Блок 5 анализа мантиссы (фиг. 5) состоит из элементов 2И-ИЛИ 49 и 50. Блок приема мантиссы 13 включает в себя элементы ЗИ-ИЛИ 51, элемент И 52, элемент 53 задержки и элемент И 54. Входы 1 поступления знакоразрядных кодов операнда (а) подключены к одноименным входам блока 2 з адержки. Выходы блока 2 соединены с первыми и вторыми входами коммутатора 3, сумматора 6 и через элемент ИЛИ 8 с входом элемента И 9. Выходы регистра 19 порядка соединены через блок 20 элементов И-ИЛИ с входами К-старших и К-младц1их разрядов регистра 21. Выходы регистра 21 подключены со смещением на один разряд в сторону старших разрядов к входам сумматора . 6 и к входам счетчика 22. Выходы стар ших разрядов сумматора 6 соединены с входами преобразователя 4 и с вхрдами блока 5 анализа. Выходам преобразователя 4 соединены с третьим и четвертым входами коммутатора 3 и с входами элементов 16 задержки. Выходы первого и второго элементов 16 задержки соединены с входами третьего и четвертого элементов 16 задержки соответственно. Входы элементов 4И-ИЛИ 18 соединены с выходами коммутатора 3, преобразователя 4, с единичными выходами триггеров 27, с выходами элементов 16 задержки и с входом 10 поступления сигнала, выделяющего порядок операндов () . Единичные входы триггеров 27 соединены с первым и вторым выходами блока 5 анализа соответственно. Первый выход счетчика соединен с управляющим входом дешифратора 11 и входом блока 20 элементов И-ИЛИ через блок 13 приема мантиссы, в рой соединен- с управляющим входо счетчика 22 и входом сумматора б через элемент ИЛИ 7. В предложенном устройстве пр водится суммирование, вычитание чисел с плавающей запятой (представленных в знакоразрядной и позиционной системах счисления) следующей последовательности. Вначале выполняются действия порядками по алгоритму: 5пв Пв 51,0 2(5;-,; - 4пД,-2)) 1, если Snel 1, если spft 6--3 О, в остальных случаях а Пс,;1гДПс, Пц , если sign Sn. о Пп,- , если б1(Гп(УП -1 1fc fl, если . Ov8n 0 ,6ignSn | о, если6Г8П - ОУВП 0 ,если6 БП -1 1 Г О, если бП-Ч| 2 L-1, если 2 . БП - 1 -ая разность порядков Лц - порядок операнд5 (t) в зиционном коде П - (-ЫЙ разряд порядка опе да (ся) в избыточном код 5 - преобразованное значени порядка операнда (Ь) в п ционном коде; Sjig - выделенные четыре старш (три знаковых и старший значащий) разряды поряд операнда (ь) i-ый разряд порядка ре тата вычислений в избыт . ном коде; SigriBtl/ - знак f -ой разности по . ков, выделенные три старших знаковых и один старший значащий) разряды (1-1 разности порядков; единичная функция выдел ной (-1)-ой разности рядков. Предложенный алгоритм техничес реализуется следующим образом. Предварительно сбрасываются в нуль (по входу 17) регистр 21, счетчик 22 и триггеры 27. Записы ся (по входу 25) в регистр 19 порядок (70 . Блок 2 задержки включается сигналом, поступающим на вход 10. При выполнении операции над порядками в первом такте информация перезаписывается по сигналу, поступающему на вход 15 из регистра 19 в К-стар шие разряды регистра 21. С выхода регистра 21 выдается порядок параллельным кодом, сдвинутый в сторону старших разрядов на один разряд на входы К-старших разрядов сумматора 6. Результат, четыре старших разряда выдается из сумматора 6 на преобразователь 4. Б преобразователе (фиг. анализируются три знаковых разряда (Зн1, Зн2 и ЗнЗ) и старший значащий разряд, в результате чего формируется знакоразрядный (избыточный) код f О, + 1 порядка П g . При этом +1 выдается элементом 45, когда результат меньше или равен -3. В остальных случаях выд|ается нуль. При выдаче +1 вырабатывается сумматором 48 по модулю два корекция знака с (+) на - и наоборот при выдаче -1 вырабатывается коррекция знака с (-) на (+. Во всех последующих тактах преобразование выполняется аналогично первому такту. Через такт после записи информации в К-старшие разряды регистра 21 записывается порядок Пд в К-младшие разряды регистра 21, что 6бусловлено задержкой преобразователя 4 кода.- В третьем такте вычитания п.орндков производятся по сигналу, поступающему на вход 10. При этом знакоразрядные коды принимаются на селективные входы сумматора с инверсией, т.е. при поступлении, например, +1 сумматор настраивается на вычитание из порядка Пв единичного разряда По| поступающего с элемента И 9. Порядок Пр , продвигаясь в сумматоре 6 в сторону старших разрядов, преобразуется в преобразователе 4 в знакоразрядный код, а в освободившиеся разряды сумматора продвигается разность порядков &П Таким образом, в конце,операции над порядками разность порядков запишется в К-старшие разряды регистра сумматора бив К-старше разряды регистра 21, а порядок преобразуется в знакоразрядный код и выдается в коммутатор 3.. Вычисленная разность порядков &П перезаписываётся из К-старших разрядов регистра 21 в счетчик 22 по сигналу, поступающему на вход 15 (З) . В коммутаторе порядков (фиг. 3) вычисляется сумматором 43 совместно с элементами 41, и 42, начиная со старших разрядов,. -е значения разности пор ядков 8П . При этом в схеме коммутатора порядков анализируют ся знаковые ЗнЗ, Зн2, Зн1 и старший значащий разряды разности порядков &П . Если разность порядков 8 П . О то элементы 37 открываются потенциалом нулевого выхода триггера 33 управления, и через открытые элементы выдается, начиная со старших разрядов, значение порядка П.р . Если знак разности порядков ЬГ) изменяетс на противоположный, то триггер 33 управления переключается в единичное состояние сигналом, поступающим с выхода элемента 36. При этом поте циалом с единичного выхода триггера 33 открываются элементы 38 и через открытые элементы выдаются старшими разрядами вперед с -ые значени порядка , причем порядок Па выдается и в тех случаях, когда,. во-первых, разность станет равна нулю, так как при этом элементы. 35 и 36 блокируются сигналом 8П О во-вторых, при выполнении условия 16 П ( 2. так как при этом элементы 31 и 32 вырабатывают сигнал переклю чения триггера 33 в единичное состо ние и тем самым элементы 35 и 36 блокируются потенциалом, поступающим с нулевого выхода триггера 33. Операция над мантиссами выполняю ся по алгоритму: Шд 1, если 6П -: О , если Sn 0 Mg t rYigl-2 , если 5n О 215 си-„+ аг2 еаибп о ).o,u-7).ecAиS 1, 3 Т, если - 3 0,в остальных случаях гт1 т(, 1,если 5 1 ЬП. т, если Sm 112 О, если | :i где SL - промежуточная .сумма (разность) мантисс в первом ; такте; п)- промежуточная сумма (разность) мантисс в позицион ном коде f rtig- - i -ый разряд мантиссы one ранда (а) в избыточном коде Wg мантисса операнда (Ь) в позициоННом коде; выделенные четыре (три знаковых и один значащий) разряды ( -ой промежуточной суммы. - (-2)-ый разряд вычисленной мантиссы в избыточном коде, нормализованное значение вычисленной мантиссы в избыточном коде, &Пс - приращения порядка вычисленного результата. При технической реализации алгоритма выключается блок 2 задержки (снятием сигнала по входу Ю) , мантисса Мй записывается (по входу 26) в регистр 12, кроме того, на входы 1 подается знакоразрядный код мантиссы операнда (а) , последний принимается на селективных входах сумматора 6 без инверсии. При этом, если разность порядков, , записанная в счетчике 22, положительная, то в начале операции над мантиссами включается дешифратор 11, кроме этого, по первому такту блоком 13 выдается импульс перезаписи мантиссы MB из регистра 12 в регистр 21 по сигналу Работа, поступающему на вход 15 (4). В дешифраторе 11 возбуждается в этом случае выходная шина, соответствующая значению входной кодовой комбинации (разности порядков 6П), поступающей с выходов . счетчика 22. Это эквивалентно подключению к входу сумматора 6 весового единичного старшего разряда ман тиссы Мя , вес которого равен 21-бП| Тем самьз при приеме, например, -1, на входе 1 (2) сумматор настраивается на вычитание и в нем выполняется операция: M.-2-. Во всех последующих тактах мантис са MB передается на входы.сумматора 6 с выхода регистра 21, сдвинут в сторону старших разрядов на один разряд. Мантисса операнда (а) поступает последовательно разряд за разрядом на входы 1 и в зависимости от знаковых разрядов сумматор 6 настраивается насуммирование или вычитание, причем, если на входы 1 поступает нуль, то результат сохраняется прежним (т.е. суммирования или вычитания не происходит) . Результат, четыре старших разряда, подается из сумматора 6 на преобразователь 4. в преобразователе формируется знакоразрядный код аналогично вышеописанному. В случае, если разность порядков 8-fT , записанная в счетчик 22, отрицательная, то потенциалом единичного выхода триггера знака счетчика 22 возбуждается шина старшего значащего разряда сумматора 6, разрешается прохождение импульсов на вход счетчика 22 и, кроме того, запрещается выработка блоком 13 сигнала перезаписи мантиссы. При этом на вход счетчика подаются импульсы (по входу 24) IL-ПО каждому импульсу уменьшается разность порядков на единицу. При достижении в счетчике 22 нулевого кода на вход счетчика поступает сиг нал запрета с единичного выхода разряда знака счетчика и в последнем фиксируется нулевой.код. Потенциалом нулевого выхода разряда зна1ка счетчика 22 включается дешифрато 11, в котором возбуждается первая шина, соответствующая нулевому значению 5П , а в блоке 13 вырабатывается сигнал, по которому мантисса М0 перезаписывается из регистра 12 в регистр 21. Такое дей ствие равносильно выполнению операцииIX nl ша, 1 . Учитывая, что старшие разряды результата преобразуются в блоке 5 в знакоразрядный код, имеем: .. 5 2(5;;,-4т ) 1, если 5,„ 3 Т, если 5 -3 О, в остальных случаях Нормализация вычисленной мантиссы-Мд выполняется в первом такте по сигналу, поступающему на вход 1 При этом информация подается с выхо да сумматора 6 в блок 5, в котором анализируются два знаковых разряда Зн2, Зн1 и старший значащий разряд При этом, если промежуточная сумма 5п, (т.е. когда знаковые разряды не совпадают, то элементом 49 выдается положительное приращение порядка (йП + 1), которое поступ ет через элемент 18, на выход устр ства 23 (1). По этому приращению переключается триггер 27 управлени в единичное состояние и потенциало с единичного выхода этого триггера открываются соответствующие схемы И элементов 4И-ИЛИ 18. При этом дополнительно включаются элементы 16 задержки, что равносильно делению числа на 2. Если промежуточная сумма 5п,1 - (т. е. , когда знаковые разряды совпадают со значением старшей значащей единицы), то элементом 50 выдается отрицательное приращение порядка (а П 1), которое поступает на выход 23 (2) через элемент 18. По этому приращению переключается триггер управления 27 в единичное состояние и потенциалом открываются соответствующие схемы И элементов 4И-ИЛИ 18. При этом включаются дополнительный элемент 16 задержки, что равносильно умножению числа на 2. Приращение порядка дп - i выдается на выход устройства вслед за порядком результата и поступает на входы других таких же устройств, где осуществляется коррекция порядка по выполненной нормализации мантиссы в данном устройстве. Введение в суммирующее устройство преобразователя позиционного кода в знакоразрядный, коммутатора порядков, регистра порядков, регистра мантиссы, дешифратора-демультиплексора, блока анализа старших разрядов мантиссы, реверсивного счет-: чика разности порядков, элементов задержки на такт, соединенных соответствугацим образом, позволяет увеличить диапазон представления чисел В 2Р раз, где Р - число разря1дов порядка. Так, например, в и звестном устройстве диапазонпредставления чисел изменяется в пределах -2 i М( ), где и - длин-а ;разряжной сетки устройства, а N оп ределяет величину числа, которую можно записать в последний и -ый разряд, в предлагаемом устройстве числа могут изменяться в диапазоне -2 N :(1-2-). 2Р- и, например, при шестиразрядном порядке () диапазон представления чисел в предлагаемом в 64 раза больц;е, чем в известном.

фиг.5

% +

ФигЛ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 1971 |

|

SU453691A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-11-23—Публикация

1982-04-16—Подача