выходом к первому входу первого элемента И, второй вход которого является синхронизирующим входом формирователя импульсов синхронизации, дешифратор соединен выходом с входом второго элемента И, остальные входы и выход которого являются входами и выходом формирователя импульсов синхронизации.

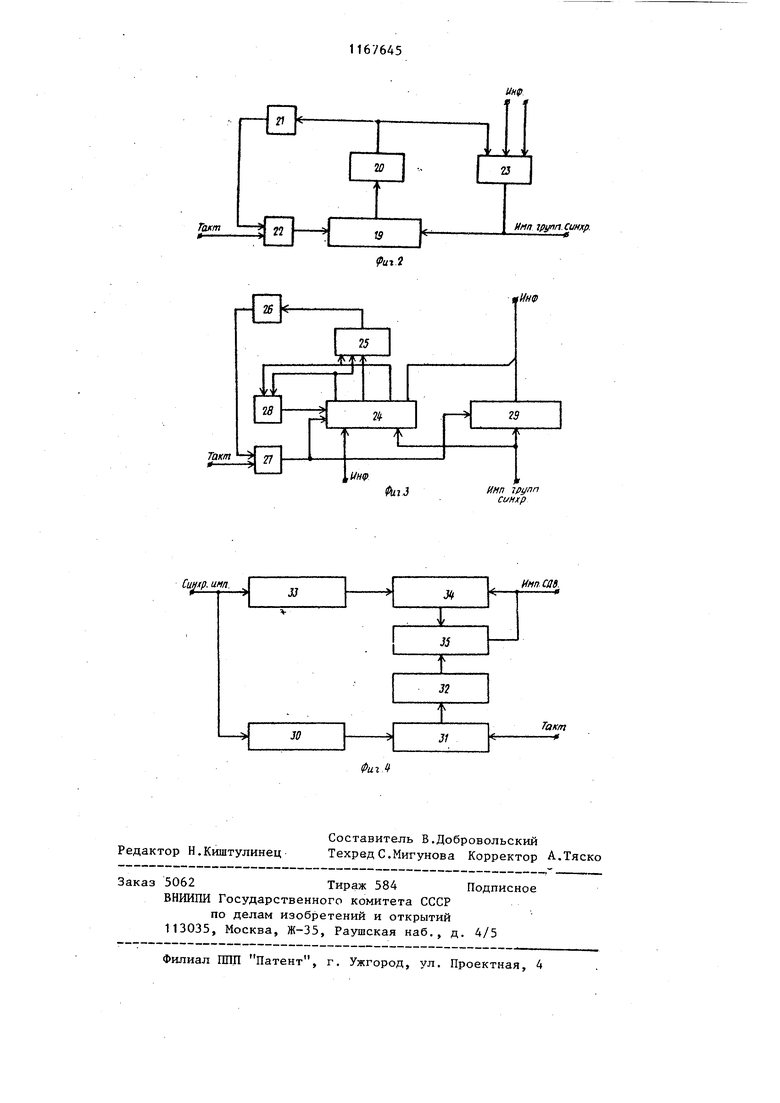

3. Устройство поп,1,отлича ю щ е е с я тем, что преобразователь кода содержит регистр сдвига, дешифратор, элемент НЕ, элемент И, формирователь сигнала обратной связи и счетчик импульсов, причем элемент НЕ соединен входом с выходом дешифратора, а выходом - с первым входом элемента И, второй вход которого является синхронизирующим входом преобразователя, регистр сдвига соединен с выходами первого и последнего разрядов с входами дешифратора и формирователя сигнала обратной связи, подключенного выходом к информационному входу регистра сдвига, подсоединенного выходами четных разрядов к дополнительным входам дешифратора, синхронизирующим входом - к выходу элемента И и к выходу счетчика импульсов, соединенного входом считывания и установки с входом считывания и

установки регистра сдвига, при этом входы разрядов регистра сдвига являюся входами преобразователя кода, выходы регистра сдвига и счетчика импульсов являются выходом преобразователя кода, а вход считывания и установки счетчика импульсов является входом считывания преобразователя кода.

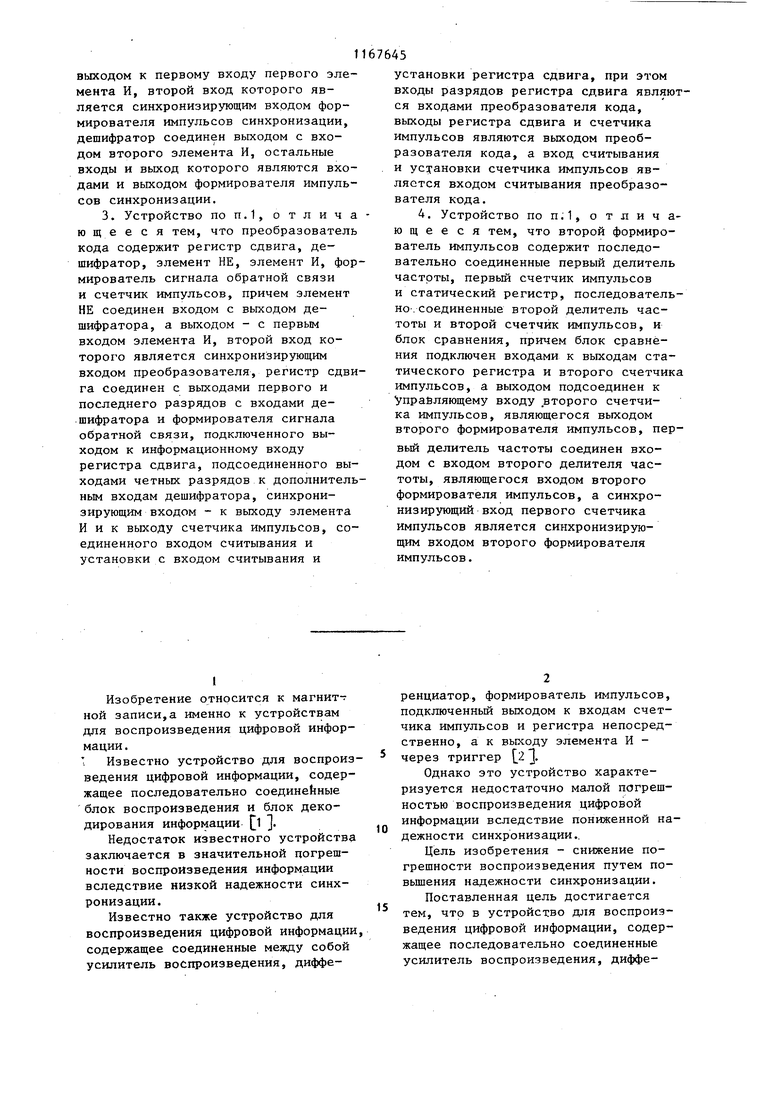

4. Устройство по п.1, о т л и ч аю щ е е с я тем, что второй формирователь импульсов содержит последовательно соединенные первый делитель частоты, первый счетчик импульсов и статический регистр, последовательно-, соединенные второй делитель частоты и второй счетчик импульсов, и блок сравнения, причем блок сравнения подключен входами к вьгходам статического регистра и второго счетчик импульсов, а выходом подсоединен к Управляющему входу второго счетчика импульсов, являющегося выходом второго формирователя импульсов, первый делитель частоты соединен входом с входом второго делителя частоты, являющегося входом второго формирователя импульсов, а синхронизирующий вход первого счетчика импульсов является синхронизирующим входом второго формирователя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи цифровой информации | 1984 |

|

SU1157569A1 |

| Устройство для воспроизведения цифровой магнитной записи | 1987 |

|

SU1422245A1 |

| Устройство для воспроизведения цифровой информации многодорожечной магнитной записи | 1989 |

|

SU1686475A1 |

| Устройство для записи цифровой информации | 1986 |

|

SU1316037A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Устройство для записи цифровой информации | 1985 |

|

SU1277189A1 |

| Синхронизирующее устройство | 1984 |

|

SU1213528A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном звукозаписи | 1985 |

|

SU1260969A2 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

1. УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ, содержащее последовательно соединенные усилитель воспроизведения, дифференциатор и первый формирователь импульсов, подключеиньш выходом к входу считывания счетчика импульсов и к первому входу триггера, вторым входом соединенного с первым выходом счетчика импульсов и с первым входом первого элемента И, подключенного вторым входом к первому выходу триггера, регистр, первым и вторым входами и выходом подсоединеный соответственно к первому входу триггера, к второму выходу и к установочному входу счетчика импульсов, соединенного счетным входом с шиной синхронизации, первую и вторую выходные шины, отличающееся тем, что, с целью уменьшения погрешности воспроизведения путем повьш1ения надежности синхронизации, в него введены регистр сдвига, второй формирователь импульсов, формирователь импульсов синхронизации, преобразователь кода, второй элемент И и элементы НЕ и ИЛИ, причем преобразователь кода и второй формирователь импульсов подключены выходами к первой и второй выходным шинам, а информационными входами подсоединены к информационным входам регистра сдвига и формирователя импульсов синхронизации и к выходу элемента 1ШИ, второй формирователь импульсов подключен входом к шине синхронизации, формирователь импульсов синхронизации подключен выходом к входам считывания регистра сдвига и преобразователя кода, регистр сдвига подключен выходами к входам преобразова(Л теля кода и выходами первого и последнего разрядов - к входам формирователя импульсов синхронизации, а синхронизирующим входом - к первому выходу счетчика импульсов, соединеного входами с выходами первого и второго элементов И, при Од этом второй элемент И подключен -VI первым входом к первому входу первоО 4 СД го элемента И, вторым входом - к второму выходу триггера, а третьим входом подсоединен через элемент НЕ к третьему входу первого элемента И и к шине управления. 2. Устройство по п.1, о т л и чающееся тем, что формирователь импульсов синхронизации содержит последовательно соединенные счетчик импульсов, дешифратор и элемент НЕ, первый и второй элементы И, причем счетчик HMnyjtbcOB соединен входами с выходами первого и второго элементов И, элемент НЕ подключен

1

Изобретение относится к магнитной записи,а именно к устройствам для воспроизведения цифровой информации .

Известно устройство для воспроизведения цифровой информации, содержащее последовательно соединейные блок воспроизведения и блок декодирования информации fl J.

Недостаток известного устройства заключается в значительной погрешности воспроизведения информации вследствие низкой надежности синхронизации.

Известно также устройство для воспроизведения цифровой информации содержащее соединенные между собой усилитель воспроизведения, дифференциатор, формирователь импульсов, подключенный выходом к входам счетчика импульсов и регистра непосредственно, а к выходу элемента И через триггер 2 J.

Однако это устройство характеризуется недостаточно малой погрешностью воспроизведения цифровой информации вследствие пониженной надежности синхронизации..

Цель изобретения - снижение погрешности воспроизведения путем повьшения надежности синхронизации.

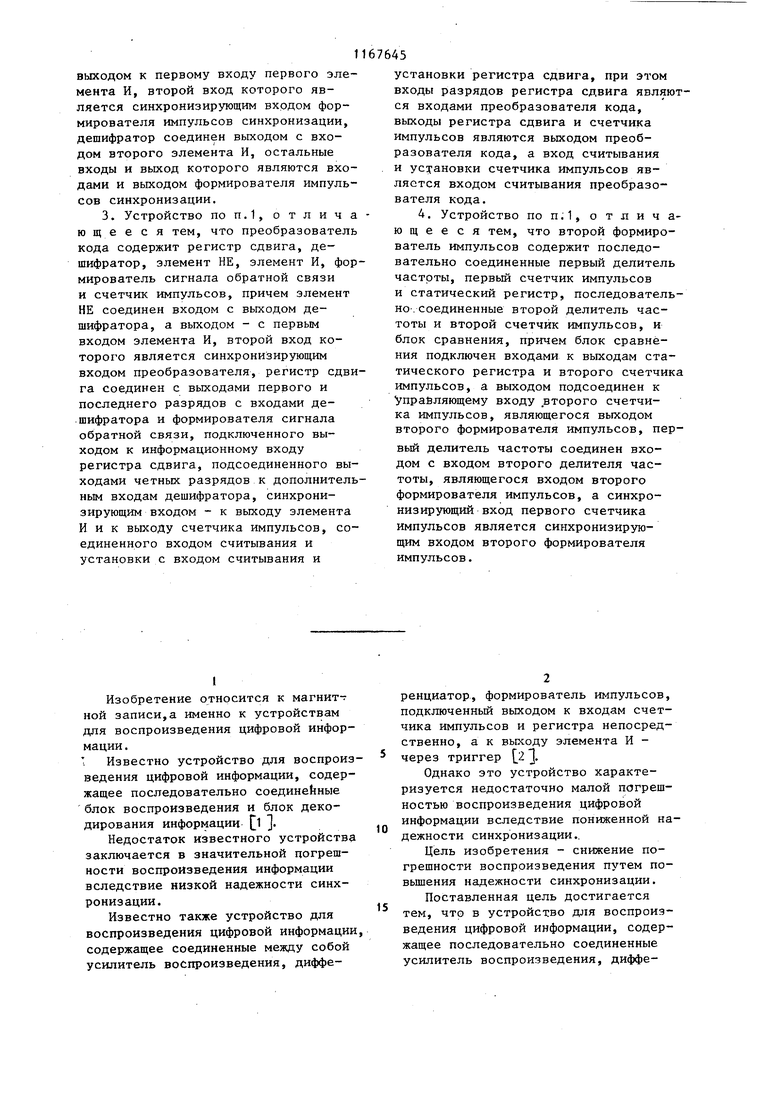

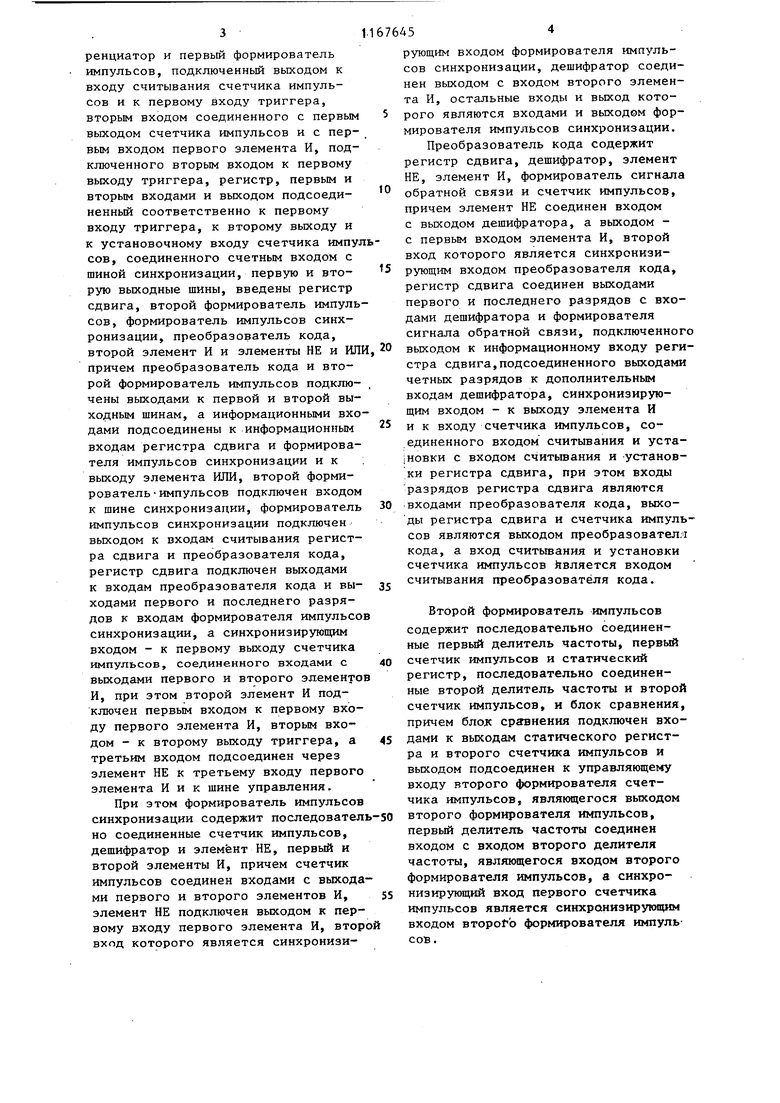

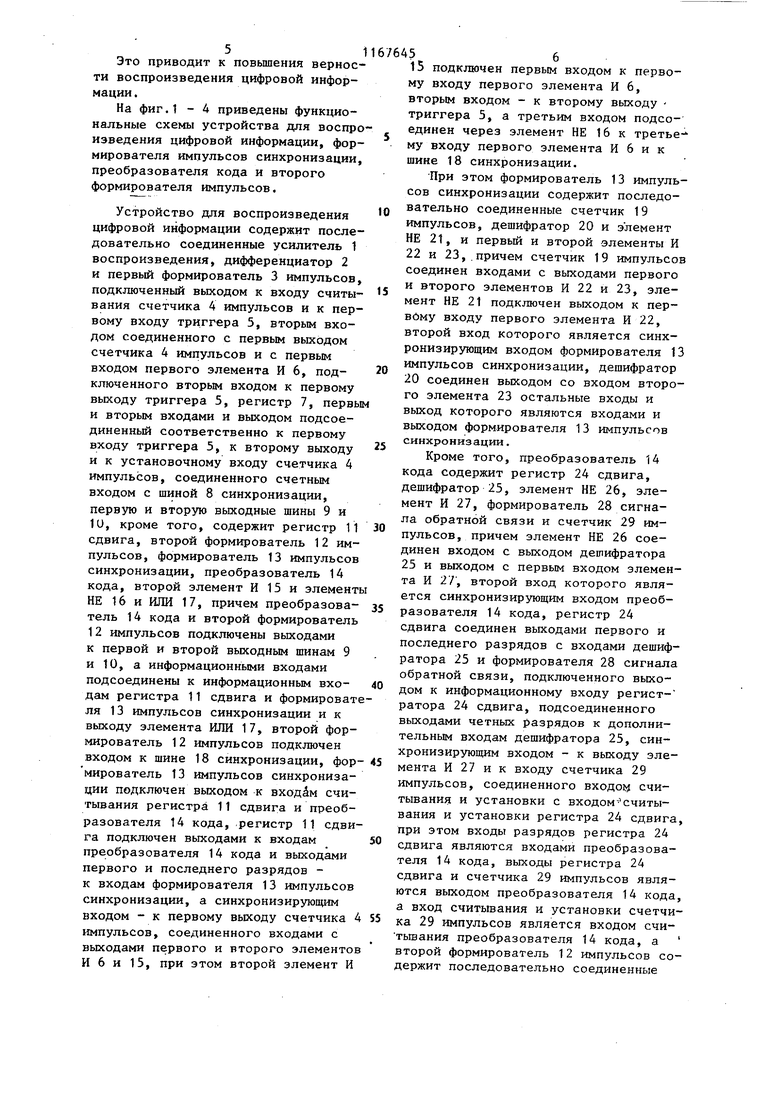

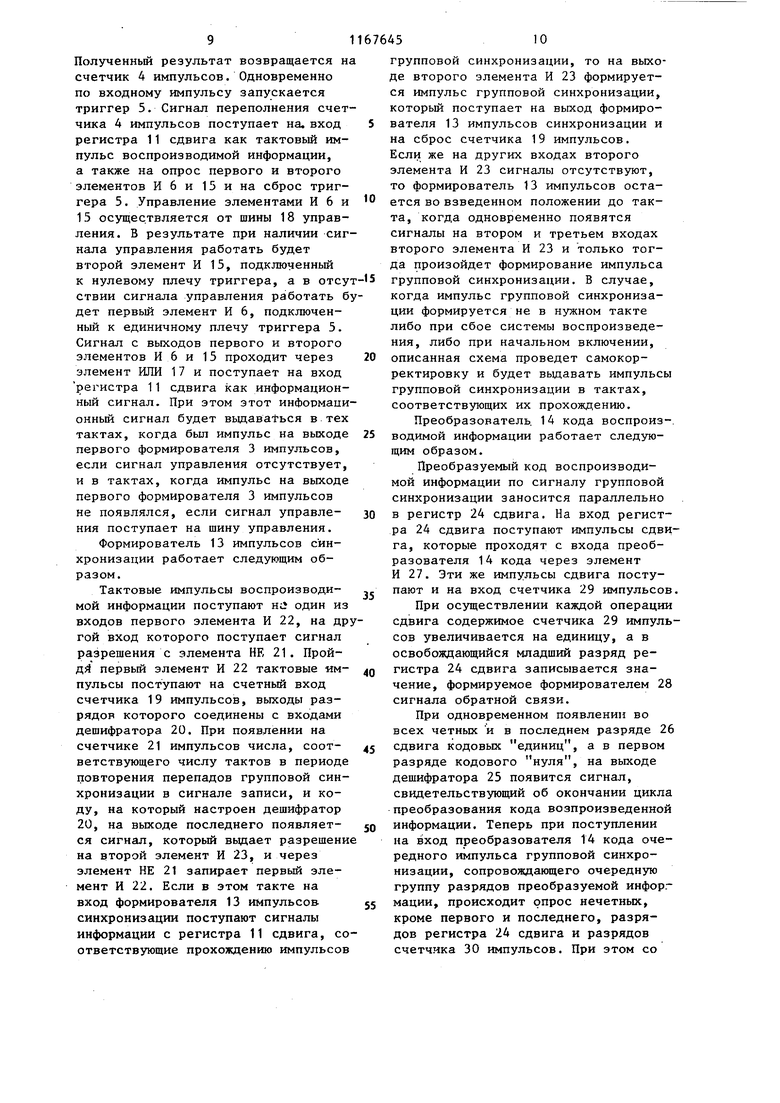

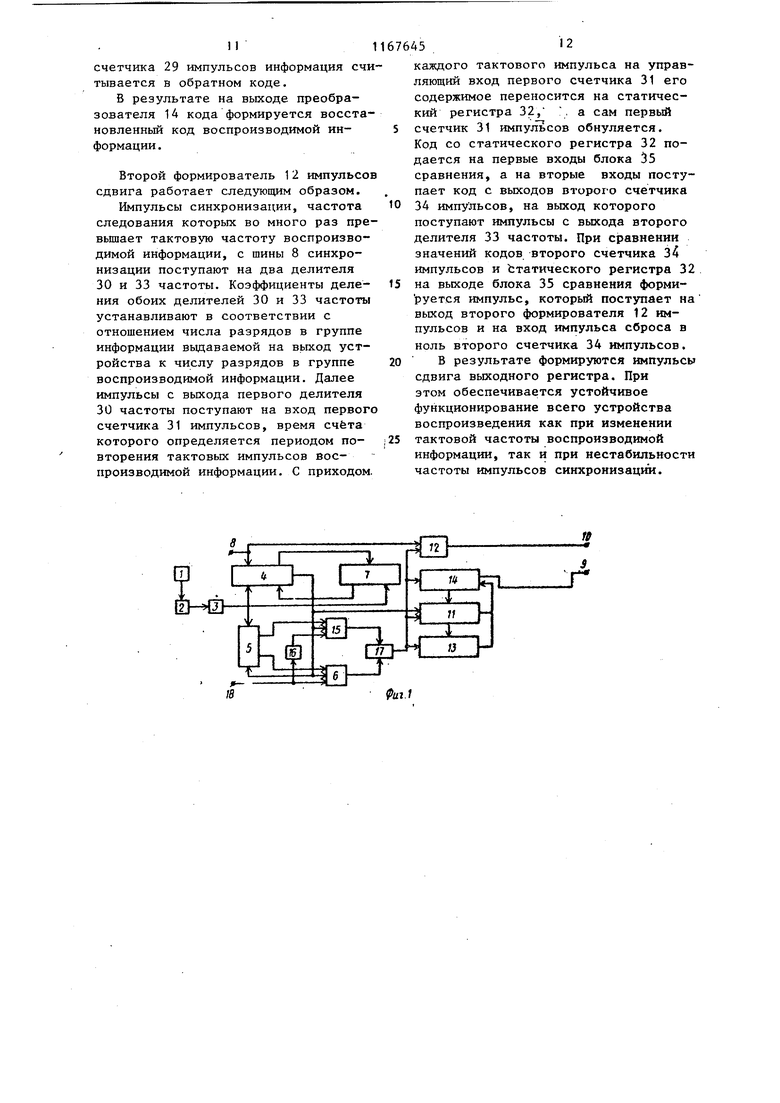

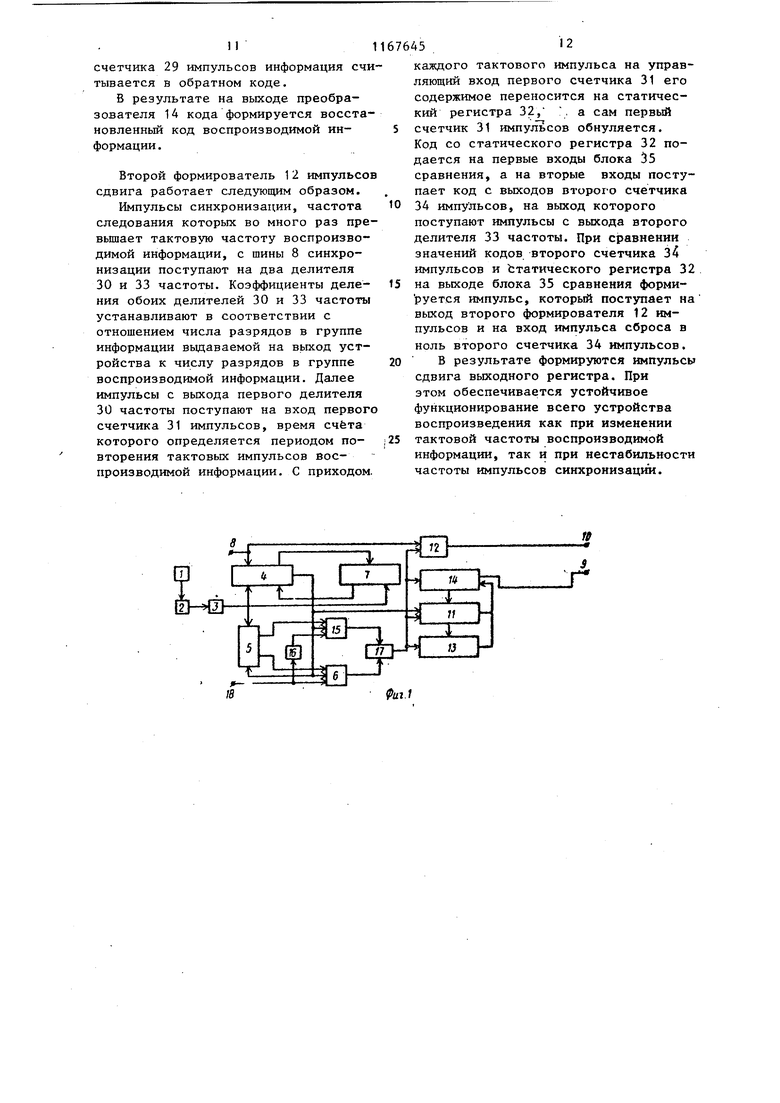

Поставленная цель достигается тем, что в устройство для воспроизведения цифровой информации, содержащее последовательно соединенные усилитель воспроизведения, дифференциатор и первый формирователь импульсов, подключенный выходом к входу считывания счетчика импульсов и к первому входу триггера, вторым входом соединенного с первым выходом счетчика импульсов и с первым входом первого элемента И, подключенного вторым входом к первому выходу триггера, регистр, первым и вторым входами и выходом подсоединенный соответственно к первому входу триггера, к второму выходу и к установочному входу счетчика импу сов, соединенного счетным входом с шиной синхронизации, первую и вторую выходные шины, введены регистр сдвига, второй формирователь импуль сов, формирователь импульсов синхронизации, преобразователь кода, второй элемент И и элементы НЕ и ИЛ причем преобразователь кода и второй формирователь импульсов подключены выходами к первой и второй выходным шинам, а информационными вхо дами подсоединены к информационным входам регистра сдвига и формирователя импульсов синхронизации и к выходу элемента ИЛИ, второй формирователь импульсов подключен входом к шине синхронизации, формирователь импульсов синхронизации подключен выходом к входам считывания регистра сдвига и преобразователя кода, регистр сдвига подключен выходами к входам преобразователя кода и выходами первого и последнего разрядов к входам формирователя импульсо синхронизации, а синхронизирующим входом - к первому выходу счетчика импульсов, соединенного входами с выходами первого и второго эл:ементо И, при этом второй элемент И подключен первым входом к первому входу первого элемента И, вторым входом - к второму выходу триггера, а третьим входом подсоединен через элемент НЕ к третьему входу первого элемента И и к шине управления. При этом формирователь импульсов синхронизации содержит последовател но соединенные счетчик импульсов, дешифратор и элемент НЕ, первый и второй элементы И, причем счетчик импульсов соединен входами с выхода ми первого и второго элементов И, элемент НЕ подключен выходом к первому входу первого элемента И, втор вход которого является синхронизи454рующим входом формирователя импульсов синхронизации, дешифратор соединен выходом с входом второго элемента И, остальные входы и выход которого являются входами и выходом формирователя импульсов синхронизации. Преобразователь кода содержит регистр сдвига, дешифратор, элемент НЕ, элемент И, формирователь сигнала обратной связи и счетчик импульсов, причем элемент НЕ соединен входом с выходом дешифратора, а выходом с первым входом элемента И, второй вход которого является синхронизирующим входом преобразователя кода, регистр сдвига соединен выходами первого и последнего разрядов с входами дешифратора и формирователя сигнала обратной связи, подключенного выходом к информационному входу регистра сдвига,подсоединенного выходами четных разрядов к дополнительным входам дешифратора, синхронизирующим входом - к выходу элемента И и к входу счетчика импульсов, соединенного входом считывания и установки с входом считывания и установки регистра сдвига, при этом входы разрядов регистра сдвига являются входами преобразователя кода, выходы регистра сдвига и счетчика импульсов являются выходом преобразователл кода, а вход считывания и установки счетчика импульсов йвляется входом считывания преобразователя кода. Второй формирователь импульсов содержит последовательно соединенные первьА делитель частоты, первый счетчик импульсов и статический регистр, последовательно соединенные второй делитель частоты и второй счетчик импульсов, и блок сравнения, причем блох сравнения подключен входами к выходам статического регистра и второго счетчика импульсов и выходом подсоединен к управляющему входу второго формирователя счетчика импульсов, являющегося выходом второго формирователя импульсов, первый делитель частоты соединен входом с входом второго делителя частоты, являющегося входом второго формирователя импульсов, а синхронизирующий вход первого счетчика импульсов является синхронизирующим входом второго формирователя импульсов. Это приводит к повьшения верности воспроизведения цифровой информации . На фиг,1-4 приведены функциональные схемы устройства для воспро изведения цифровой информации, формирователя импульсов синхронизации, преобразователя кода и второго формирователя импульсов. Устройство для воспроизведения цифровой информации содержит последовательно соединенные усилитель 1 воспроизведения, дифференциатор 2 и первый формирователь 3 импульсов, подключенный выходом к входу считывания счетчика 4 импульсов и к первому входу триггера 5, вторым входом соединенного с первым выходом счетчика 4 импульсов и с первым входом первого элемента И 6, подключенного вторым входом к первому выходу триггера 5, регистр 7, первы и вторым входами и выходом подсоединенный соответственно к первому входу триггера 5, к второму выходу и к установочному входу счетчика 4 импульсов, соединенного счетным входом с шиной 8 синхронизации, первую и вторую выходные шины 9 и 1U, кроме того, содержит регистр 11 сдвига, второй формирователь 12 импульсов, формирователь 13 импульсов синхронизации, преобразователь 14 кода, второй элемент И 15 и элемент НЕ 16 и ШШ 17, причем преобразователь 14 кода и второй формирователь 12 импульсов подключены выходами к первой и второй выходным шинам 9 и 10, а информационными входами подсоединены к информационным входам регистра 11 сдвига и формироват ля 13 импульсов синхронизации и к выходу элемента ИЛИ 17, второй формирователь 12 импульсов подключен входом к шине 18 синхронизации, фор мирователь 13 импульсов синхронизации подключен выходом к входим считывания регистра 11 сдвига и преобразователя 14 кода, регистр 11 сдви га подключен выходами к входам преобразователя 14 кода и выходами первого и последнего разрядов к входам формирователя 13 импульсов синхронизации, а синхронизирующим входом - к первому выходу счетчика импульсов, соединенного входами с выходами первого и второго элементо И 6 и 15, при этом второй элемент И 1 5 15 подключен первым входом к первому входу первого элемента И 6, вторым входом - к второму выходу триггера 5, а третьим входом подсоединен через элемент НЕ 16 к третье- му входу первого элемента И 6 и к шине 18 синхронизации, При этом формирователь 13 импульсов синхронизации содержит последовательно соединенные счетчик 19 импульсов, дешифратор 20 и элемент НЕ 21, и первый и второй элементы И 22 и 23,.причем счетчик 19 импульсов соединен входами с выходами первого и второго элементов И 22 и 23, элемент НЕ 21 подключен выходом к первйму входу первого элемента И 22, второй вход которого является синхронизирующим входом формирователя 13 импульсов синхронизации, дешифратор 20 соединен выходом со входом второго элемента 23 остальные входы и выход которого являются входами и выходом формирователя 13 импульсов синхронизации, Кроме того, преобразователь 14 кода содержит регистр 24 сдвига, дешифратор 25, элемент НЕ 26, элемент И 27, формирователь 28 сигнала обратной связи и счетчик 29 импульсов, причем элемент НЕ 26 соединен входом с выходом дешифратора 25 и выходом с первым входом элемента И 27, второй вход которого является синхронизирующим входом преобразователя 14 кода, регистр 24 сдвига соединен выходами первого и последнего разрядов с входами дешифратора 25 и формирователя 28 сигнала обратной связи, подключенного выходом к информационному входу регистратора 24 сдвига, подсоединенного выходами четных разрядов к дополнительным входам дешифратора 25, синхронизируюш;им входом - к выходу элемента И 27 и к входу счетчика 29 импульсов, соединенного входоц считывания и установки с входомсчитывания и установки регистра 24 сдвига, при этом входы разрядов регистра 24 сдвига являются входами преобразователя 14 кода, выходы регистра 24 сдвига и счетчика 29 импульсов являются выходом преобразователя 14 кода, а вход считывания и установки счетчика 29 импульсов является входом считьшания преобразователя 14 кода, а второй формирователь 12 импульсов содержит последовательно соединенные

первый делитель 30 частоты, первый счетчик 31 импульсов и статический регистр 32, последовательно соединенные делитель 33 частоты и второй счетчик 34 импульсов, и блок 35 , сравнения, причем блок 35 сравнения подключен входами к выходам статичеокого регистра 32 и второго счетчика 33 импульсов и выходом подсоединен к управляющему входу второго счетчика 34 импульсов, являющегося выходом второго формирователя 12 импульсов, первыйделитель 30 частоты соединен входом с входом второго делителя 33 частоты, являющегося входом второго формирователя 12 импульсов, а синхронизирующий вход первого счетчика 31 импульсов является синхронизирующим входом второго формирователя 12 импульсов.

Устройство для воспроизведения цифровой информации обеспечивает воспроизведение цифровой информации, подвергнутой при записи перекодированию, для получения двухчастотного сигнала с однозначным представлен ием информации сигналом записи с по- вышенной устойчивостью, и возможностью тактовой и групповой синхронизации как при записи прямым сигналом, так и модифицированным сигналом повышенной информационной емкости.

Результат воспроизведения записан ного сигнала, поступающий из усилителя 1 воспроизведения, дифференцируется в дифференциаторе 2 и подается на первый формирователь 3 им ульсов, с выхода которого сигнал поступает на триггер 5, и счетчик 4 импульсов, в котором осуществляется компенсация фазовых искажений воспроизведенного сигнала, формирование тактовых импульсов Воспроизведенной информации и информационных импульсов, соответствующих прохождению перепадов в сигнале записи. В случае воспроизведения модифицированного сигнала записи и при подаче на корректор соответствующего сигнала управления с щины 18 управления информационные импульсы, на выходе счетчика 4 импульсов формируются в тех тактах сигнала воепроизводимой информации, в которых перепады сигнала записи не происходили.

С выхода счетчика 4 импульсов информация записывается в регистр 11 сдвига, число разрядов в котором на один больше, чем число тактов в периоде повторения перепадов групповой синхронизации в сигнале записи. При появлении на входе фор-мирователя 13 импультя синхронизации сигналов первого и последнего дзазрядов регистра-11 сдвига, соответствующих прохождению перепадов групповой синхронизации и тактового импульса воспроизводимой информации, на выходе формирователя 13 импульсов синхронизации формируется импульс опроса регистра 11 сдвига и запуска преобразователя 14 кода.

При запуске преобразователя 14 кода с НеУо на первую выходную шину 9 поступает декодированная в предьвдущем цикле воспроизведенная информация, и под действием тактовых сигналов выполняется очередной цикл преобразования воспроизведенной информации. По окончании преобразования полученная информация хранится в преобразователе до прихода следующего импульса групповой синхронизации.

Второй формирователь 12 импульсов обеспечивает формирование импульсов сдвига с частотой следования соотносящейся с частотой тактовых импульсов воспроизводимой информации в точном соответствии с сботношением числа разрядов в группе информации, выдаваемой на выход устройства ив - . группе воспроизведенной информации. Для формирования импульсов сдвига с необходимыми характеристиками и синхронизации с работой всего устройства на вход второго формирователя 12 импульсов подаются сивхрочастота с шины 8 синхронизации и тактовые импульсы воспроизведенной информации с выхода элемента ИЛИ 17.

Входной импульс, соответствующий наличию перепада в сигнале записи, поступает с выхода первого формирователя 3 импульсов, на опрос счетчика 4 импульсов, который осуществляет счет синхросигналов времени. По входному импульсу результат просчета со счетчика 4 импульсов поступает на регистр 7 со сдвигом на один разряд в сторону младших разрядов. При этом сохраняется состояние старшего разряда, gi в соседний с ним записьтается его инверсное значение. 9 Полученный результат возвращается н счетчик 4 импульсов. Одновременно по входному импульсу запускается триггер 5. Сигнал переполнения счет чика 4 импульсов поступает на. вход регистра 11 сдвига как тактовый импульс воспроизводимой информации, а также на опрос первого и второго элементов И 6 и 15 и на сброс триггера 5. Управление элементами И 6 и 15 осуществляется от шины 18 управления. В результате при наличии сиг нала управления работать будет второй элемент И 15, подключенный к нулевому плечу триггера, а в отсу ствии сигнала управления работать б дет первый элемент И 6, подключенный к единичному плечу триггера 5. Сигнал с выходов первого и второго элементов И 6 и 15 проходит через элемент ИЛИ 17 и поступает на вход регистра 11 сдвига как информационный сигнал. При этом этот информаци онный сигнал будет вьщаваТься в тех тактах, когда был импульс на выходе первого формирователя 3 импульсов, если сигнал управления отсутствует и в тактах, когда импульс на выходе первого формирователя 3 импульсов не появлялся, если сигнал управления поступает на шину управления. Формирователь 13 импульсов синхронизации работает следующим образом. Тактовые импульсы воспроизводимой информации поступают н; один из входов первого элемента И 22, на др гой вход которого поступает сигнал разрешения с элемента НЕ 21. Пройди первый элемент И 22 тактовые импульсы поступают на счетный вход счетчика 19 импульсов, выходы разрядов которого соединены с входами дешифратора 20. При появлении на счетчике 21 импульсов числа, соответствующего числу тактов в периоде цовторения перепадов групповой синхронизации в сигнале записи, и коду, на который настроен дешифратор 20, на выходе последнего появляется сигнал, который вьщает разрешени на второй элемент И 23, и через элемент НЕ 21 запирает первый элемент И 22. Если в этом такте на вход формирователя 13 импульсов синхронизации поступают сигналы информации с регистра 11 сдвига, со ответствующие прохождению импульсов 45 групповой синхронизации, то на выходе второго элемента И 23 формируется импульс групповой синхронизации, который поступает на выход формирователя 13 импульсов синхронизации и на сброс счетчика 19 импульсов. Если же на других входах второго элемента И 23 сигналы отсутствуют, то формирователь 13 импульсов остается во взведенном положении до такта, когда одновременно появятся сигналы на втором и третьем входах второго элемента И 23 и только тогда произойдет формирование импульса групповой синхронизации. В случае, когда импульс групповой синхронизации формируется не в нужном такте либо при сбое системы воспроизведения, либо при начальном включении, описанная схема проведет самокорректировку и будет вьщавать импульсы групповой синхронизации в тактах, соответствующих их прохождению. Преобразователь. 14 кода воспроиз-. водимой информации работает следующим образом. Преобразуемый код воспроизводимой информации по сигналу групповой синхронизации заносится параллельно в регистр 24 сдвига. На вход регистра 24 сдвига поступают импульсы сдвига, которые проходят с входа преобразователя 14 кода через элемент И 27. Эти же импульсы сдвига поступают и на вход счетчика 29 импульсов. При осуществлении каждой операции сдвига содержимое счетчика 29 импульсов увеличивается на единицу, а в освобождающийся младший разряд регистра 24 сдвига записывается значение, формируемое формирователем 28 сигнала обратной связи. При одновременном появлении во всех четных и в последнем разряде 26 сдвига кодовых единиц, а в первом разряде кодового нуля, на выходе дешифратора 25 появится сигнал, свидетельствующий об окончании цикла преобразования кода возпроизведенной информации. Теперь при поступлении на вход преобразователя 14 кода очередного импульса групповой синхронизации, сопровождающего очередную группу разрядов преобразуемой инфорг мации, происходит опрос нечетных, кроме первого и последнего, разрядов регистра 24 сдвига и разрядов счетчика 30 импульсов. При этом со

счетчика 29 импульсов информация считывается в обратном коде.

В результате на выходе преобразователя 14 кода формируется восстановленный код воспроизводимой ИИформации.

Второй формирователь 12 импульсов сдвига работает следующим образом.

Импульсы синхронизации, частота следования которых во много раз превышает тактовую частоту воспроизводимой информации, с шины 8 синхронизации поступают на два делителя 30 и 33 частоты. Коэффициенты деления обоих делителей 30 и 33 частоты устанавливают в соответствии с отношением числа разрядов в группе информации вьщаваемой на вьгход устройства к числу разрядов в группе воспроизводимой информации. Далее импульсы с выхода первого делителя 30 частоты поступают на вход первого счетчика 31 импульсов, время счёта которого определяется периодом повторения тактовых импульсов воспроизводимой информации. С приходом.

каждого тактового импульса на управляющий вход первого счетчика 31 его содержимое переносится на статический регистра 32, , а сам первый счетчик 31 импульсов обнуляется. Код со статического регистра 32 подается на первые входы блока 35 сравнения, а на вторые входы поступает код с выходов второго счетчика 34 импульсов, на выход которого поступают импульсы с выхода второго делителя 33 частоты. При сравнении значений кодов второго счетчика 34 импульсов и Статического регистра 32 на выходе блока 35 сравнения формируется импульс, который поступает на выход второго формирователя 12 импульсов и на вход импульса сброса в

ноль второго счетчика 34 импульсов.

В результате формируются импульсы сдвига выходного регистра. При этом обеспечивается устойчивое функционирование всего устройства воспроизведения как при изменении тактовой частоты воспроизводимой информации, так и при нестабильности частоты импульсов синхронизации.

Инп -групп

ФигЗ синхр

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сб | |||

| Вопросы радиоэлектроники, сер | |||

| ЭВТ, вып | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ воспроизведения цифровой ин-фОРМАции C НОСиТЕля МАгНиТНОй зАпиСии уСТРОйСТВО для ЕгО ОСущЕСТВлЕНия | 1979 |

|

SU838719A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-07-15—Публикация

1984-02-27—Подача