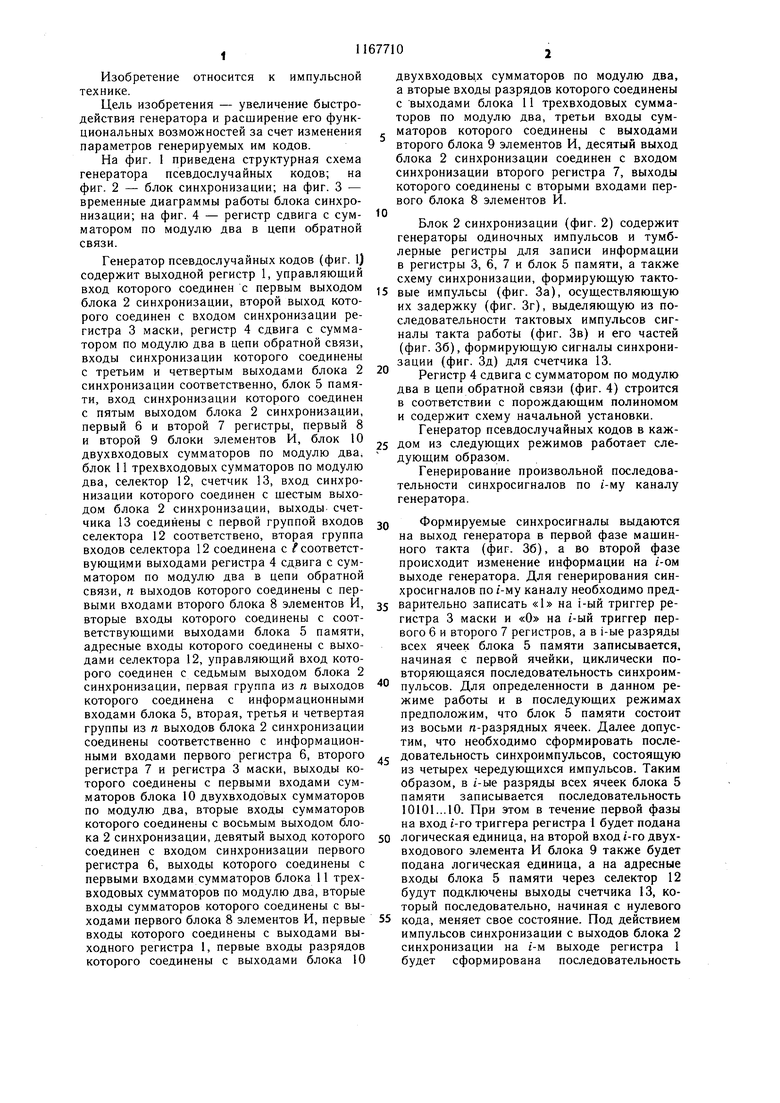

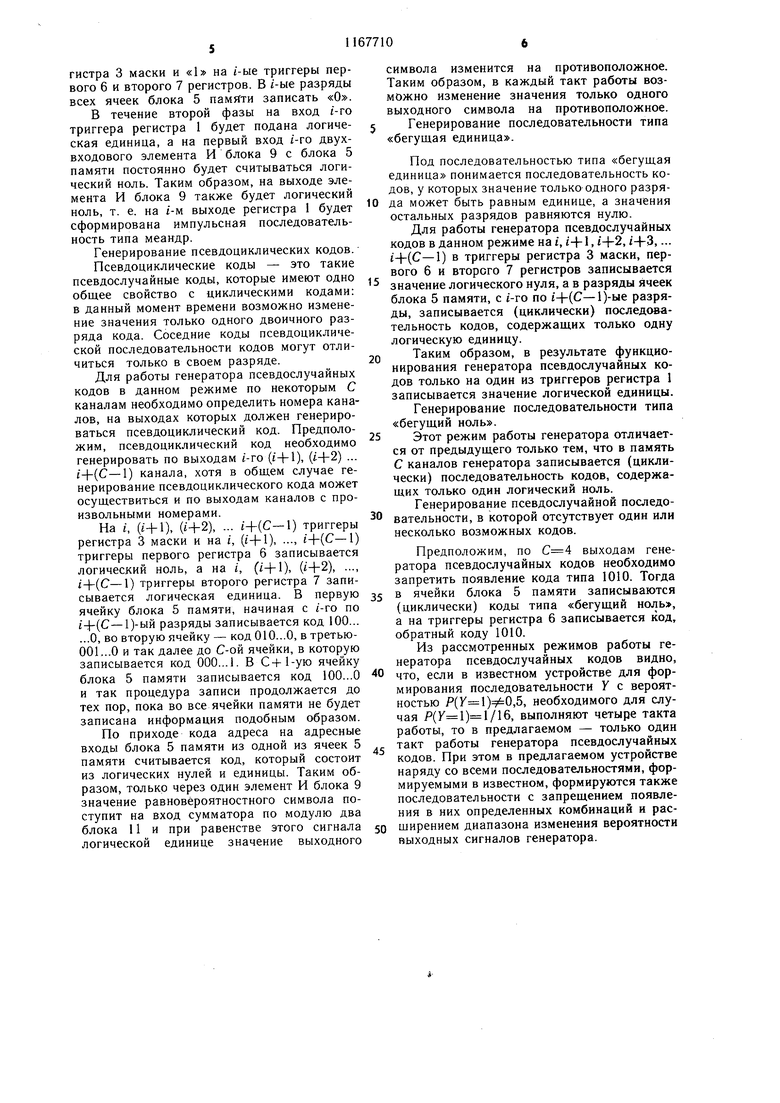

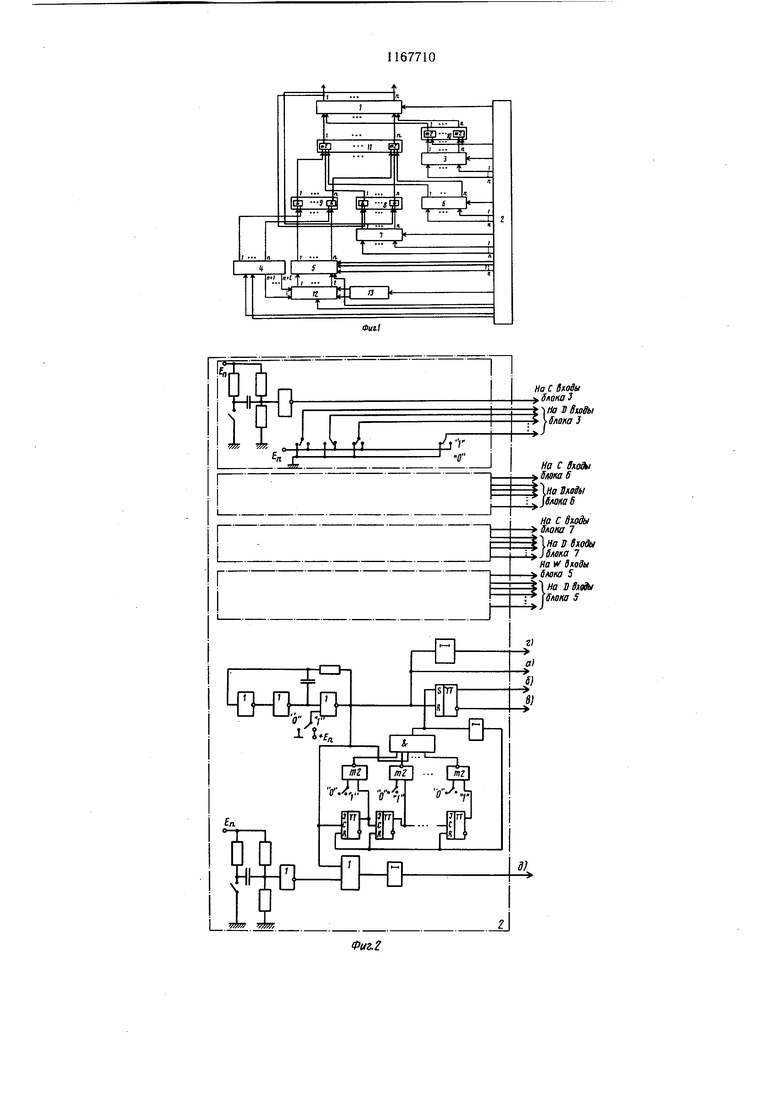

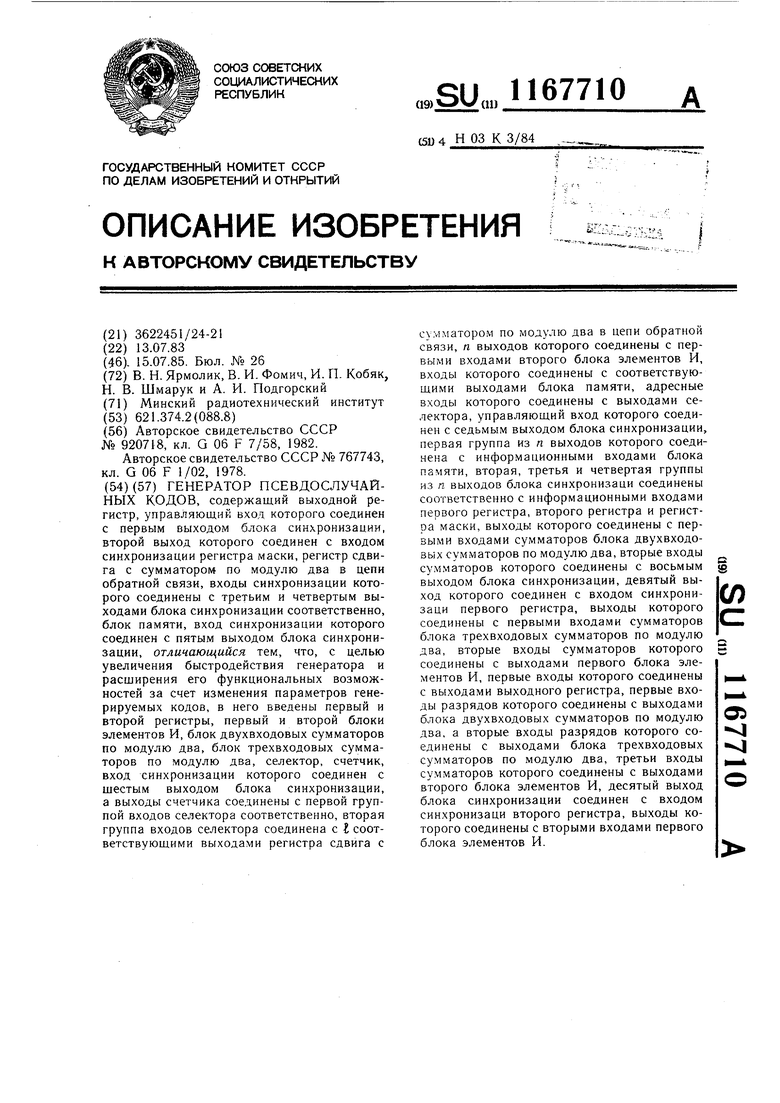

Изобретение относится к импульсной технике. Цель изобретения - увеличение быстродействия генератора и расширение его функциональных возможностей за счет изменения параметров генерируемых им кодов. На фиг. 1 приведена структурная схема генератора псевдослучайных кодов; на фиг. 2 - блок синхронизации; на фиг. 3 - временные диаграммы работы блока синхронизации; на фиг. 4 - регистр сдвига с сумматором по модулю два в цепи обратной связи. Генератор псевдослучайных кодов (фиг. 1) содержит выходной регистр 1, управляющий вход которого соединен с первым выходом блока 2 синхронизации, второй выход которого соединен с входом синхронизации регистра 3 маски, регистр 4 сдвига с сумматором по модулю два в цепи обратной связи, входы синхронизации которого соединены с третьим и четвертым выходами блока 2 синхронизации соответственно, блок 5 памяти, вход синхронизации которого соединен с пятым выходом блока 2 синхронизации, первый 6 и второй 7 регистры, первый 8 и второй 9 блоки элементов И, блок 10 двухвходовых сумматоров по модулю два, блок 11 трехвходовых сумматоров по модулю два, селектор 12, счетчик 13, вход синхронизации которого соединен с шестым выходом блока 2 синхронизации, выходы счетчика 13 соединены с первой группой входов селектора 12 соответствено, вторая группа входов селектора 12 соединена с соответствующими выходами регистра 4 сдвига с сумматором по модулю два в цепи обратной связи, п выходов которого соединены с первыми входами второго блока 8 элементов И, вторые входы которого соединены с соответствующими выходами блока 5 памяти, адресные входы которого соединены с выходами селектора 12, управляющий вход которого соединен с седьмым выходом блока 2 синхронизации, первая группа из п выходов которого соединена с информационными входами блока 5, вторая, третья и четвертая группы из п выходов блока 2 синхронизации соединены соответственно с информационными входами первого регистра 6, второго регистра 7 и регистра 3 маски, выходы которого соединены с первыми входами сумматоров блока 10 двухвходовых сумматоров по модулю два, вторые входы сумматоров которого соединены с восьмым выходом блока 2 синхронизации, девятый выход которого соединен с входом синхронизации первого регистра 6, выходы которого соединены с первыми входами сумматоров блока 11 трехвходовых сумматоров по модулю два, вторые входы сумматоров которого соединены с выходами первого блока 8 элементов И, первые входы которого соединены с выходами выходного регистра 1, первые входы разрядов которого соединены с выходами блока 10 двухвходовых сумматоров по модулю два, а вторые входы разрядов которого соединены с выходами блока 11 трехвходовых сумматоров по модулю два, третьи входы сумматоров которого соединены с выходами второго блока 9 элементов И, десятый выход блока 2 синхронизации соединен с входом синхронизации второго регистра 7, выходы которого соединены с вторыми входами первого блока 8 элементов И. Блок 2 синхронизации (фиг. 2) содержит генераторы одиночных импульсов и тумблерные регистры для записи информации в регистры 3, 6, 7 и блок 5 памяти, а также схему синхронизации, формирующую тактовые импульсы (фиг. За), осуществляющую их задержку (фиг. Зг), выделяющую из последовательности тактовых импульсов сигналы такта работы (фиг. Зв) и его частей (фиг. 36), формирующую сигналы синхронизации (фиг. Зд) для счетчика 13. Регистр 4 сдвига с сумматором по модулю два в цепи обратной связи (фиг. 4) строится в соответствии с порождающим полиномом и содержит схему начальной установки. Генератор псевдослучайных кодов в каждом из следующих режимов работает следующим образом. Генерирование произвольной последовательности синхросигналов по г-му каналу генератора. Формируемые синхросигналы выдаются на выход генератора в первой фазе машинного такта (фиг. 36), а во второй фазе происходит изменение информации на /-ом выходе генератора. Для генерирования синхросигналов по г-му каналу необходимо предварительно записать «1 на i-ый триггер регистра 3 маски и «О на /-ый триггер первого 6 и второго 7 регистров, а в i-ые разряды всех ячеек блока 5 памяти записывается, начиная с первой ячейки, циклически повторяющаяся последовательность синхроимпульсов. Для определенности в данном режиме работы и в последующих режимах предположим, что блок 5 памяти состоит из восьми я-разрядных ячеек. Далее допустим, что необходимо сформировать последовательность синхроимпульсов, состоящую из четырех чередующихся импульсов. Таким образом, в г-ые разряды всех ячеек блока 5 памяти записывается последовательность 10101... 10. При этом в течение первой фазы на вход t-ro триггера регистра 1 будет подана логическая единица, на второй вход г-го двухвходового элемента И блока 9 также будет подана логическая единица, а на адресные входы блока 5 памяти через селектор 12 будут подключены выходы счетчика 13, который последовательно, начиная с нулевого кода, меняет свое состояние. Под действием импульсов синхронизации с выходов блока 2 синхронизации на г-м выходе регистра 1 будет сформирована последовательность

синхроимпульсов, состоящая из четырех импульсов.

Геиерирование псевдослучайной последовательности К с вероятностью P(Y- 1 - 0,5 по г-му каналу генератора.

Изменение информации на /-ом триггере выходного регистра 1, т. е. изменение значения Y будет происходить при этом во второй фазе такта работы генератора.

Для генерирования псевдослучайной последовательности Y с вероятностью P(Y 0,5 по /-му каналу предварительно необходимо записать «О на i-ые триггера регистра 3 маски, первого 6 и второго 7 регистров, а в /-ые разряды всех ячеек блока 5 памяти записать значения единицы.

В течение второй фазы на вход г-го триггера регистра 1 будет подана логическая единица и на первый вход /-го двухвходового элемента И блока 9 с блока 5 памяти постоянно будет считываться логическая единица. На второй вход /-го элемента И блока 9 с г-го разряда регистра 4 во второй фазе такта работы будет подаваться значение равновероятностной двоичной цифры R(Xi 1)0,5, значение которой в каждом такте работы записывается в t-ый разряд выходного регистра 1.

Генерирование псевдослучайных последовательностей Y с вероятностью Р() 0,5 по г-му каналу генератора.

Для генерирования псевдослучайной последовательности Ус вероятностью P(Y) ,5 по г-му каналу предварительно необходимо записать «О на г-ые триггеры регистра 3 и второго регистра 7. На i-ый триггер первого регистра б записывается «О, если R()0,5 и записывается «1, если R()0,5.

Для случая, когда Р();0,5, в г-ые разряды всех ячеек блока 5 памяти записывается такое количество единиц, которое определяется заданной вероятностью R(Y 1). Рассматриваемый генератор позволяет задавать любую вероятность Р() из следующего ряда вероятностей:

О JL -2. fcl ь biJ 2b-2 2bil ,

2Ь 2Ь 2Ь гЬ 2Ь 2Ь 2Ь 2Ь

где b - количе.. во ячеек памяти блока 5 памяти.

Любую вероятность при этом можно представить в следующем виде:

Р(), если )0,5 Р()1-, если Р()0,5

.

Величина g определяет количество единиц, которое необходимо записать в г-ые разряды всех ячеек памяти.

В течение второй фазы на вход г-го триггера регистра 1 будет подана логическая

единица. На первый вход г-го трехвходового сумматора по модулю два блока 11 подана логическая единица, на второй - логический ноль, на третий вход подключен выход г-го элемента И блока 9, на первый вход которого подключен г-ый выход регистра 4 а на второй вход - г-ый выход блока 5 памяти, на адресные входы которого подключены { выходов регистра 4.

Так как адрес ячейки памяти задается

0 регистром 4, то с равной вероятностью считывается содержимое той или иной ячейки памяти блока 5, т. е. P(Z| 1) будет определяться количеством ячеек памяти блока 5 и количеством записанных в них единиц. 5 В общем случае P() ig 0,Ь. где b - количество ячеек блока 5 памяти.

Можно показать, что

P()P().P(X,)-|-.|.

Так как на один из входов трехвходо0вого сумматора по модулю два подана логическая единица, то

P()1-P() .

Генерирование псевдослучайной последовательности У с вероятностью Р(У 1)0,5 5 по г-ому каналу генератора и с вероятностью R{f) изменения выходного сигнала У на противоположный в каждом такте работы генератора.

Для организации работы генератора 0 псевдослучайных кодов в данном режиме предварительно необходимо записать «О на г-ые триггеры регистров 3 маски и первого регистра 6. На г-ый триггер второго регистра 7 записывается «1.

Вероятность P(f) изменения выходного сигнала У на противоположный в каждом такте работы генератора определяется величиной

P(/)P()P(Z, l)-P(X,)-f-X

4xJ.J

- 2 2Ь

40

При этом выход г-го триггера регистра 1 через г-ый элемент И блока 8 подключается к входу трехвходового сумматора по модулю два блока 11. Таким образом, г-ый триггер

регистра 1 вместе с сумматором по модулю два блока 11 представляет собой триггер со счетным входом, который меняет свое состояние на противоположное только в том случае, когда на его вход поступает логическая единица.

0 Таким образом, на выходе г-го канала генератора генерируется последовательность У с вероятностью Р()0,5 и с вероятностью изменения выходного сигнала на противоположный Р(/).

Генерирование импульсной последователь5 ности типа меандр.

Для работы генератора псевдослучайных кодов в данном режиме необходимо предварительно записать «О на i-ый триггер регистра 3 маски и «1 на г-ые триггеры первого 6 и второго 7 регистров. В i-ые разряды всех ячеек блока 5 памяти записать «О.

В течение второй фазы на вход t-ro триггера регистра I будет подана логическая единица, а на первый вход i-ro двухвходового элемента И блока 9 с блока 5 памяти постоянно будет считываться логический ноль. Таким образом, на выходе элемента И блока 9 также будет логический ноль, т. е. на t-м выходе регистра 1 будет сформирована импульсная последовательность типа меандр.

Генерирование псевдоциклических кодов.

Псевдоциклические коды - это такие псевдослучайные коды, которые имеют одно общее свойство с циклическими кодами: в данный момент времени возможно изменение значения только одного двоичного разряда кода. Соседние коды псевдоциклической последовательности кодов могут отличиться только в своем разряде.

Для работы генератора псевдослучайных кодов в данном режиме по некоторым С каналам необходимо определить номера каналов, на выходах которых должен генерироваться псевдоциклический код. Предположим, псевдоциклический код необходимо генерировать по выходам i-ro (i+1), (t+2) ... (C-1) канала, хотя в общем случае генерирование псевдоциклического кода может осуществиться и по выходам каналов с произвольными номерами.

На i, (i-f 1), (1+2), ... J+(C-1) триггеры регистра 3 маски и на i, (i-f I), ..., i-}-(C-1) триггеры первого регистра 6 записывается логический ноль, а на г, (/+1), (/+2), ..., (C-1) триггеры второго регистра 7 записывается логическая единица. В первую ячейку блока 5 памяти, начиная с /-го по i+(C-1)-ый разряды записывается код 100... ...О, во вторую ячейку - код 010...О, в третью001...О и так далее до С-ой ячейки, в которую записывается код 000...1. В C-f 1-ую ячейку блока 5 памяти записывается код 100...О и так процедура записи продолжается до тех пор, пока во все ячейки памяти не будет записана информация подобным образом.

По приходе кода адреса на адресные входы блока 5 памяти из одной из ячеек 5 памяти считывается код, который состоит из логических нулей и единицы. Таким образом, только через один элемент И блока 9 значение равновероятностного символа поступит на вход сумматора по модулю два блока 11 и при равенстве этого сигнала логической единице значение выходного

символа изменится на противоположное. Таким образом, в каждый такт работы возможно изменение значения только одного выходного символа на противоположное. 5 Генерирование последовательности типа «бегущая единица.

Под последовательностью типа «бегущая единица понимается последовательность кодов, у которых значение только одного разряда может быть равным единице, а значения остальных разрядов равняются нулю.

Для работы генератора псевдослучайных кодов в данном режиме на i, г+1, /+2, /+3,... i+(C-1) в триггеры регистра 3 маски, первого 6 и второго 7 регистров записывается значение логического нуля, а в разряды ячеек блока 5 памяти, с i-ro по г+(С-1)-ые разряды, записывается (циклически) последовательность кодов, содержащих только одну логическую единицу.

Q Таким образом, в результате функционирования генератора псевдослучайных кодов только на один из триггеров регистра 1 записывается значение логической единицы. Генерирование последовательности типа «бегущий ноль.

5 Этот режим работы генератора отличается от предыдущего только тем, что в память С каналов генератора записывается (циклически) последовательность кодов, содержащих только один логический ноль.

Генерирование псевдослучайной последовательности, в которой отсутствует один или несколько возможных кодов.

Предположим, по выходам генератора псевдослучайных кодов необходимо запретить появление кода типа 1010. Тогда

5 в ячейки блока 5 памяти записываются (циклически) коды типа «бегущий ноль, а на триггеры регистра 6 записывается код, обратный коду 1010.

Из рассмотренных режимов работы генератора псевдослучайных кодов видно,

что, если в известном устройстве для формирования последовательности У с вероятностью P()tO,5, необходимого для случая Р()1/16, выполняют четыре такта работы, то в предлагаемом - только один

такт работы генератора псевдослучайных кодов. При этом в предлагаемом устройстве наряду со всеми последовательностями, формируемыми в известном, формируются также последовательности с запрещением появления в них определенных комбинаций и расширением диапазона изменения вероятности выходных сигналов генератора.

4. ... t

к блокам 9 , 12

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Генератор псевдослучайных кодов | 1978 |

|

SU767743A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Генератор псевдослучайных чисел | 1979 |

|

SU868734A1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| Генератор псевдослучайных последовательностей | 1983 |

|

SU1127079A1 |

| Генератор псевдослучайных последовательностей | 1981 |

|

SU1023325A1 |

| Устройство генерации равномерно распределенных псевдослучайных чисел | 2024 |

|

RU2840424C1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ КОДОВ, содержащий выходной регистр, управляющий вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с входом синхронизации регистра маски, регистр сдвига с сумматором по модулю два в цепи обратной связи, входы синхронизации которого соединены с третьим и четвертым выходами блока синхронизации соответственно, блок памяти, вход синхронизации которого соединен с пятым выходом блока синхронизации, отличающийся тем, что, с целью увеличения быстродействия генератора и расширения его функциональных возможностей за счет изменения параметров генерируемых кодов, в него введены первый и второй регистры, первый и второй блоки элементов И, блок двухвходовых сумматоров по модулю два, блок трехвходовых сумматоров по модулю два, селектор, счетчик, вход синхронизации которого соединен с шестым выходом блока синхронизации, а выходы счетчика сое.цинены с первой группой входов селектора соответственно, вторая группа входов селектора соединена с I соответствующими выходами регистра сдвига с сумматором по людулю два в цепи обратной связи, п выходов которого соединены с первыми входами второго блока элементов И, входы которого соединены с соответствующими выходами блока памяти, адресные входы которого соединены с выходами селектора, управляющий вход которого соединен с седьмым выходом блока синхронизации, первая группа из п выходов которого соединена с информационными входами блока памяти, вторая, третья и четвертая группы из п выходов блока синхронизаци соединены соответственно с информационными входами первого регистра, второго регистра и регистра маски, выходы которого соединены с первыми входами сумматоров блока двухвходовых сумматоров по модулю два, вторые входы I сум.маторов которого соединены с восьмым выходом блока синхронизации, девятый выел ход которого соединен с входом синхронизаци первого регистра, выходы которого соединены с первыми входами сумматоров блока трехвходовых сумматоров по модулю два, вторые входы сумматоров которого соединены с выходами первого блока элементов И, первые входы которого соединены с выходами выходного регистра, первые входы разрядов которого соединены с выходами О5 блока двухвходовых сумматоров по модулю два, а вторые входы разрядов которого соединены с выходами блока трехвходовых сумматоров по модулю два, третьи входы сумматоров которого соединены с выходами второго блока элементов И, десятый выход блока синхронизации соединен с входом синхронизаци второго регистра, выходы которого соединены с вторыми входами первого блока элементов И.

xj

v§

| Генератор псевдослучайных кодов | 1980 |

|

SU920718A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор псевдослучайных кодов | 1978 |

|

SU767743A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-15—Публикация

1983-07-13—Подача