Изобретение относится к вычислительной технике, в частности к аппаратуре контроля цифровых узлов вычислительных машин и средств цифровой автоматики.

Цель изобретения - увеличение глубины контроля за счет обеспечения контроля цифровых 641ОКОВ,входящих в состав контролируемого цифрового узла.

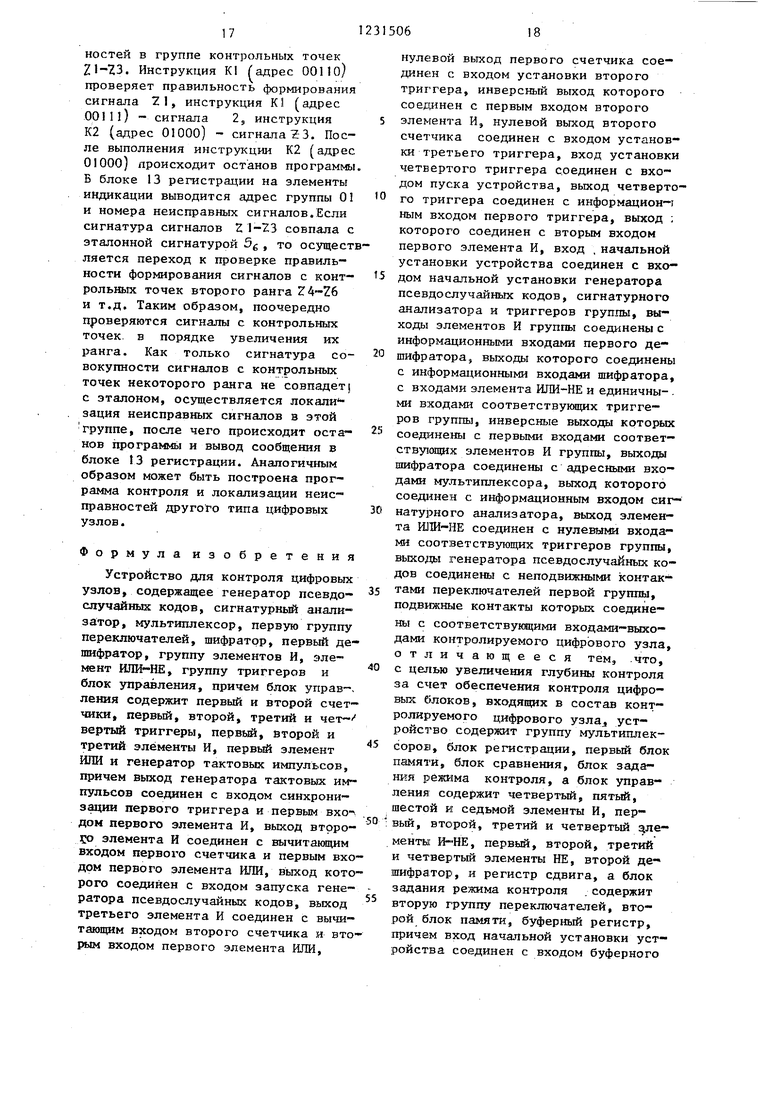

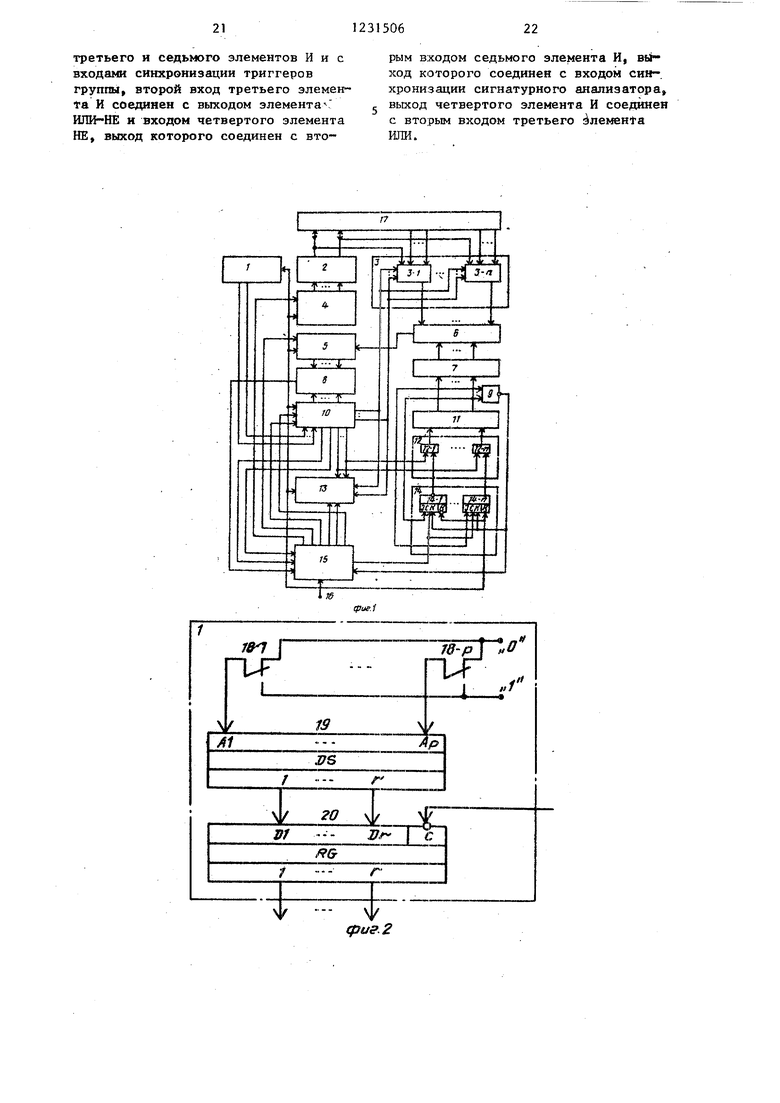

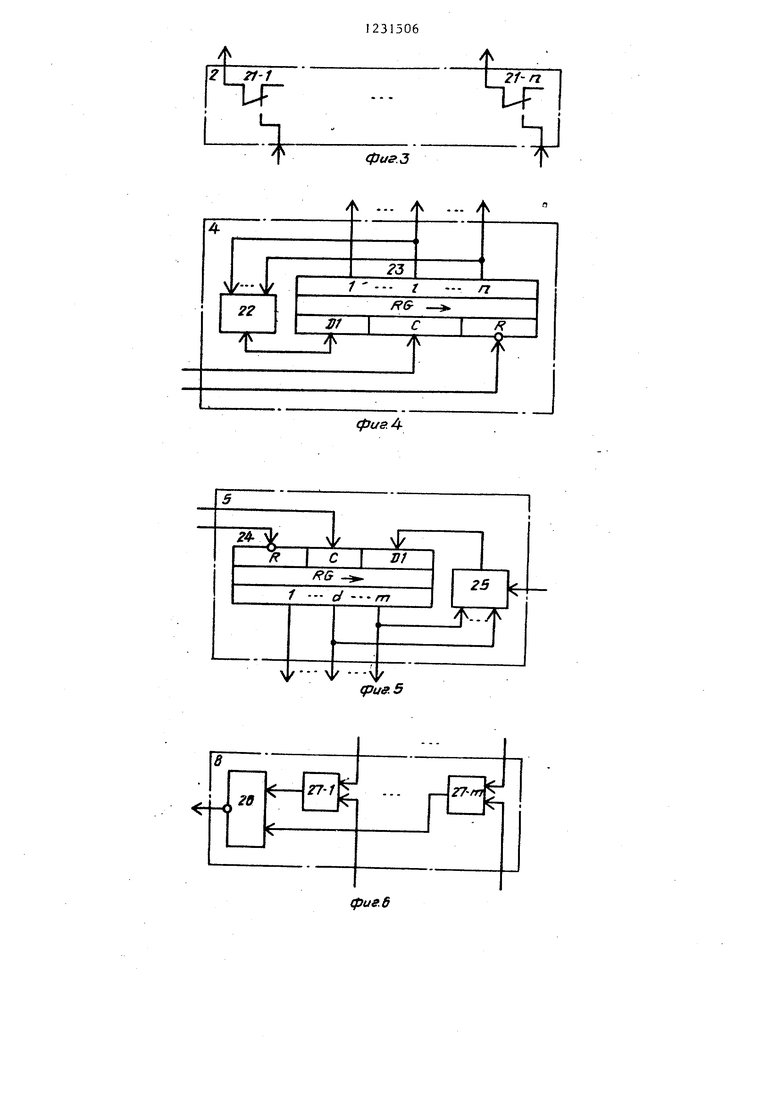

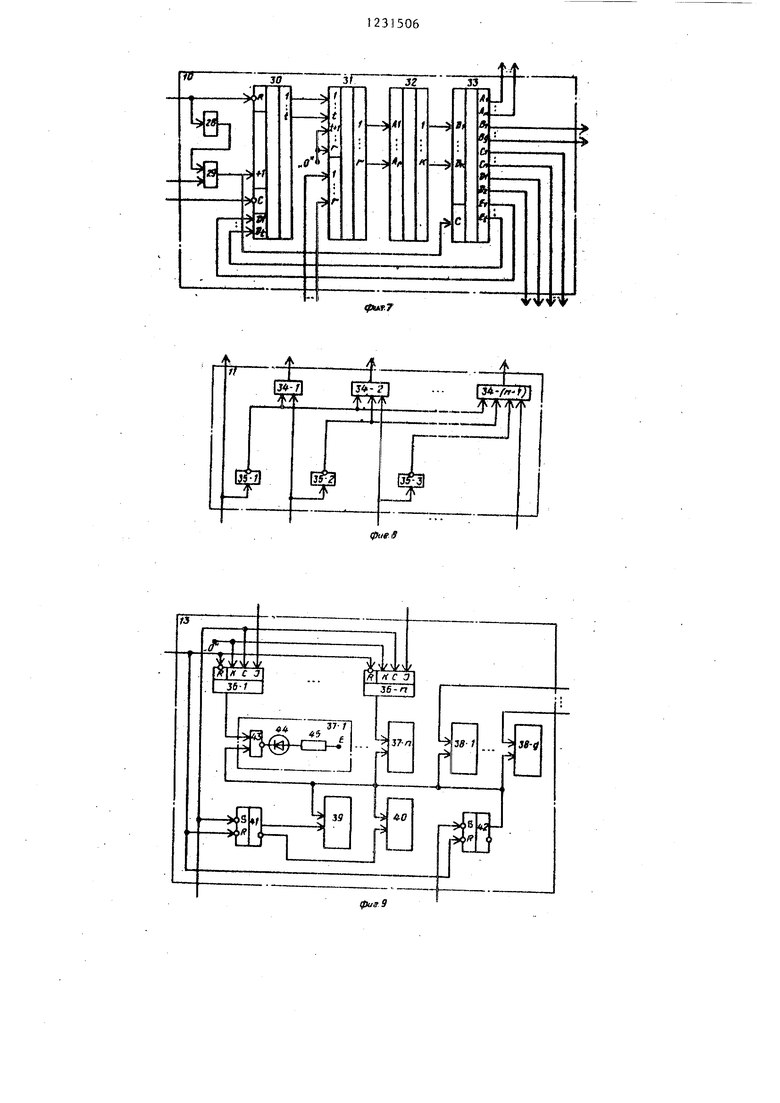

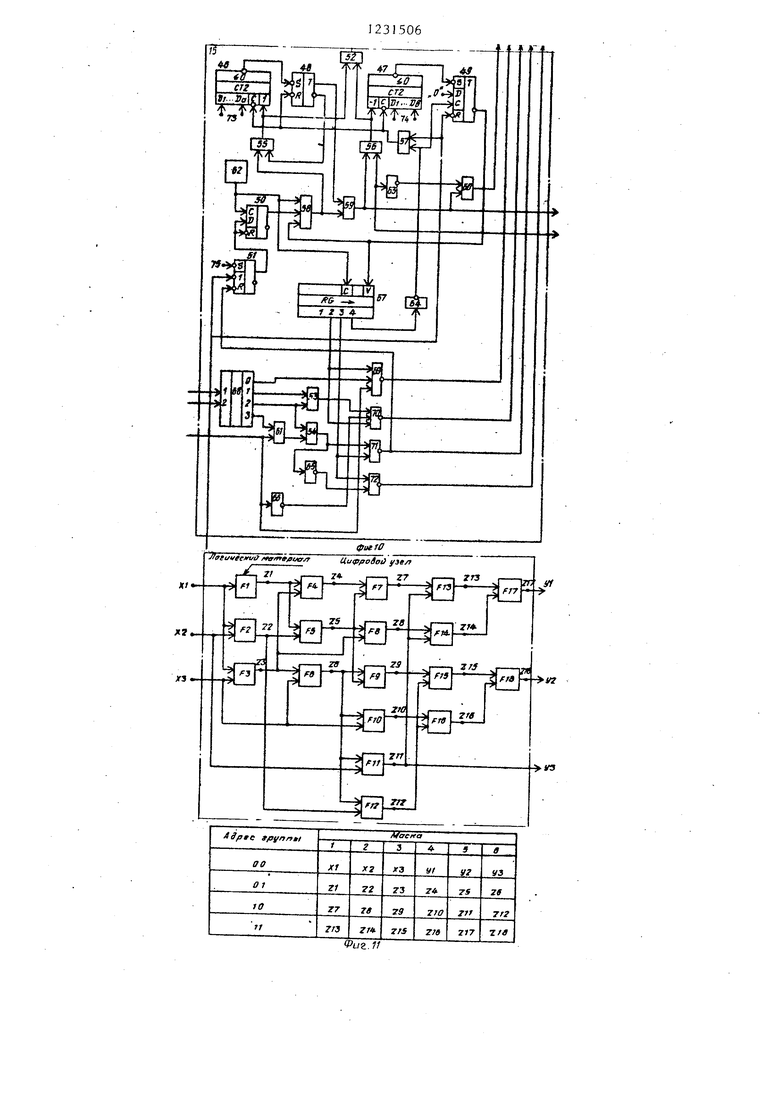

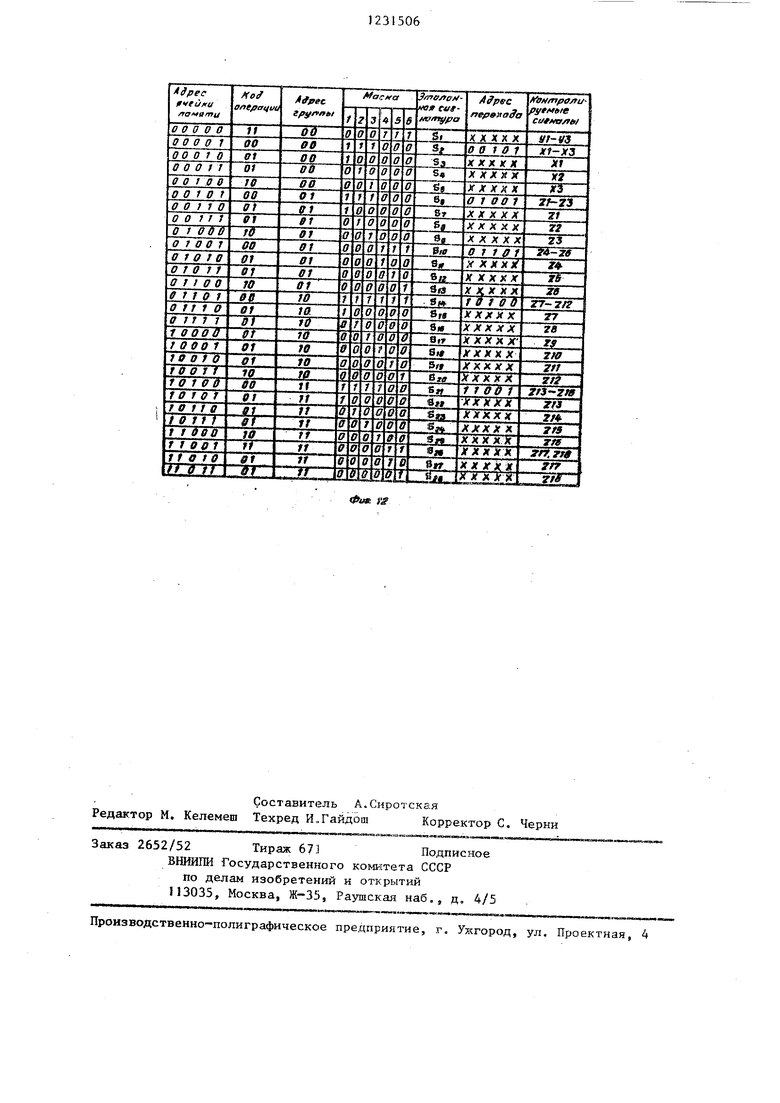

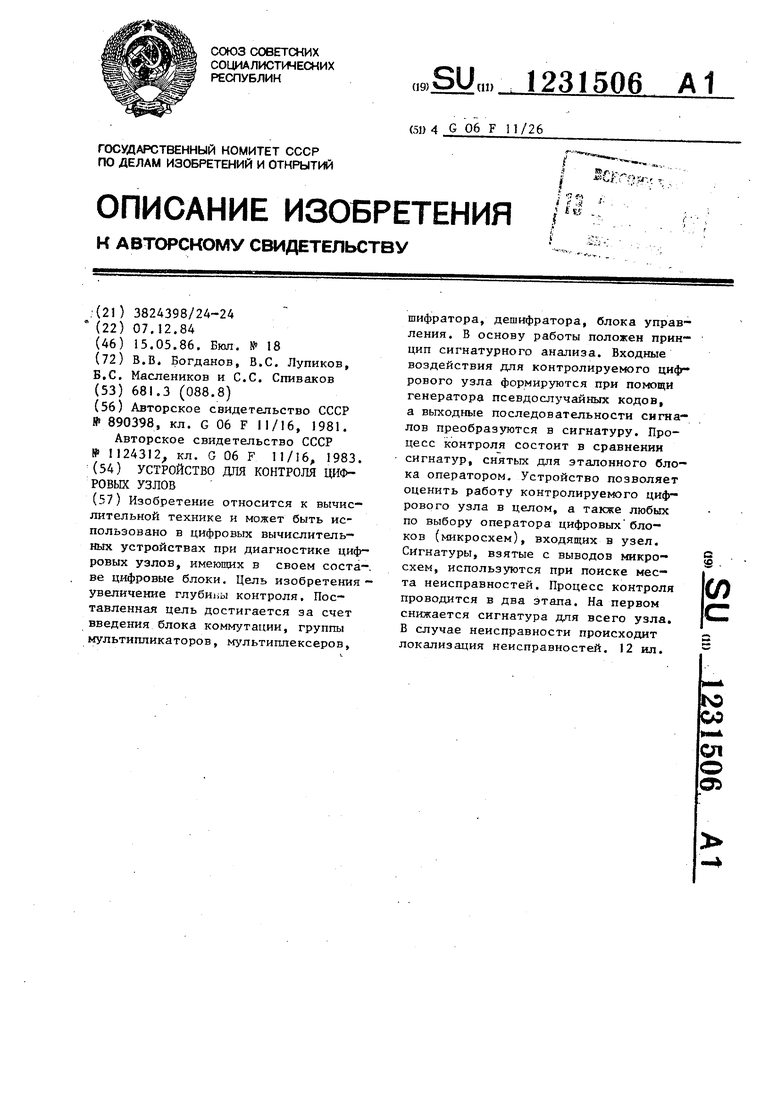

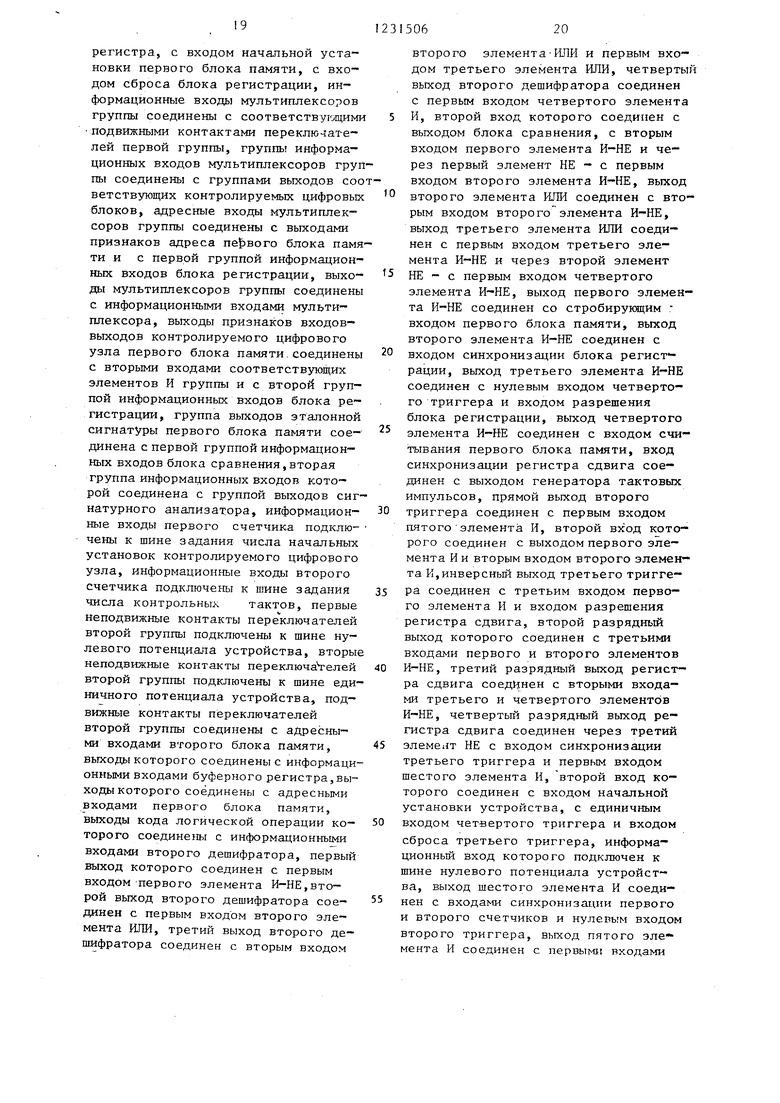

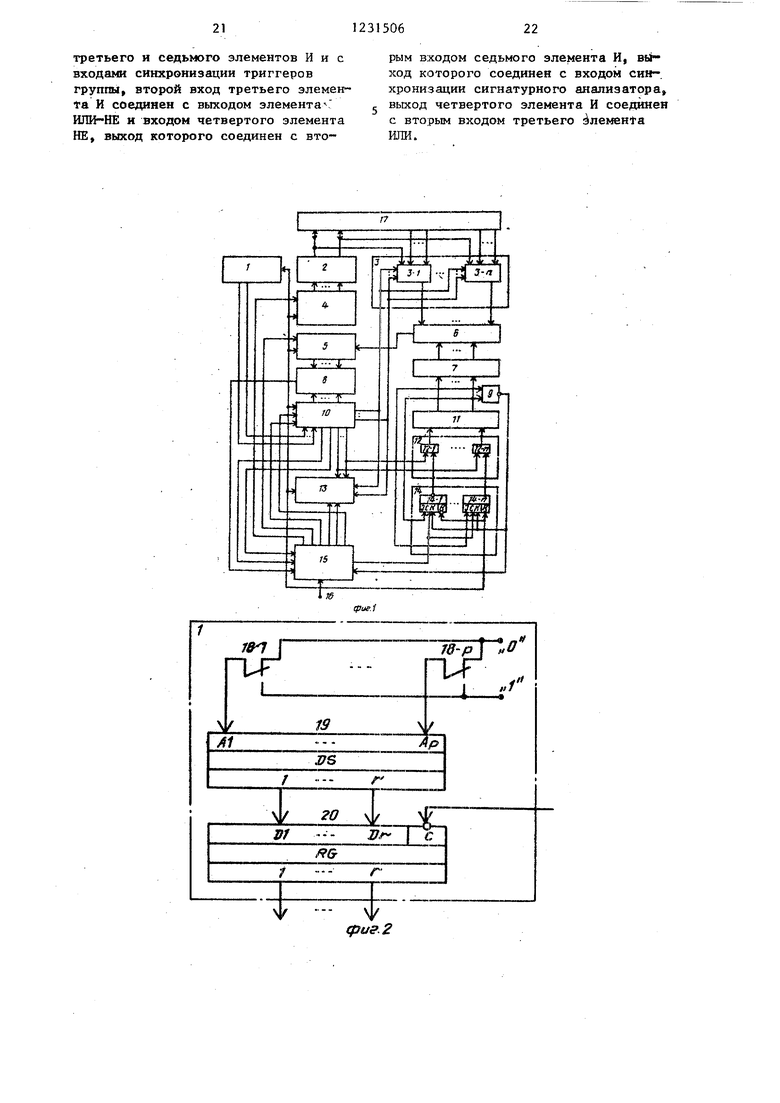

На фиг. приведена структурная схема устройства для контроля цифровых узлов; на фиг. 2 - пример технической реализации блока задания режима контроля; на фиг. 3 - то же, блока коммутации; на фиг. 4 - то же генератора псевдослучайных кодов; на фиг. 5 - то же, сигнатурного анализатора} на фиг. 6 - то же, блока сравнения} на фиг. 7 - то же, блока памяти} на фиг. 8 - то же, блока приоритетов} на фиг. 9 -тоже блока регистрации} на фиг. 10 - то же, блока управления} на фиг. 11 - пример контролируемого цифрового узла и таблица подключения его выходов, входов и контрольных точек к устройству} на фиг. 12 - программа контроля и локализации неисправностей в цифровом узле, схема ко торого представлена на фиг. П.

Устройство для контроля цифровых узлов (фиг. 1) содержит блок 1 задания режима контроля, блок 2 коммутации, группу мультиплексоров 3-1, 3-2,...,, генератор псевдослучайных кодов пек 4, сигнатурный анализатор 5, мультиплексор 6, шифратор 7, блок 8 сравнения, элемент ИЛИ-НЕ 9, блок 10 памяти, де- шифратор 11, группу элементов И 12-1, 12-2,. ..12-и, блок 13 регистрации, группу триггеров 14-1, 14-2,...,14-п, блок 15 управления, вход 16 начальной установки устройс ва (п - число входов и выходов контролируемого цифрового узла 17),

Блок 1 задания режима контроля содержит р переключателей 18-1, 18-2,...,18- р ( р - чиа1б режимов работы устройства), блок 19 памяти и буферный регистр 20 (фиг. 2).

Блок 2 ко 1утации содержит переключателей 21-1, 21-2,...,21- и (Фкг. 3).

Генератор ПСК 4 содержит сумматор 2 2 по модулю два и и,-разрядный ре- гастр 23 сдвига (фиг. 4).

Сигнатурный анализатор 5 содерит m -разрядный регистр 24 сдвиа и сумматор 25 по модулю два фиг. 5), где tn произвольное чисБлок 8 сравнения содержит элемент ЛИ-Н)3 26 и m сумматоров 27-1, 27-2, . . ., 7-т по модулю два (фиг.6).

Блок 10 памяти содержит элемент 28 за,цержки, элемент И 29, счетчик 30, сумматор 31, ПЗУ 32 и регистр 33

(фиг. 7).

Дешифратор 11.содержит И -Г элеменов И 34-1., 34-2, ...,34-Сп-) и n-i

лементов НЕ 35-1, 35-2,... ,35-(ti-l) фиг, 8).

Блок 13 регистрации содержит групп:)Г из п триггеров 36-1,36-2,..., 36-п, группу из п элементов индикации 37-1, 37-2,...,37-п, группу из и элементов индикации 38-1, 38-2, ..., 38-ff, первый 39 и второй 40 элементы индикации, первый 41 и втоой 42 триггеры (фиг.9, Ф - длина сигнатуры).

Элемент индикации блока 13 регистрации содержит элемент И-НЕ 43, све- тодиод 44 и резистор 45 fфиг. 9).

Блок 115 управления содержит счетчики 46 и 47, триггеры 48-51, элементы ИЛИ 52-54, элементы И 55-61, генератор 62 тактовых импульсов, элементы НЕ 63-66, регистр 67 сдвига, дешифратор 68, элементы И-НЕ 69-72, шину 73 задания числа начальных установок контролируемого цифрового узла, шину 74 задания числа контролы;1ьгх тактов, вход 75 запуска (фиг. 10).

Отдельные узлы и элементы устройства могут быть реализованы на микросхемах 133 и К556 серий. В частности, триггеры 14-1, 14-2,...14-п, 36-1, ,...,36-ц могут быть вьшолнены на микросхемах 133TBI, триггеры 49 и 50 - на микросхемах 133та2, триг- . геры 41,42, 48 и 51 - на элементах И-НЕ 133ЛАЗ,, 133ЛА4, регистр 20 - на микросхемах 133ИЕ7, регистры 23 и 24 сдвига - на D - триггерах 133ТМ2, счетчик 30 --на микросхемах 133ИЕ7, сумматор 31 - на микросхемах 133ИМЗ, регистр 33 - на микросхемах ЗЗИР, вычитающие счетчики 46 и 47 - на микросхемах 133ИЕ7, регист з 67 сдвига - на микросхеме 133ИР1, ПЗУ 19 и 32 - на микросхе- MSJC К556РТ4. Реализация остальных элементов и узлов устройства на :микросхемах 133 серии не вызывает

3

затруднений. В качестве переключателей 18-1, 18-2,,..,18-р, 21-1, 21-2,.,.,21- И могут быть использованы переключатели типа П2К.

Устройство работает следунш им образом.

Работа устройства осуществляется по программе, хранящейся в блоке 10 памяти. Для каждого типа цифрового узла в блоке 10 памяти записана программа контроля и локализации неисправностей, которая представляет собой последовательность инструкций Каждая инструкция занимает .одну ячейку памяти,

Устройство может выполнять четыре типа инструкций: КО - контроль с условным переходом при совпадении снятой сигнатуры с эталоном; К1 - контроль с регистрацией результатов К2 - контроль с регистрацией результатов и остановом; КЗ - контроль с условным остановом при совпадении

снятой сигнатуры с зталоном.

Все инструкции имеют следующий формат: в разрядах А,- А содержится эталонная сигнатура; в разрядах В(-Вд - адрес группы контролируемых сигналов; в разрядах - маска, определяющая сигналы из выбранной группы, участвующие -в формировании сигнатуры; в разрядах D, , С. - код операции тип выполняемой ин- струк1щи , в разрядах; , - .

адрес перехода (только для инструк- ции КО). D, задает выполнение инструкции КО; D,l,O 0 - инструкции К1; В, 0, инструкции К2; - инструкции КЗ, Инструкция КО позволяет осуществлять контроль сигналов с входов, выходов и контрольных точек цифрового узла, Номенклатура контролируемых сигналов задается адресом группы В,-Во и мае- кой C,-Cj,, В процессе контроля на входы цифрового узла подгиотся тестовые воздействия, в качестве которых используются псевдослучайные коды, а реакции с контролируемых то- чек преобразу1отся в ключевой код - . сигнатуру. По окончании тестовой последовательности получения сигнатура сравнивается с эталонной сигнатурой, содержащейся в разрядах Л,-А инструкции. При совпадении снятой сигнатуры с эталоном (т,е, при правнпьном формировании контролируемых

0

3

s

О 5

5

о 5

0

5064

сигналов) осуществляется переход к инструкции программы, записанной в блоке 10 памяти по адресу, равному сумме начального адреса программы и адреса перехода, хранящегося в разрядах Е -Е инструкции. При совпадении снятой сигнатуры с эталоном выполняется таким образом условный переход. При несовпадении полученной сигнатуры с зталоном осуществ- . ляется переход к инструкции, записанной в следующей по порядку ячейке памяти. Инструкция-К1 позволяет контролировать выбранные сигналы цифрового узла и регистрировать результаты контроля, В процессе контроля производится формирование сигнатуры из сигналов, выбранных разрядами Bj-Вл, инструкции. По окончании тестовой последовательности снятая сигнатура сравнивается с эталонной сигнатурой /разряды А,-А инструкции). При несовпадении снятой сигнатуры с зталоном в блоке 13 регистрируются номера неправильно формируемых сигналов цифрового узла. Затем осу1 |;ествляется переход к - инструкции програмгФ, записанной в следующей ячейке памяти. Инструкция К2 выполняется аналогично инструкции К1 за исключением .того, что-по окончании ее выполнения происходит останов в работе устройства. Инструкция КЗ позволяет контролировать сигналы цифрового узла, выбранные разряда- . ми , С,- С инструкции, В случае правильного формирования этих сигналов,т,е, при совпадении сндтой сигнатуры с эталонной сигнатурой (разряды А,-Aj инструкции , происходит останов в работе устройства.В противном случае осус;ествляется переход к следующей по порядку инструкции программы.

Рассмотрим работу устройства при выполнении им отдельных инструкций программы.

Перед началом работы в блоке 1 задания режима производится установка переключателей 18-1, 18-2,,.,, 18-р, с помощью которых задается двоичный код типа контролируемого цифрового узла 17, Этот код поступает на адресные входы ПЗУ 19, на выходах которого считывается начальный адрес программы контроля и локализации неисправностей для выбранного типа контролируемого узла, В

блоке . 2 коммутации устанавливаются переключатели , 21-2,,..., 21-п в соответствии с назначением выводов ко.нтролируемого узла (вход или выход). В исходном состоянии все переключатели 21-1, ,..., 21- h выключены (на фиг. 3 переключатели 21-1, 21-2,...,21- И показаны в выключенном состоянии). При установке включаются те переключатели, которые соответствуют входам ; контролируемого узла. При этом соответствующие выходы генератора ПСК 4 подключаются к входам цифрового уз- ла 17. После установки переключателей в блоке 1 задания режима контроля и блоке 2 коммутации на вход 16 начальной установки устройства подается отрицательный импульс (логи- ческий О), который в блоке 1 задания режима контроля переписывает с выходов ПЗУ 19 в регистр 20 началь-. ный адрес программы контроля и локализации неисправностей цифрового узла ,17. В генераторе ПСК 4 сигнал начальной установки поступает на установочный вход регистра 23 сдвига и приводит его в исходную кодовую комбинацию. В сигнатурном анализа- торе 5 сигнал начальной установки подается на установочный вход регист ра 24 сдвига и обнуляет его. В блоке 10 памяти сигнал начальной установки поступает на вход установки в нулевое состояние счетчика 30 и обнуляет его. Сумматор 31 осуществляет сложение кодов с выходов счетчика 30 и блока 1 задания режима. На его выходах формируется началь- ный адрес программы контроля и лока- .лизадии неисправностей цифрового узла 17, поступающий на адресные входал ПЗУ 32. На выходы ПЗУ 32 считывается первая инструкция nporpciM- мы, которая додается на информационные входы регистра 33. СигнагЕ нчальной установки в блоке 10 проходит также через элемент 28 задержки и элемент И 29 на счетный вход счетчика 30 и вход записи ре. :гистра 33. По переднему фронту задержанного импульса начальной установки происходит запись первой инструкции программы в регистр 33. По заднему фронту задержанного импульс начальной установки осуществляется увеличение на единицу содержимого

счетчика 30. При этом на выходах сумматора 31 формируется адрес следующей инструкции программы, В блоке 13 регистрации сигнал начальной установки поступает на входы установки в нулевое состояние триггеров 36-1, 36-2,...,, 36-h, 41,42 и обнуляет их. Сигнал логического О с выхода триггера 42, поступая на входы элементов И 43,, злементов индикации 37-1, 37-2,...,37-h, 38-1, 38-2,...., 38-j, 39, 40, запрещает вывод на них информации. Светодиоды 44 :во всех элементах индикации не светятся. В блоке 15 управления сигнал начальной установки /логический поступает на входы установки в нулевое состоянии триггеров 49 и 51, обнуляя их, и на В1ХОД элемента И 57. Сигнал логического О с выхода элемента И 57 подается на входы записи вычитаю- щих счетчиков 46, 47 и вход установки в нулевое состояние триггера 48. При этом триггер 48 обнуляется, а в вычитающие счетчики 46, 47 с информационных входов 73, 74 записываются двоичные коды N,, Код . N., определяет число псевдослучайных кодов генератора ПСК 4, необходимых для приведения контролируемого цифрового узла. 17 в исходное состояние. Код N;, задает число кодов генератора ПСК 4, используемых для снятия сигнатуры контролируемых сигналов узла 17. Сигнал логического О с выхода триггера 51 поступает на вход установки в нулевое состояние триггера 50, обнуляя его и принудительно удерживая в нулевом состоянии. Сигнал логического О с выхода триггера 50 запрещает прохождение тактовых импульсов с выхода задающего генератора 62 через элемент И 58. Сигнал логической 1 с инверсного вьпсода триггера 49 поступает на вход управления регистра 67 сдвига и задает режим записи в него параллельного кода,, Тактовые импульсы от задающего генератора 62 подаются на вход синх1)онизации (с) регистра 67 сдвига. По заднему фронту этого тактового имггульса в регистр 67 сдвига заносится код iOOO. По сигналу начальной установки обнуляются также триггеры 14-1, 14-2,...,14-п.

Начало работы устройства задает ся импульсом на выходе 75 запуска.

который устанавливает в единичное состояние триггер 51. Сигнал логи ческой. с выхода триггера 51 подается на вход установки в нулевое состояние и информационный вход триггера 50. По переднему фронту тактового импульса от генератора 62 тактовых импульсов, поступающему на вход синхронизации триггера 50, триггер 50 переводится в единичное состояние Сигнал логической 1 с выхода триггера 50 разрешает прохождение тактовых импульсов от генератора 62 такто вых импульсов через элемент И 58. Сигнал логической 1 с прямого выхода триггера 48 разрешает прохождение тактовых импульсов от элемента И 58 через элементы И 55, ИЛИ 52 на вход синхронизации регистра 23 сдви- га генератора ПСК 4. При этом генератор пек 4 формирует псевдослучайные 1коды, которые через блок 2 коммута- |Ции поступают на входы цифрового узла 7 и производят установку циф- ровых блоков контролируемого узла в исходное состояние,что необходимо для получения однозначных результатов контроля,Каждый тактовый импульс с выхода элемента И 55 приходит также на счетный вхо /счетчика 46 и уменьшает его содержимое на единицу. После того, как генератор ПСК 4 сформирует N, кодов, счетчик 46 обнулится и на его выхо™ де заема выставится сигнал логичес- кого О, который установит триггер 48 в единичное состояние. Сигнал логического О с прямого выхода триггера 48 запрещает прохождение тактовых импульсов через элемент И 55, а сигнал логической 1 с инверсного выхода триггера 48 разрешает прохождение тактовых импульсов через элемент И 59 на входы синхронизации триггеров I 4-1,14-2,.., , 1 4-п.В исходном состоянии триггеры 14-1, 14-2,. .. обнулены.Сигналы логической 1 син- версных выходов.этих триггеров поступают на первые входы элементов И , 12-2,...,12-п, на вторые вхо- ды которых подается маска из разрядов регистра 33 блока 10 памяти. Каждьй разряд С; (i 1,2,. .., п) маски определяет, участвует (Ci) или не участвует (С;.0) в формировании сигнатурыi -и сигнал из группы контролируемых сигналов узла 17, подключенных с помощью мультиплексоров

3-1, 3-2,...,3- п к информационным входам мультиплексора 6. С помощью мультиплексоров группы 3 под воздействием адреса группы, поступающего из разрядов я регистра 33 блока 10 памяти, к информационным входам мультиплексора 6 могут быть подключены сигналы с входов-выходов цифрового узла 17 или сигналы с его контрольных точек. Пусть контролю подвергаются первый и второй сигналы из выбранной группы, т.е. в выполняемой инструкции содержится маска С,, .... Тогда на выходах элементов И 12-3, 12-4,..., 12- fi в течение выполнения инструкции удерживается сигнал логического О. Сигналы логической 1 с выходов элементов И 12-1, 12поступают на соответствующие входы дешифратора 11. Дешифратор 11 из этих сигналов выбирает один от элемента И 12-1J , имеющий максимальный приоритет, и формирует на первом своем выходе сигнал логической 1. На остальных выходах дешифратора 11 устанавливается сигнал логического О. Сигнал логической 1 с первого выхода дешифратора I1 вызывает появление на выходах шифратора 7 кода, который, поступая на адресные входы мультиплексора 6, обеспечивает подключение через него к входу сумматора 25 по модулю два сигнатурного анализатора 5 первого сигнала из выбранной мультиплексорами 3-1, 3-2,...Згруппы сигналов цифрового узла 17. На выходе элемента ИЛИ-НЕ 9 формируется сигнал логического О, который, поступая на первый вход блока 15 управления, разрешает прохождение тактового импульса от элемента И 59 через элемент И 60 на вход синхронизации регистра 24 сдвига сигнатурного анализатора 5. По переднему фронту этого тактового импульса осуществляется запись первого сигнала из выбранной группы в сигнатурный анализатор 5 .По заднему фронт этого импульса, поступаняцего с выхода элемента И 59 на входы синхронизации триггеров 14-1, 14-2,. . . , 14-ft, триггер 14-1 устанавливается в единичное состояние, поскольку на его единичный (3) вход поступает сигнал логической 1 с первого выхода

блока 1 1 гфиоритетов, а на Hy.nej3Oi j (К) вход снгнсчл логического О с выхода элемента Ш1И-НЕ 9. О стальные триггеры группы 14 обнулены и своего состояния не изменяютj поскольку на их единичных и нулевых входах присутствуют сигналы логического о. После того, как .триггер 4-1 установится в единичное состояниеj на его инверсном выходе сформирует- ся сигнал логического О который вызовет ноявление на выходе элемента И 12-1 сигнала логического О. Теперь на. входы дешифратора. 1 пост

пает один сигнал логической 1 с

выхода элемента И.12--2, Дешифратор 11 формирует на втором своем выходе сигнал логической I на осталь- пых выходах дешифратора I1 выстав™ ляется сигнал логического О). На выходах шифратора 7 появляется новый код, обеспечивающий подключение второго контролируемого сигнала через мультиплексор 6 к информал.ион ному входу сигнатурног о анализатора .5 По переднему фронту следутощего тактового импульса на входе синхро- Ш1зации сигнатурного анализатора 5 осуществляется запись в него второго контролируемого сигнала,,а по заднему фронту этого тактового .. пульса постз пающего на входы хронизации триггеро.в группы 14, триг гер устанавливается в ед.иничное состояние. По окончании регистр;щии первого и второго контролируемь х сигналов в сигнатурном анализаторе 5 триггеры , 4-2 оказываются установленными в единичное состояние на выходах элементов И 12-, 2-2 12™25,о,,12 И и на выходах блока 11 приоритетов формир5 н)тся сигналы логического О, В результате на выходе элемента ШТИ-НЕ 9 появля€;тся сигнал логической М, который,, пос™ тупая на первый вход блока 15 .в™ ления запрещает прохождение так товьщ импульсов с выхода элемента И 60 на вход синхронизации сигнатур ного анализатора 5 и разрешает прохолодение тактового импульса через элемент И 56 на счетный вход счетчика 47 и через элементы И 56 ШШ 52 на вход синхронизадии генератора ПСК 4, На выходах генератора ПСК 4 про™ . исходит смена псевдос.г(учайв:ого кода а содержимое счетчика 47 уменьшает- СИ на единицу. Этот же тактовый им-

пульс, поступая с выхода элемента И .59 :ia входы синхронизации триггеров группы 14, сбрасывает триггеры 14-1,, 14-2 в нулевое состояние, поскольку на единичных входах этих триггеров присутствует сигнал логического О, а на нулевые входы по дается сигнал логической 1 с вьгхо да элемента ЙЛИ™НЕ 9, После сброса триггеров 14-IJ в нулевое сое-, тоян.ие на выходах элементов И 12-1, 12-2 н на первом выходе дешифратора IJ появл.яются сигналы логической 1 На вфсоде элемента ИЛИ-НЕ 9 форми™

5 руется сигнал логического О , ко25

20 30 ч JQ 45

торый запрещает прохождение тактовых импул:осо.в чврез элемент И 56 на счет вход вычитающего счетчика 47 и через элемента И 56, ИЛИ 52 на вход си:яхрониз щии генератора ПСК 4 и раз решает прохождение тактовых импульсов через элемент И 60 на вход син кронизации сигнатурного анализатора

5,, Далее повторяется описанный про™ цесс поспедовательной регистрации выСэранньЕк; сигналов цифрового узла 17 3 1:игнатурном анализаторе 5, Та- образом,, после каждой смены кода Па выход.ах генератора. ПСК 4 происходит запись реакции цифрового узла 17 с 1зыбранных точек в сигнатурный анализатор 5, Это продолжается до ; тех nops пока не произойдет обнуле- m-ie Счетчика 47 (т.,е. пока генератор ПСК 4 не сформирует N кодов в процессе снятия сигнатуры). При этом на нулевом выходе счетчика 47 формируется сигнал логического О, - устанавливсцощий в едигохчное состояние т эиггер 49 „Сигнал логического О с инверсного выхода триг.гера 49 защ ещает прохож, тактовьк им-; пульсов через элемент И 58 и устанав лизает режим сдвига на управляющем .входе регистра 67 сдвига. Тактовые импу.лзсы, поступсшщие от генератора 62 та1.:товьг -: иьшульсов на вход сдвига регистра 67,. осуш,ествляет в нем про™ дв:гйке гше 1 % записанной в первом разря,де регистра ( на последовательный информ)дионный В вхад регистра

67 поддается сигнал логического О). Далее работа устройства зависит от кода опершдии вьшолняемой инструкции , Код оаерации поступает из разрядов :D. ;D регистра 33 блока 10 памяти на в:5чоды дешифратора . 68. Если выпол- . пяется инструкпия КО; то сигнал ло-

гической l с нулевого выхода де- пшфратора 68 разрешает прохождение импульса с второго выхода регистра 67 сдвига через элемент 69 на вход записи счетчика 30 блока 10 па мяти, если на выходе блока 8 сравнения установлен сигнал логической 1 Блок 8 сравнения осуществляет сравнение сигнатуры, полученной в процессе контроля сигнатурным анализатором 5, с эталонной сигнатурой, поступающей из разрядов А,-А регистра 33 блока 10 памяти. При совпадении сигнатур на выходе элемента ИЖ-НЕ 26 блока 8 сравнения формируется сигнал логической 1. В противном случае на выходе блока В сравнения формируется сигнал логического О. При совпадении снятой сигнатуры с эталоном в блоке IО памяти осуществляется запись в счетчик 30 адреса условного перехода из разрядов Е,-Е регистра 33. Адрес следующей инструкции, которую будет выполнять устройство при совпадении снятой сигнатуры с эталоном, формируется сумматором 31 и равен сумме начального адреса программы контроля и локализации неисправностей цифрового узла 17 и адреса .перехода. Если снятая сигнатура не совпадает с эталоном, то в счетчик 30 адрес перехода не записывается и следующей выполняется инструкция, хранящаяся в сосед- ней ячейке памяти. Импульс с третьего выхода регистра 67 сдвига проходит через элемент И-НЕ 72 на вход элемента И 29 блока 10 памяти. С выхода элемента И 29 отрицательный импульс поступает на счетный вход счетчика 30 и вход записи регистра 33. По переднему фронту этого импуль са в регистр 33 записывается слеующая инструкция программы, а по заднему фронту импульса содержимое счетчика 30 увеличивается на единиу, Шпульс с четвертого выхода реистра 67 сдвига проходит через элеент НЕ 64 и элемент И 57 на вход становки в нулевое состояние триггера 48 и входы записи вычитаищих счетчиков 46, 47. Триггер 48 обнуяется, а в счетчики 46, 47 с ин- ормациоиных входов 73,74 записыаются коды N, , Кроме этого, имульс с выхода элемента НЕ 64 подается на вход синхронизации триггера 49 и по заднему фронту устанавливает его в нулевое состояние, поскольку на информационном входе этого триггера присутствует сигнал логического о. Сигнал логической инверсного выхода триггера 49 вновь разрешает прохождение тактовых им- 10 пульсов от задающего генератора 62 через элемент И 58, а в регистр сдвига 67 разрешается запись исходной кодовой комбинации 1000. На этом процесс выполнения инструкции КО завер- fS шается и начинается выполнение еле- дуюшей инструкции программы. При выполнении инструкции К1 процессы установки цифрового узла 17 в исходное состояние и снятие сигнатуры с 20 контролируемых сигналов осуществляются аналогично бписанному. По окончанию этих процессов регистр 67 сдвига формирует стробирующие импульсы. При выполнении инструкции К1 на пер- 25 вом выходе дешифратора 68 появляет-ч ся сигнал логической 1, который вызывает формирование сигнала логической l на выходе элемента Ш1И 53. Сигнал логической 1 с выхода 30 элемента ИЛИ 53 разрешает прохождение импульса с второго выхода регистра 67 сдвига элемент И-НЕ 70 на вход установки в единичное состояние триггера 41 и на входы синхрониза- 5 ции триггеров 36-1, 36-2,...,36-и блока 13 регистрации при условии, что на выходе блока 8 сравнения устанавливается сигнал логического О, т.е если полученная анализатором 0 5 сигнатура не совпадает с эталоном. При несовпадении полученной сигнатуры с эталоном в блоке 13 регистрации триггер 41 переводится в . единичное состояние, запоминая нали- 5 чие неправильного функционирования контролируемого узла 17, а в триггеры 36-1, 36-2,... ,36-г записываются разряды маски инструкции, установленные в I, тем самым фиксируются не- 0 правильно формируемые сигналы из выбранной для контроля группы. пульс с третьего выхода регистра 67 проходит через элемент И-НЕ 72 на вход элемента И 29 блока 10 памяти и вызывает считывание из ПЗУ 32 . в регистр 33 следующей инструкции программы, а также увеличение на единицу содержимого счетчика 30. Импульс

с четвертого выхода регистра 67 сдвига производит запись кодов N,, N,j в счетчики 46, 47 и обнуляет триггеры 48,49, На этом кончается выполнение инструкции К1. Инструкция К2 выцолняется аналогично инструкции К1. Инструкция К2 выполняется аналогично инструкции К1. Отличие состоит в том, что логическая I на втором вьщоде дешифратора 68 вызывает .появление на выходе элемента ИЛИ 54 сигнала логической 1, который разрешает прохождение импульса с третьего выхода регистра 67 сдвига через элемент И-НЕ 71 на вход установки в нулевое состояние триггера 51 и вход установки в единичное состояние 42 блока }3 регистрации. Сигнал лоп1ческой на выходе элемента.ИЛИ 54 вызывает также появление на выходе элемента . НЕ 65 логического О, который запрещает прохождение импульса с третьего выхода регистра 67 через элемент И-НЕ 72, тем .самым запрещается запись следующей инструкции в регистр 33 и модификация счетчика 30 в блоке 10 памяти.По импульсу с третьего выхода регистра 67 триг- гер 51 обнуляется, сигнал логического О с его выхода устанавливает в нулевое состояние триггер 50. Сигнал логического О с выхода триггера 50 запрещает прохождение тактовых импульсов от задающего генератора 62 через элемент И 58. Триггер 42 в блоке 13 регистрации устанавливается в единичное состояние, и сигнал логической 1 с его выхода разрешает вывод информации на элементы индикации 37-1, 37-2,... ,37-и 38-1, 38-2,...,38-, 39,40. Элементы индикации 39, 40 служат для вывода сообщений о работоспособности или неработоспособности проверяемого цифрового узла 17. Если триггер 41 в процессе выполнения программы был установлен в единичное состояние, т.е. имело место неправильное функционирование цифрового узла 1-7, то будет светиться элемент 39 индикации, свидетельствуя о неработоспособности цифрового узла 17. В противном случае будет светиться элемент 40 индикации, свидетельствуя о работоспособности контролируемого узла. На элементы индикшдии

38-1, 38-,... 38- выводится адрес выбранной группы контролируемьш сигналов из разрядов В,-Ва инструкции К2, а на элементы индикации 37-1, 37-2,...,37- П - номера неверно формируемых в группе сигналов, зафиксированные в триггерах 36-1, 36-2,. . .36-П. После выполнения инструкции К2 происходит останов в работе устройства, поскольку триггер 50 блокирует прохождение тактовых импульсов через элемент И 58. При выполнении инструкции КЗ процессы установки цифрового узла 17 в исходное состояние и снятия сигнатуры 1(;онтро31ируегФ1х сигналов выполняются также, как и в инструкциях КО, К1, К2, После завершения операций контроля регистр 67 сдвига формирует последовательность импульсов. Импульс с третьего выхода регистра 67 проходит через элемент И-НЕ 71, если полученная анализатором 5 сигнатура совпадает с эта- . лоном, или через элемент И-НЕ 72 в противном случае. В первом случае, если снятая сигнатура совпадает с эталоном, в блоке 13 регистрации устанавливается в единичное состояние триггер 42 и разрешается вывод информации на элементы индикации, о а также происходит останов программы вследствие сброса в нулевое состояние триггеров 50,51. Во втором случае, если снятая сигнатура не совпадает с эталоном, в блоке 10 памяти в регистр 33 из ПЗУ 32 считывается следующая инструкция программы и происходит модификация счетчика 30. Импульс с четвертого выхода регистра 67 записывает в счетчики 46,47 коды П, 5 N к сбрасывает в нулевое состояние триггеры 48,49.

Рассмотрим процесс контроля и локализации неисправностей в цифровом узле, схема которого приведена на фиг. 11. Цифровой узел состоит из логических элементов , образующих цифровые блоки, каждый из которых может предстайлять из себя произвольную комби1Е1ационную или ., последовательностную схему. Цифровой узел имеет входам Х1-ХЗ, выходы Y1-Y3 и контролыале точки . Конструктивно цифровой узел может иметь два разъема, на первый из КОТОРЬЕХ выведены взсодныа Х1-ХЗ и выходные

Y1-Y3 сигналы,, а на второй - сигналы с контрольных точек 211-218. В этом случае первый разъем в рабочем режиме служит для подключения узла к.аппаратуре, в состав которой он входит, а второй разъем или не ис- полъзуется, или подключен к средствам встроенного контроля. В режиме контроля оба разъема используются для подключения к устройству контроля и локализации неисправностей вхдов X 1 -ХЗ, выходов 1 -ХЗ и контрольных тчек Z1-ZI8.B таблице на фиг. 11 приведено возможное распределение сигна- лов Х1-ХЗ, 1-Y3, Z1-218 контролируемого узла по группам и разрядам маски инструкции программы при под- :ключении узла к устройству. Конструция узла должна также обеспечивать разрыв обратных связей между логическими элементами, например, с помощью перемычек;, переключателей и т.д. Перед контролем и локализацией, неисправностей эти обратные связи разрываются (внутри логических элементов р1-FI8 обратные связи могут иметь место). Контроль и локализация неисправностей рассматриваемого узла осуществляется по программе, приведенной на фиг. 12. Первая инструкция программы КЗ осущестляет контроль правильности формирования выходных сигналов V1-Y3 узла т.е. реализует пповерку работоспо- собности всего узла в целом. Если сигнатура, снятая с совокупности выходов Y1-Y3 узла, совпадает по окончанию контроля с эталонной сигнатурой S, , то происходит останов в работе устройства, а в блоке ре- гистрации 13 будет светиться элемент 40 индикации, сообщая оператору об исправности контролируемого узла. В противном случае устройство переходит к выполнению инструкции, записанной по адресу 00001. С этого момента начинается процесс локализации неисправностей. Все контрольные точки цифрового узла разбиваются на группы с присвоенным им рангом. Ко гтрольной точкой первого ранга считают выход .логического элемента, все входы которого соединены с входами узла. Контрольной точ- кой второго ранга считают выход логического элемента, входы которого соединены с контрольными точками

5

f, О 1520

0

первого ргшга, некоторые входы этого элемента могут - :быть подключены к входам узла. Контрольной точкой третьего ранга считают выход логического элемента, входы которого соединены с контрольными точками второго ранга, некоторые входы этого элемента могут быть подключены к входам узла и контрольным точкам первого ранга и т.д. У рассматриваемого узла контрольные точки распределяются по рангам след5тощим ...образом: Z1-Z3 - контрольные точки первого ранга; Z4-Z6 - контрольные точки второго ранга; - контрольные точки третьего ранга; Z13-Z16 - контрольные точки четвертого ранга; 217, Z 18 - контрольные точки пятого ранга. Инструкция КО, записанная по адресу 00001, проверяет правильность формирования входных сигналов XI-ХЗ узла. Если сигнатура, снятая с этих сигналов, совпадает по окончанию контроля с эталонной сигнатурой 5 , то осуществляется переход к инструкции программы, хранящейся по адресу boidi. В противном случае выполняет- ся поиск неисправности по входам XI-ХЗ узла. С помощью инструкции К1 (адрес 00010) проверяется правильность формирования сигнала X. Если сигнатура сигнала XI не совпадает с эталонной сигнатурой э то в блоке 13 регистрации запоминает- ся номер неисправного сигнала. Затем аналогичным образом с помощью инструкции К1 (адрес 0001l) проверяется правильность формирования сигнаг ла Х2, ас помощью инструкции К2 (адрес ООЮО) - правильность формирования сигнала ХЗ, после чего про- исходит останов программы. В блоке 13 регистрации на элементы индикации выводится адрес группы 00 и номера неисправных в этой группе сигналов. Если входные сигналы Х1-ХЗ узла формируются правильно, то выполняется инструкция КО (адрес OOlOl), с помощью которой проверяется правильность формирования совокупности сигналов с контрольных точек первого ранга , Если сигнатура контрольных точек 21-73 совпадает с эталонной сигнатурой Sg , то осуществляется переход к инструкции, записанной по адресу 01001. В противном случае производится поиск неислравностей в группе контрольных точек Z 1-7.3. Инструкция К1 (адрес ООПО) проверяет правильность формирования сигнала 21, инструкция KI (адрес 001 П) - сигнала 2, инструкция К2 (адрес ОЮОО) - сигнала Z3. После выполнения инструкции К2 (адрес ОЮОО) происходит останов программы Б блоке 13 регистрации на элементы индикации выводится адрес группы 01 и номера неисправных сигналов.Если сигнатура сигналов Z1-Z3 совпала с эталонной сигнатурой 5, то осущестляется переход к проверке правильности формирования сигналов с конт- рольньпс точек второго ранга Z4-Z6 и т.д. Таким образом, поочередно проверяются сигналы с контрольных точек, в порядке увеличения их ранга. Как только сигнатура со- вокупности сигналов с контрольных точек некоторого ранга не совпадет с эталоном, осзтдествляется локали - зация неисправных сигналов в этой группе, после чего происходит оста- нов программь и вывод сообщения в блоке 13 регистрации. Аналогичным образом может быть построена программа контроля и локализации неисправностей другого типа цифровых узлов.

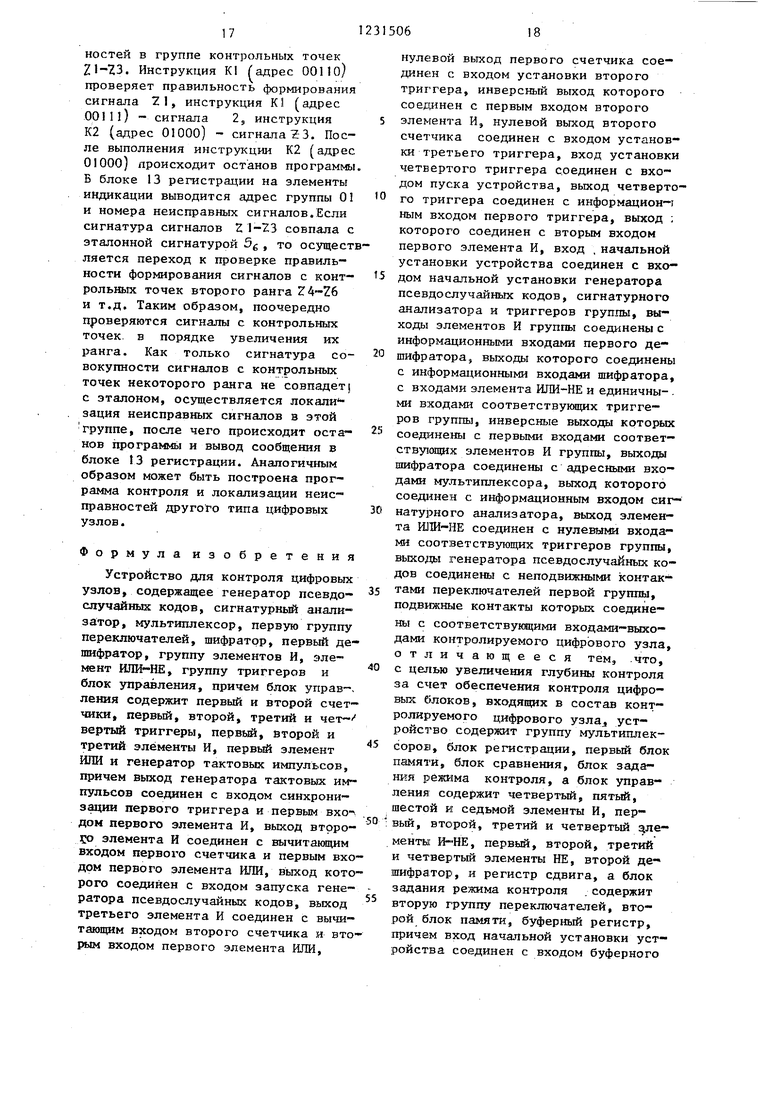

Формула изобретения Устройство для контроля цифровых

,-

узлов, содержащее генератор псендо случайных кодов, сигнатурный анализатор, мультиплексор, первую группу переключателей, шифратор, первый дешифратор, группу элементов И, элемент ИЛИ-НЕ, группу триггеров и блок управления, причем блок управ-. ления содержит первый и второй счетчики, первый, второй, третий и чет- вертый триггеры, первый, второй и третий элементы И, перв элемент ИЛИ и генератор тактовых импульсов, причем выход генератора тактовых импульсов соединен с входом синхронизации первого триггера и первьм вхо- дом первого элемента И, выход второ- JCO элемента И соединен с вычитаницнм входом первого счетчика и первым входом первого элемента ИЛИ, выход которого соединен с входом запуска генератора псевдослучайных кодов, выход третьего элемента И соединен с вычитающим входом второго счетчика и вторым входом первого элемента ИЛИ,

5 О 520 25 30

35

40

45

50

55

нулевой выход первого счетчика соединен с входом установки второго триггера, инверсный выход которого соединен с первым входом второго элемента И, нулевой выход второго счетчика соединен с входом установки третьего триггера, вход установки четвертого триггера соединен с входом пуска устройства, выход четвертого триггера соединен с информацион-i ным входом первого триггера, ; которого соединен с вторым входом первого элемента И, вход , начальной установки устройства соединен с входом начальной установки генератора псевдослучайных кодов, сигнатурного анализатора и триггеров группы, выходы элементов И группы соединены с информационными входами первого дешифратора, выходы которого соединены с информационными входами шифратора, с входами элемента ИЛИ-НЕ и единичны- . ми входами соответствукнцих триггеров группы, инверсные выходы которых соед1чнены с первыми входами соответствующих элементов И группы, выходы шифратора соединены с адресными входами мультиплексора, выход которого соединен с информационным входом сигнатурного анализатора, выход элемента ИЛИ-НЕ соединен с нулевыми входами соответствующих триггеров группы, выхода генератора псевдослучайных кодов соединены с неподвижными контактами переключателей первой группы, подвижные контакты которых соединены с соответствукяцики входами-выходами контролируемого цифрового узла, отличающееся тем, .что, с целью увеличения глубины контроля за счет обеспечения контроля цифровых блоков, входящих в состав конт- ролир уемого цифрового узла устройство содержит группу мультиплексоров, блок регистрации, первый блок памяти, блок сравнения, блок задания рёшша контроля, а блок управления содержит четвертый, пятый, шестой и седьмой элементы И, пер- вый, второй, третий и четвертый ле- менты И-НЕ, первый, второй, третий и четвертый элементы НЕ, второй дешифратор, и регистр сдвига, а блок задания режима контроля . содержит вторую группу переключателей, второй блок памяти, буферный регистр, причем вход начальной установки устройства соединен с входом буферного

регистра, с входом начальной установки первого блока памяти, с входом сброса блока регистрации, информационные входы мультиплексоров группы соединены с соответствующими подвижными контактами переклю- ате- лей первой группы, группы информационных входов мультиплексоров группы соединены с группами выходов сооветствующих контролируемых цифровых блоков, адресные входы мультиплексоров группы соединены с выходами признаков адреса пе|)вого блока памяти и с первой группой информационных входов блока регистрации, выхо- ды мультиплексоров группы соединены с информационными входами мультиплексора, выходы признаков входов- выходов контролируемого цифрового узла первого блока памяти.соединены с вторыми входами соответствующих элементов И группы и с второй группой информационных входов блока регистрации, группа выходов эталонной сигнатуры первого блока памяти сое- динена с первой группой информационных входов блока сравнения,вторая группа информационных входов которой соединена с группой выходов сигнатурного анализатора, информацион- ные входы первого счетчика подклю- чены к шине задания числа начальных установок контролируемого цифрового узла, информационные входы второго счетчика подключены к шине задания

числа контрольных

тактов, первые

неподвижные контакты переключателей второй группы подключены к шине нулевого потенциала устройства, вторые неподвижные контакты переключаЧ-елей второй группы подключены к шине единичного потенциала устройства, подвижные контакты переключателей второй группы соединены с адресными входами второго блока памяти, выходы которого соединены с информационными входами буферного регистра,выходы которого соединены с адресными входами первого блока памяти, выходы кода логической операции ко- торого соединены с информационными входами второго дешифратора, первый выход которого соединен с первым входом -первого элемента И-НЕ,второй выход второго дешифратора сое- динен с первым входом второго элемента ИЖ, третий выход второго дешифратора соединен с вторым входом

второго элемент а-lillH и первым входом третьего элемента ИЛИ, четверты выход второго дешифратора соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом блока сравнения, с вторым входом первого элемента И-НЕ и через первый элемент НЕ - с первым входом второго элемента И-НЕ, выход второго элемента ИЛИ соединен с вторым входом второго элемента И-НЕ, выход третьего элемента ИЛИ соединен с первым входом третьего элемента И-НЕ и через второй элемент НЕ - с первым входом четвертого элемента И-НЕ, выход первого элемента И-НЕ соединен со стробирукщим входом первого блока памяти, выход второго элемента И-НЕ соединен с входом синхронизации блока регистрации, выход третьего элемента И-НЕ соединен с нулевым входом четвертого триггера и входом разрешения блока регистрации, выход четвертого элемента И-НЕ соединен с входом считывания первого блока памяти, вход синхронизации регистра сдвига соединен с выходом генератора тактовых импульсов, прямой выход второго триггера соединен с первым входом пятого элемента И, второй вход которого соединен с выходом первого элемента И и вторым входом второго элемента И,инверсный выход третьего триггера соединен с третьим входом первого элемента И и входом разрешения регистра сдвига, второй разрядньй выход которого соединен с третьими входами первого и второго элементов И-НЕ, третий разрядный выход регистра сдвига с вторыми входами третьего и четвертого элементов И-НЕ, четвертый разрядный выход регистра сдвига соединен через третий элемент НЕ с входом синхронизации третьего триггера и первым входом шестого элемента И, второй вход которого соединен с входом начальной установки устройства, с единичным входом четвертого триггера и входом сброса третьего триггера, информационный вход которого подключен к шине нулевого потенциала устройства, выход шестого элемента И соединен с входами синхронизации первого и второго счетчиков и нулевым входом второго триггера, выход пятого мента И соединен с первыми входами

третьего и седьмого элементов И и с входами синхронизации триггеров группы, второй вход третьего элемента И соединен с выходом элемента и входом четвертого элемента НЕ, выход которого соединен с вторым входом седьмого элемента И, выход которого соединен с входом син-. хронизации сигнатурного анализатора, выход четвертого элемента И соединен с вторым входом третьего : лeмeнta ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Устройство для диагностики неисправностей цифровых узлов | 1987 |

|

SU1481773A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах при диагностике цифровых узлов, имеющих в своем соста-, не цифровые блоки. Цель изобретения - увеличение глубины контроля. Поставленная цель достигается за счет введения блока коммутации, группы мультипликаторов, мультиплексеров. шифратора, дешифратора, блока управления. В основу работы положен принцип сигнатурного анализа. Входные воздействия для контролируемого цифрового узла формируются при помощи генератора псевдослучайных кодов, а выходные последовательности сигналов преобразуются в сигнатуру. Процесс контроля состоит в сравнении сигнатур, снятых для эталонного блока оператором. Устройство позволяет оценить работу контролируемого цифрового узла в целом, а также любых по выбору оператора цифровых блоков (микросхем), входящих в узел. Сигнатуры, взятые с выводов микросхем, используются при поиске места неисправностей. Процесс контроля проводится в два этапа. На первом снижается сигнатура д.пя всего узла. В случае неисправности происходит локализация неисправностей. 12 ил. а о СО

ipuff.2

21-гг

фиг.З

фи$Л

24У . t . i:

I с sf

RS

1 с//77

/ -- V -- V

(puff. 5

.У

-И

гв

i

г

-/Г7

30

i

зг

л

Л1

л

Л

т

tfiiM.7

f г

П

) / /1 /к/

УЗ

Составитель A.Сиротская Редактор М. Келемеш Техред И,.Гайдош Корр-ектор С, Черни

Заказ 2652/52 Тираж 67:1Подписное

ВНИИПИ Государственного ког тета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-15—Публикация

1984-12-07—Подача