I ;/

(Л

.с

4

ОО

;о ел

а

J2

1А39564

тор 12 псевдослучайных кодов, блок 13 управления, буферные регистры 14, 15, первую 16 и вторую 17 группы вхо- дов, выход 18. Генератор 12 псевдослучайных кодов содержит регистр сдвига и сумматор по модулю два. Блок 13 управления содержит блок памяти микрокоманд, счетчик, регистр,микро- . команд, дешифратор микрокоманд, регистр адреса, формирователь стробирующта тр Це вв зу ши бл 5, фющих сигналов, узел синхронизации, тактовый генератор, счетчик тактов, триггер пуска, буферный регистр. Цель изобретения достигается за счет введения (т-1) регистров масок, образующих блок 3 регистров масок, дешифратора 4, групп элементов И 2,10, блоков мультиплексоров 8,9, регистров 5,6, буферных регистров 14,15. 1 з.п. флы, 5 ило

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Генератор испытательных последовательностей | 1987 |

|

SU1543396A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

Генератор относится к средствам айтоматического контроля и диагностики цифровых объектов при юс производстве и техническом обслуживании. Цель изобретения - повышение быстро-, действия. Генератор содержит выходной регистр, первую группу элементов И 2j лок 3 регистров масок, дешифратор 4, регистры 5,6, арифметико- логическое устройство 7, блоки мультиплексоров 8,9, вторую группу элементов И 10, блок 11 памяти, генера

1

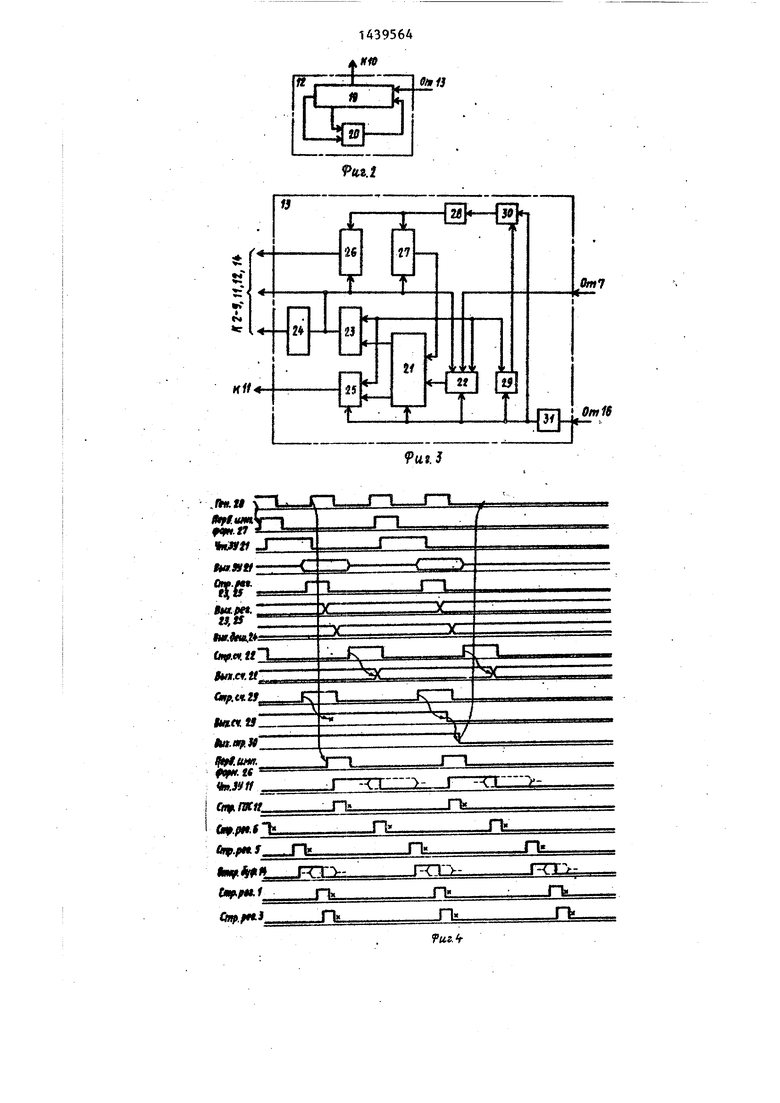

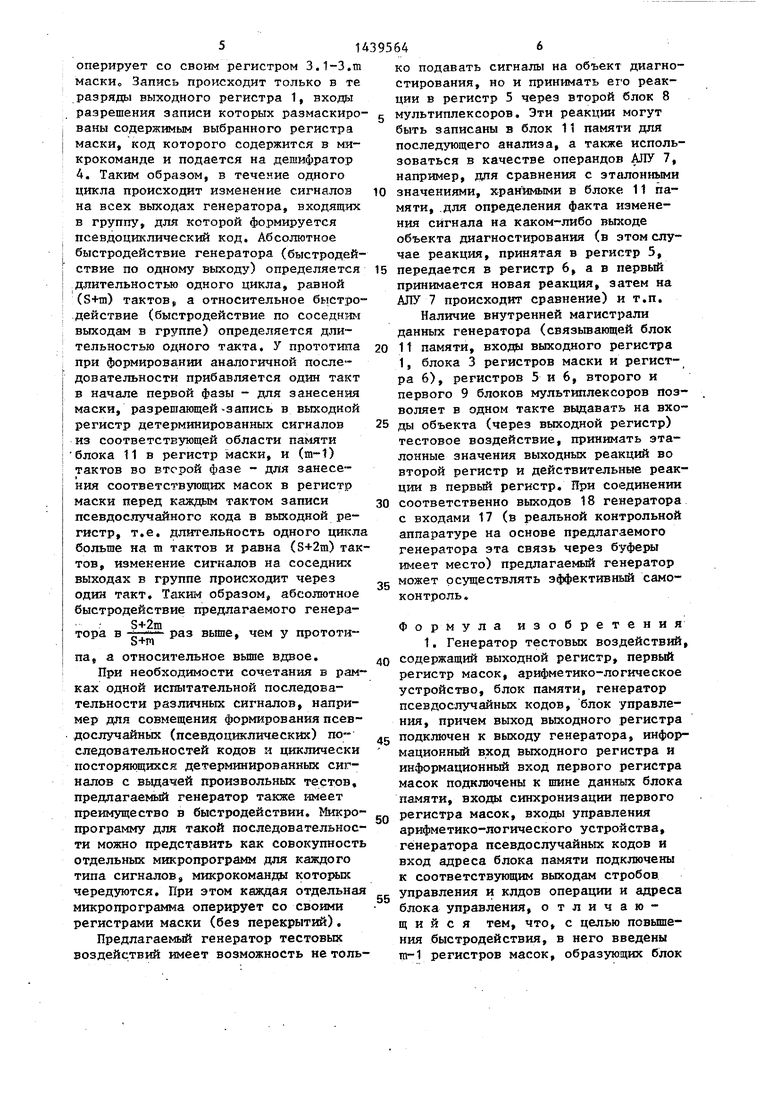

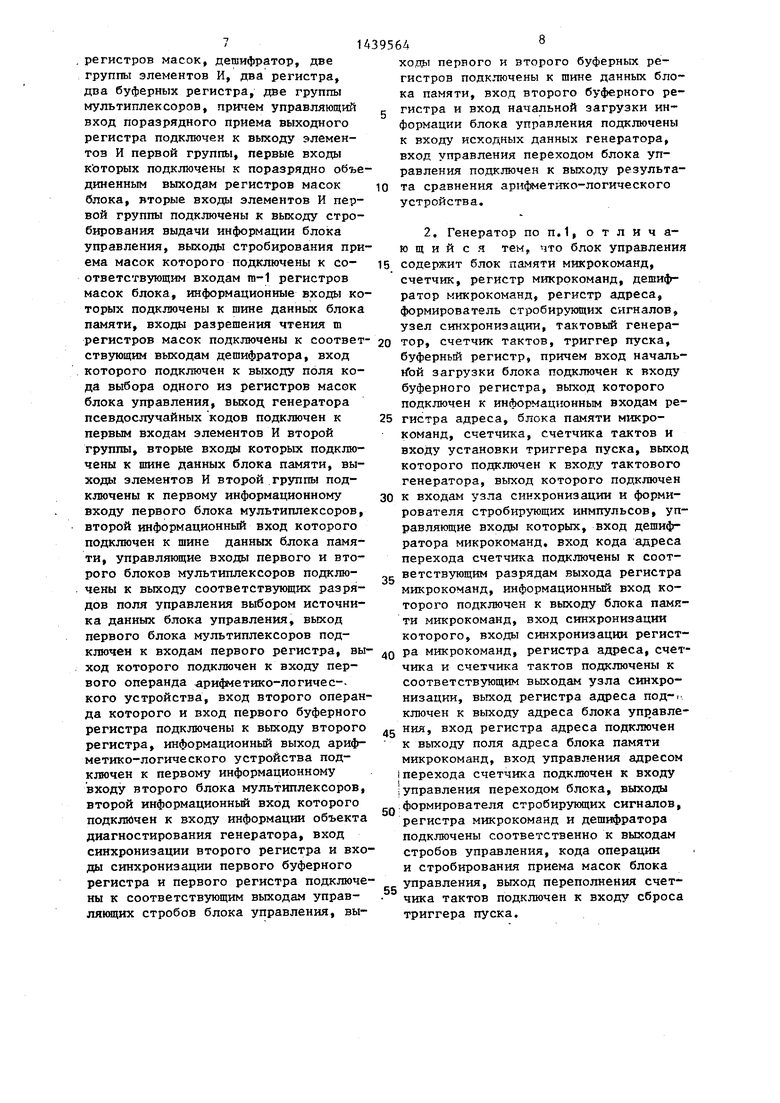

Изобретение относится к вычислительной технике, в частности.к средствам автоматической проверки цифровых объектов, и может быть использовано для фу11К1{Ионального контроля процессоров, контроллеров, запоЬтнаю щих устройств и прочих блоков и уз- |лов ЭВМ, а та1сже других средств циф- Iровой техники при их производстве и техническом обслуживании. Цель изобретения - повышение бы- 1стродействия генератора. На фиго1 представлейа структурная схема предлагаемого reHepaTopaj на фиг.2 - схема генератора псевдослу- I чайных кодов; на фиг.З - схема .блока управления5 на фиг.4 - временная диаграмма работы генератора; на фиг.5- формат микрокоманд блока управления. I Генератор (фиг,1) тестовых воз- действий содержит выходной регистр 1 ;первую группу элементов И 2, блок 3 ;регистров маски, дешифратор 4, регистры 5 и 6, арифметико-логическое устройство (АПУ) 7, второй 8 и первы 9 блоки мультиплексоров, вторую группу элементов И 10, блок 11 памяти, генератор 12 псевдослучайньш кодов, блок 13 управления, буферные регистры 14 и 15, первую 16 и вторую 17 группы входов и выходы 18 генератора тестовых воздействий.

Генератор псевдослучайных кодов (фиг.2) содержит регистр 19 сдвига и сумматор 20 по модулю 2,

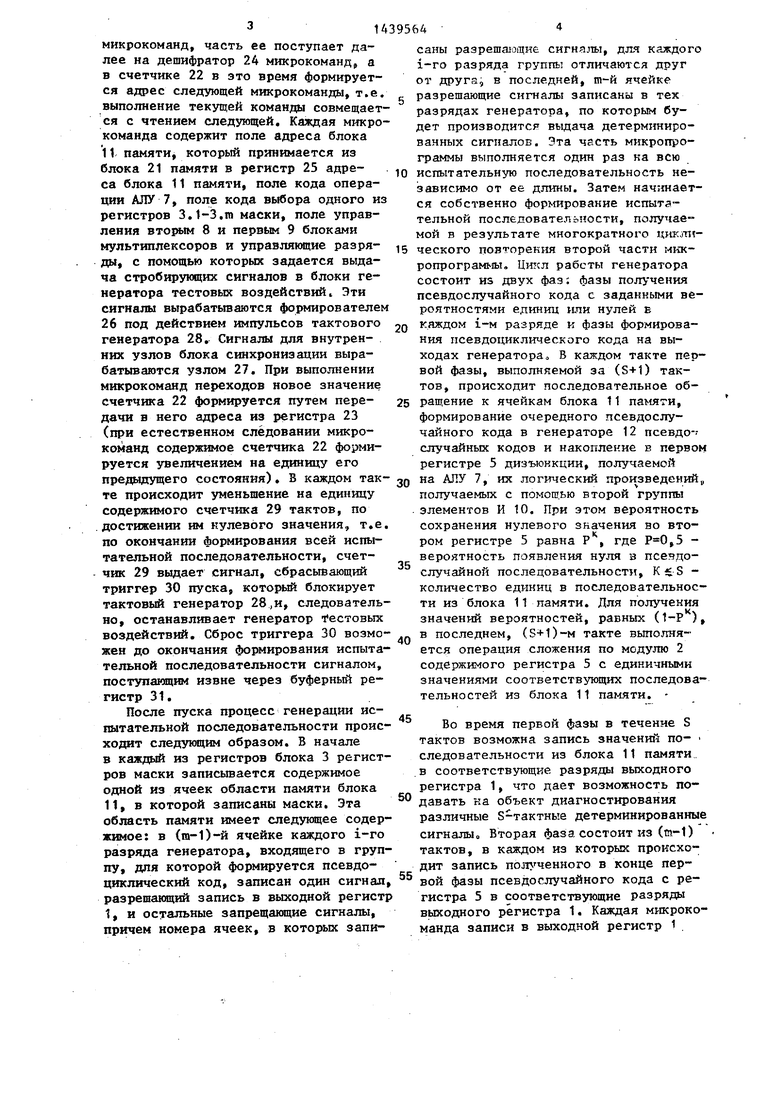

Блок 13 управления (фиг.З), предназначенный для подачи управляющих и стробирующих сигналов на остальные блоки генератора тестовых воздейст- ..

5

0

5

0

5

ВИЙ, содержит блок 21 памяти, счетчик 22 и регистр 23 микрокоманд, тор 24 микрокоманд, регистр 25 адреса, формирователь 26 стробируницих сигналов, узел 27 синхронизации, тактовый генератор 28, счетчик 29 так тов, триггер 30 пуска и буферный регистр 31.

АЛУ 7 представляет сббой универсальное арифметико-логическое устройство и может быть реализовано по известной схеме.

Генератор работает следующим образом.

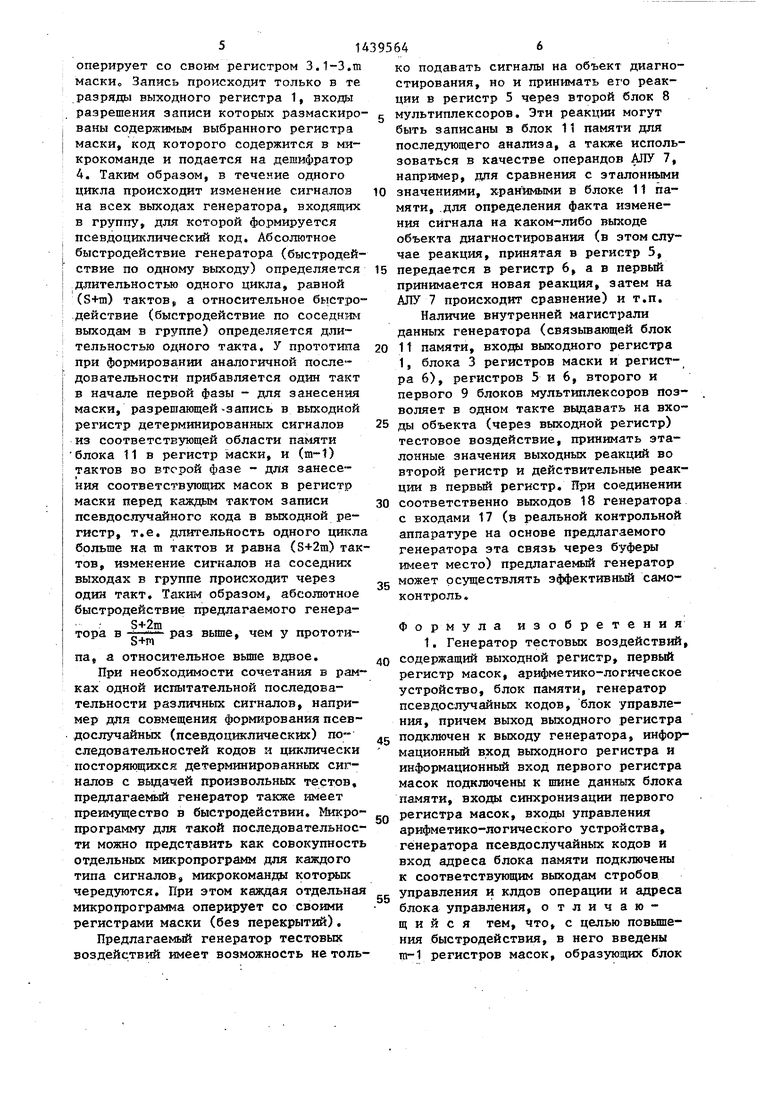

Перед началом генерации производится загрузка данных, необходимых для формирования испытательных последовательностей, в блок 11 памяти через буферный регистр.15, при этом адреса загружемых ячеек блока 11 памяти принимаются в регистр 25 через буферный регистр 31. Через этот же регистр с входа 16 в блок 21 памяти микрокоманд загружается микропрограмма, определяющая последовательность операций генератора в каждом такте, с использованием для задания адресов, блока 21 памяти счетчика 22; в счетчик 29 тактов - общая длина (а тактах) испытательной последовательности, в счетчик 22 - начальный адрес микропрограммы в блоке 21 памяти. После завершения ввода начинасгтся процесс генерации, для чего вводится триггер 30 пуска, который включает тактовый генератор 28. В процессе работы происходит выборка микрокоманд из блока 21 памяти. Прочитанная микрокоманда принимается в регистр 23

10

15

3U39564

микрокоманд, часть ее поступает далее на дешифратор 24 микрокоманд а в счетчике 22 в это время формируется адрес следующей микрокоманды, т.е. выполнение текущей команды совмещается с чтением следующей. Каждая микрокоманда содержит поле адреса блока 11 памяти, который принимается из блока 21 памяти в регистр 25 адреса блока 11 памяти, поле кода операции АЛУ 7, поле кода выбора одного из регистров 3.1-3,т маски, поле управения вто{я 1м 8 и первым 9 блоками ультиплексоров и управляющие разряы, с помощью которых задается выдаа стробирующих сигналов в блоки геератора тестовых воздействий. Эти сигналы вырабатьгааются формирователем 26 под действием импульсов тактового генератора 28, Сигналы для внутрених узлов блока синхронизации вырабатываются узлом 27. При выполнении икрокоманд переходов новое значение счетчика 22 формируется путем переачи в него адреса из регистра 23 (при естественном следовании микрокоманд содержимое счетчика 22 формиуется увеличением на единицу его предыдущего состояния). В каждом такте происходит уменьщение на единицу содержимого счетчика 29 тактов, по остижении им нулевого значения, т.е. о окончании формирования всей испытательной последовательности, счет- чшс 29 выдает сигнал, сбрасывающий триггер 30 пуска, который блокирует тактовый генератор 28,и, следователь20

25

30

35

са iотра ра де ва гр ис за ся те мо че ро со пс ро ка ни хо во то ра ча сл ре на по эл со

ро ве сл ко ти зн в ет со зн те

но, останавливает генератор тестовых воздействий. Сброс триггера 30 возможен до окончания формирования испытательной последовательности сигналом, поступающим извне через буферный регистр 31.

После пуска процесс генерации испытательной последовательности происходит следующим образом. В начале в каждый из регистров блока 3 регистров маски записывается содержимое одной из ячеек области памяти блока 11, в которой записаны маски. Эта область памяти имеет следукицее содержимое: в (т-1)-й ячейке каждого i-ro разр51да генератора, вход5пцего в группу, для которой формируется псевдо40

ром регистре 5 равна Р , где ,5 - вероятность появления нуля в псевдослучайной последовательности, К i S - количество единиц в последовательнос ти из блока 11 памяти. Для получения значений вероятностей, равных ) в последнем, ()-м такте выполняется операция сложения по модулю 2 содержимого регистра 5 с единичными значениями соответствующих последовательностей из блока 11 памяти.

45

Во время первой фазы в течение S тактов возможна запись значений по- следовательности из блока 11 памяти,, в соответствующие разряды выходного регистра 1, что дает возможность по- давать ка объект диагностирования различные S-тактные детерминированные сигналЫо Вторая фаза состоит из (tn-1) тактов, в каждом из которых происходит запись пол ченного в конце перциклический код, записан один сигнал, вой фазы псевдослучайного кода с ре- разрещанщий запись в выходной регистр гистра 5 в соответствующие разряды и

1, и остальные запрещающие сигналы, причем номера ячеек, в которых запивыходного регистра 1. Каждая микроко манда записи в выходной регистр 1.

0

5

0

5

0

5

0

саны разрешающие сигналы, для каждого iro разряда группы отличаются друг от друга, в последней, т-й ячейке разрешающие сигналы записаны в тех разрядах генератора, по которым будет производится вьщача детерминированных сигналов. Эта часть микропрограммы выполняется один раз на всю испытательную последовательность независимо от ее длины. Затем начгшает- ся собственно формирование испытательной последовательности, получае™ мой в результате многократного цикш1- ческого повторения второй части мгас- ропрограммы. Цшсл работы генератора состоит из двух фаз; фазы получения псевдослучайного кода с заданными вероятностями единиц 1тк нулей в каждом i-M разряде к фазы формирования исевдоциклического кода на выходах генераторао В каждом такте первой фазы, выполняемой за (S+1) тактов, происходит последовательное обращение к ячейкам блока 11 па1 {яти, формирование очередного псевдослучайного кода в генераторе 12 псевдо- случайных кодов и накопление в первом регистре 5 дизъюнкции, получаемой на АЛУ 7, их логический произведений„ получаемых с помощью второй группы элементов И 10. При этом вероятность сохранения нулевого значения но вто1

ром регистре 5 равна Р , где ,5 - вероятность появления нуля в псевдослучайной последовательности, К i S - количество единиц в последовательности из блока 11 памяти. Для получения значений вероятностей, равных ), в последнем, ()-м такте выполняется операция сложения по модулю 2 содержимого регистра 5 с единичными значениями соответствующих последовательностей из блока 11 памяти.

45

Во время первой фазы в течение S тактов возможна запись значений по- следовательности из блока 11 памяти,, в соответствующие разряды выходного регистра 1, что дает возможность по- давать ка объект диагностирования различные S-тактные детерминированные сигналЫо Вторая фаза состоит из (tn-1) тактов, в каждом из которых происходит запись пол ченного в конце пер вой фазы псевдослучайного кода с ре- гистра 5 в соответствующие разряды

вой фазы псевдослучайного кода с ре- гистра 5 в соответствующие разряды

выходного регистра 1. Каждая микрокоманда записи в выходной регистр 1.

оперирует со своим регистром 3.1-З.т маскио Запись происходит только в те разряды выходного регистра 1, вход1Ь1 разрешения записи которых размаскированы содержимым выбранного регистра маски, код которого содержится в микрокоманде и подается на дешифратор 4. Таким образом, в течение одного цикла происходит изменение сигналов на всех выходах генератора, входящих в группу, для которой формируется псевдоциклический код. Абсолютное быстродействие генератора (быстродействие по одному выходу) определяется длительностью одного цикла, равной (S+m) тактов, а относительное бь1стро действие (быстродействие по соседн 1м выходам в группе) определяется длительностью одного такта, У прототипа при формировании аналогичной последовательности прибавляется один такт в начале первой фазы - для занесен я маски, разрешающей-запись в выходной регистр детерминированны х сигналов из соответствующей области памяти блока 11 в регистр маски, и (т-1) тактов во второй фазе - для занесения соответствующих масок в регист)э маски перед каждым тактом записи псевдослучайного кода в выходной регистр, т,е, длительность одного цикла больше на тп тактов и равна (S+2m) тактов, изменение сигналов на соседни: выходах в группе происходит через один такт. Таким образом абсолютное быстродействие предлагаемого генераS-«-2m

тора в -:;- - раз вьнпе, чем у прототи- S+m

па, а относительное вьнпе вдвое,

При необходимости сочетания в рамках одной испытательной последовательности различных сигналов, например для совмещения формирования псевдослучайных (псевдоциклических) последовательностей кодов и циклически посторяющихся детерминированных сигналов с вьздачей произвольных тестов, предлагаемый генератор также имеет преимущество в быстродействии. Микропрограмму для такой последовательности можно представить как совокупность отдельных микропрограмм для каждого типа сигналов, микрокоманды котогйпс чередуются. При этом каждая отдельная микропрограмма оперирует со своими регистрами маски (без перекрытий), Предлагаемьй генератор тестовых воздействий имеет возможность не только подавать сигналы на объект диагностирования, но и принимать его реакции в регистр 5 через второй блок 8

5 мультиплексоров. Эти реакции могут быть записаны в блок 11 памяти для последующего анализа, а также использоваться в качестве операндов АЛУ 7, например, для сравнения с эталонными

0 значениями, хран ймыми в блоке 11 памяти, .для определения факта изменения сигнала на каком-либо выходе объекта диагностирования (в этом случае реакция, принятая в регистр 5,

5 передается в регистр 6, а в первый принимается новая реакция, затем на АЛУ 7 происходит сравнение) и т,п.

Наличие внутренней магистрали данных генератора (связьгоающей блок

0 1t памяти, входы выходного регистра 1, блока 3 регистров маски и регистра 6), регистров 5 и 6, второго и первого 9 блоков мультиплексоров позволяет в одном такте выдавать на вхо5 ды объекта (через выходной регистр) тестовое воздействие, принимать эталонные значения выходных реакций во второй регистр и действительные реакции в первьй регистр. При соединении

0 соответственно выходов 18 генератора с входами 17 (в реальной контрольной аппаратуре на основе предлагаемого генератора эта связь через буферы имеет место) предлагаемый генератор

g может осуществлять эффективный самоконтроль.

Формула изобретения 1, Генератор тестовых воздействий,

0 содержащий выходной регистр, первый регистр масок, арифметико-логическое устройство, блок памяти, генератор псевдослучайных кодов, блок управления, причем выход выходного регистра

5 подключен к выходу генератора, информационный вход выходного регистра и информационньй вход первого регистра масок подключены к шине данных блока памяти, входы синхронизации первого регистра масок, входы управления арифметико-логического устройства, генератора псевдослучайных кодов и вход адреса блока памяти подключены к соответствующим выходам стробов управления и клдов операции и адреса блока управления, отличающийся тем, что, с целью повышения быстродействия, в него введены га-1 регистров масок, образующих блок

0

5

15

20

25

, регистров масок, дешифратор, две группы элементов И, два регистра, два буферных регистра, две группы мультиплексоров, присеем управляющий вход поразрядного приема выходного регистра подключен к выходу элементов И первой группы, первые входы которых подключены к поразрядно объединенным выходам регистров масок ю блока, вторые входы элементов И первой группы подключены к выходу стро- бирования выдачи информации блока управления, выходы стробирования приема масок которого подключены к соответствующим входам га-1 регистров масок блока, информационные входы которых подключены к шине данных блока памяти, входы разрешения чтения m регистров масок подключены к соответствующим выходам дешифратора, вход которого подключен к выходу поля кода выбора одного из регистров масок блока управления, выход генератора псевдослучайных кодов подключен к первым входам элементов И второй группы, вторые входы которых подключены к шине данных блока памяти, выходы элементов И второй группы подключены к первому информационному входу первого блока мультиплексоров, второй информационный вход которого подключен к шине данных блока памяти, управляющие входы первого и второго блоков мультиплексоров подключены к выходу соответствующих разрядов поля управления выбором источника данных блока управления, выход первого блока мультиплексоров подключен к входам первого регистра, выход которого подключен к входу первого операнда -арифметико-погичес-. кого устройства, вход второго операнда которого и вход первого буферного регистра подключены к выходу второго регистра, информационный выход арифметико-логического устройства подключен к первому информационному входу второго блока мультиплексоров, второй информационньй вход которого подключен к входу информации объекта диагностирования генератора, вход синхронизации второго регистра и входы синхронизации первого буферного

и первого регистра подключеходы первого и второго буферных регистров подключены к шине данных блока памяти, вход второго буферного регистра и вход начальной загрузки информации блока управления подключены к входу исходных данных генератора, вход управления переходом блока управления подключен к выходу результата сравнения ари(5 етико-логического устройства.

30

2, Генератор по п.1, отличающийся тем, что блок управления содержит блок памяти микрокоманд, счетчик, регистр микрокоманд, дешифратор микрокоманд, регистр адреса, формирователь стробирующих сигналов, узел синхронизации, тактовый генератор, счетчик тактов, триггер пуска, буферный регистр, причем вход началь- 1Л)й загрузки блока подключен к входу буферного регистра, выход которого подключен к информационным входам регистра адреса, блока памяти микрокоманд, счетчика, счетчика тактов и входу установки триггера пуска, выход которого подключен к входу тактового генератора, выход которого подключен к входам узла синхронизации и формирователя стробирующих инмпульсов, управляющие входы которых, вход дешифратора микрокоманд, вход кода адреса перехода счетчика подключены к соответствующим разрядам выхода регистра микрокоманд, информационный вход которого подключен к выходу блока памяти микрокоманд, вход синхронизации которого, входы синхронизации регистра микрокоманд, регистра адреса, счетчика и счетчика тактов подключены к соответствующим выходам узла синхронизации, выход регистра адреса под-, ключен к выходу адреса блока управле- Д5 ния, вход регистра адреса подключен к выходу поля адреса блока памяти микрокоманд, вход управления адресом i перехода счетчика подключен к входу управления переходом блока, выходы gj.:формирователя стробирующих сигналов, регистра микрокоманд и дешифратора подключены соответственно к выходам стробов управления, кода операции и стробирования приема масок блока

35

40

регистра и первого регистра подключе- управления, выход переполнения счет- ны к соответствующим выходам управ- . чика тактов подключен к входу сброса

ляннцих стробов блока управления, выю9564

ходы первого и второго буферных регистров подключены к шине данных блока памяти, вход второго буферного регистра и вход начальной загрузки информации блока управления подключены к входу исходных данных генератора, вход управления переходом блока управления подключен к выходу результата сравнения ари(5 етико-логического устройства.

2, Генератор по п.1, отличающийся тем, что блок управления содержит блок памяти микрокоманд, счетчик, регистр микрокоманд, дешифратор микрокоманд, регистр адреса, формирователь стробирующих сигналов, узел синхронизации, тактовый генератор, счетчик тактов, триггер пуска, буферный регистр, причем вход началь- 1Л)й загрузки блока подключен к входу буферного регистра, выход которого подключен к информационным входам регистра адреса, блока памяти микрокоманд, счетчика, счетчика тактов и входу установки триггера пуска, выход которого подключен к входу тактового генератора, выход которого подключен к входам узла синхронизации и формирователя стробирующих инмпульсов, управляющие входы которых, вход дешифратора микрокоманд, вход кода адреса перехода счетчика подключены к соответствующим разрядам выхода регистра микрокоманд, информационный вход которого подключен к выходу блока памяти микрокоманд, вход синхронизации которого, входы синхронизации регистра микрокоманд, регистра адреса, счетчика и счетчика тактов подключены к соответствующим выходам узла синхронизации, выход регистра адреса под-, ключен к выходу адреса блока управле- ния, вход регистра адреса подключен к выходу поля адреса блока памяти микрокоманд, вход управления адресом перехода счетчика подключен к входу управления переходом блока, выходы формирователя стробирующих сигналов, регистра микрокоманд и дешифратора подключены соответственно к выходам стробов управления, кода операции и стробирования приема масок блока

триггера пуска.

1

fcS

-S

ffC

L

oi /arffn.

fi4. .

Alv.pMt У n ,.

iv .

ff.fM.1

fti.fff-i

jJT

пь«

гъ

Лг

Jl.

гь

П

АПГ

НОГ

КРН Ш

;

СбГ

м

АПК

9иг.5

| Установка для получения многоцветных мультиплицированных изображений | 1973 |

|

SU468211A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор псевдослучайных кодов | 1978 |

|

SU767743A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1987-03-06—Подача