$ ю

01 д

Изобретение относится к вычислительной технике и автоматике, может быть использовано в цифровых системах управления для преобразования в цифровой код сигналов частотных датчиков и является дополнительным к изобретению по авт. св. К 970681.

Цель изобретения - повышение быстродействия и расширение области использования за счет возможности предварительного получения грубой оценки измеряемой частоты.

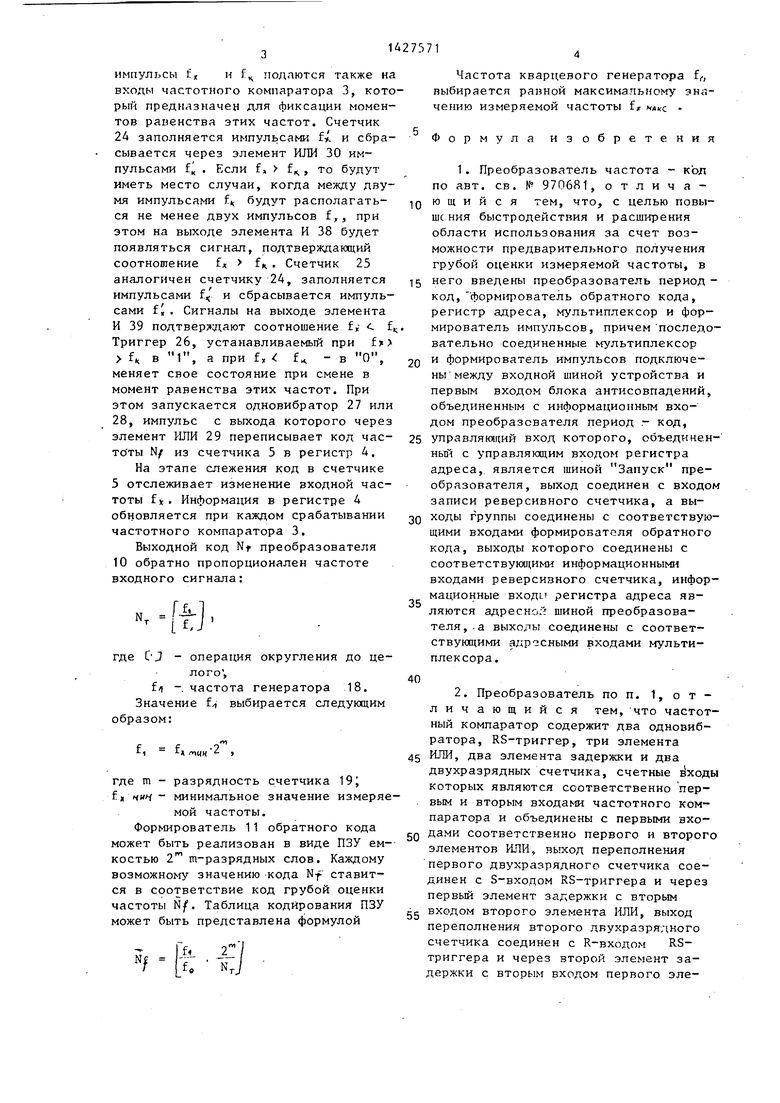

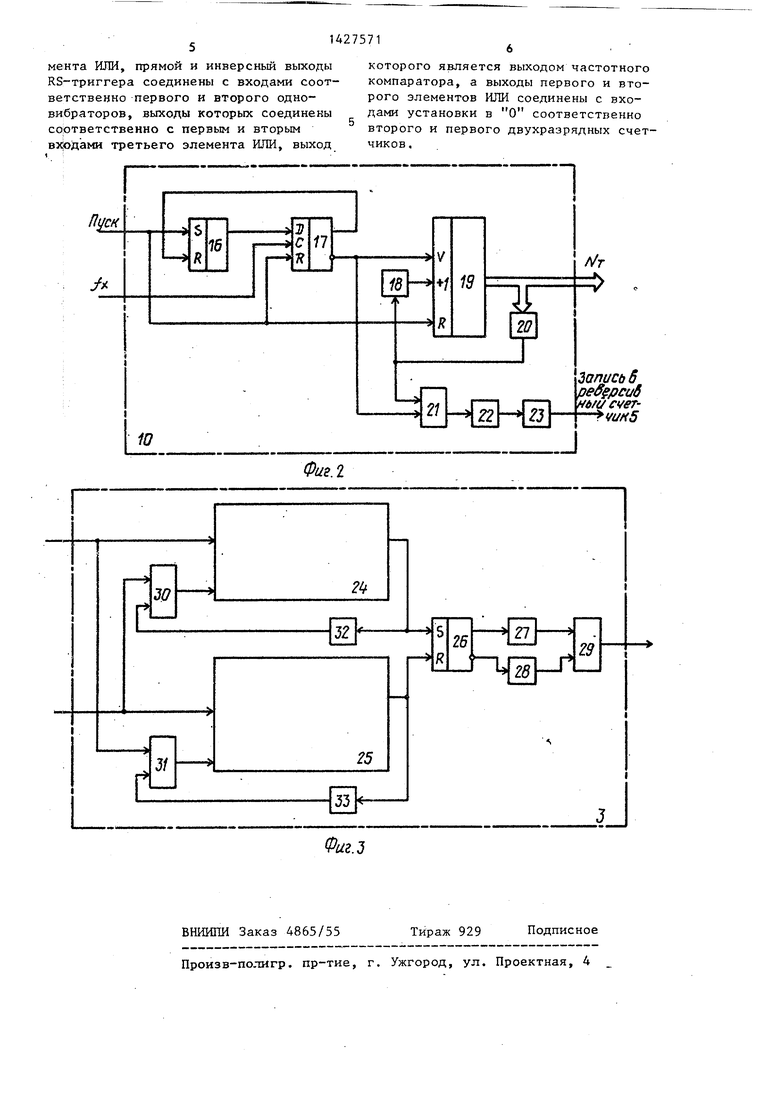

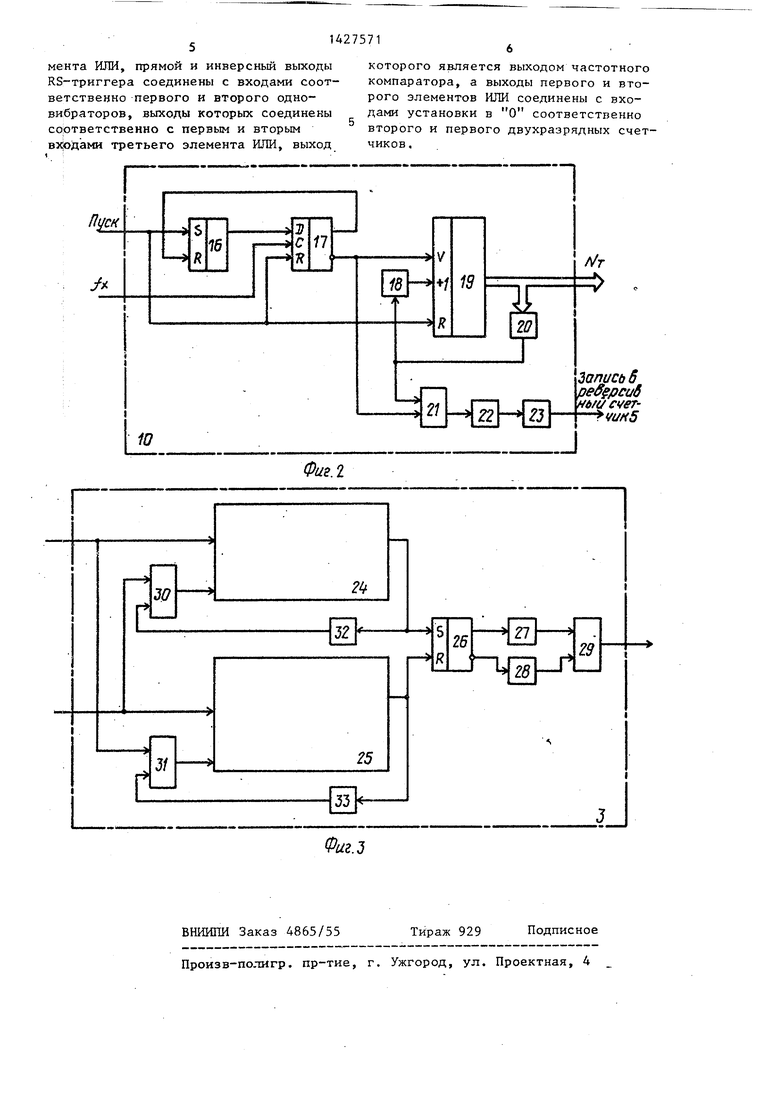

На фиг. 1 представлена структурная схема предлагаемого преобразователя, на фиг. 2 и 3 - схемы соответственно преобразователя период - код и частотного компаратора.

Преобразователь (фиг.1) содержит блок 1 антисовпадений,кварцевый генератор 2,частотный компаратор 3,регистр 4 памяти, реверсивный счетчик 5, преобразователь 6 код - частота, регистр 7 адреса, мультиплексор 8,.формирователь 9 импульсов, преобразователь 10 период - код, формирователь 11 обратного кода, шину 12 Запуск, адресную шину 13, входную шину 14 и выходную шину 15.

Преобразователь период - код (фиг. 2) образуют RS-триггер 16, D- триггер 17, генератор 18, счетчик 19, элемент И 20, элемент ИЛИ 21, элемент 22 задержки и одновибратор 23. :

Частотный компаратор (фиг. 3) включает двухразрядные счетчики 24 и 25, RS-триггер 26, одновибраторы 27 и 28, элементы ИЛИ 29-31 и элементы 32 и 33 задержки.

Преобразователь работает следующим образом.

Весь процесс получения кода частоты состоит из трех этапов: этап быстрого получения грубой ошибки измеряемой частоты, эта-п дослеживания и этап слежения.

На этапе грубой оценки импульс на шине 12 осуществляет запись кода с шины 13 в регистр 7 адреса. При этом код адреса поступает на вход мультиплексора 8, коммутирующего в соответствии с ним один из входных сигналов с шины 14 через формирователь 9 импульсов на первый вход блока 1 антисовпадений и информационный вход преобразователя 10. После окончания импульса запуска преобразователь 10 измеряет интервал времени между первым и вторым импульсами входной час

0

5

0

5

0

5

0

5

0

5

тоты fjc следующим образом. Импульс запуска устанаш1Ивает в единицу три1- гер 16 и обнуляет счетчик 19 и триггер 17. Первьй импульс f устанавливает в единицу триггер 17, который сбрасывает триггер 16 и разрешает работу счетчика 19. Счетчик 19 заполняется импульсами частоты f генератора 18. Второй импульс fi сбрасывает триггер 17 и запрещает работу счетчика 19. Сигнал с инверсного выхода триггера 17 проходит через элемент ИЛИ 21, элемент 22 задержки и запускает одновибратор 23, импульс которого стробирует запись в счетчик 5. Элемент И 20 срабатывает при заполнении счетчика 19, при этом блокируется работа генератора 18, и через элемент ИЛИ 21 и элемент задержки 22 запускается одновибратор 23. Это необходимо для предотвращения переполнения счетчика 19. Код периода N,. с выхода преобразователя 10 поступает на формирователь 11, который преобразует код периода N в код грубой оценки частоты V}, записываемый в старшие разряды реверсивного счетчика 5 по импульсу одновибрато- ра 23. Элемент 22 задержки необходим для задержки импульса записи на время получения обратного кода в формирователе 11.

На этапе дослеживания устраняется рассогласование истинным значением измеряемой частоты и грубой оценкой, полученной при измер.ении периода if . Преобразователь 6, представляющий собой триггерный делитель частоты, управляемьп кодом счетчика 5, формирует из частоты fj. -кварцевого генератора 2 сигнал компенсирующей частоты f , соответствующий коду в счетчике 5 в каждый момент времени. Частоты ЕЛ и fx подаются на входы блока 1, который осуи;ествляет их привязку.к двум синхронизирукщим несовпадающим последовательностям - сигналам с прямого и инверсного выходов генератора 2. С выходов блока 1 импульсы fi и f поступают соответственно на суммирующий и вычитающий входы счетчика 5. При этом направление и скорость изменения кода в счетчике определяются разностью частот i) - ЕК . Например, если f fк, код в счетчике 5 увеличивается, при этом частота f будет возрастать вплоть до момента f f . С выход; , блока 1

импульсы I K н Гц, подаются также на входы частотного компаратора 3, который предназначен для фиксации моментов равенства этих частот. Счетчик 2А заполняется импульсами fiJ. и сбрасывается через элемент ИЛИ 30 импульсами f . Если f, fк,, то будут иметь место случаи, когда между двумя импульсами f, будут располагать- ся не менее двух импульсов ,, при этом на выходе элемента И 38 будет появляться сигнал, подтверждающий соотношение « fк. Счетчик 25 аналогичен счетчику 24, заполняется импульсами f и сбрасывается импульсами , . Сигналы на выходе элемента И 39 подтверз :дают соотношение f f Триггер 26, устанавливаемый при if f в 1, а при f, f - в О, меняет свое состояние при смене в момент равенства зтих частот. При этом запускается одновибратор 27 или 28, импульс с выхода которого через элемент ИЛИ 29 переписывает код час- то ты N/ из счетчика 5 в регистр 4.

На этапе слежения код в счетчике 5 отслеживает изменение входной частоты fк. Информация в регистре 4 обновляется при каждом срабатывании частотного компаратора 3.

Выходной код Nf преобразователя 10 обратно пропорционален частоте входного сигнала:

N Л NT f

где Cj

операция округления лого ,

fi -.частота генератора Значение f выбирается сле образом:

пу

к

где m - разрядность f, пин счетчика 19J

минимальное значение измеряемой частоты.

Формирователь 11 обратного кода может быть реализован в виде ПЗУ емкостью 2 т-разрядных слов. Каждому возможному значению кода Nf ставится в соответствие код грубой оценки частоты N. Таблица кодирования ПЗУ может быть представлена формулой

Nf

1.1 f

2

NT,

Q g 5

Q

5

Частота кварцевого генератора f, выбирается равной максимальному значению измеряемой частоты f/

Формула изобретения

1. Преобразователь частота - код по авт. св. № 970681, отличающийся тем, что, с целью повыше ния быстродействия и расширения области использования за счет возможности предварительного получения грубой оценки измеряемой частоты, в него введены преобразователь период - код,формирователь обратного кода, регистр адреса, мультиплексор и формирователь импульсов, причем последовательно соединенные мультиплексор и формирователь импульсов подключены между входной шиной устройства и первым входом блока антисовпадений, объединенным с информационным входом преобразователя период .- код, управляющий вход которого, объединен- Hbtfi с управляющим входом регистра адреса, является шиной Запуск преобразователя, выход соединен с входом записи реверсивного счетчика, а выходы группы соединены с соответствующими входами формирователя обратного кода, выходы которого соединены с cooтвeтcтвyюu ими информационными входами реверсивного счетчика, информационные входи регистра адреса являются адресное шиной преобразователя,, а выходы соединены с соответ- ствуюа1ими адр зсными входами мультиплексора.

40

5

0

2. Преобразователь по п. 1, о т - личающийся тем, что частотный компаратор содержит два одновиб- ратора, RS-триггер, три элемента ИЛИ, два элемента задержки и два двухразрядных счетчика, счетные йходы которых являются соответственно первым и вторым входами частотного компаратора и объединены с первыми входами соответственно первого и второго элементов ИЛИ, выход переполнения первого двухразрядного счетчика соединен с S-входом RS-триггера и через первый элемент задержки с вторым g входом второго элемента ИЛИ, выход переполнения второго двухразрядного счетчика соединен с R-входом RS- триггера и через второй элемент задержки с вторым входом первого элес1А27571

j6

мента ИЛИ, прямой и инверсный выходыкоторого является выходом частотного

RS-триггера соединены с входами соот-компаратора, а выходы первого и втоветственно первого и второго одно-рого элементов ИЛИ соединены с вховибраторов, выходы которых соединеныдами установки в О соответственно

соответственно с первым и вторымГ1тг, „ г,г,„

входами третьего элемента ИЛИ, выход

второго и первого двухразрядных счетчиков ,

Г1тг, „ г,г,„

второго и первого двухразрядных счетчиков ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ЧЕТЫРЕХФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1998 |

|

RU2133550C1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Преобразователь частота-код | 1981 |

|

SU970681A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство коммутации сенсорных площадок | 1987 |

|

SU1554134A1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

Изобретение относится к вычислительной технике и автоматике, может быть использовано в цифровых системах управления для преобразования в циф ровой код сигналов частотных датчиков и является дополнительным к основному авт. св. № 970681. Изобретение позволяет повысить быстродействие и расширить область использования преобразователя. Для этого в преобразователь, содержащий блок 1 антисовпадений, кварцевый генератор 2, частот- ньй компаратор 3, регистр 4 памяти, реверсивный счетчик 5, преобразователь 6 код - частота, введены регистр 7.адреса, мультиплексор 8, формирователь 9 импульсов, преобразователь 10 период - код и формирователь 11 обратно1 о кода, что позволило быстро получагь грубую оценку измеряемой частоты с последующим устранением рассогласования между полученным и истинным значениями измеряемой частоты, а также применять преобразователь Q в многоканальных системах измерения частотных сигналов, в которых при переключении кььапов значение измеряемой частоты и- меняется скачкообразно. 1 з.п. ф-лы, 3 ил. S (Л

| Преобразователь частота-код | 1981 |

|

SU970681A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-30—Публикация

1987-03-30—Подача