блока вьщеления большей и меньшей частоты, выход второго элемента И соединен с единичным входом второго триггера и с вторым входом элемента ИЛИ, выход элемента 2И-ИЛИ соединен с нулевыми входами первого и второго триггеров и является вторым входом блока вьделения большей и меньшей ча

169146

стоты, прямой выход первого триггера подключен к третьему входу элемента 2И-ИЛИ, инверсный выход - к второму входу второго элемента И, прямой выход второго триггера - к четвертому входу элемента 2И-ИЛИ, а инверсный выход - к второму входу первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ детектирования манипулированных по частоте и фазе сигналов воспроизведения цифровой магнитной записи и устройство для его осуществления | 1989 |

|

SU1608743A2 |

| Стереоприемник частотномодулированных сигналов | 1986 |

|

SU1328940A1 |

| Сумматор @ частотно-импульсных сигналов | 1982 |

|

SU1156068A1 |

| Когерентный демодулятор сигналов двукратной относительной фазовой манипуляции | 1986 |

|

SU1345369A1 |

| Способ детектирования манипулированных по частоте и фазе сигналов воспроизведения цифровой магнитной записи и устройство для его осуществления | 1987 |

|

SU1529282A1 |

| Цифровой фильтр | 1980 |

|

SU926761A1 |

| Цифровой имитатор радиотелеграфного канала связи | 1985 |

|

SU1275465A1 |

| Система передачи цифровой информации | 1984 |

|

SU1185636A1 |

| Вычислительное устройство | 1986 |

|

SU1325474A1 |

| Измеритель временных интервалов | 1979 |

|

SU845140A1 |

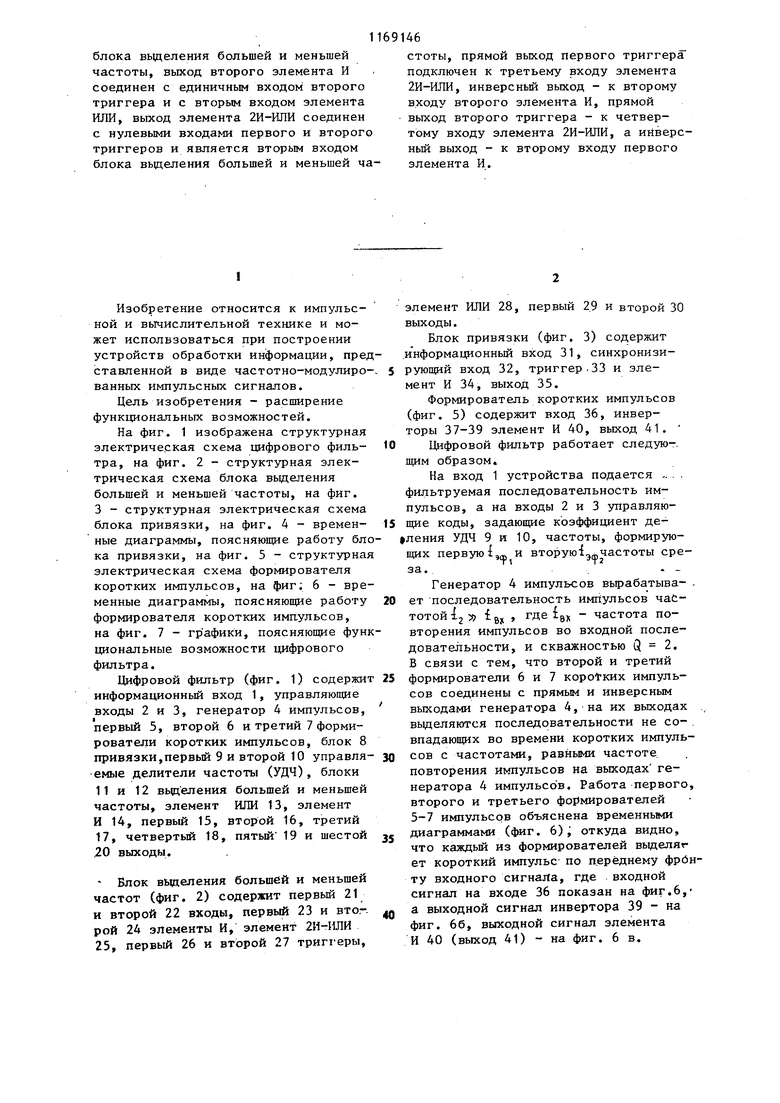

1. ЦИФРОВОЙ ФИЛЬТР, содержащий генератор импульсов, первый и ... второй управляемые делители частоты, первьш формирователь коротких импульсов, вход .которого является информационным входом цифрового фильтра, и элемент И, отличающий с я тем, что, с целью расширения функциональных возможностей, введены второй и третий формирователи коротких импульсов, блок привязки, первый и второй блоки вьщеления большей и меньшей частоты и элемент ИЛИ, при .этом вход второго .формирователя коротких импульсов подключен к прямому выходу генератора импульсов, а выход - к входам лервого и второго управляемых делителей частоты, вход третьего формирователя коротких импульсов подключен к инверсному выходу генератора импульсов, а выход - к синхронизирующему входу блока привязки, информационный вход которого соединен с выходом первого формирователя коротких импульсов, а выход - с первыми входами первого и второго блоков выделения большей и меньшей частоты, вторые входы которых подключены к выходам соответственно первого и второго управляемых делителей частоты, при этом первый выход первого блока вьщеления большей и меньшей частоты соединен с первым входом элемента И и является первым выходом цифрового фильтра, второй выход соединен с первым входом элемента ИЛИ и является вторым выходом цифрового фильтра, первый выход второго блока выделения большей и меньшей частоты 1О соединен с вторым входом элемента (Л ИЛИ, выход которого является третьим .. выходом цифрового фильтра,и является с: четвертым выходом цифрового фильтра,а второй выход является пятым выходом цифрового фильтра и соединен с втог рым входом элемента И, выход кото-, рого является шестым выходом цифрового фильтра. О5 2. Фильтр Но п. 1, отличаюсо 4 щийся тем, что каждьй блок вьщеления большей и меньшей частоты содержит два элемента И, элемент 2ИО) ИЛИ, элемент ИЛИ-и два триггера, при этом первый вход первого элемента И объединен с первым входом элемента 2И-ИЛИ и является первым входом блока выделения большей и меньшей чacтoты вторым входом которого являются объединенные первый вход второго элемента И и второй вход элемент-а 2И-ИЛИ, выход первого элемента И соединен с единичным входом первого триггера и с первым входом элемента ИЛИ, выход которого является первым-выходом

Изобретение относится к импульсной и вычислительной технике и может использоваться при построении устройств обработки информации, представленной в виде частотно-модулированных импульсных сигналов.

Цель изобретения - расширение функхщональных возможностей.

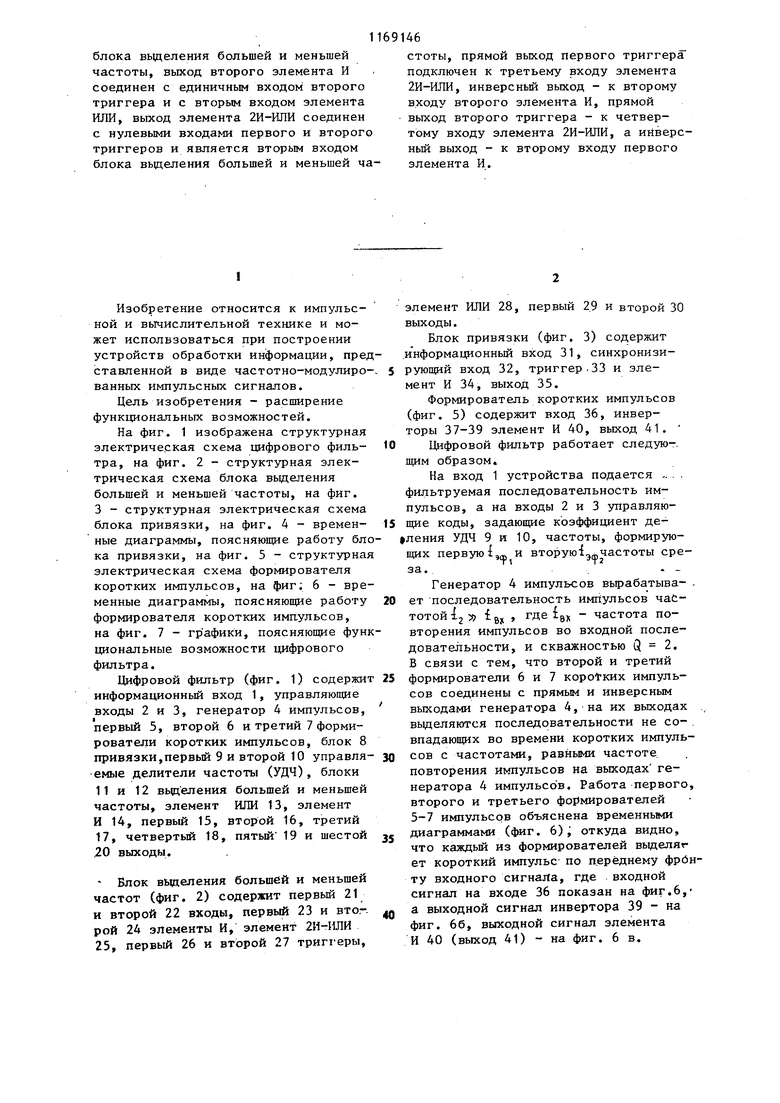

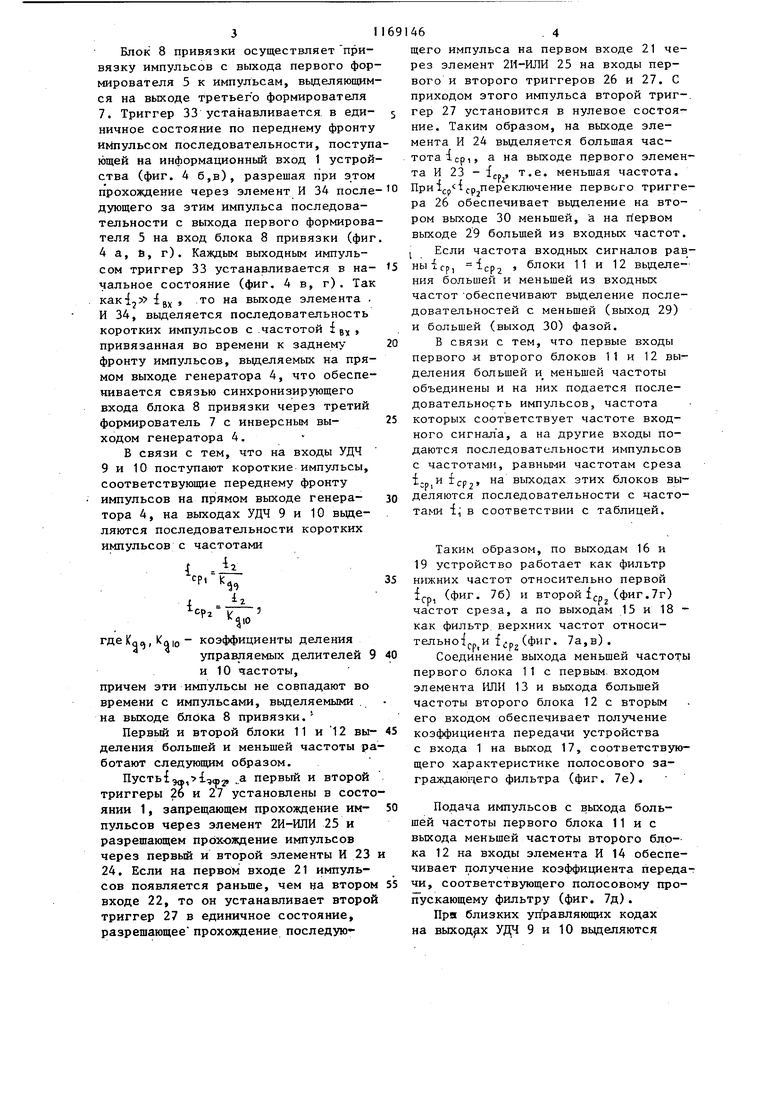

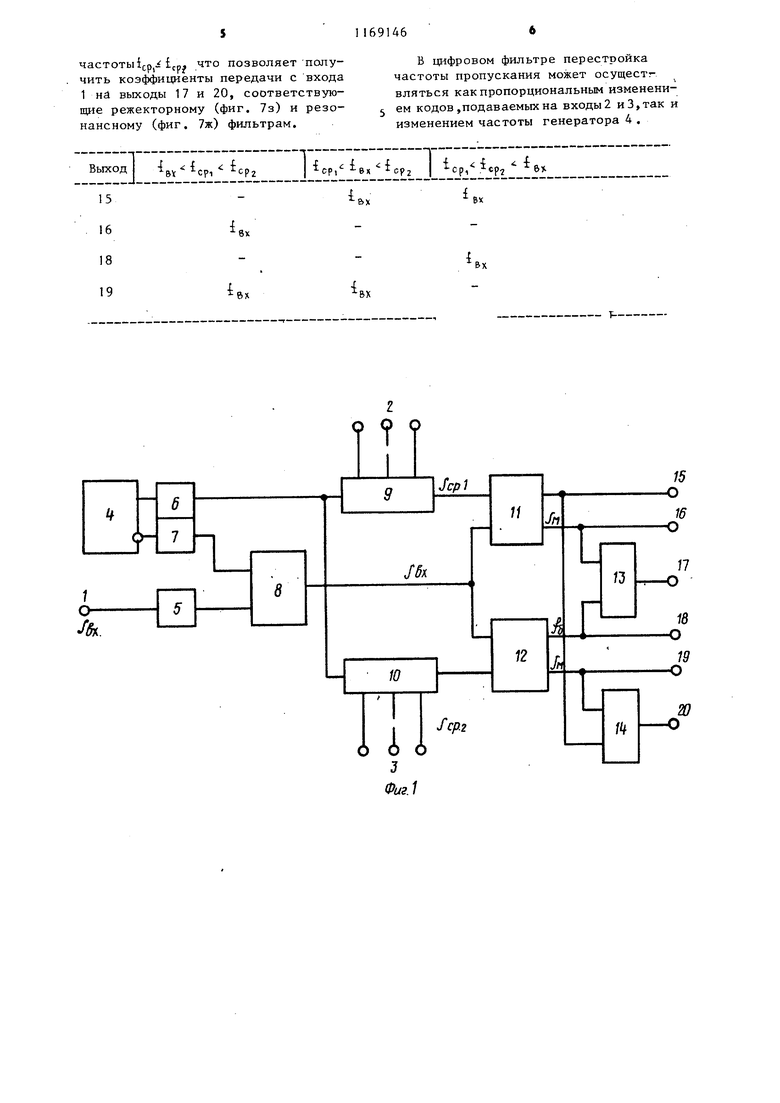

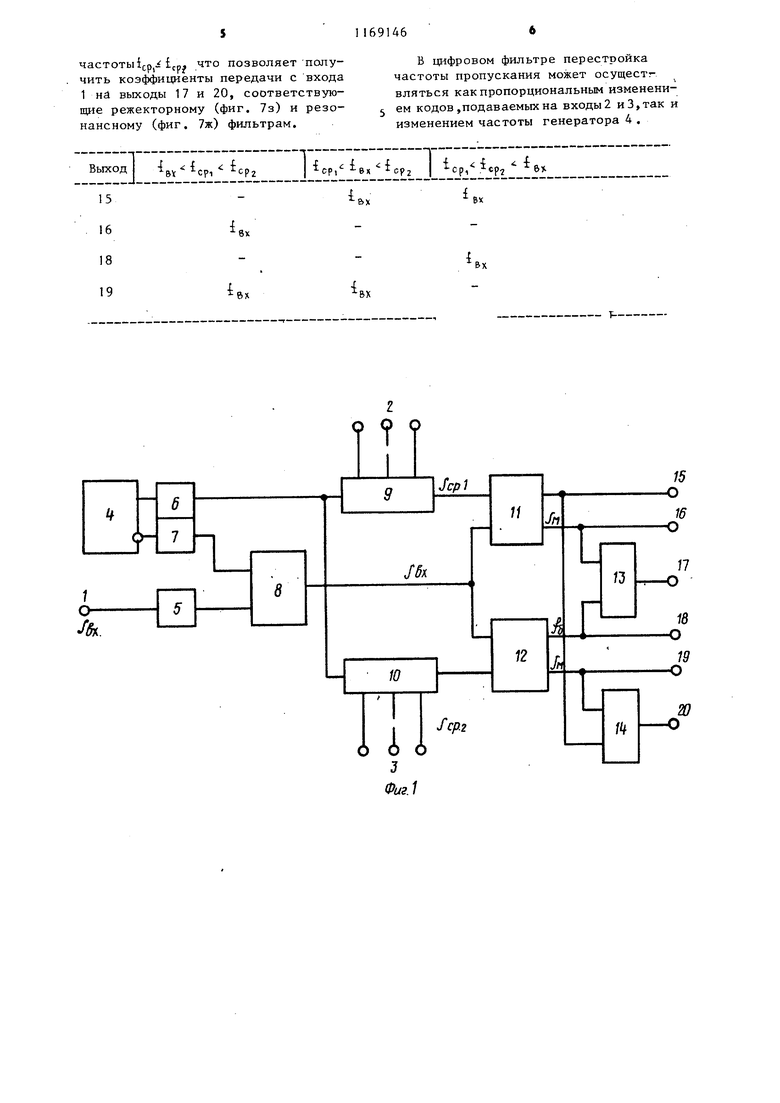

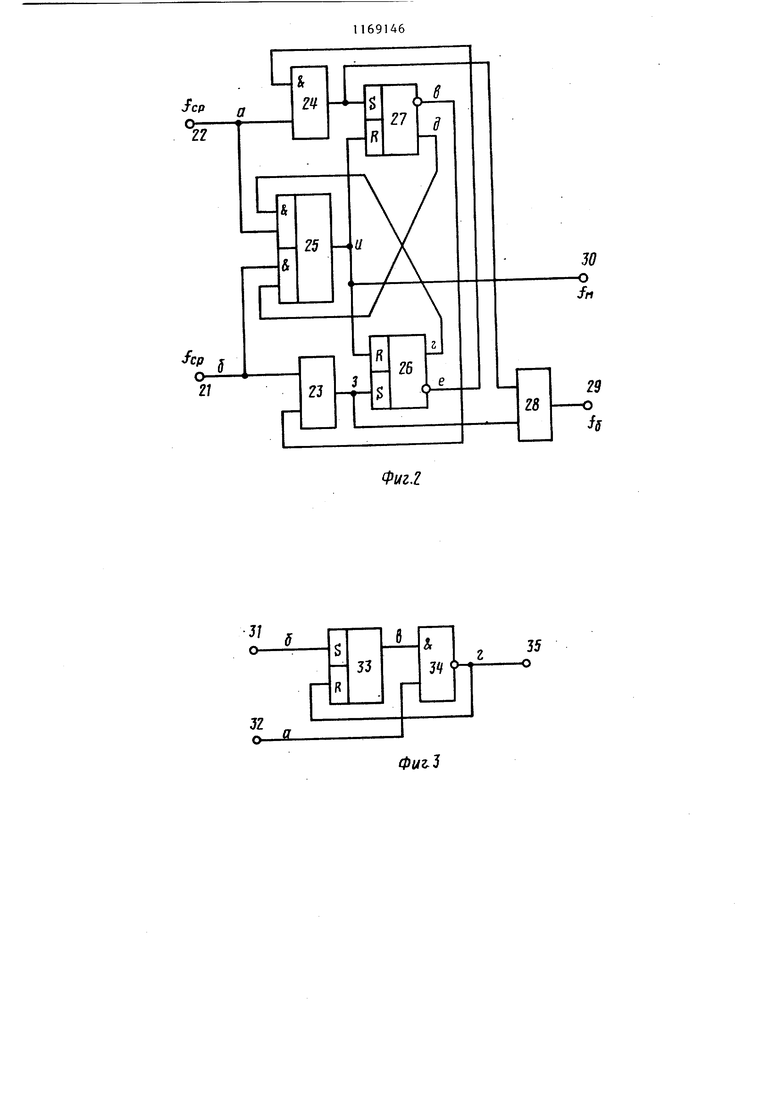

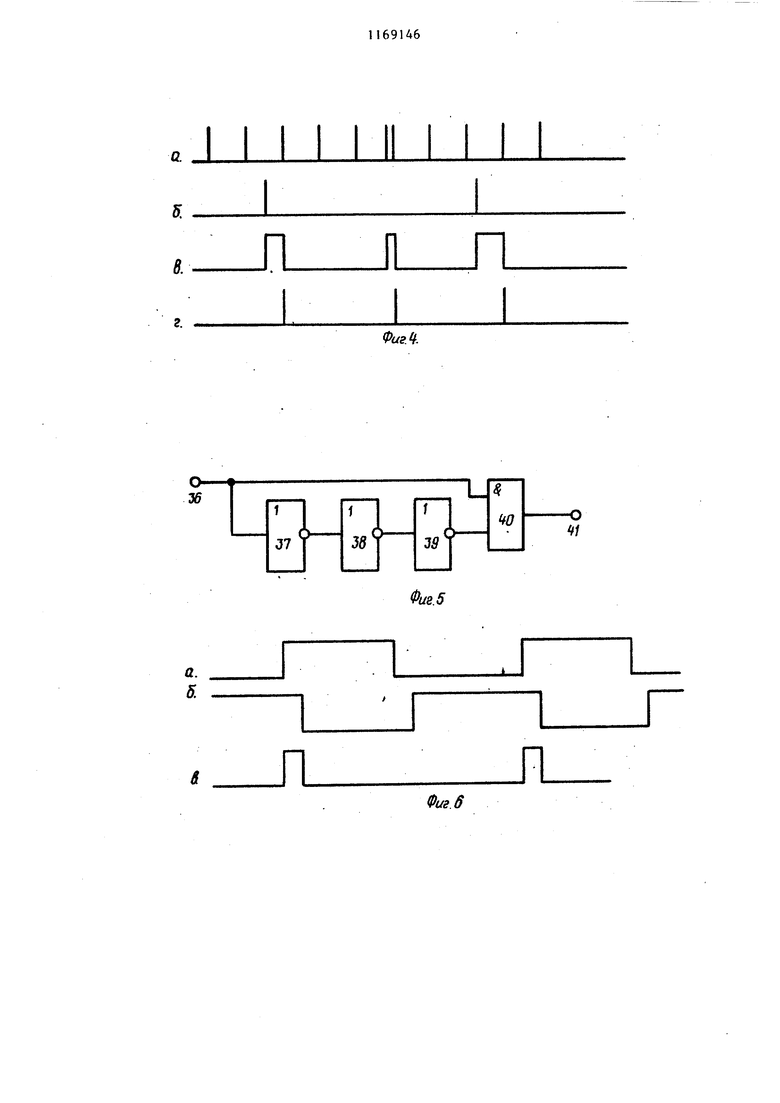

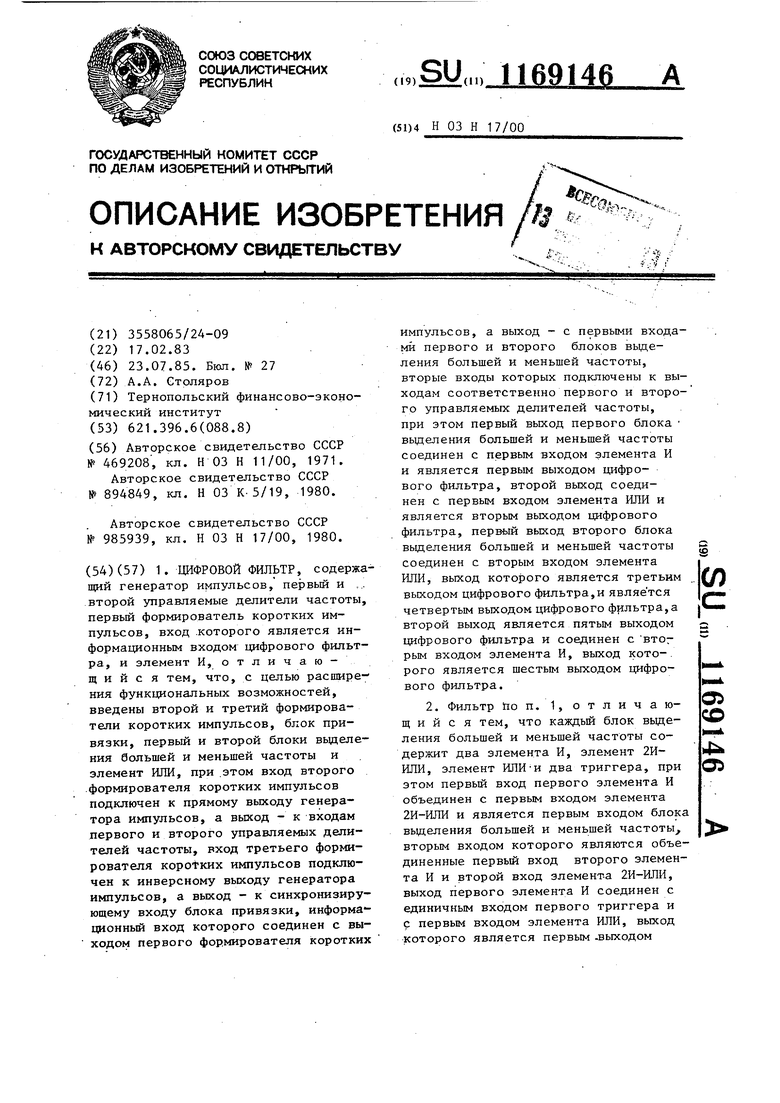

На фиг. 1 изображена структурная электрическая схема цифрового фильтра, на фиг. 2 - структурная электрическая схема блока вьщеления большей и меньшей частоты, на фиг. 3 - структурная электрическая схема блока привязки, на фиг. 4 - временные диаграммы, поясняющие работу блока привязки, на фиг. 5 - структурная электрическая схема формирователя коротких импульсов, на фиг; 6 - временные диаграммы, поясняющие работу формирователя коротких импульсов, на фиг. 7 - графики, поясняющие функциональные возможности цифрового фильтра.

Цифровой фильтр (фиг. 1) содержит информационный вход 1, управляющие входы 2 и 3, генератор 4 импульсов, первый 5, второй 6 и третий 7 формирователи коротких импульсов, блок 8 привязки,первьш 9 и второй 10 управляемые делители частоты (УДЧ), блоки 11 и 12 вьиеления большей и меньшей частоты, элемент ИЛИ 13, элемент И 14, первый 15, второй 16, третий 17, четвертый 18, пятый 19 и шестой .20 выходы.

Блок вьщеления большей и меньшей частот (фиг. 2) содержит первый 21 и второй 22 входы, первый 23 и второй 24 элементы И, элемент 2И-1ШИ 25, первый 26 и второй 27 триггеры,

элемент ИЛИ 28, первый 29 и второй 30 выходы.

Блок привязки (фиг. 3) содержит .информационный вход 31, синхронизирующий вход 32, триггер.33 и элемент И 34, выход 35.

Формирователь коротких импульсов (фиг. 5) содержит вход 36, инверторы 37-39 элемент И 40, выход 41.

Цифровой фильтр работает следую-, щим образом.

На вход 1 устройства подается

фильтруемая последовательность импульсов, а на входы 2 и 3 управляющие коды, задающие коэффициент де ления УДЧ 9 и 10, частоты, формирующих первую 1,ф и вторую1,,я,частоты сре,

этГ за.

Генератор 4 импульсов вырабатывает последовательность имйульсов частотой Xj i вл гД вх частота повторения импульсов во входной последовательности, и скважностью Q 2. В связи с тем, что второй и третий формирователи 6 и 7 импульсов соединены с прямым и инверсным выходами генератора 4, на их выходах выделяются последовательности не совпадающих во времени коротких импульсов с частотами, равными частоте повторения импульсов на выходах генератора 4 импульсов. Работа первого, второго и третьего формирователей 5-7 импульсов объяснена временньми диаграммами (фиг. 6)j откуда видно, что каждый из формирователей выделягет короткий импульс по дерёднему фрбнту входного сигнала, где входной сигнал на входе 36 показан на фиг.б,а выходной сигнал инвертора 39 - на фиг. 6б, выходной сигнал элемента И 40 (выход 41) - на фиг. 6 в. 3 Блок 8 привязки осуществляет привязку импульсов с выхода первого фор мирователя 5 к импульсам, выделяющим ся на выходе третьего формирователя 7. Триггер 33 устанавливается в единичное состояние по переднему фронту импульсом последовательности, поступ ющей на информационный вход 1 устрой ства (фиг. 4 б,в), разрешая при этом прохождение через элемент И 34 после дующего за этим импульса последовательности с выхода первого формирова теля 5 на вход блока 8 привязки (фи 4 а, в, г). Каждым выходным импульсом триггер 33 устанавливается в начальное состояние (фиг. 4 в, г). Так KaKlj ia)( , то на выходе элемента . И 34, выделяется последовательность коротких импульсов с .частотой i zt привязанная во времени к заднему фронту импульсов, выделяемых на прямом выходе генератора 4, что обеспечивается связью синхронизирующего входа блока 8 привязки через третий формирователь 7 с инверсным выходом генератора 4. В связи с тем, что на входы УДЧ 9 и 10 поступают короткие импульсы, соответствующие переднему фронту импульсов на прямом выходе генератора 4, на выходах УДЧ 9 и 10 выделяются последовательности коротких импульсов с частотами ЬСрг гдеКад,Кл1о- коэффициенты деления управляемых делителей 9 и 10 частоты, причем эти импульсы не совпадают во времени с импульсами, выделяемыми . на выходе блока 8 привязки. Первый и второй блоки 11 и 12 вы- деления большей и меньшей частоты ра ботают следующим образом. Пусть эа, 90)2 .. первый и второй триггеры 26 и 27 установлены в состо янии 1, запрещающем прохождение импульсов через элемент 2И-ИЛИ 25 и разрешающем прохождение импульсов через первый и второй элементы И 23 24. Если на первом входе 21 импульсов появляется раньше, чем на втором входе 22, то он устанавливает второй триггер 27 в единичное состояние, разрешающее прохождение последую46. 4 щего импульса на первом входе 21 через элемент 2И-ИЛИ 25 на входы первого и второго триггеров 26 и 27. С приходом этого импульса второй триг-. гер 27 установится в нулевое состояние. Таким образом, на выходе элемента И 24 выделяется большая частота Icpi, а на выходе п.ервого элемента И 23 - 1,0. т.е. меньшая частота. г г гг При1(. (.р переключение первого триггера 26 обеспечивает выделение на втором выходе 30 меньшей, а на йервом выходе 29 большей из входных частот. J Если частота входных сигналов равны icp, срг блоки 11 и 12 вьделе- ния большей и меньшей из входных частот обеспечивают выделение последовательностей с меньшей (выход 29) и большей (выход 30) фазой. В связи с тем, что первые входы первого и второго блоков 11 и 12 выделения большей и меньшей частоты объединены и на них подается последовательность импульсов, частота которых соответствует частоте входного сигнала, а на другие входы подаются последовательности импульсов с частотами, равными частотам среза 1. и icf2 выходах этих блоков выделяются последовательности с частотами ii в соответствии с таблицей. Таким образом, по выходам 16 и 19 устройство работает как фильтр нижних частот относительно первой icp, (фиг. 76) н второй f(.p (фиг.7г) частот среза, а по выходам 15 и 18 как фильтр верхних частот относитeльнoi P и 1(.р2(фиг. 7а,в). Соединение выхода меньшей частоты первого блока 11 с первым входом элемента ИЛИ 13 и выхода большей частоты второго блока 12 с вторым его входом обеспечивает получение коэффициента передачи устройства с входа 1 на выход 17, соответствующего характеристике полосового заграждающего фильтра (фиг. 7е). Подача импульсов с выхода большей частоты первого блока 11 и с выхода меньшей частоты второго блока 12 на входы элемента И 14 обеспечивает получение коэффициента передачи, соответствующего полосовому пропускающему фильтру (фиг. 7д). Пра близких управляющих кодах на выходах УДЧ 9 и 10 выделяются частотыi|;p| fp. что позволяет получить коэффициенты передачи с входа 1 ни выходы 17 и 20, соответствующие режекторному (фиг. 7з) и peso- , нансному (фиг, 7ж) фильтрам. В цифровом фильтре перестройка частоты пропускания может осущестгвляться как пропорциональным изменением кодов,подаваемых на входы 2 и 3,так и изменением частоты генератора 4.

ГСР

21

Фиг.

а. 5.

&

а

.2

К

к

д

Лд).Z

к

е

ЛрЛ

Ж1

J

J

ср.2

ср.2

Scp.2

п

J

Фиг: 7

| Фильтр нижних частот для импульсных сигналов | 1972 |

|

SU469208A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Анализатор частотно-фазовых соотношений двух импульсных последовательностей | 1980 |

|

SU894849A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фильтр | 1980 |

|

SU985939A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-07-23—Публикация

1983-02-17—Подача