образователя основания кода и с тактовым входом потребителя цифровой информации, выход входного согласующего блока подключен к входу порогового формирователя.

2. Система по п. 1, отличающаяся тем, что формирователь выходного сигнала содержит первый и второй операциош ые усилители, первый, йТорой, третий и четвертый элементы 2И, счетный триггер и элемент 2ИЛИ, выход которого подключен к входу счетного триггера, единичный выход которого соединен с пе)вым входом первого элемента 2И и с первым входом второго элемента 2И, второй вход которого подключен к первому входу третьего элемента 2И и к первому входу элемента 2ИЛИ, второй

вход которого подключен к второму входу первого элемента 2И и к первому входу четвертого элемента 2И, второй вход которого соединен с инверсным выходом счетного триг гера и с вторым входом третьего элемента 2И, выход которого соединен с первым входом первого операционного усилителя, второй вход которого соеди1;ен с выходом второго элемента 2И, выход первого элемента 2И подключен к первому входу второго операционного усилителя, второй вход которого соединен с выходом четвертого элемента 2И, выходы первого и второго операционных усилителей объединены и являются выходом формирователя выходного сигнала, информационными входами которого являются первый и второй входы элемента 2ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема двоичной дискретной информации | 1984 |

|

SU1218489A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1988 |

|

SU1841042A1 |

| Устройство для программного управления | 1982 |

|

SU1071998A1 |

| Устройство для приема и передачи информации | 1982 |

|

SU1089606A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| Измерительный прибор | 1989 |

|

SU1661653A1 |

| Устройство для передачи и приема информации | 1989 |

|

SU1656572A1 |

| Устройство для измерения индикатрис рассеяния света | 1990 |

|

SU1723456A1 |

| Устройство для цифровой магнитной записи | 1987 |

|

SU1432328A1 |

1. СИСТЕМА ПЕРЕД.ЛЧИ ЦИФРОВОЙ ИНФОРМАЦИИ, содержащая иа передающей стороне источник цифровой информации, информационные выходы которого соединены с информационными Бхода.п( преобразователя основания кода, формирователь выходного сигнала, выход которого подключен к вхоцу выходного согласующего блока, а на приемной стороне - входной согласующий блок, потребитель цифровой информации, информационные входы которого подключены к информационным выходам обратного преобразователя основания кода, информационные входы которого соединены с выходами решающего блока, первый вход которого соединен с выходом формирователя втори 1ных тактов, вход которого подключен к входу порогового формирователя, выход которого соединен с вторым входом рещающего блока, отличающаяся тем, что, с целью повыщения скорости передачи, на передающей стороне введены Щ1фровой модулятор и блок управления передачей, выход которого соединен с тактовым входом источника цифровой информации и с тактовым входом преобразова: еля основания кода. информационные выходы :соторого подклют чены к информационным входам цифрового модулятора, информационные выходы которого соединены с информационными входами формирователя выходного сигнала, синхронизирую1Ц1 Й выход цифрового модулятора подключен к синхронизирующему входу блока управления передачей, при этом цифровой модулятор содержит первый и второй элементы 2И, элемент 311, первый и второй элементы 2ИЛИ, делитель частоты на два и генератор стандартных импульсов, выход которого соединен с первым входом делителя частоты на два, с первым входом первого элемента 2ИЛИг § и с первым входом первого элемента 2И, W выход которого соединен с первым входом второго элемента 21ШИ и с вторым входом с делителя частоты на два, выход которого подключен к первому входу второго элемен§ та 2И и к второму входу первого элемента 2ИЛИ, выхоц которого соединен с первым входом элемента ЗН, выход которого подключен к второму входу второго элемента 2ИЛИ, второй 00 вход первого элемента 2И соединен с втopы м ел входом элемента ЗИ, третий вход которого Oi соединен с вторым входом второго элемента 2И, вторые входь первого и второго элемен00 тов 2И являются информационными входами о цифрового модулятора, информационными выходами которого являются выходы второго элемента 2И и второго элемента 2ИЛИ, выход первого элемента 2ИЛИ является синхронизирующим выходом цифрового модулятора, а на приемной .стороне введены блок управления приемом, первый и второй входы которого соединены соответственно с первым и вторым входами решаюи1его блока, третий вход которого подключен к первому вькоду блока упразпет я приемом, второй выход которого соединен с тактовым входом обратного пре

1

Изобретение относится к технике связи и может быть использовано для передачи информации.

Целью изобретения является повыщение скорости передачи.

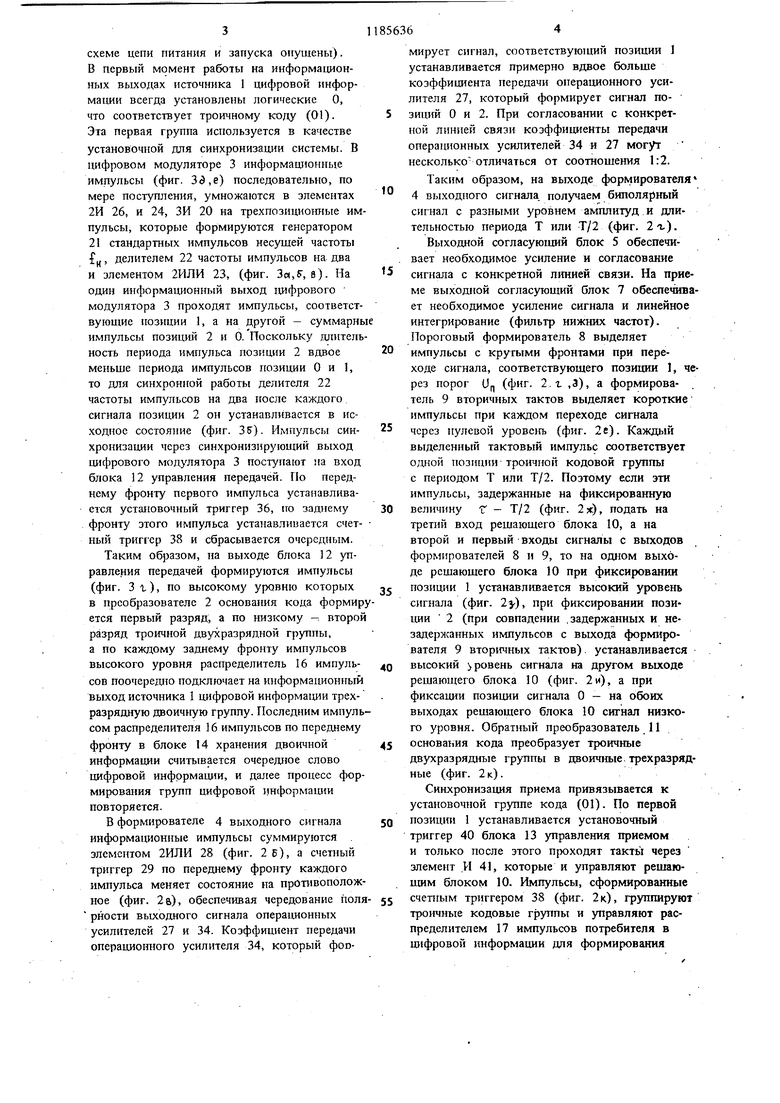

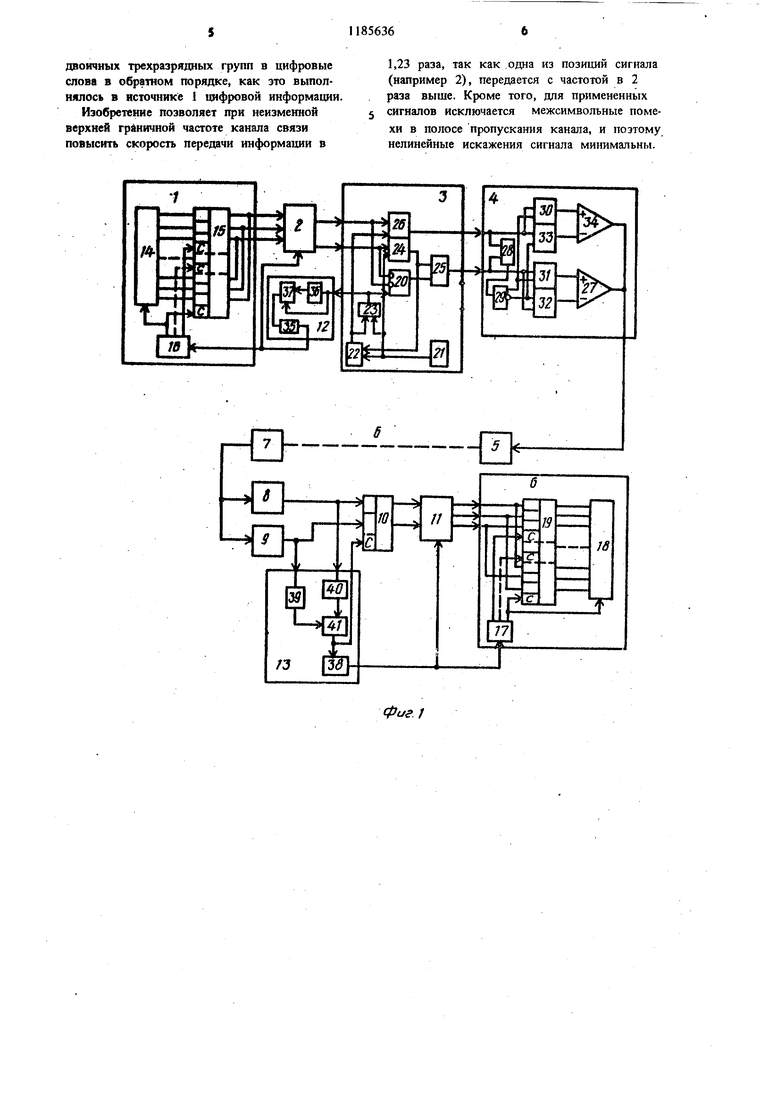

На фиг. 1 изображена структурная электрическая схема предлагаемой системы передачи; на фиг. 2 - временные диаграммы работы системы; на фиг. 3 - временные диаграммы работы цифрового модулятора.

Система передачи цифровой ш формации содержит ИСТОШ1ИК 1 цифровой информации, преобразователь 2 основания кода, цифровой модулятор 3, формирователь 4 выходного сигнала, выходной согласующий блок 5, потребитель 6 цифровой информации, входной согласующий блок 7, пороговый формирователь 8, формирователь 9 вторичных тактов, решающий блок 10, обратный преобразователь II основания кода, блок 12 управления передачей, блок 13 управления приемом.

Источник 1 цифровой информации содержит блок 14 хранения двоичной информации, формирователь 15 двоичных кодовых групп, распределитель 16 импульсов.

Потребитель 6 цифровой информации содерм ит распределитель 17 импульсов, блок 18 хранения двоичной цифровой информашш, формирователь 19 двоичных кодовых rpyim.

Цифровой модулятор 3 содержит элемент ЗИ 20, генератор 21 стандартных импульсов, делитель 22 частоты на два, первый элемент

2ИЛИ 23, первый элемент 2И 24, второй элемент 2ИЛИ 25, второй элемент 2И 26.

Формирователь 4 выходного сигнала содержит первый операционный усилитель 27, элемент 2ИЛИ 28, счетный триггер 29, первый элемент 2И 30, второй элемент 2И 31, третий элемент 2И 32, четвертый элемент 2И 33, второй операционный усилитель 34.

Блок 12 управления передачей содержит

счетный 35 и установочный 36 триггеры,

элемент И 37.

Блок 13 управления приемом содержит счетный триггер 38, элемеот задержки 39, установочный триггер 40, элемент И 41.

Система работает следующим образом. В источнике 1 цифровой информации преобразуются двоичные цифровые слова разрядностью N- Зп, где п- 1,2,..., ц -1 в двоичные трехразрядные группы (фиг. 2а),

а в преобразователе 2 основания кода они последовательно перекодируются в даухразрядные троичные группы таким образом, что наличие импульса на одном информационном выходе преобразователя 2 основания

кода соответствует троичной позиции 1, наличие импульса на другом информационном выходе - позиции 2, а отсутствие на обоих выходах им 1ульса - позиции 0. После подачи питания установочные 36 и 40

и счетные 35 и 38 триггеры и распределители 16 и 17 импульсов сбрасываются в нулевые состояния и запускается генератор 21 стандартных импульсов (на функциональной 3 схеме цепи питания и запуска опущены). В первый момент работы на информационных выходах источника 1 цифровой информации всегда установлены логические О, что соответствует троичному коду (01). Эта первая группа используется в качестве установочной для синхронизации системы. В цифровом модуляторе 3 информационные импульсы (фиг. ЗЭ,е) последовательно, по мере поступления, умножаются в элементах 2И 26, и 24, ЗИ 20 на трехпозиционные им пульсы, которые формируются генератором 21 стандартных импульсов несушей частоты f ц, делителем 22 частоты импульсов на два и элементом 2ИЛИ 23, (фиг. Зя,5, в). На один информационный выход дафрового модулятора 3 проходят импульсы, соответст вующие позиции 1, а на другой - суммарн импульсы позиций 2 и 0. Поскольку щ итель ность периода импульса позиции 2 вдвое меньше периода импульсов позиции О и 1, то для синхронной работы делителя 22 частоты импульсов на два после каждого сигнала позиции 2 он устанавливается в исходное состоя}1ие (фиг. 35). Импульсы синхронизации через синхронизирующий выход цифрового модулятора 3 поступают на вход блока 12 управления передачей. По переднему фронту первого импульса устанавливается установочный триггер 36, по заднему фронту этого импульса устанавливается счетный триггер 38 и сбрасывается очередным. Таким образом, на выходе блока 12 управления передачей формируются импульсы (фиг. 3 г), по высокому уровню которых в преобразователе 2 основания кода формир ется первый разряд, а по низкому - второ разряд троичной двухразрядной группы, а по каждому заднему фронту импульсов высокого уровня распределитель 16 импульсов поочередно подключает на информационный выход источника 1 цифровой информации трехразрящгую двоичную группу. Последним импуль сом распределителя 16 импульсов по переднему фронту в блоке 14 хранения двоичной информации считывается очередное слово цифровой информации, и далее процесс фор мирования групп цифровой янформашш повторяется. В формирователе 4 выходного сигнала информационные импульсы суммируются . элементом 2ИЛИ 28 (фиг. 2 5), а счетный триггер 29 по переднему фронту каждого импульса меняет состояние на противополож ное (фиг. 2б), обеспечивая чередование пол рности выходного сигнала операционных усилителей 27 и 34. Коэффициент передачи операционного усилителя 34, который фоо64мирует сигнал, соответствующий позиции 1 устанавливается примерно вдвое больше коэффициента передачи операционного усилителя 27, который формирует сигнал позиций О и 2. При согласовании с конкретной линией связи коэффициенты передачи операционных усилителей 34 и 27 могут несколько отличаться от соотношения 1:2. Таким образом, на выходе формирователя 4 выходного сигнала получаем биполярный сигнал с разными уровнем амплитуд и длительностью периода Т или Т/2 (фиг. 2i-). Выходной согласующий блок 5 обеспечивает необходимое усиление и согласование сигнала с конкретной линией связи. На приеме выходной согласующий блок 7 обеспечивает необходимое усиление сигнала и линейное интегрирование (фильтр нижних частот). Пороговый формирователь 8 выделяет импульсы с крутыми фронтами при переходе сигнала, соответствующего позиции I, через порог и (фиг. 2, г ,3), а формирователь 9 вторичных тактов выделяет короткие импульсы при каждом переходе сигнала через пулевой уровет (фиг. 2е). Каждый выделенный тактовый импульс соответствует одной позиции троичной кодовой группы с периодом т или Т/2. Поэтому если эти импульсы, задержанные на фиксированную величину i - 112 (фиг. 2х), подать на третий вход решающего блока 10, а на второй и первый входы сигналы с выходов формирователей 8 и 9, то на одном выходе рещаюшего блока 10 при фиксировании позиции 1 устанавливается высокий уровень сигнала (фиг. 2), при фиксировании позиции 2 (При совпадении .задержанных и незадерясанных импульсов с выхода формирователя 9 вторичных тактов). устанавливается высокий ; ровень сигнала на другом выходе решающего блока 10 (фиг. 2м), а при фиксации позиции сигнала О - на обоих выходах решающего блока 10 сигнал низкого уровня. Обратный преобразователь 11 основания кода преобразует троичные двухразрядные группы в двоичные трехразрядные (фиг. 2к). Синхронизация приема привязывается к установочной группе кода (01). По первой позицш 1 устанавливается установочный триггер 40 блока 13 управления приемом и только после этого проходят такть: через элемент И 41, которые и управляют решающим блоком 10. Импульсы, сформированные счетным триггером 38 (фиг. 2к), группируют троичные кодовые группы и управляют распределителем 17 импульсов потребителя в цифровой информации для формирования

двоичных трехразрядных групп в цифровые слова в обратном порядке, как это выпопиллось в источнике 1 цифровой информации.

Изобретение позволяет при неизменной верхней граничной частоте канала связи повысить скорость передачи информации в

1,23 раза, так как одна из позиций сигнала (например 2), передается с частотой в 2 раза выше. Кроме того, для примененных сигналов исключается межсимвопьные помехи в полосе пропускания канала, и поэтому нелинейные искажения сигнала ми1гамальны.

If О о Г, 7-П±Г7 7-г о о а

.atfi effMa/r т et yrjrar 7tf anna i ytaijnntn тглшпа.

cfit.atfoeffi tfynno Г Белова Л

.p -

n п

л.

JL

Л

n n

7Г

I 7 ; 7 I 011 I 100

п n п

n п

JL

П п

п П

Л

ГП

I ото

| Система передачи дискретной информации | 1976 |

|

SU688082A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Система передачи цифровой информациибииМпульСНыМ СигНАлОМ | 1976 |

|

SU815953A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-10-15—Публикация

1984-05-28—Подача