третьей группы входов третьего коммутатора, а вход знакового разряда третьей группы входов соединен с выходом знакового разряда блока оперативной памяти, входом знакового разряда накопительного сумматора и управляющим входом четвер того коммутатора, входы которого подключены к выходам блока ПОСТОЯ1Л1ЙЙ памяти, а выходы соединены с входами накопительного сумматора, управляющий вход которого

995

соединен с выходом рторого ключа, третий вход которого соединен с выходом служебного разряда блока оперативной памяти и первым входом третьего ключа, выход которого соединен с входом служебного разряда третьей группы входов третьего коммутатора, а второй вход - с выходом сигнала переполнения сумматора, вторая группа входов которого является входом второго слагаемого.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования частотно-манипулированного сигнала в многоканальных системах связи | 1984 |

|

SU1234992A1 |

| Нерекурсивный цифровой фильтр | 1983 |

|

SU1171994A1 |

| Цифровой нерекурсивный фильтр | 1987 |

|

SU1429294A1 |

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1270876A1 |

| Устройство для формирования частотно-манипулированного сигнала в многоканальных системах связи | 1986 |

|

SU1354434A1 |

| Нерекурсивный цифровой фильтр | 1986 |

|

SU1365349A2 |

| Цифровой нерекурсивный фильтр | 1988 |

|

SU1566472A1 |

| Цифровой нерекурсивный фильтр | 1974 |

|

SU516043A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

НЕРЕКУРСИВНЫЙ ЦИФРОВОЙ ФИЛЬТР, содержащий блок управления, первый управляюпщй выход которого соединен с входом служебного разряда буферного регистра, вход знаково- . го разряда которого является входом нерекурсивного цифрового фильтра, блок оперативной памяти, информационные выходы которого соединены с адресными входами блока постоянной памяти, и накопительный сумматор, выходы которого являются выходами нерекурсивного цифрового фильтра, отличающийся тем, что, с целью повышения быстродействия, в него введены формирователь импульсов, двоичный счетчик, регистр, первый, второй и третий ключи, первый, второй, третий и четвертый коммутаторы и сумматор, причем вход знакового разряда буферного регистра соединен с входом знакового разряда регистра и входом формирователя га пульсов, выход которого соединен с первыми информационными входами первого и второго коммутаторов, выходы которых соединены с входами сдвига буферного регистра и регистра соответственно, выходы информационных, знакового и служебного разрядов которых соединены соответственно с первой. и второй группами одноименных входов третьего коммутатора, первый управляющий вход которого соединен с управляющим входом первого коммутатора, первым управляющим входом второго коммутатора и входами служебных разрядов буферного регистра и регистра, входы информационных разрядов которых поразрядно объединены и подключены к выходам двоичного счетчика, счетный и установочный входы которого соединены соответственно с выходом первой тактовой частоты и выходом (Я сброса блока управления, второй управляющий выход которого соединен с. пepвы fl входами первого и второго ключей и вторым управляющим входом третьего коммутатора, третий управляющий вход которого соединен с вто|рым управляющим входом второго коммутатора и третьим управляющим выходом блока управления, выход второй тактовой частоты которого соединен с вторыми информационными входами первого и второго коммутаторов, вторым входом со второго ключа и вторым входом первоел го ключа, третий вход которого соединен с входом служебного разряда блока оперативной памяти и выходом служебного разряда, третьего коммутатора, а выход - с входом сдвига блока оперативной памяти, вход знакового разряда которого соединен с соответствующим выходом третьего коммутатора, выходы информационных разрядов которого через последовательно соединенные блок оперативной памяти и сумматор подключены к одноимен1П)1м входам

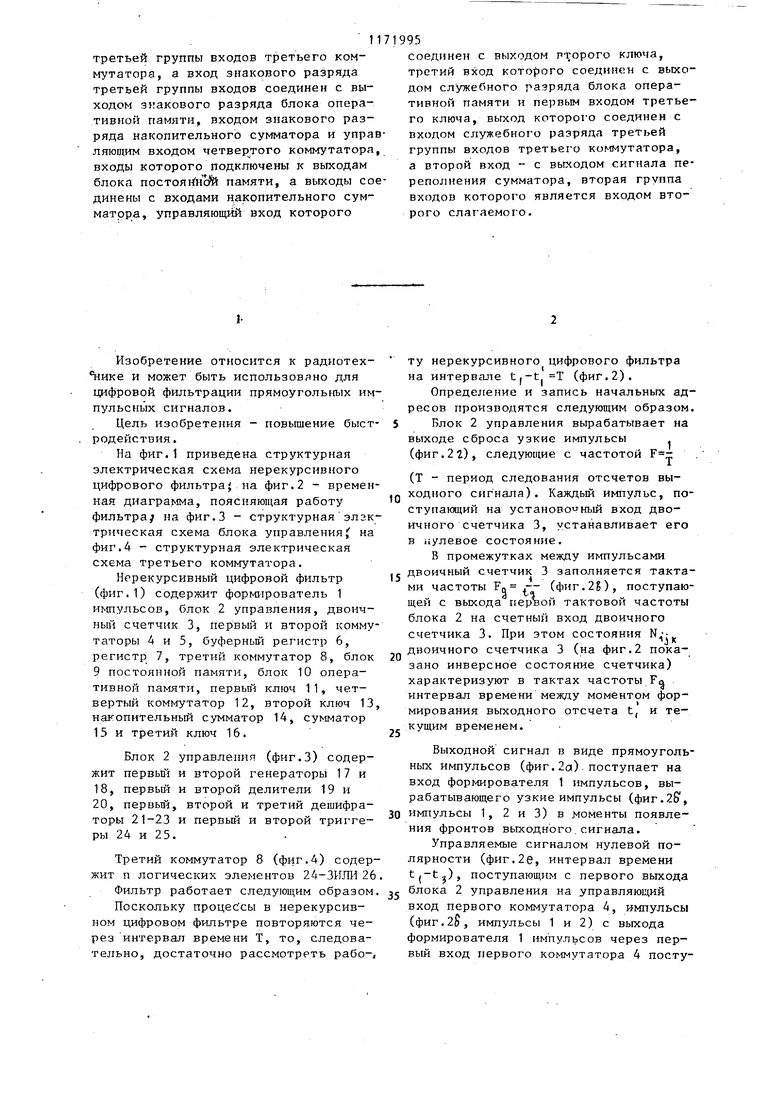

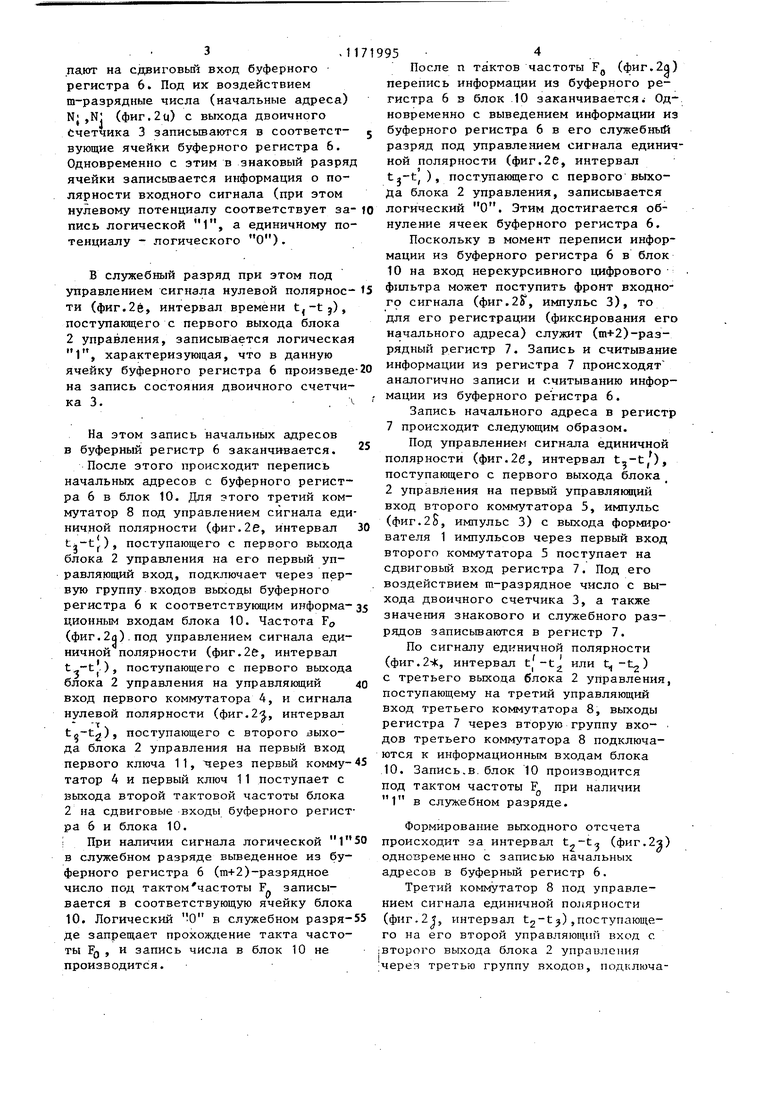

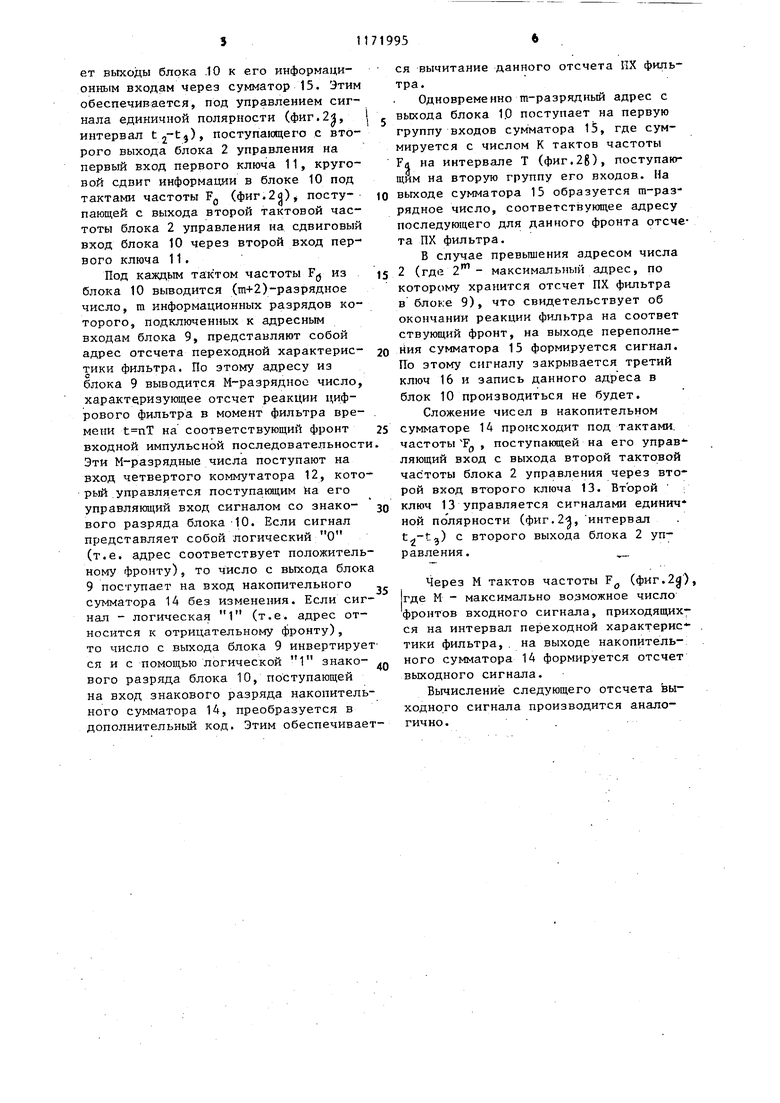

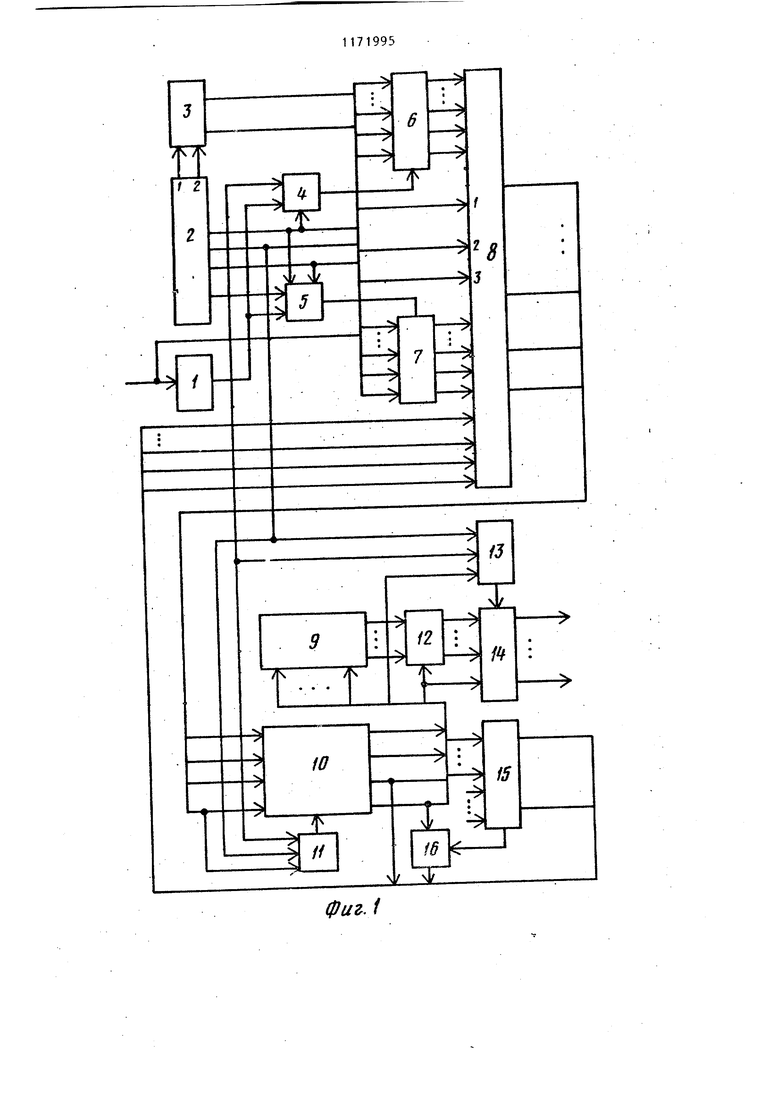

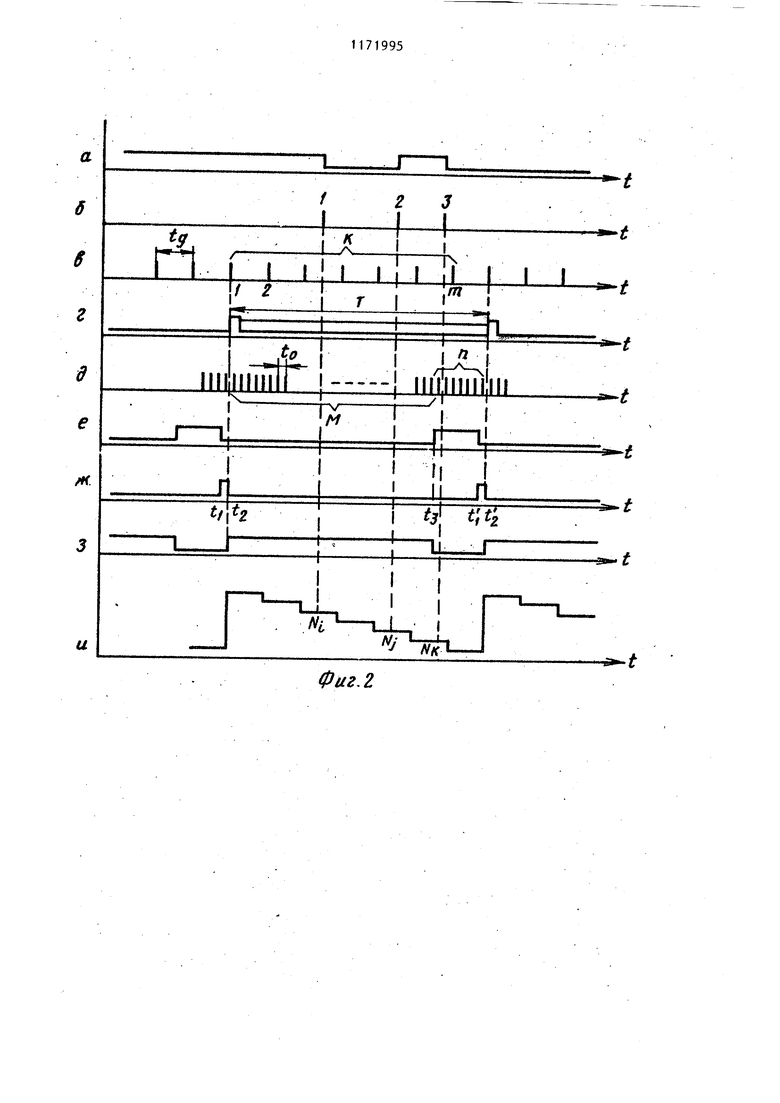

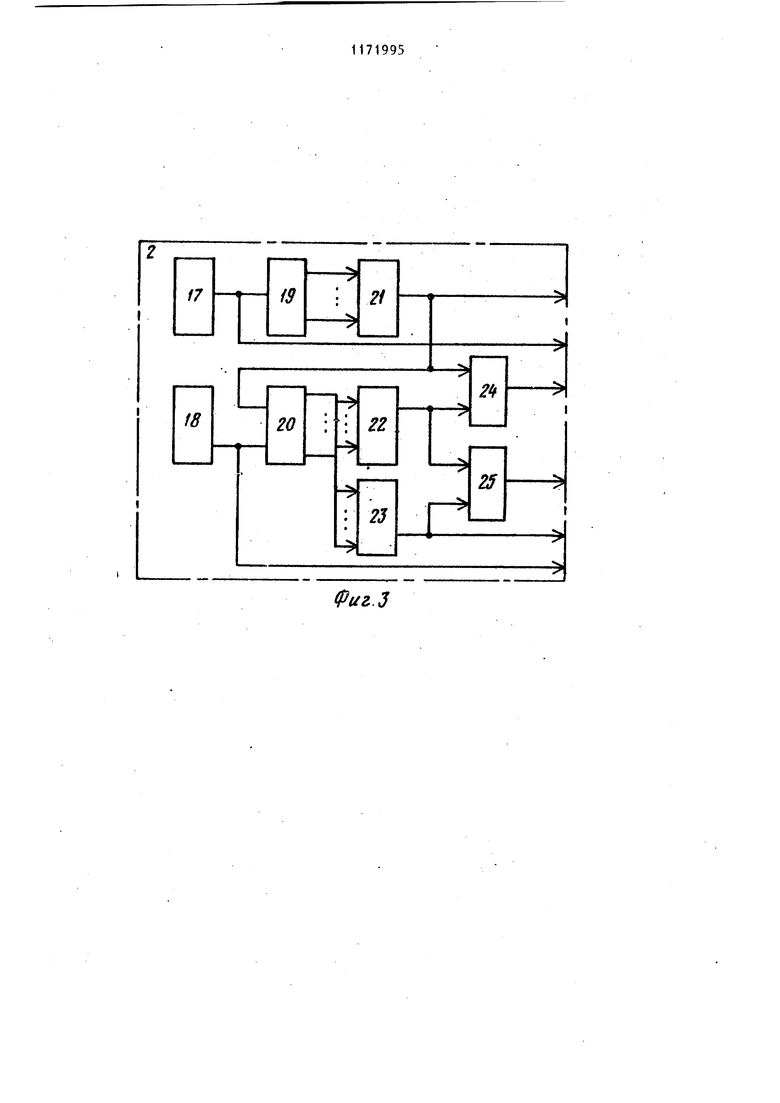

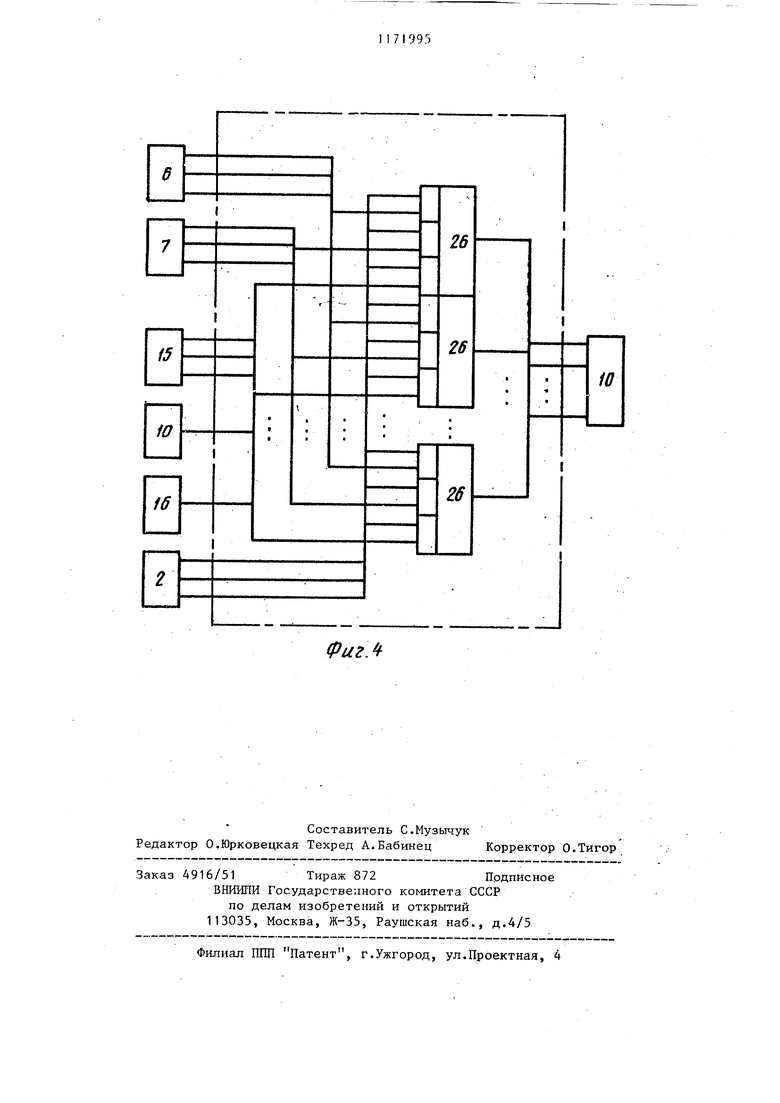

Изобретение относится к радиотех тнике и может быть использовано для цифровой фильтрации прямоугольных им пульсных сигналов. Цель изобретения - повышение быст родействия. На фиг.1 приведена структурная электрическая схема нерекурсивного цифрового фильтра} на фиг.2 - времен ная диаграмма, поясняющая работу фильтра; на фиг.З - структурная элзк трическая схема блока управленияJ на фиг.4 - структурная электрическая схема третьего коммутатора. Нерекурсивный цифровой фильтр (фиг.1) содержит формз-фователь 1 и тульсов, блок 2 управления, двоичHboi счетчик 3, первый и второй комму таторы 4 и 5, буферный регистр 6, регистр 7, третий коммутатор 8, блок 9 постоянной памяти, блок 10 оперативной памяти, первьй клгоч 11, четвертый коммутатор 12, второй ключ 13 накопительный сумматор 14, сумматор 15 и третий ключ 16. Блок 2 управления (фиг.З) содержит первьй и второй генераторы 17 и 18, первый и второй делители 19 и 20, первьй, второй и третий дешифраторы 21-23 и первый и второй триггеры 24 и 25. Третий коммутатор 8 (фиг.4) содер жит п логических элементов 24-ЗИЛИ 26 Фильтр работает следующим образом Поскольку процессы в нерекурсивном цифровом фильтре повторяются через интервал времени Т, то, следовательно, достаточно рассмотреть рабо- ту нерекурсивного цифрового фильтра на интервале tj-t Т (фиг.2). Определение и запись начальных адресов производятся следующим образом. Блок 2 управления вырабатывает на выходе сброса узкие импульсы . (фиг.22), следующие с частотой (Т - период следования отсчетов выходного сигнала). Каждьй импульс, поступающий на установочный вход двоичного счетчика 3, устанавливает его в нулевое состояние. В промежутках между импульсами двоичный счетчик 3 заполняется тактами частоты FQ 4- (фиг.2), поступающей с выхода первой тактовой частоты блока 2 на счетный вход двоичного счетчика 3. При этом состояния Ы -двоичного счетчика 3 (на фиг.2 показано инверсное состояние счетчика) характеризуют в тактах частоты Fn интервал времени между моментом формирования выходного отсчета t, и текущим временем. Выходной сигнал в виде прямоугольных импульсов (фиг.2а) поступает на вход формирователя 1 импульсов, вырабатывающего узкие импульсы (фиг.28, импульсы 1, 2 и 3) в хоменты появления фронтов выходного.сигнала. Управляемые сигналом нулевой полярности (фиг.2е, интервал времени tj-tj), поступающим с первого выхода блока 2 управления на управляющий вход первого коммутатора 4, импульсы (фиг.2о, импульсы 1 и 2) с выхода формирователя 1 импульсов через первый вход первого коммутатора 4 посту 3,1

пяют на сдвиговьй вход буферного регистра 6. Под их воздействием т-разрядные числа (начальные адреса) N;,N (фиг.2ц) с выхода двоичного Счетчика 3 записьтаются в соответствующие ячейки буферного регистра 6. Одновременно с этим в знаковый разряд ячейки записывается информация о полярности входного сигнала (при этом нулевому потенциалу соответствует запись логической 1, а единичному потенциалу - логического О).

В служебный разряд при этом под управлением сигнала нулевой полярноети (фиг.2ё, интервал времени t,-tj), поступающего с первого выхода блока 2 управления, записывается логическая 1, характеризующая, что в данную ячейку буферного регистра 6 произведе на запись состояния двоичного счетчика 3..ЛНа этом запись начальных адресов в буферный регистр 6 заканчивается.

После этого происходит перепись начальных адресов с буферного регистра 6 в блок 10. Для этого третий коммутатор 8 под управлением сигнала единичной полярности (фиг.2е, интервал tg-tp, поступающего с первого выхода блока 2 управления на его первый управляющий вход, подключает через первую группу входов выходы буферного регистра 6 к соответствующим информационным входам блока 10. Частота FC, (фиг.2а).под управлением сигнала единичной полярности (фиг.2&, интервал .), поступающего с первого выхода блока 2 управления на управляющий вход первого коммутатора 4, и сигнала нулевой полярности (фиг.2, интервал

tg-t), поступающего с второго выхода блока 2 управления на первый вход первого ключа 1 1, через первый коммутатор 4 и первый ключ 11 поступает с выхода второй тактовой частоты блока 2 на сдвиговые входы буферного регистра 6 и блока 10.

При наличии сигнала логической 1 в служебном разряде выведенное из буферного регистра 6 (т+2)-разрядное число под тактомчастоты F. записывается в соответствующую ячейку блока 10. Логический О в служебном разряде запрещает прохождение такта частоты Fg , и запись числа в блок 10 не производится.

995 4.

После и тактов частоты F (фиг.2а перепись информации из буферного регистра 6 в блок .10 заканчивается.- Одновременно с выведением информации и буферного регистра 6 в его служебный разряд под управлением сигнала едининой полярности (фиг.2е, интервал tf-t,}, поступающего с первого выхода блока 2 управления, записывается логический О. Этим достигается обнуление ячеек буферного регистра 6.

Поскольку в момент переписи информации из буферного регистра 6 в блок 10 на вход нерекурсивного цифрового флпьтра может поступить фронт входно го сигнала (фиг.28, импульс 3), то для его регистрации (фиксирования ег начального адреса) служит (т+2)-разрядный регистр 7. Запись и считывани информации из регистра 7 происходят аналогично записи и считыванию информации из буферного регистра 6.

Запись начального адреса в регистр 7 происходит следующим образом.

Под управлением сигнала единичной полярности (фиг.2е, интервал ,), поступающего с первого выхода блока 2 управления на первый управлякиций вход второго коммутатора 5, импульс (фиг.25, импульс 3) с выхода формирователя 1 импульсов через первый вход второго коммутатора 5 поступает на сдвиговый вход регистра 7. Под его воздействием га-разрядное число с выхода двоичного счетчика 3, а также значения знакового и служебного разрядов записьтаются в регистр 7.

По сигналу единичной полярности (фиг., интервал t-t или t ) с третьего выхода блока 2 управления, поступающему на третий управляющий вход третьего коммутатора 8, выходы регистра 7 через вторую группу входов третьего коммутатора 8 подключаются к информационным входам блока 10. Запись.в.блок 10 производится под тактом частоты F при наличии 1 в служебном разряде.

Формирование выходного отсчета происходит за интервал (фиг.2-3) одновременно с записью начальных адресов в буферный регистр 6.

Третий коммутатор 8 под управлением сигнала единичной полярности (фиг.2, интервал tg-t),поступающего на его второй управляющий вход с iBTOporo выхода блока 2 управления черея третью группу входов, подключает выходы блока .10 к его информационным входам через сумматор 15. Этим обеспечивается, под управлением сигнала единичной полярности (фиг.21, интервал tj-tj), поступающего с второго выхода блока 2 управления на первый вход первого ключа 11, круговой сдвиг информации в блоке 10 под тактами частоты (фиг.2ч) поступающей с выхода второй тактовой частоты блока 2 управления на сдвиговый вход блока 10 через второй вход первого ключа 11.

Под каждым тактом частоты F из блока 10 выводится {т+2)-разрядное число, m информационных разрядов которого, подключенных к адресным входам блока 9, представляют собой адрес отсчета переходной характеристики фильтра. По этому адресу из

О -.

блока 9 выводится М-разряднос число, характеризующее отсчет реакции цифрового фильтра в момент фильтра времеии на соответствующий фронт входной импульсной последовательности Эти М-разрядные числа поступают на вход четвертого коммутатора 12, который управляется поступаилдим На его управляющий вход сигналом со знакового разряда блока -10. Если сигнал представляет собой логический О (т.е. адрес соответствует положительному фронту), то число с выхода блока 9 поступает на вход накопительного сумматора 14 без изменения. Если сигнал - логическая 1 (т.е. адрес относится к отрицательному фронту), то число с выхода блока 9 инвертирует ся и с помощью логической 1 знакового разряда блока 10, поступающей на вход знакового разряда накопительного сумматора 14, преобразуется в дополнительный код. Этим обеспечивается вычитание данного отсчета ИХ фильтра.

Одновременно т-разрядный адрес с выхода блока 10 поступает на первую группу входов сумматора 15, где суммируется с числом К тактов частоты Frt на интервале Т (фиг.28), поступанг щим на вторую группу его входов. На выходе сумматора 15 образуется га-разрядное число, соответствующее адресу последующего для данного фронта отсчета ИХ фильтра.

В случае превьпиения адресом числа 2 (где 2 - максимальный адрес, по которому хранится отсчет ПХ фильтра в блоке 9), что свидетельствует об окончании реакции фильтра на соответ ствующий фронт, на выходе переполнейия сумматора 15 формируется сигнал. По зтому сигналу закрывается третий ключ 16 и запись данного адреса в блок 10 производиться не будет.

Сложение чисел в накопительном сумматоре 14 происходит под тактами, частоты Tjj , поступакяцей на его управ ляющий вход с выхода второй тактовой частоты блока 2 управления через второй вход второго ключа 13. Второй ключ 13 управляется сигналами единич ной полярности (фиг,2, интервал ) с второго выхода блока 2 управления.

Через М тактов частоты F (фиг.2) где М - максимально возможное число фронтов входного сигнала, приходящихся на интервал переходной характерис тики фильтра,. на выходе накопительного сумматора 14 формируется отсчет вькодного сигнала.

Вычисление следующего отсчета выходного сигнала производится аналогично.

7W4

i

/

W

//

(ij/г. /

f

Ч

3

Т

-

f3

12

/«

-

-

/5

7

I

/

Фи.З

15

16

Фаг Л

26

26

| Рабинер Л., Гоулд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| М., Мир, 1978, с | |||

| Способ получения раствора нитродиазобензола и применения его в крашении | 1921 |

|

SU598A1 |

| Нерекурсивный цифровой фильтр нижних частот | 1977 |

|

SU669476A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-07—Публикация

1984-02-09—Подача