Изобретение относится к электросвязи и.может быть использовацо в системах передачи данных.

Цель изобретения - повышение быстродействия и точности формирования.

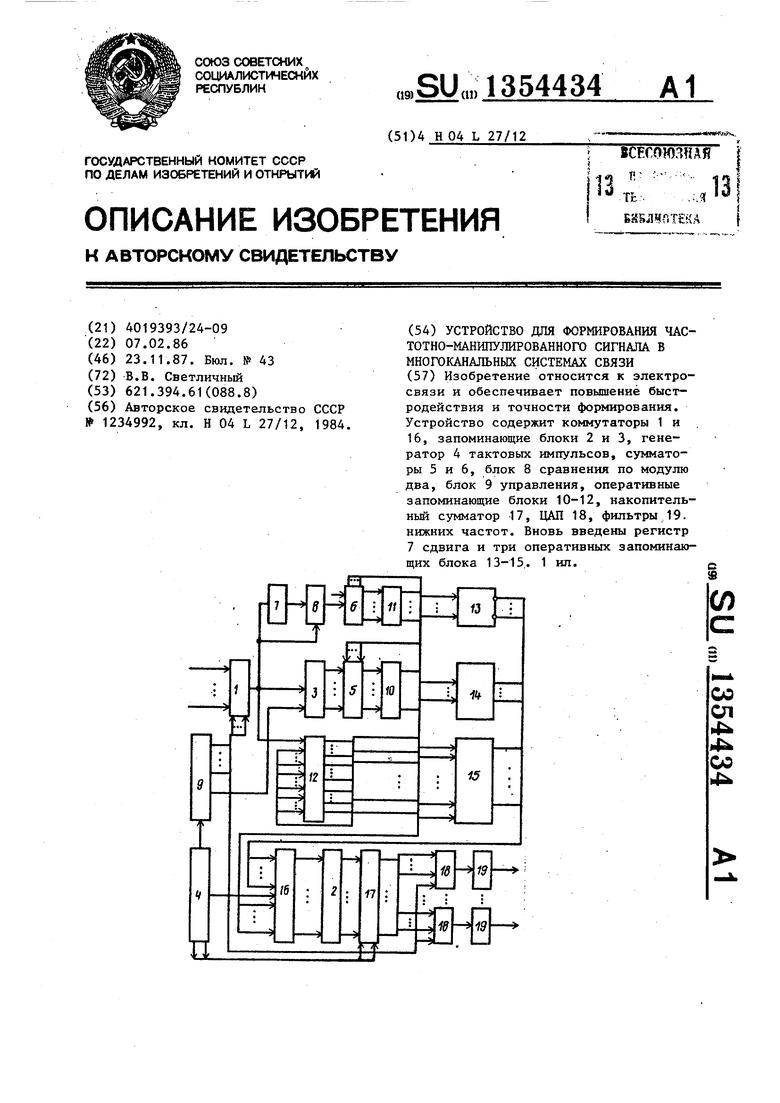

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство для формирования час- тотно-манипулированного сигнала в многоканальных системах связи содержит первый коммутатор 1, первый 2 и второй 3 постоянные запоминающие блоки, генератор 4 тактовых импуль- сов, первый 5 и второй 6 сумматоры, регистр 7 сдвига, блок 8 сравнения по модулю два, блок 9 управления, первый 10, второй 11, третий 12, четвертый 13, пятый 14 и шестой 15 оперативные запоминающие блоки, второй коммутатор 16, накопительный сумматор 17, цифроаналоговые преобразователи (ЦАП) 18, фильтры 19 нижних частот.

Устройство работает следующим образом.

Двоичные сигналы от N источников информации (не показаны) поступают на соответствующие информационные входы первого коммутатора 1.

Тактовые импульсы с первого выхода генератора 4 тактовых импульсов, имеющие частоту F, поступают на вхо блока 9 управления, имекнцего столько адресов, сколько каналов обслуживается устройством. Позтому каждый из источников информации опрашивается с частотой ,, где N - число обслуживаемых каналов связи, Т - ин- тервал между отсчетами выходного ЧМ сигнала с ограниченным спектром.

В течение времени л тг- выборка

0

двоичного сигнала, от первых входов блока 9 управления поступающих на .-. (адресные) управляющие входы первого коммутатора 1, поступает на первый вход постоянного запоминающего бло- ка (ПЗБ) 3 на второй вход которого, синхронно с выборкой, поступает информация о скорости передачи в данном направлении с второго выхода блока 9 управления. С выходов ПЗБ 3 . : сформированное под воздействием управляющих сигналов га-разрядное число, характеризующее приращение ЧМ сигнала за интервал Т, поступает на пер

Q s 0 5

о

Q

5

5

g

вые входы слагаемого первого, сумматора 5. . i

Одновременно с выхода оперативного запоминающего блока (ОЗБ) 10 на вторые входы второго слагаемого сумматора 5 поступает т-разрядное число, характеризующее фазу ЧМ сигнала в пре- дьщущий отсчет в этом же направлении. В сумматоре 5 происходит суммирование т-разрядных чисел первого и второго слагаемых, полученная т-разрядная сумма, характеризующая текущую фазу ЧМ сигнала, поступает на входы ОЗБ 10 для записи.

Выборки двоичного сигнала с выхода первого коммутатора 1 поступают также на вход регистра 7 сдвига для записи . и на второй вход блока 8 сравнения по модулю два, на первый вход которого с выхода регистра 7 сдвига поступает выборка двоичного сигнала, соответствующая предыдущему отсчёту двоичного сигнала этого же направления.

В случае различия полярностей (на- личие изменения полярности посылки) на выходе блока 8 сравнф1ия по модулю два формируется сигнал, устанавливающий по первому входу сумматор 6 в нулевое, состояние.

Сумматор 6 и ОЗБ 11 образуют N двоичных делителей с коэффициентом деления 2, работа которых идентична. Состояние Ni-ro делителя, характеризующее зону текущей двоичной посьш- ки, выводится из ОЗБ 11 и поступает на вторые входы первого слагаемого сумматора 6, на третий вход второго слагаемого которого подается 1. Сумматор 6 суммирует эти числа и результат с его выхода записывается в ОЗБ 11.

Выборки двоичного сигнала с выхода первого коммутатора 1 поступают на управляющий вход ОЗБ 1.2. Запись и продвижение выборок осуществляется с, частотой FO, поступающей на сдвиговый вход ОЗБ 12. Каждый i-й выход ОЗБ 12 соединен с (1+1)-м входом, чем обеспечивается продвижение выборки двоичного сигнала по ОЗБ 12.

После N тактов частоты записанная по управляющему входу выборка появляется на первом выходе ОЗБ 12. ; После этого она поступает на второй вход ОЗБ 12 для записи и т.д. Записанная по первому входу выборка появляется на последнем (р-1) выходе ОЗБ 12 через N(P-1) М тактов

частоты Fj, . Таким образом, в каждый момент времени на выходах ОЗБ 12 появляются РМ выборок двоичных сигнало информации, относящихся к одному направлению.

N выходов ОЗБ 11, n+m выходов ОЗБ 10, а также 1,...,(М+1)-й, ..., (2М+1)-й, ..., С() выходы ОЗБ 12 подключены к соответствующим входам ОЗБ 13-15, а также к соответствующим входам второго коммутатора 16.

В ОЗБ 13 и 15 происходит задерж- ка чисел ОЗБ 11 и 12 на тактов частоты FJJ . В ОЗБ 14 происходит задержка чисел с выхода первого ОЗБ 10 на 21pN тактов частоты F.

Выходы ОЗБ 13-15 подключены к

.соответствующим входам второго комму- 20 блока, входы которого подключены татора 16.

Второй коммутатор 16 под воздейстк выходам второго коммутатора, такто вьй вход которого подключен к втором выходу генератора тактовых импульсов выход первого коммутатора соединен с первым входом второго постоянного за поминающего блока, выходы которого соединены с первыми входами первого сумматора, выходы которого соединены с входами первого оперативного запо30 минающего блока, выходы которого соединены с вторыми входами первого сумматора, блок сравнения по модулю два, второй сумматор, выходы которого соединены с входами второго опера тивного запоминающего блока, третий оперативный запоминающий блок, при этом второй выход блока управления подключен к второму входу второго постоянного запоминающего блока, а

вием частоты Fg, поступающей на его тактовый вход с второго выхода генератора 4 тактовых импульсов, первые полпериода частоты Fg подключает к соответствующим адресным входам второго ПЗБ 2 выходы первого ОЗБ 10-12, а вторые полпериода - выходы ОЗБ 13-1 Под воздействием сигналов, nocTynaio- щих на (адресные) входы ПЗБ 2, на его выходах формируются т-разрядные числа, характеризующие реакцию фильтра на ЧМ сигнал соответствующей формы, которые затем суммируются накопи- тельньм сумматором 17 под воздействием управляющих сигналов, поступающих на его тактовые счетный и установочный входы с третьего и четвертого выходов генератора 4 тактовых импульсов, . выходы цифроаналоговых преобразовате-

Сформированные на выходе накопи- лей подключены к входам соответствую-

тельного сумматора 17 отсчет ЧМ сиг- щих фильтров нижних частот, о т л инала с ограниченным спектром в виде т-разрядного числа поступает на информационные входы всех ЦАП 18.

Под воздействием сигнала с.соответствующего (адресного) выхода блока 9 управления, поступающего на (адресный) вход одного из ЦАП 18, т-раз- рядная сумма, присутствующая на его входе, преобразуется им в аналоговый сигнал, который поступает на вход соответствующего фильтра 19 нижних частот для ограничения высокочастотных составляющих. Выходы фильтра 19 нижних частот являются в.ыходами устройства.

Вычисление отсчета выходного ЧМ сигнала для следующего направления

1 производится аналона интервале гичным образом.

Формула изобретения

Устройство для формирования час- тотно-манипулированного сигнала в многоканальных системах связи, содержащее генератор тактовьас импульсов, первый выход которого соединен с входом блока управления, первые выходы которого подключены к управляющим входам первого коммутатора и дифроаналоговых преобразователей, сигнальные входы которых подключены к выходам накопительного сумматора, сигнальные входы которого подк.гаочены к выходам первого постоянного запоминающе-

блока, входы которого подключены

к выходам второго коммутатора, такто- вьй вход которого подключен к второму выходу генератора тактовых импульсов, выход первого коммутатора соединен с первым входом второго постоянного запоминающего блока, выходы которого соединены с первыми входами первого сумматора, выходы которого соединены с входами первого оперативного запо; минающего блока, выходы которого соединены с вторыми входами первого сумматора, блок сравнения по модулю два, второй сумматор, выходы которого соединены с входами второго оперативного запоминающего блока, третий оперативный запоминающий блок, при этом второй выход блока управления подключен к второму входу второго постоянного запоминающего блока, а

чающееся тем, что, с целью повышения быстродействия и точности формирования, введены четвертый, пятый и шестой оперативные запоминающие блоки и регистр сдвига, выход которого соединен с первым входом блока сравнения по модулю два, выход которого соединен с первым входом второго сумматора, вторые входы которого подключены к выходам второго оперативного запоминающего блока, к входам четвертого оперативного запоминающего блока и к первым сигнальным входам второго коммутатора, вторые сигнальные входы которого подключены к выходам первого оператив-: ного запоминающего блока и входам

б13544346 .

пятого оперативного запоминающего ход первого коммутатора соединен с .блока, .выходы которого соединены . входом регистра сдвига, с :втррым вхо- с третьими сигнальными входами дом блока сравнения по-модулю два и второго коммутатора, четвертые - управляющим входом тре тьего запоминаю- сигнальные входы которого под- щего блока, сигнальные входы которо- ключены к выходам третьего оперативно- го подключены к соответствукнцим вхо- го запоминающего блока и входам шесто- дам шестого оперативного запоминаю- го оперативного запоминакицего блока, щего блока, при этом третий и 1ётвер- выходы которого с:оединены с пятыми Q тый выходы генератора тактовых им- сигнйльными входами второго коммута- . пульсов подключены к соответствзпяцим тора, шестые сигнальные входы которо- тактовым входам накопительного сумма- го подключены к выходам четвертого тора, а третий вход второго суммато- оперативного запоминающего блока, вы- ра является опорным входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования частотно-манипулированного сигнала в многоканальных системах связи | 1984 |

|

SU1234992A1 |

| Устройство асинхронного приема импульсных сигналов | 1988 |

|

SU1684930A1 |

| Устройство поиска шумоподобного сигнала | 1988 |

|

SU1540020A1 |

| Устройство для обмена информацией между микро ЭВМ и периферийными устройствами | 1983 |

|

SU1195351A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1992 |

|

RU2012014C1 |

| Система передачи сообщений | 1986 |

|

SU1356268A1 |

| Устройство для формирования частотно-манипулированного сигнала | 1980 |

|

SU919147A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Цифровой измеритель задержки | 1981 |

|

SU951228A1 |

Изобретение относится к электросвязи и обеспечивает повьшениё быстродействия и точности формирования. Устройство содержит коммутаторы 1 и 16, запоминающие блоки 2 и 3, генератор 4 тактовых импульсов, сумматоры 5 и 6, блок 8 сравнения по модулю два, блок 9 управления, оперативные запоминающие блоки 10-12, накопительный сумматор 17, ЦАП 18, фильтры 19. нижних частот. Вновь введены регистр 7 сдвига и три оперативных запоминающих блока 13-15.. 1 ил. (Л ел .4 4 СО иС

| Устройство для формирования частотно-манипулированного сигнала в многоканальных системах связи | 1984 |

|

SU1234992A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-11-23—Публикация

1986-02-07—Подача