16

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

| Рекурсивный цифровой фильтр | 1989 |

|

SU1658376A1 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| Цифровой фильтр | 1987 |

|

SU1474676A1 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1332519A1 |

| Нерекурсивный цифровой фильтр | 1984 |

|

SU1171995A1 |

| Устройство для определения характеристик случайного процесса | 1983 |

|

SU1100628A1 |

| Цифровой нерекурсивный фильтр | 1983 |

|

SU1124430A1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| Устройство для транспортирования спектров,начинающихся от нуля | 1984 |

|

SU1205250A1 |

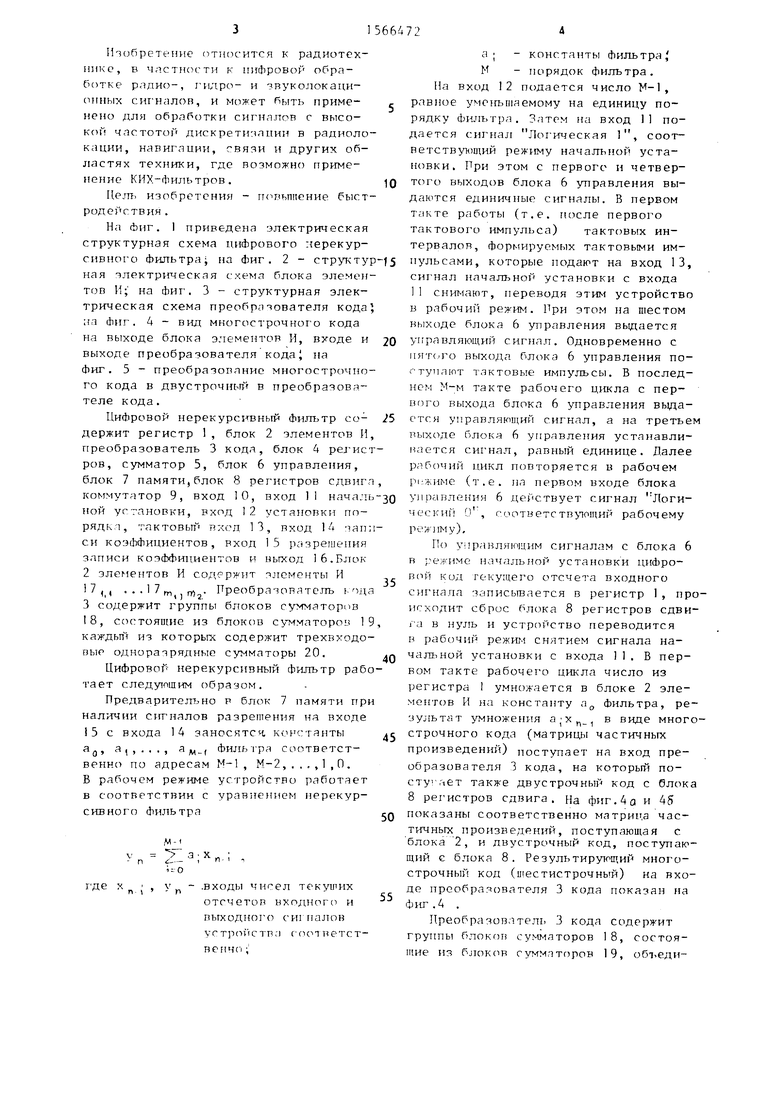

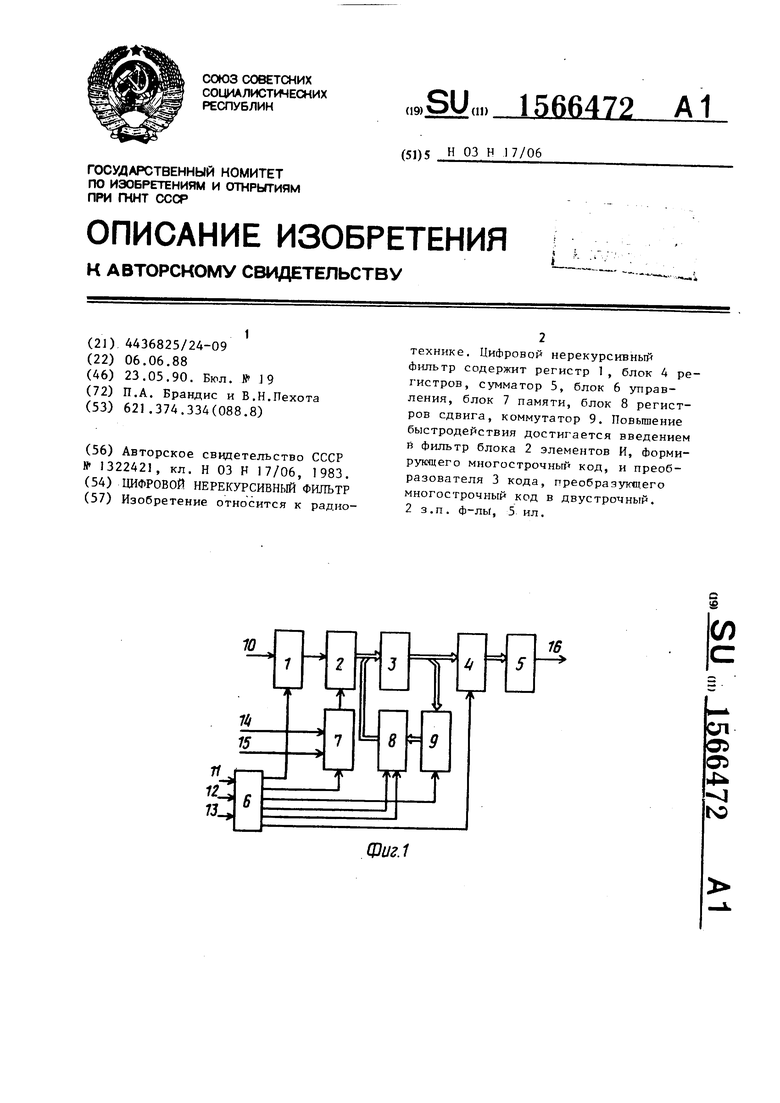

Изобретение относится к радиотехнике. Цифровой нерекурсивный фильтр содержит регистр 1, блок 4 регистров, сумматор 5, блок 6 управления, блок 7 памяти, блок 8 регистров сдвига, коммутатор 9. Повышение быстродействия достигается введением в фильтр блока 2 элементов И, формирующего многострочный код, и преобразователя 3 кода, преобразующего многострочный код в двустрочный. 2 з.п. ф-лы, 3 ил.

ел

О5

о

4 N3

Фиг.1

Изобретение относится к радиотехнике, в частности к цифровой обработке радио-, гидро- и звуколокационных сигналов, и может быть приме- нено для обработки сигналов с высокой частотой дискретизации в радиолокации, навигации, связи и других областях техники, где возможно применение КИУ-фильтров.

Цель изобретения - повышение быстродействия .

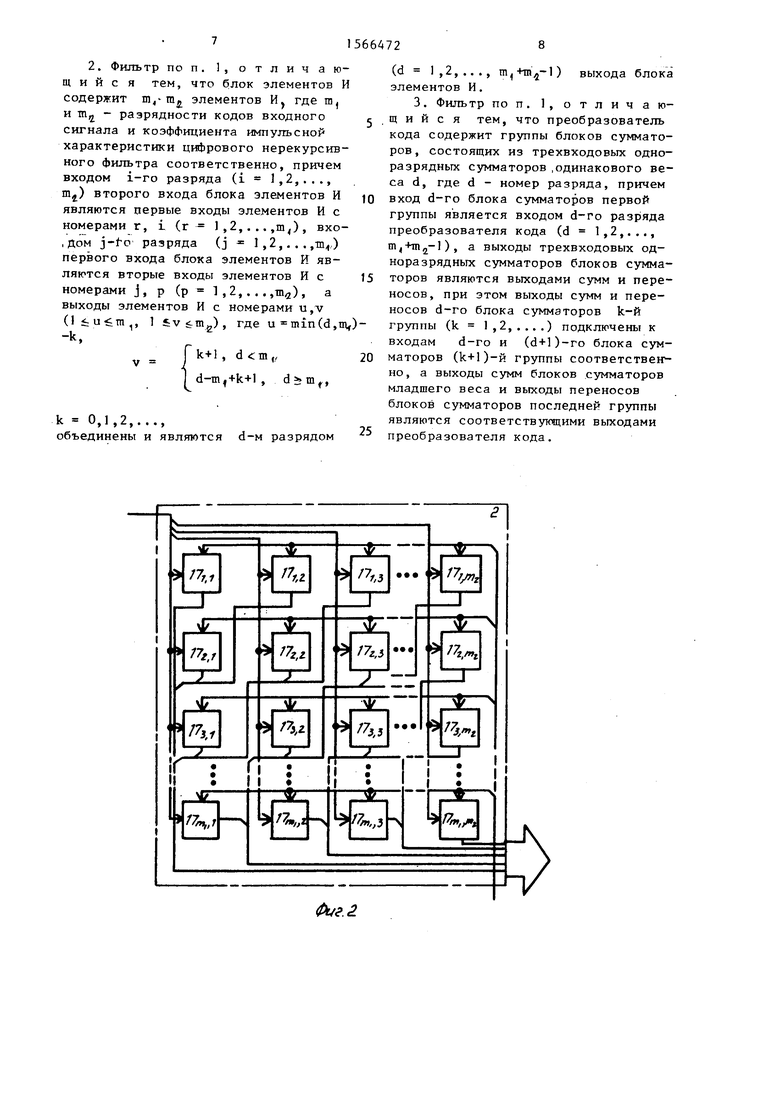

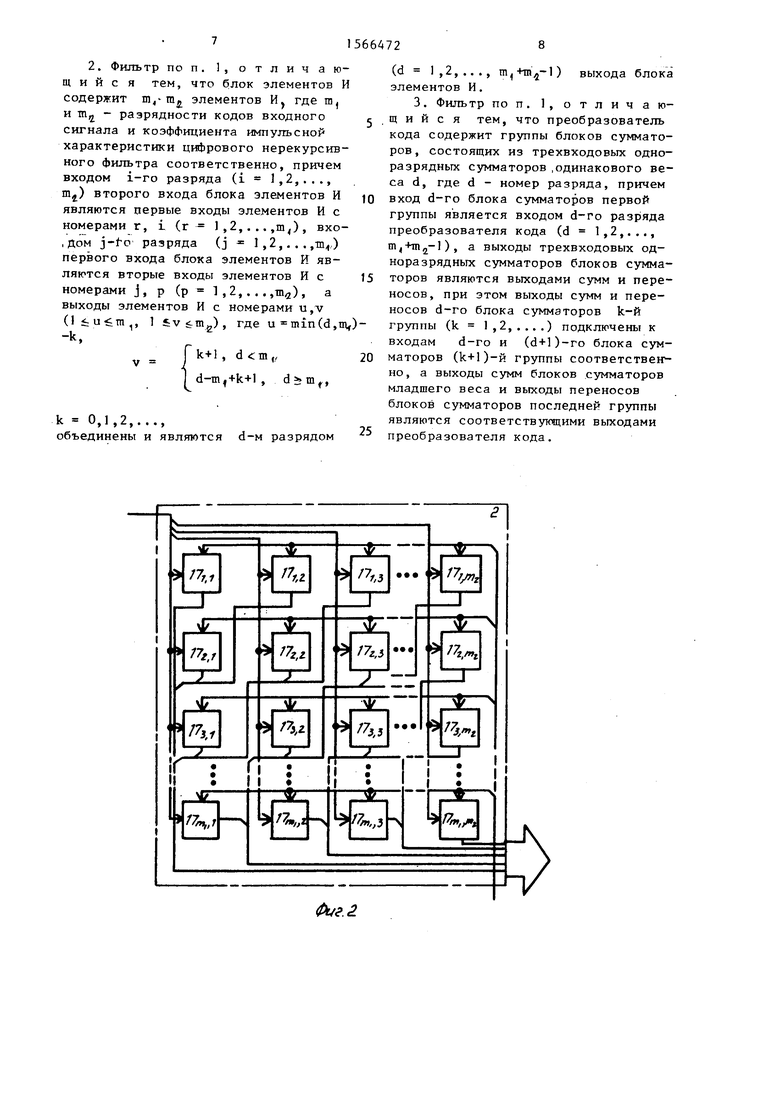

На Фиг. I приведена электрическая структурная схема цифрового нерекурсивного фильтра; на фиг. 2 - структур ная электрическая схема блока элементов И; на фиг. 3 - структурная электрическая схема преобразователя кода} :гз Фиг. 4 - вид многострочного кода на выходе блока элементов И, входе и выходе преобразователя кода на Фиг. 5 - преобразование многострочного кода в двустрочньтй в преобразователе кода.

Цифровой нерекурсивный фильтр со- держит регистр 1, блок 2 элементов И, преобразователь 3 кода, блок 4 регистров, сумматор 5, блок 6 управления, блок 7 памяти,блок 8 регистров сдвип коммутатор 9, вход 10, вход 1 1 началь ной установки, вход 12 установки по - рядкт, тактовый РХОЛ 13, вход 14 -ian;i си коэффициентов, вход 15 разрешения записи коэффициентов и выход 16.Блок

2элементов И содержит элементы И 17,, . . . 1 7 m т , Преобразорателъ i ода

3содержит группы блоков сумматоров 8, состоящие из блоков сумматоров 19 каждый из которых содержит трехвходо- вые одноразрядные сумматоры 20.

Цифровой нерекурсивный фильтр работает следующим образом.

Предварительно я блок 7 памяти при наличии сигналов разрешения на входе 15 с входа 14 заносятся кон -танты а0, а,,..., ям, Филь1ра соответственно по адресам М-1, М-2,,.,,1,0. В рабочем режиме устройство работает в соответствии с уравнением нерекурсивного Фильтра

Ml Уп ; ,

xn , у - .входы чисел текуших отсчетов входного и выходного CHI палов устройства соответст- венчо;

с

5 0

5 о

п

5

0

5

а; - константы Фильтра, М - порядок фильтра.

На вход 12 подается число М-1, равное уменьшаемому на единицу порядку фильтра. Затем на вход 11 подается сигнал Логическая 1, соответствующий режиму начальной установки. При этом с первого и четвертого выходов блока 6 управления выдаются единичные сигналы. В первом такте работы (т.е. после первого тактового импульса) тактовых интервалов, формируемых тактовыми импульсами, которые подают на вход 13, сигнал начальной установки с входа 11 снимают, переводя этим устройство в рабочий режим. При этом на шестом выходе блока 6 управления выдается управляющий сигнал. Одновременно с пятого выхода блока 6 управления по- - туплют тактовые импульсы. В последнем М-м такте рабочего цикла с первого выхода блока 6 управления выдается управляющий сигнал, а на третьем выходе блока 6 управления устанавливается сигнал, равный единице. Далее рабочий цикл повторяется в рабочем pi жиме (т.е. на первом входе блока управления 6 действует сигнал Логи- ч ее кий fi , соответствующий рабочему ре/ьпму).

По управляющим сигналам с блока 6 в режиме начальной установки цифровой код текущего отсчета входного еигнапа записывается в регистр 1, происходит сброс блока 8 регистров сдви- 1 а в нуль и устройство переводится в рабочий режим снятием сигнала начальной установки с входа 11. В первом такте рабочего цикла число из регистра 1 умножается в блоке 2 элементов И на константу а0 фильтра, результат умножения ajXh-1 в виде многострочного кода (матрицы частичных произведений) поступает на вход преобразователя 3 кода, на который посту1 .чет также двустрочный код с блока 8 регистров сдвига. На фиг.4 а и 45 показаны соответственно матрица частичных произведений, поступающая с блока 2, и двустрочный код, поступающий с блока 8. Результирующий многострочный код (шестистрочный) на входе преобразователя 3 кода показан на фиг .4 .

Преобразователь 3 кода содержит группы блоков сумматоров 18, состоящие из блоков сумматоров 19, объединяющие трехвходовые одноразрядные сумматоры 20 одинакового веса. В этом блоке осуществляется последовательное (за несколько тактов работы) преобразование многострочного кода в двустрочный. На диаграммах этого преобразования (фиг.5) рамками обведены числа, подаваемые на вход одного трехвходового одноразрядного сумматора 20. Слева проставлены номера тактов преобразования. Многострочный код (фиг.) за три такта трехвходового одноразрядного сумматора 20 преобразуется в двустрочный код (фиг.5). Сформированный двустрочный код с преобразователя 3 кода записывается в блок 4 регистров путем подачи импульса записи с шестого выхода блока 6. Двустрочный код результата, записанный в блок 4, с помощью сумматора 5 преобразуется к однострочному коду, причем на первый вход сумматора 5 подается первая строка, а на второй вход - вторая строка двустрочного кода. Однострочный код на выходе сумматора 5 есть результат фильтрации на данном такте работы устройства.

После записи кода в блок 4 (одновременно с работой сумматора 5) осуществляется М-1 сдвигов по кольцу содержимого блока 8 через преобразователь 3 кода и коммутатор 9. Синхронно с сдвигами на второй вход блока 2 элементов И подают константы а0, а, . ..,ай. 4 из блока 7. На выходе блока 2 элементов И формируются произведения числа из регистра 1 на константы Фильтра (в виде многострочного кода) Полученные произведения суммируют с соответствующими двустрочными кода- Ми чисел с выхода блока 8 и заносятся в него двустрочным кодом с выхода преобразователя 3 кода через коммутатор 9, на управляющий вход которого поступают импульсы с третьего выхода блока 6.

Коммутатор состоит из двух групп элементов 2И, первые входы элементов 2И обеих групп соединены между собой и являются управляющим входом коммутатора . Вторые входы элементов 2И обеих групп элементов объединены в шину и являются информационным входом коммутатора 9. Входы обеих групп элементов 2И обт единены в шину и являются выходом коммутатора 9. Каждая

0

5

из групп элементов 2И коммутирует одну из строк двустрочного кода.

В последнем М-м такте рабочегр цикла в блок 8 регистров сдвига записывается произведение ад,,хп, а в регистр J осуществляется запись нового значения текущего отсчета входного сигнала. Сдвиг информации (двустрочного кода) в блоке 8 регистров сдвига осуществляется под воздействием тактирующих импульсов, поступающих с пятого выхода блока 6. В М-м такте рабочего цикла производится установка в нуль блока 4 путем подачи сигнала с шестого выхода блока 6. Далее рабочий цикл устройства повторяется .

20 Формула изобретения

5

0

5

0

5

0

5

I. Цифровой нерекурсивный Фильтр, содержащий блок памяти, регистр,вход которого является входом цифрового нерекурсивного фильтра, входами записи и разрешения записи коэффициентов которого являются информационный вход и вход разрушения записи блока памяти соответственно, блок регистров, сумматор, блок регистров сдвига, коммутатор, выходы которого соединены с входами блока регистров сдвига, и блок управления, первый, второй и третий входы которого являются входами начальной установки, установки порядка и тактовым входом цифрового нерекурсивного фильтра соответстственно, а выходы блока управления с первого по шестой соединены с входом записи регистра, адресным входом блока памяти, управляющим входом коммутатора, входами сброса и записи блока регистров сдвига и входом записи блока регистров соответственно, отличающийся тем, что, с целью повышения быстродействия, введены блок элементов И, первый и второй входы которого соединены с выходами регистра и блока памяти соответственно, и преобразователь кода, входы которого соединены с соответствующими выходами блока элементов И и блока регистров сдвига, а выходы преобразователя кода соединены с соответствуюшими входами коммутатора и блока регистров, входы которого соединены с входами сумматора, выход которого является выходом цифрового нерекурсивно:о фильтра.

v

k+1 , d m ,, , d mf,

k 0,1,2,...,

объединены и являются d-м разрядом

Фиг. 2.

JQ 15 20

5

(d - 1,2,..., .j-1) выхода блока элементов И.

группы (k 1,2) подключены к

входам d-ro и (d+l)-ro блока сумматоров (k+O-й группы соответствен но, а выходы сумм блоков сумматоров младшего веса и выходы переносов блоков сумматоров последней группы являются соответствующими выходами преобразователя кода.

765432/7 6 J 4 J 2 17 6 S 4 3 2 J

a 5 6

Фиг.З

Фиг Л

в 7 6 f if 327

Фиг. 5

| Нерекурсивный цифровой фильтр | 1983 |

|

SU1322421A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-05-23—Публикация

1988-06-06—Подача