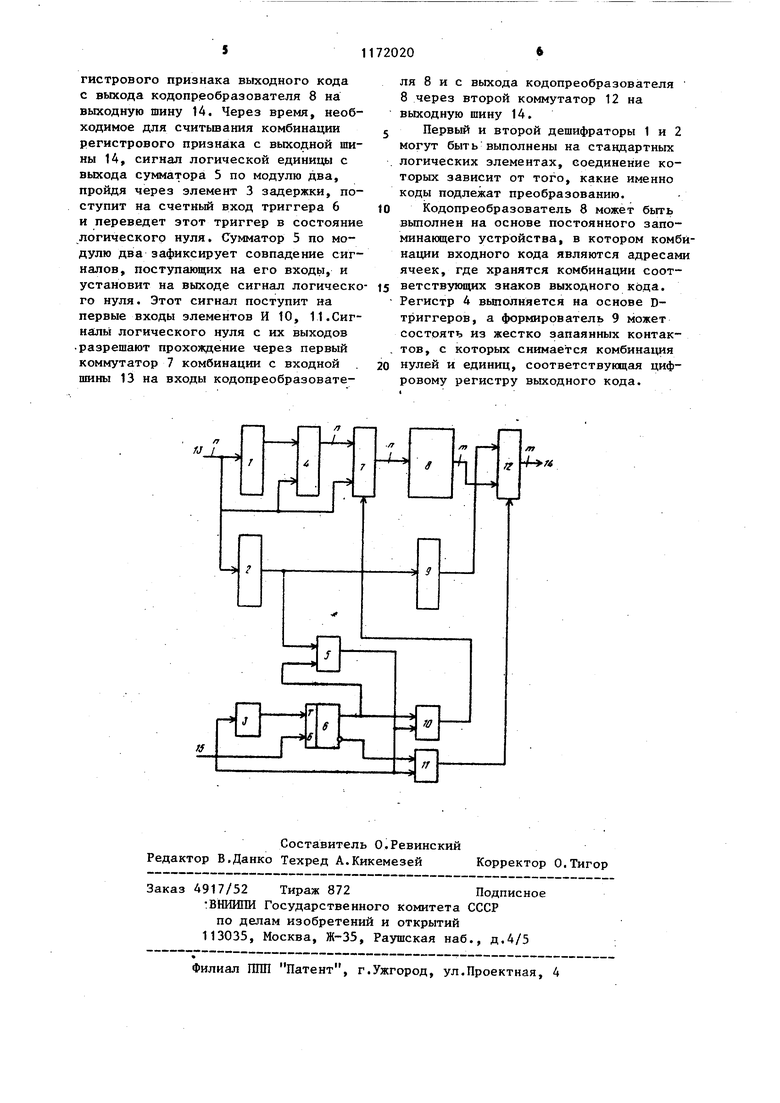

Изобретение относится к вычислительной технике и может быть использовано при построении преобразовате лей в устройствах обмена и ввода-вывода информации. Цель изобретения - расширение функ циональных возможностей путем обеспечения преобразования двухрегистровык кодов в трехрегистровые. На чертеже приведена структурная схема устройства преобразования алфавитно-цифровых кодов. Устройство преобразования алфавитно-цифровых кодов содержит первый дешифратор 1, определяниций регистровый признак входного кода, второй дешифратор 2, определяющий принадлежность комбинации входного кода цифровому регистру выходного кода, элемент 3 задержки, регист)й 4 те1 ущего код ового признака, сумматор 5 по модулю два, триггер 6, первый коммутатор 7, подключающий к выходам первые или вторые входы в зависимости от управляющего сигнала, кодопреобразователь 8, преобразующий комбинации знаков входного кода в комбинации знаков выходного кода в соответствии с таблицей, формирователь 9 признака цифрового регистра, первый и второй злементы И 10, 11, второй коммутатор 12 аналогичный первому, входную информационную шину 13 для приема П-разрядного кода, выходную шину 14 для выдачи, т-разрядного кода и шину 15 началь ной установки. При преобра- овании кодов, имеющих два регистровых (кодовых) признака (русский, латинский), в код, имеющий три регистровых признака (русский, латинский, цифровой), прямое преобразование невозможно. Цифры и некоторые знаки входного кода не имеют регистрового признака, а в выходном коде они принадлежат цифровому регистру. Позтому при поступлении на вход устройства преобразования кодов комбинации цифры или знака, принадлежащего .цифровому регистру выходного кода, необходимо сформировать комбинацию цифрового регистра и вьщать ее перед комбинацией цифры или знакг. По окончании преобразования знаков, принадлежащих цифровому регистру выходного кода, необходимо произвести возврат к тому регистровому признаку, который бьш установлен регистровой комбинацией входного кода на момент прихода омбинации цифр или знаков, принадлеащих цифровому регистру выходного коа, т.е. при поступлении комбинации е цифрового регистра надо сформироать комбинацию прежнего регистровоо признака и выдать ее перед комбиацией знака. Работа устройства происходит следующим образом. Перед началом работы устройства по шине 15 поступает сигнал Начальный сброс, который устанавливает в О триггер 6 (признака цифрового регистра) . Комбинация знака входного кода поступает на входную шину 13 устройства. При поступлении комбинации регистрового признака (русский, латинский) дешифратор 1 вырабатывает сигнал, по которому производится запись комбинации регистрового признака в регистр 4. Эта же комбинация поступает на вход второго дешифратора 2. Так как данная комбинация не принадлежит цифровому регистру выходного кода, то на выходе дешифратора 2 будет присутствовать сигнал логического нуля, который поступит на первый вход сумматора 5 по модулю два. На второй его вход также поступает сигнал логического нуля с первого выхода триггера 6. Таким образом, произойдет сравнение сигналов, поступивших на вход сумматора 5 модулю два, и на его выходе будет сохраняться сигнал логического нуля. Этот сигнал поступит на первые входы соответственно первого и второго злементов И 10, 11. При этом на выходах этих элементов И 10, 11 будет присутствовать сигнал логического нуля. Сигнал с выхода первого элемента И 10 поступит на управлякщий вход первого коммутатора 7, который под воздействием этого сигнала разрешит прохождение кодовой комбинации с входной шины 13 на входы кодопреобразователя 8, где произойдет преобразование кодовой комбинации входного кода в комбинацию соответствующего знака выходного кода. Сигнал с выхода второго элемента И 11 поступит на управляющий вход второго коммутатора 12, который под воздействием этого сигнала разрешит вьщачу комбинации с выхода кодопреобразователя на выходную шину 1 4 . При поступлении на входную шину 1 комбинации знака, не принадлежащего цифровому регистру выходного кода, работа устройства происходит аналогичным образом, за исключейием того, что не будет производиться запись в регистр 4 текущего кодового признака В случае поступления на входную шину 13 комбинации знака, принадлежащего цифровому регистру выходного кода, второй дешифратор 2 фиксирует это и вырабатьшает сигнал логической единицы., который поступает на первый вход сумматора 5 по модулю два и на вход формирователя 9 признака цифрового регистра, который под воздействием этого сигнала вьщает на первую группу входов второго коммутатора 12 комбинацию цифрового регистра выходного кода. Сумматор 5 по модулю два фиксирует несравнение сигналов с вых да дешифратора 2 и с прямого выхода триггера 6 и вырабатывает сигнал логической единицы, который поступает на входы элемента 3 задержки и элементов И 10, 11. На входы первого элемента И 10 будут поступать сигналы различных уровней и с его выхода будет вьщаваться сигнал логического нуля, который, поступая на управляющий вход первого коммутатора 7, разрешит прохождение комбинации с входной шины 13 на входы кодопреобра зователя 8. На входы второго элемента И 1 1 будут поступать сигналы логической единицы с выхода сумматора по модулю два и с инверсного выхода триггера 6. С выхода второго элемента И 1 1 вьщается при этом сигнал лог ческой единицы, который поступит на управляющий вход второго коммутатора 12 и разрешит вьщачу комбинации цифрового регистра выходного кода с выхода формирователя 9 признака цифрового регистра на выходную шину 14. Сигнал логической единицы с выхода сумматора 5 по модулю два поступает также на вход элемента 3 задерж ки, который задерживает сигнал на время, необходимое для считьшания комбинации цифрового регистра с выхо ной шины 14. По истечении этого времени с выхода элемента 3 задержки вьщается сигнал на счетный вход триг гера 6, который переводится в единич ное состояние. Сумматор 5 по модулю два фиксирует совпадение поступающих на его входы сигналов и формирует на своем выходе сигнал логического нуля. Этим сигналом закрываются оба элемента И 10, 11. Сигнал логического нуля с выхода первого элемента И 10, поступая на управляющий вход первого коммутатора 7, разрешает прохождение комбинации с входной шины 13 на входы кодопреобразователя 8. Сигнал логического нуля с выхода второго элемента И 11, поступая на управляющий вход второго коммутатора 12, разрешает вьщачу комбинации знака с выхода кодопреобразователя 8 на выходную шину 14. Если далее на входную шину 13 поступает комбинация , принадлежащего цифровому регистру выходного кода, работа устройства будет происходить аналогично работе, рассмотренной при поступлении в начале работы комбинации регистрового признака за исключением записи в регистр 4 текущего кодового признака. При поступлении вслед за комбинацией знака, принадлежащего цифровому регистру, комбинации знака, не принадлежащего цифровому регистру выходного кода, необходимо перед выдачей знака выдать комбинацию регистрового признака, установленного до перехода к цифровому регистру. Этот признак хранится в регистре 4 текущего кодового признака. Работа устройства в этом случае происходит следующим образом. Дешифратор 2, не зафиксировав эту принадлежность, переводит состояние своего выхода из уровня логической единицы в уровень логического нуля. Сумматор 5 по модулю два фиксирует несравнение сигналов, поступающих на его входы, и формируют сигнал логической единицы. Этот сигнал поступает на первые входы элементов И 10, 11. На второй вход первого элемента И 10 поступает сигнал логической единицы с прямого выхода триггера 6. На выходе первого элемента И 10 формируется сигнал логической единицы, который, поступая на управляющий вход первого коммутатора 7, разрешает прохождение комбинации регистрового признака с выходов регистра 4 на входы кодопреобразователя 8. Сигнал логического нуля с выхода второго элемента И, поступая на управляющий вход второго коммутатора 12, разрешает выдачу комбинации ре

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Аналого-цифровой микропроцессор | 1979 |

|

SU858024A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для преобразования последовательныхМНОгОРЕгиСТРОВыХ КОдОВ B пАРАллЕльНыЕ СКОНТРОлЕМ | 1979 |

|

SU840877A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство цифровой передачи и приема телевизионного сигнала | 1985 |

|

SU1309327A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2233552C2 |

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ АЛФАВИТНО-ЦИФРОВЫХ КОДОВ, содержащее первый и второй дешифраторы, регистр текущего кодового признака, синхронизирующий вход которого подК1ночен к выходу первого дешифратора, кодопреобразователь и формирователь признака цифрового регистра, вход которого подключен к выходу второго дешифратора, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения преобразования двухрегистровых кодов в трехрегистровые, в него введены первый и второй коммутаторы, сумматор по модулю два, элемент задержки, первый и второй элементы И и триггер, вход установки в О которого соединен с шиной начальной J установки, прямой выход подключен к первому входу сумматора по модулю два, второй вход которого соединен с выходом второго дешифратора, а выход подключен к первым входам первого и второго элементов И и через элемент задержки - к счетному входу триггера, прямой и инверсный выходы которого соединены с вторыми входами соответственно первого и второго элементов И, выходы которых подключ ены к управляющим входам соответствующих коммутаторов, первые входы которых соединены с выходами соответственно регистра текущего регистрового S признака и формирователя признака (Л цифрового регистра, вторые входы первого коммутатора объединены с соответствукнцими входами регистра текущего регистрового признака, первого и второго де1Щ1фраторов и подключены к входной информационной шине устройства, выходы первого коммутатора соединены с входами кодопреобразог SD вателя, выходы которого соединены с вторыми входами второго коммутатора, выходы которого подключены к выходной шине.

| Устройство преобразования кодов | 1976 |

|

SU595859A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 915072, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| , | |||

Авторы

Даты

1985-08-07—Публикация

1984-03-16—Подача