устройства, выходы сумматоров по модулю два группы соединены с первым информационным входом первого блока памяти и информационным входом второго регистра., входы синхронизашш всех регистров соединены с входом тактовых импульсов устройства, выход дешифратора соединен с информаци- . онным входом третьего регистра и вторым информационШ)1м входом первого блока памяти, третий информационный вход которого соединен с входом задания знака устройства и первым информационным входом второго блока памяти, выход первого блока памяти соединен с первой группой входов первого сумматора, входы младших разрядов второй группы которого сое.динены с выходами с маторов по модулю два группы, входы старших раз057942

рядов второй группы первого сумматора соединены с входом задания знака устройства, выход первого регистра соединен с первой группой входов второго сумматора, вторая группа входов которого соединена с выходом второго блока памяти, второй информационный вход которого соединен с выходом третьего регистра,,третий информационный вход второго блока памяти соединен с выходом второго регистра, выход второго сумматора соединен с информа:ционным входом младших разрядов сдвигателя, вход старшего разряда которого соединен с входом «Задания знака устройства, уп.равляю1ций вход сдвигателя соединен i с выхода первого сумматора блока управления,выход сдвигателя соединен с выхо. дом кода результата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| УСТРОЙСТВО СОВМЕСТНОГО КОДИРОВАНИЯ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497180C1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

Устройство относится к вычислительной технике и может быть использовано в цифровых устройствах, фильтрации сигналов.

Известно устройство для вычисления показательных функций, содержащее регистр аргумента, накопитель, состоянщй из -П сдвигающих регистр(№, блок умножения, .(п+) элементов И и блок выборки информации, выходы блока управления соединены с входами блока умножения,входами управления сдвигающих регистров накоптеля, входом блока выборки информации, выходы блока выборки соединены с входами блока умножения, входы сдвигающих регистров являются входами ус&ройства, а выходы через элементы Н соединены с входами блока выборки

Недостатком устройства является ограниченное быстродействие, обусловленное последовательным рекурсивным методом выполнения вычислительных операций.

Наиболее близким по технической сущности к предлагаемому является устройство для возведения в степень содержащее регистр операнда, регистры промежуточных и окончательных результатов, сумматор, блок управления, причем входы регистров промежуточных результатов подключены к выходам сумматора, первая группа входов которого подключена к выходам perijCTpoB промежуточных результатов, первый выхо блока управления подключен к управляющим входам сдвига регистров окончательных и промежуточных результатов, счетчик, сдвигатель, распределитель сигналов, кодопреобразователь и триггеры цифр результатов, выходы счетчика подключены к входам регистров окончательных результатов, выходы которых подключеш к входам счетчика, а также к входам сдвигателя, вторая группа входов сумматора подключена к выходам регистрА операнда, а третья группа входов - к выходам сдвигателя, выходы прямых и инверсных значений трех старших разрядов сумматора подключены к входам кодопреобразователя, первый и второй входы которого соединены с входами первого и второго триггеров ищфр результата, другие входы которых подключены к первому выходу блока управления, входы которого соединены с выходами триггеров цифр результата, а также с управляв входами счетчика и регистра

операнда, выходы распределителя сигналов подключены к входам младших разрядов регистра операнда и к управляющим входам сдвигателя, входны шины устройства подключены к управляющим входам сдвигателя и регистра операнда, второй выход блока управления соединен с управляющими входа ми регистра операнда и распределителя сигналов, остальные 2 выходов блока управления подключены к выход ным шинам устройства 2 , Недостаток известного устройства заключается в ограниченном быстроде ствии обусловленном последовательным рёкурсианым характером вычислений. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в устройство лдя вычисления функции у 2 , содержащее три регистра, первый сумматор, первый блок памяти, блок управления и сдви гатель, причём выход первого сумматора соединен с информационным вход первого регистра, дополнительно вве дены дешифратор, второй блок памяти группа сумматоров по модулю два и второй сумматор, причем блок управления содержит три элемента И, два элемента НЕ, два элемента ИЛИ, два cyMhiaTOpa и группу сумматоров по мо дулю два, выходы которых соединены с первой группой входов первого сумматора, первый, второй и четвертый разряды второй группы входов ко торого соединены с выходом первого элемента НЕ и первыми входами сумматоров по модулю два группы, вторые входы которых соединены с выход ми второго сумматора, первый и Tpieтий разрядь первой группы входов ко торого соединены с выходом первого элемента ИЛИ, входы которого соединены с выходами первого и второго элементов И и второго элемента НЕ, выход которого соединен с первым вх дом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, выходы элементов ИЛИ соединены с выходом признака масштабирования устройства, вход первого элемента НЕ соединен с выхо дом знака второго регистра, вход за дания знака ус- ройства соединен с вторым и четвертым разрядами первой группы входов второго сумматора и третьим разрядом второй группы входов первого сумматора блока управления, первые входы элементов И и- вход второго элемента НЕ соединены с первым входом задания режима устройства, второй вход задания режима которого соединен с вторыми входами элементов И, первый вход второго регистра соединен с третьим входом первого элемента И и первымразрядом второй группы входов второго сумматора блока управления, второй разояд второй группы входов которого соединен с вторым разрядным выходом второго регистра, четвертым входом первого и третьим входом второго элементов И, пятый и четвертый входь которых соединены соответственно с третьим и четвертым разрядными выходами второго регистра и третьим и четвертым разрядами второй группы входов второго сумматора блока управления, пятый разрядный выход второго регистра аргумента устройства соединен с третьим входом третьего элемента И, входы мантиссы и порядка аргумента устройства соединены с первыми входами сумматоров по модулю два группы, вторые входы которых соединены с входом знака аргумента устройства, выходы сумматоров по модулю два группы соединены с первым информационным входом первого блока памяти и информационным входом второго ре-гистра, входы синхронизации всех регистров соединены с входом тактовых импульсов устройства, выход дешифратора соединен с информациЬнным входом третьего регистра и вторым информационным входом первого блока памяти, третий информационный вход которого соединен с входом задания знака устройства и первым информационным входом второго блока памяти, выход первого блока памяти соединен с первой группой входов первого сумматора, входы младших разрядов второй группы которого соединены с выходами сумматоров по модулю два группы, входы старших разрядов второй группы первого сумматора соединены с входом задания .знака устройства, выход первого регистра соединен с первой группой входов второго сумматора, вторая группа входов которого соединена с выходом второго блока памяти, второй информационньш вход которого соединен с выходом третьего регистра, третий информационный

вход второго блока памяти соединен с i выходом второго регистра, выход второго сумматора соединен с информационным входом младших разрядов сдвигателя, вход старшего разряда которого соединен с входом задания знака устройства, управляющий вход сдвигателя соединен с выходом первого сумматора блока управления, выход сдвигателя соединен с выходом кода результата устройства.

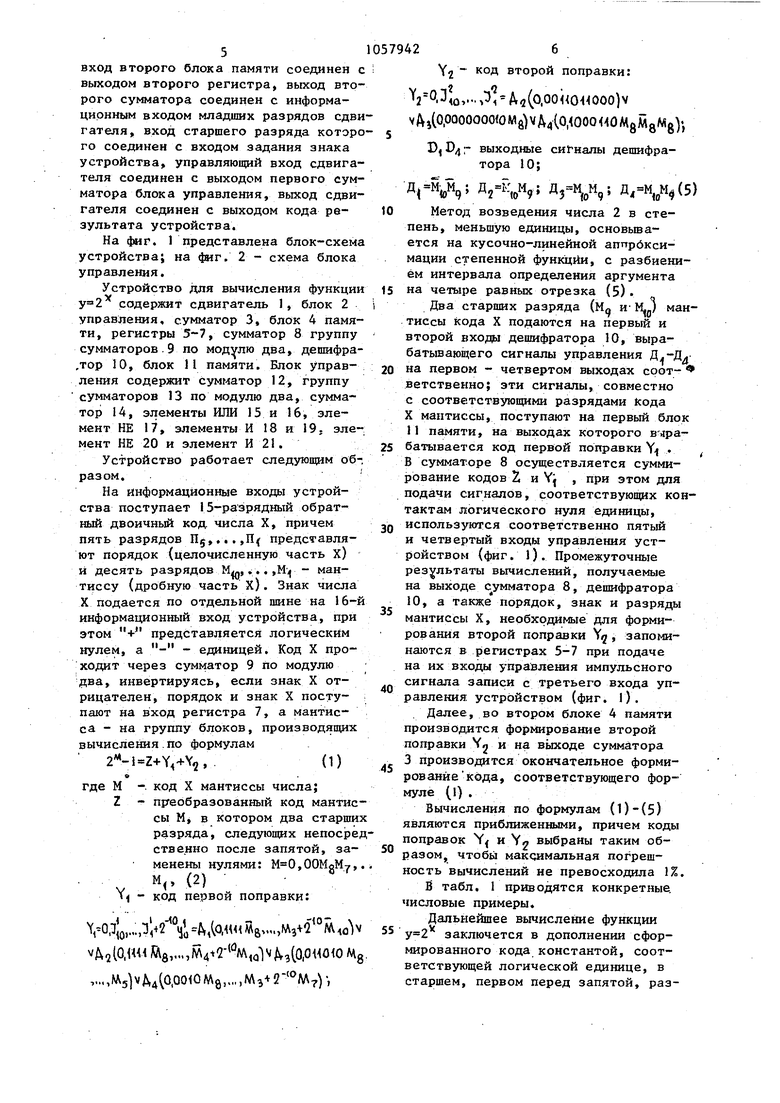

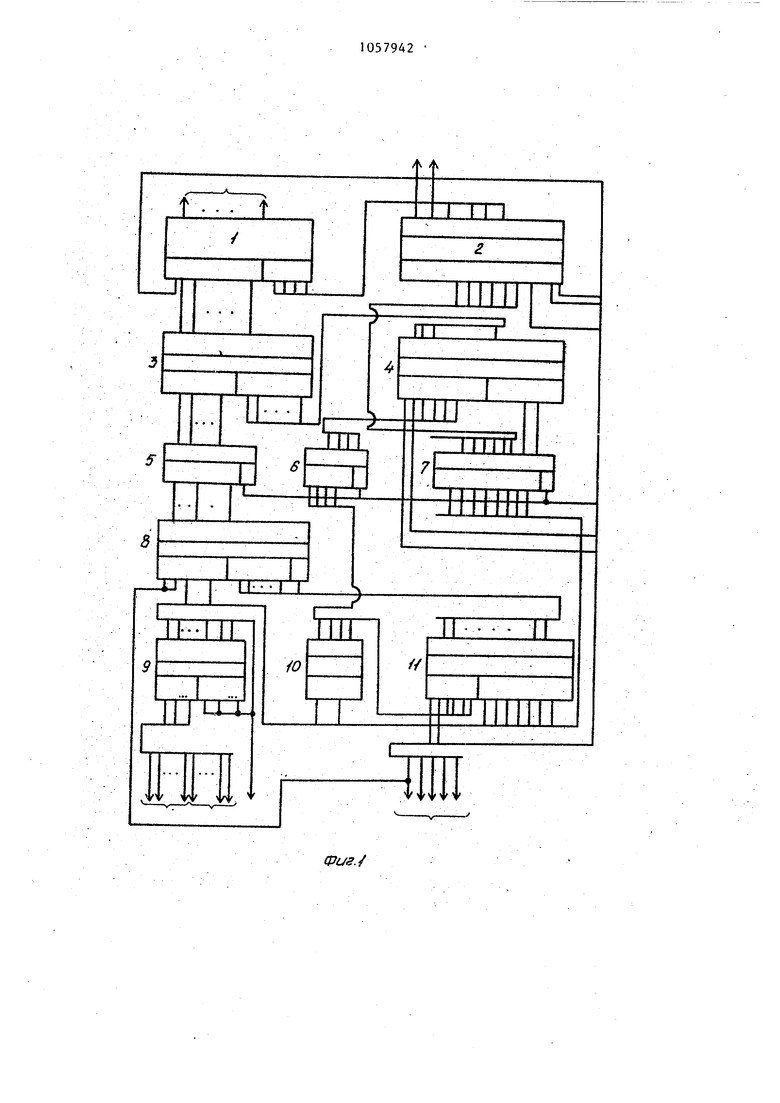

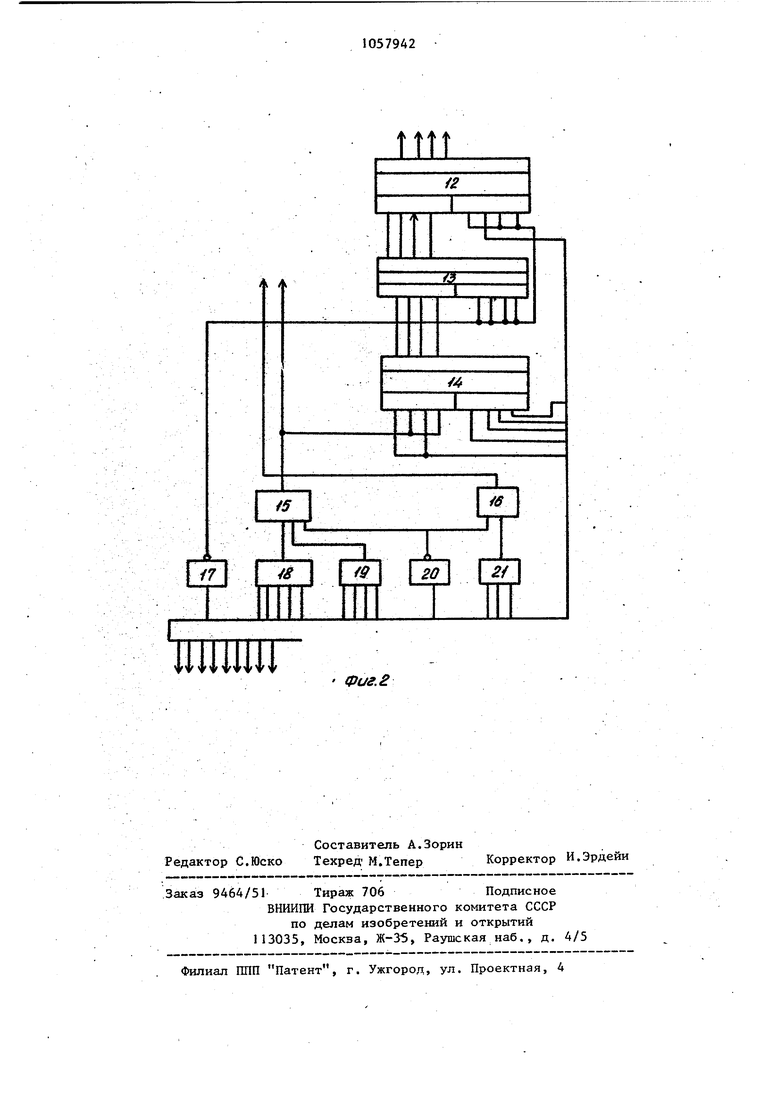

На фиг. 1 представлена блок-схема стройства; на 4мг. 2 - схема блока управления.

Устройство для вычисления функции содержит сдвигатель 1 , блок 2 i управления, сумматор 3, блок 4 памяти, регистры 5-7, сумматор 8 группу сумматоров.9 по модулю два, дешифратор 10, блок 11 памяти. Блок управления содержит сумматор 12, группу сумматоров 13 по модулю два, сумматор 14, элементы ИЛИ 15 и 16, элемент НЕ 17, элементы И 18 и 19, элемент НЕ 20 и элемент И 21.

Устройство работает следующим образом.

На информационные входы устройства поступает 15-разрядный обратный двоичный код. числа X, причем пять разрядов П,,..,П| представляют порядок (целочисленную часть Х) и десять разрядов М, v..,М - мантиссу (дробную часть Х). Знак числа X подается по отдельной шине на 16-й информационный вход устройства, при этом + представляется логическим нулем, а - - единицей. Код X проходит через сумматор 9 по модулю два, инвертируясь, если знак X отрицателен, порядок и знак X поступают на вход регистра 7, а мантисса - на группу блоков, производящих вычисления.по формулам

,j, .(1)

ft где М -. код X мантиссы числа;

Z - преобразованный код мантиссы М, в котором два старших разряда, следующих непосредственно после запятой, заменены нулями: ,ООМоМ7,.i

V .О .

М«, (2)

Viкод первой поправки:

V0.4..M 1 2Ai AQ-«MMa,.u,,oV vA,2(o.fH4 ,...,,(0, Mg,

v..,..,,M3+2-°AA7)-,

Yj код второй поправки:

,3,Q,...p ;,2(o ooino ooo)v

vAi(0,0000000{OMg)vA4(0,000 40MgM8Mg),

Dj 4 r выходные сигналы дешифратора 10;

,; д,м,„м(5)

Метод возведения числа 2 в степень, меньшую единицы, основьюается на кусочно-линейной аппрбксимации степенной функции, с разбиением интервала определения аргумента на четыре равных отрезка (5) .

Два старших разряда (Мп и- R) мантиссы кода X подаются на первый и второй входы дешифратора 10, вырабатьшающего сигналы управления на первом - четвертом выходах срот- ветственно; эти сигналы, совместно с соответствующими разрядами кода X мантиссы, поступают иа первый блок 11 памяти, на выходах которого влрабатывается код первой поправки Y . В сумматоре 8 осуществляется суммирование кодов 2i и YI , при этом для подачи сигналов, соответствующих контактам логического нуля единицы, используются соответственно пятый и четвертый входы управления устройством (фиг. 1). Промежуточные результаты вычислений, получаемые на выходе сумматора 8, дешифратора 10, а также порядок, знак и разряды мантиссы X, необходимые для формирования второй поправки Y, запоминаются в регистрах 5-7 при подаче на их входы управления импульсного сигнала записи с третьего входа управления устройством (фиг. 1).

Далее, во втором блоке 4 памяти производится формирование второй поправки Ул и на выходе сумматора 3 производится окончательное формирование кода, соответствующего формуле (1) .

Вычисления по формулам (1)-(5) являются приближенными, причем коды поправок V и Yn выбраны таким образом, чтобы максимальная погрешность вычислений не превосходила 1%.

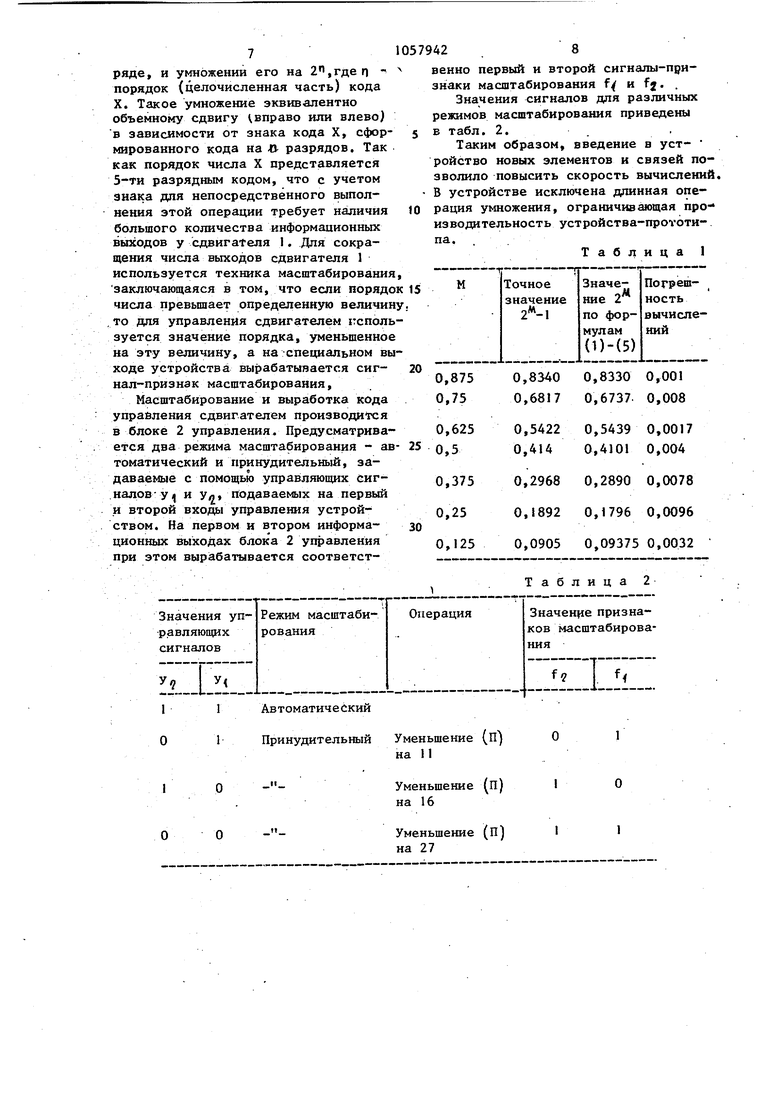

В табл. 1 приводятся конкретные, числовые примеры.

Дальнейшее вычисление функции 5 заключется в дополнении сформированного кода константой, соответствующей логической единица, в старшем, первом перед запятой, разряде, и умножении его на 2,тр,ег порядок (целочисленная часть) кода X. Такое умножение эквивалентно объемному сдвигу вправо или влево) в зависимости от знака кода X, сформированного кода на JO- разрядов. Так как порядок числа X представляется З-ти разрядным кодом, что с учетом знака для непосредственного выполнения этой операции требует наличия большого количества информационных выходов у сдвигателя 1. Для сокращения числа выходов сдвигателя 1 используется техника масштабирования, заключающаяся в том, что если порядок 15 числа превьшает определенную величину. ,то для управления сдвигателем гспользуется значение порядка, уменьшенное на эту величину, а на специальном выходе устройства вырабатывается сиг- 20 нал-признак масштабирования. Масштабирование и выработка кода управления сдвигателем производится в блоке 2 управления. Предусматривается два режима масштабирования - ав- 25 томатический и принудительный, задаваемые с помощью управляющих сигналов -у i| и ул, подаваемых на первый и второй входы управления устройством. На первом и втором информа- зо ционных выходах блока 2 управления при этом вырабатывается соответст1 Автоматический

1 Принудительный Уменьшение (п)

О - -Уменьшение (п)

О - -Уменьшение (П) 1057 5

Таблица 2

на 11

О

на 16

на 27 428 венно первый и второй сигналы-признаки масштабирования f| и fj. . Значения сигналов для различных режимов масштабирования приведены в табл. 2. . , Таким образом, введение в устройство новых элементов и связей позволило повысить скорость вычислений. В устройстве исключена длинная операция умножения, ограничивающая про изводительность устройства-прототипа. Таблица

л

фаз./

т

ффффффффф

Фиг. 2

tttt

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления показательных функций | 1975 |

|

SU728126A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-11-30—Публикация

1981-07-02—Подача