Изобретение относится к технике телевидения и может быть использовано в системах передачи сигналов монохромного или цветного телевизионного сигнала методом импульсно-кодовой модуляции .

Цель изобретения - повышение точности передачи телевизионного сигнала.

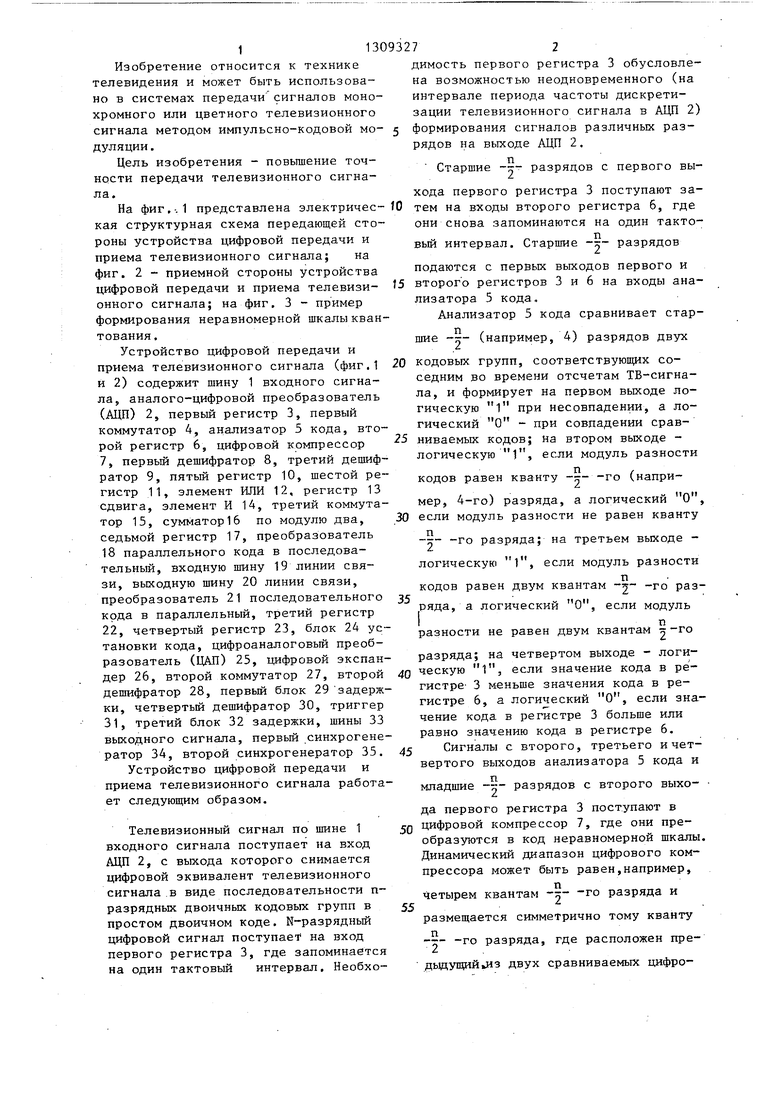

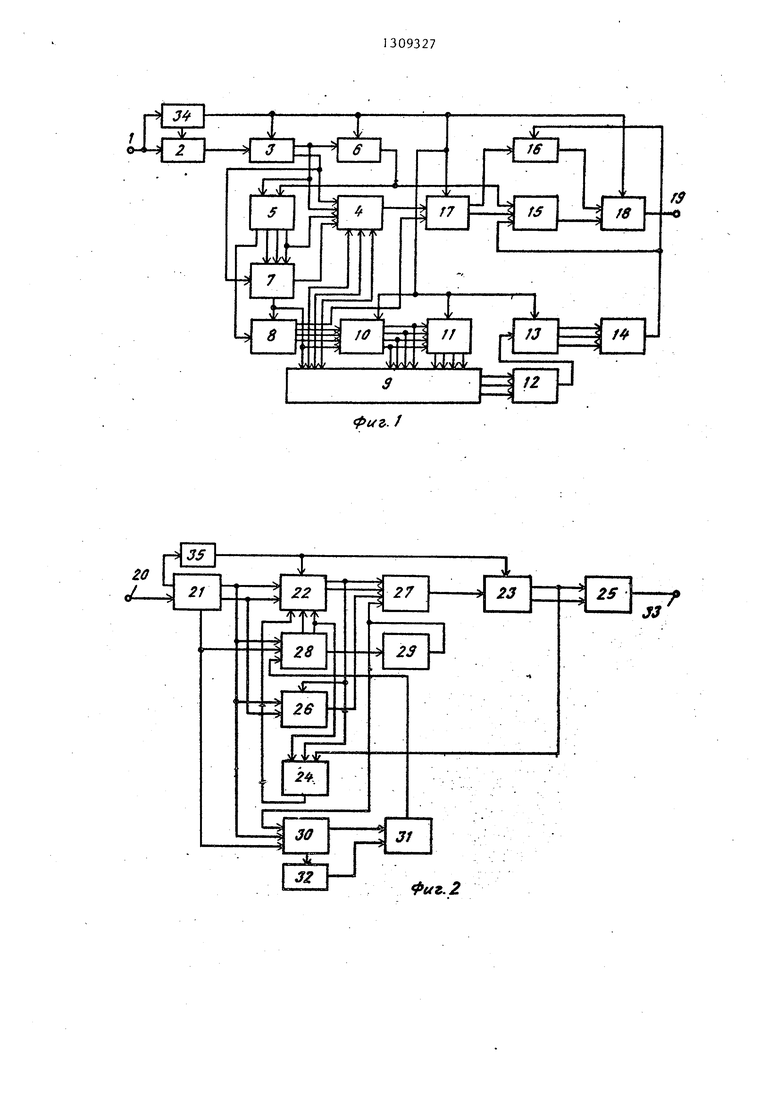

На фиг,-. 1 представлена электричес- 10 тем на входы второго регистра

димость первого регистра 3 обу на возможностью неодновременно интервале периода частоты диск зации телевизионного сигнала в формирования сигналов различны рядов на выходе АЦП 2,

г

Старшие разрядов с перв хода первого регистра 3 поступ

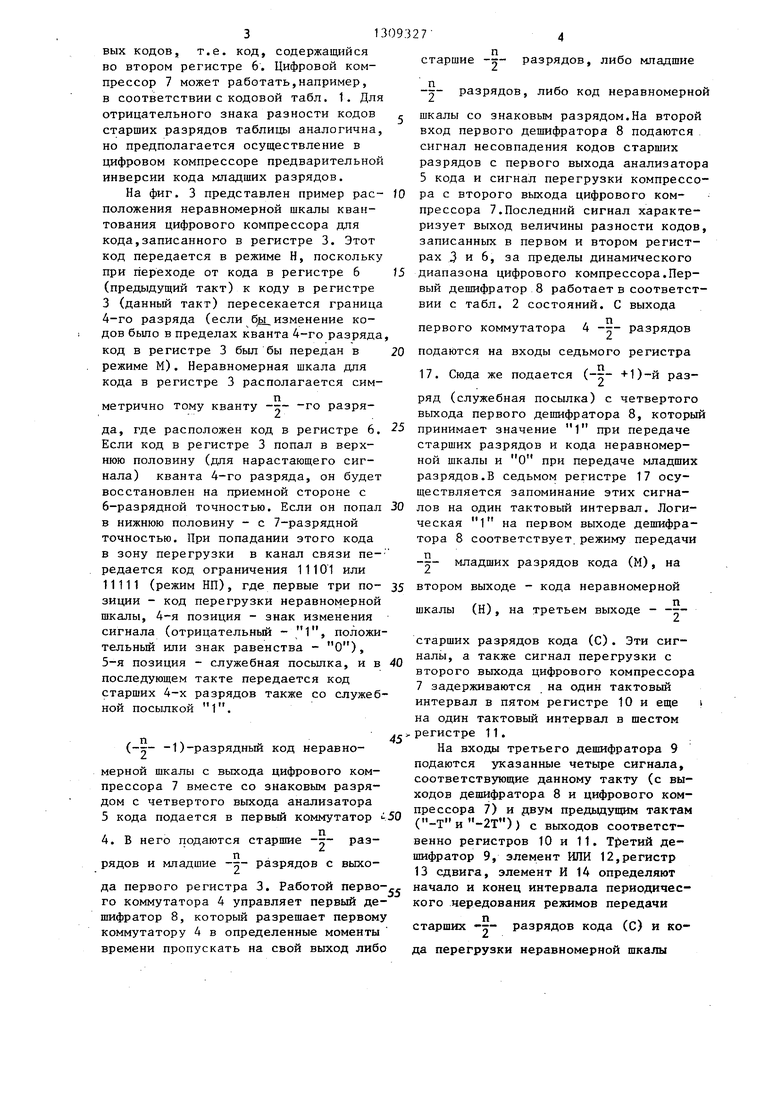

б, где тактокая стр уктурная схема передающей сто РОНЫ устройства цифровой передачи и приема телевизионного сигнала; на фиг. 2 - приемной стороны устройства цифровой передачи и приема телевизи- 15 онного сигнала; на фиг. 3 - пример формирования неравномерной шкалы квантования.

Устройство цифровой передачи и приема телевизионного сигнала (фиг.1 20 и 2) содержит шину 1 входного сигнала аналого-цифровой преобразователь (АЦП) 2, первьш регистр 3, первый коммутатор 4, анализатор 5 кода, второй регистр 6, цифровой компрессор ниваемык кодов; На втором выходе - 7, первьш дешифратор 8, третий дешиф- логическую 1, если модуль разности

они снова запоминаются на один

л,П

выи интервал. Старшие разрядов

подаются с первых выходов первого и второго регистров 3 и 6 на входы анализатора 5 кода.

Анализатор 5 кода сравнивает старп .. , ч шие (.например, 4; разрядов двух

кодовых групп, соответствующих соседним во времени отсчетам ТВ-сигнала, и формирует на первом выходе логическую l при несовпадении, а логический О - при совпадении сравратор 9, пятый регистр 10, шестой регистр 11, элемент ИЛИ 12, регистр 13 сдвига, элемент И 14, третий коммутатор 15, сумматор 16 по модулю два, седьмой регистр 17, преобразователь 18 параллельного кода в последовательный, входную шину 19 линии связи, выходную шину 20 линии связи, преобразователь 21 последовательного кода в параллельный, третий регистр 22, четвертый регистр 23, блок 24 установки кода, цифроаналоговый преобразователь (ЦАП) 25, цифровой экспандер 26, второй коммутатор 27, второй дешифратор 28, первый блок 29 задержки, четвертый дешифратор 30, триггер 31, третий блок 32 задержки, шины 33 выходного сигнала, первый синхрогене- ратор 34, второй синхрогенератор 35.

Устройство цифровой передачи и приема телевизионного сигнала работает следующим образом.

Телевизионный сигнал по шине 1 входного сигнала поступает на вход АЦП 2, с выхода которого снимается цифровой эквивалент телевизионного сигнала в виде последовательности п- разрядных двоичных кодовых групп в простом двоичном коде. N-разрядный цифровой сигнал поступает на вход первого регистра 3, где запоминается на один тактовый интервал. Необхотем на входы второго регистра

димость первого регистра 3 обусловлена возможностью неодновременного (на интервале периода частоты дискретизации телевизионного сигнала в АЦП 2) формирования сигналов различных разрядов на выходе АЦП 2,

г

Старшие разрядов с первого выхода первого регистра 3 поступают заб, где тактониваемык кодов; На втором выходе - логическую 1, если модуль разности

они снова запоминаются на один

л,П

выи интервал. Старшие разрядов

подаются с первых выходов первого и второго регистров 3 и 6 на входы анализатора 5 кода.

Анализатор 5 кода сравнивает старп .. , ч шие (.например, 4; разрядов двух

кодовых групп, соответствующих соседним во времени отсчетам ТВ-сигнала, и формирует на первом выходе логическую l при несовпадении, а логический О - при совпадении сравкодов равен кванту -s- -го (например, 4-го) разряда, а логический О, если модуль разности не равен кванту

п -го разряда; на третьем выходе логическую l,

если модуль разности

п

кодов равен двум квантам -j- -го разряда, а логический О, если модуль

Iп

разности не равен двум квантам - го

разряда; на четвертом выходе - логическую 1, если значение кода в регистре- 3 меньше значения кода в регистре 6, а логический О, если значение кода в регистре 3 больше или равно значению кода в регистре 6.

Сигналы с второго, третьего и четвертого выходов анализатора 5 кода и

п младшие -т;- разрядов с второго выхо-

да первого регистра 3 поступают в цифровой компрессор 7, где они преобразуются в код неравномерной шкалы Динамический диапазон цифрового компрессора может быть равен,например.

четырем квантам

п

.- -го

разряда и

размещается симметрично тому кванту

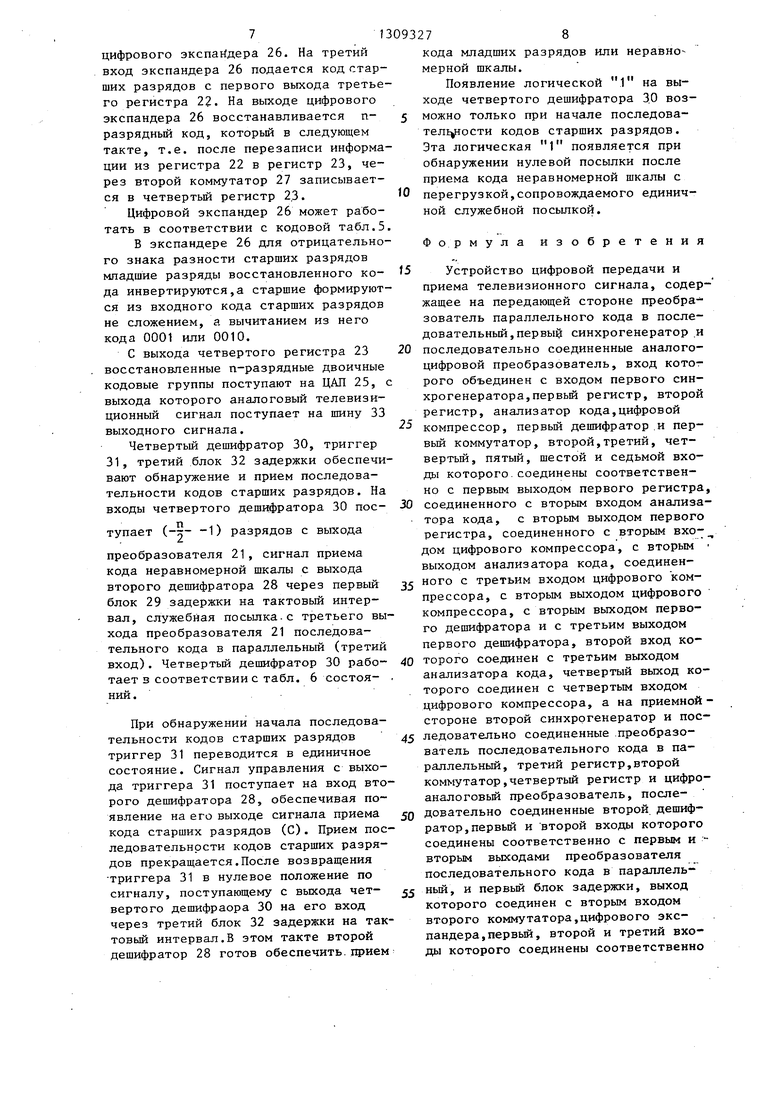

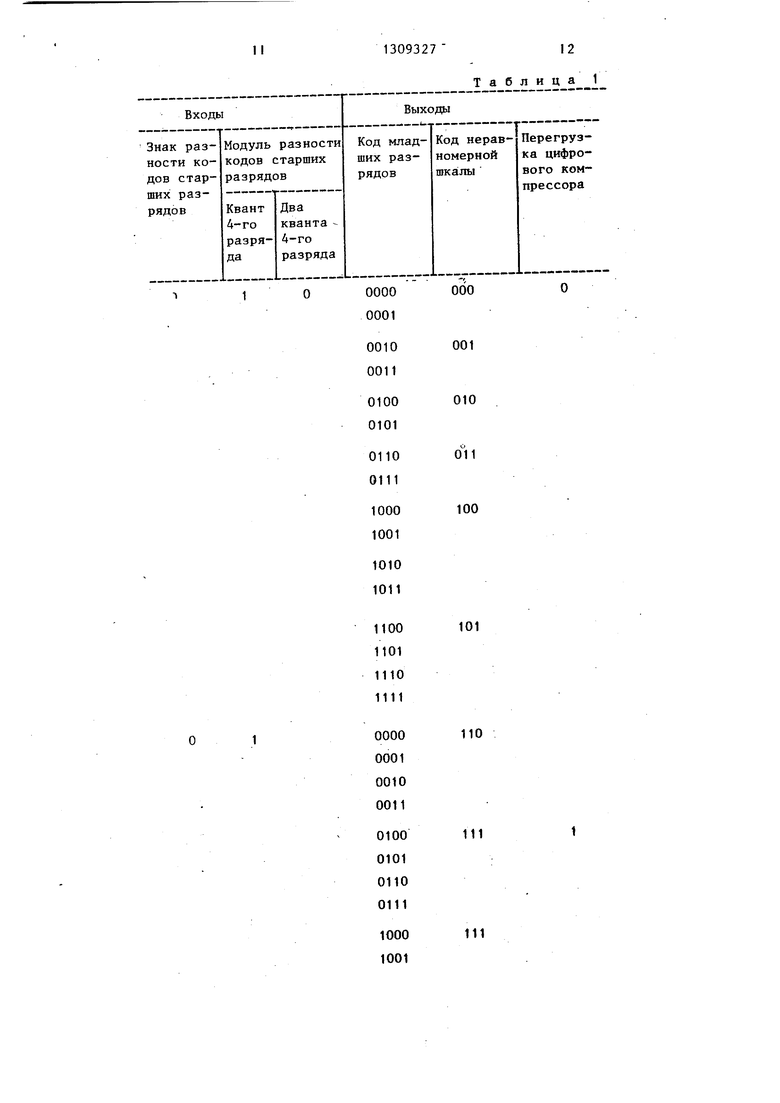

п --- -го разряда, где расположен предьвдущ;ий из двух сравниваемых цифровых кодов, т.е. код, содержащийся во втором регистре 6. Цифровой компрессор 7 может работать,например, в соответствии с кодовой табл. 1. Для отрицательного знака разности кодов старших разрядов таблицы аналогична, но предполагается осуществление в цифровом компрессоре предварительной инверсии кода младших разрядов.

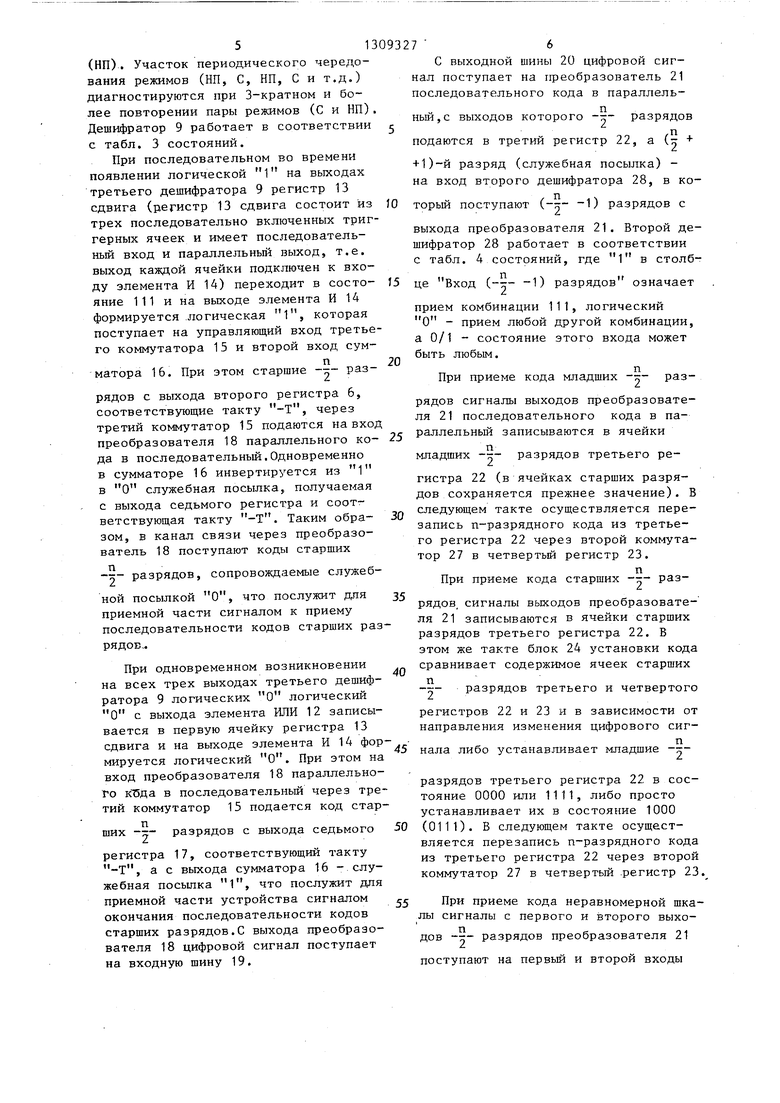

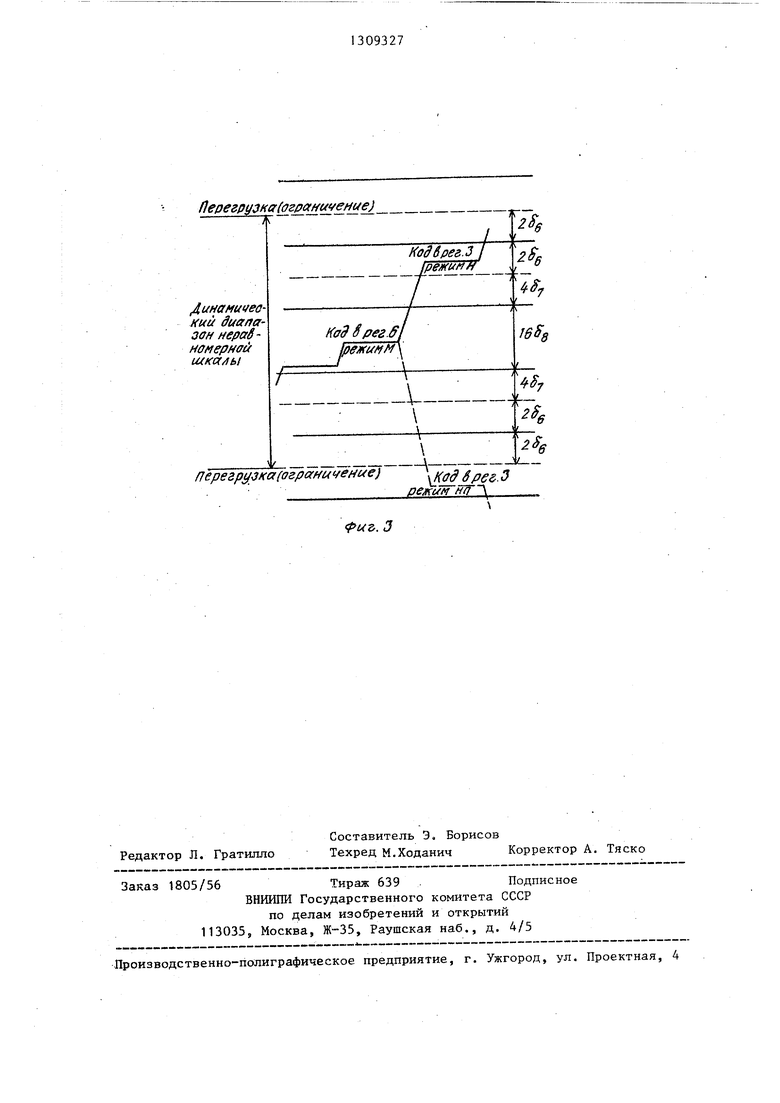

На фиг. 3 представлен пример рас- W положения неравномерной шкалы квантования цифрового компрессора для кода,записанного в регистре 3. Этот код передается в режиме Н, поскольку при переходе от кода в регистре 6 15 (предыдущий такт) к коду в регистре 3 (данный такт) пересекается граница 4-го разряда (если бд изменение кодов было в пределах кванта 4-го разряда, код в регистре 3 был бы передан в 20 режиме М). Неравномерная шкала для кода в регистре 3 располагается симп

метрично тому кванту -го разряда, где расположен код в регистре 6. -5 Если код в регистре 3 попал в верхнюю половину (для нарастающего сигнала) кванта 4-го разряда, он будет восстановлен на приемной стороне с 6-разрядной точностью. Если он попал 30 в нижнюю половину - с 7-разрядной точностью. При попадании этого кода в зону перегрузки в канал связи пе-- редается код ограничения 11101 или 11111 (режим НП), где первые три по- 35 зиции - код перегрузки неравномерной шкалы, 4-я позиция - знак изменения сигнала (отрицательный - 1, положительный или знак равенства - О), 5-я позиция - служебная посылка, и в 40 последующем такте передается код старших 4-х разрядов также со служебной посылкой 1.

г п .. „45

(-j- -1 -разрядный код неравномерной шкалы с выхода цифрового компрессора 7 вместе со знаковым разрядом с четвертого выхода анализатора 5 кода подается в первый коммутатор ц50

/ п

4. В него подаются старшие -г- разп

рядов и младшие разрядов с выхода первого регистра 3. Работой парно-„ го коммутатора 4 управляет первый дешифратор 8, который разрешает первому коммутатору 4 в определенные моменты времени пропускать на свой выход либо

старшие разрядов, либо младшие

-J- разрядов, либо код неравномерно

шкалы со знаковым разрядом.На второй вход первого дешифратора 8 подаются сигнал несовпадения кодов старших разрядов с первого выхода анализатор 5 кода и сигнал перегрузки компрессора с второго выхода цифрового компрессора 7.Последний сигнал характеризует выход величины разности кодов записанных в первом и втором регистрах 3 и 6, за пределы динамического диапазона цифрового компрессора.Первый дешифратор 8 работает в соответствии с табл. 2 состояний. С выхода

/ п первого коммутатора 4 разрядов

подаются на входы седьмого регистра 17. Сюда же подается (- +1)-й разряд (служебная посылка) с четвертого выхода первого дешифратора 8, которы принимает значение 1 при передаче старших разрядов и кода неравномерной шкалы и О при передаче младших разрядов.В седьмом регистре 17 осуществляется запоминание этих сигналов на один тактовый интервал. Логическая 1 на первом выходе дешифратора 8 соответствует, режиму передачи

-г- младших разрядов кода (М), на втором выходе - кода неравномерной шкалы (Н), на третьем выходе - --старших разрядов кода (С). Эти сигналы, а также сигнал перегрузки с второго выхода цифрового компрессора 7 задерживаются на один тактовый интервал в пятом регистре 10 и еще на один тактовый интервал в шестом .регистре 11.

На входы третьего дешифратора 9 подаются указанные четыре сигнала, соответствующие данному такту (с выходов дешифратора 8 и цифрового компрессора 7) и двум предыдущим тактам

/11 mil „ II OT 1

ч -i и -/1 }) с выходов соответственно регистров 10 и 11. дешифратор 9, элемент ИЛИ 12,регистр 13 сдвига, элемент И 14 определяют начало и конец интервала периодического чередования режимов передачи

старших -т- разрядов кода (С) и кода перегрузки неравномерной шкалы

(НП), Участок периодического чередования режимов (НП, С, НП, Сит.д.) диагностируются при 3-кратном и более повторении пары режимов (С и НП) Дешифратор 9 работает в соответствии с табл. 3 состояний.

При последовательном во времени появлении логической 1 на выходах третьего дешифратора 9 регистр 13 сдвига (регистр 13 сдвига состоит из трех последовательно включенных триг герных ячеек и имеет последователь- ньш вход и параллельный выход, т.е. выход каждой ячейки подключен к входу элемента И 14) переходит в состо- яние 111 и на выходе элемента И 14 формируется .логическая 1, которая поступает на управляющий вход третьего коммутатора 15 и второй вход сумматора 16. При этом старшие разрядов с выхода второго регистра 6, соответствующие такту -Т, через третий коммутатор 15 подаются на вход преобразователя 18 параллельного ко- да в последовательный,Одновременно в сумматоре 16 инвертируется из 1 в О служебная посылка, получаемая с выхода седьмого регистра и соответствующая такту -Т. Таким обра- зом, в канал связи через преобразователь 18 поступают коды старших

-т;- разрядов, сопровождаемые служебной посылкой О, что послужит для приемной части сигналом к приему последовательности кодов старших разрядов,.

При одновременном возникновении на всех трех выходах третьего дешифратора 9 логических О логический О с выхода элемента ИЛИ 12 записывается в первую ячейку регистра 13 сдвига и на выходе элемента И 14 формируется логический О. При этом на вход преобразователя 18 параллельно- го кТЗда в последовательный через третий коммутатор 15 подается код старших -;

разрядов с выхода седьмого

регистра 17, соответствующий такту -Т, а с выхода сумматора 16 - служебная посылка 1, что послужит для приемной части устройства сигналом окончания последовательности кодов старших разрядов.С выхода преобразователя 18 цифровой сигнал поступает на входную шину 19.

5 0

5

0

0

5

С выходной шины 20 цифровой сигнал поступает на преобразователь 21 последовательного кода в параллельпныи,с выходов которого -г- разрядов

подаются в третий регистр 22, а ( +

+1)-й разряд (служебная посылка) - на вход второго дешифратора 28, в коX ПV

торыи поступают (-о U разрядов с

выхода преобразователя 21. Второй дешифратор 28 работает в соответствии с табл. 4 состояний, где 1 в столбце Вход ( -1) разрядов означает

прием комбинации 111, логический О - прием любой другой комбинации, а 0/1 - состояние этого входа может быть любым.

п

При приеме кода младших разрядов сигналы выходов преобразователя 21 последовательного кода в параллельный записываются в ячейки

п

младших разрядов третьего регистра 22 (в ячейках старших разрядов сохраняется прежнее значение). В следующем такте осуществляется перезапись п-разрядного кода из третьего регистра 22 через второй коммутатор 27 в четвертый регистр 23.

п

При приеме кода старших --- разрядов, сигналы выходов преобразователя 21 записываются в ячейки старших разрядов третьего регистра 22. В этом же такте блок 24 установки кода сравнивает содержимое ячеек старших

п

разрядов третьего и четвертого

регистров 22 и 23 н в зависимости от направления изменения цифрового сигп

нала либо устанавливает младшие - разрядов третьего регистра 22 в состояние 0000 или 1111, либо просто устанавливает их в состояние 1000 (0111). В следующем такте осуществляется перезапись п-разрядного кода из третьего регистра 22 через второй коммутатор 27 в четвертый .регистр 23.

При приеме кода неравномерной шкалы сигналы с первого и второго выходов --- разрядов преобразователя 21

поступают на первьй и второй входы

цифрового экспандера 26. На третий вход экспандера 26 подается код старших разрядов с первого выхода третьего регистра 22. На выходе цифрового экспандера 26 восстанавливается п- разрядный код, который в следующем такте, т.е. после перезаписи информации из регистра 22 в регистр 23, через второй коммутатор 27 записывается в четвертый регистр 2,3.

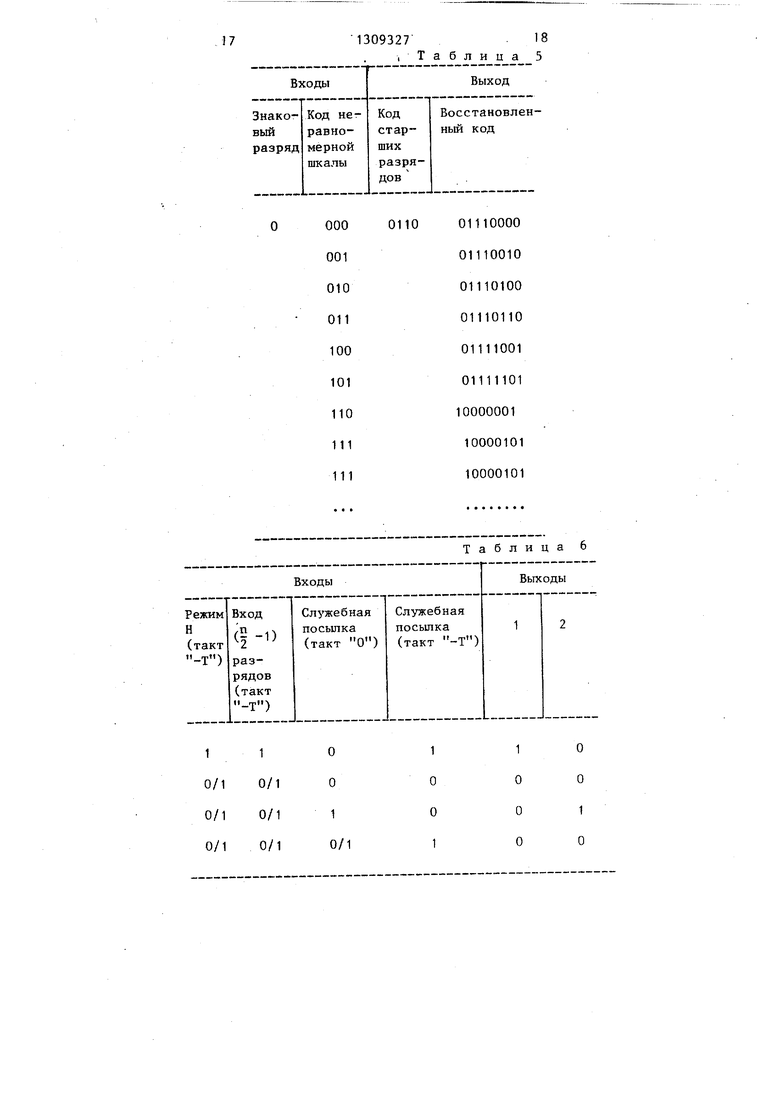

Цифровой экспандер 26 может работать в соответствии с кодовой табл.5 В экспандере 26 для отрицательного знака разности старших разрядов младшие разряды восстановленного ко- да инвертируются,а старшие формируются из входного кода старших разрядов не сложением, а вычитанием из него кода 0001 или 0010.

С выхода четвертого регистра 23 восстановленные п-разрядные двоичные кодовые группы поступают на ЦАП 25, выхода которого аналоговый телевизи- ционный сигнал поступает на шину 33 выходного сигнала.

Четвертьй дешифратор 30, триггер 31, третий блок 32 задержки обеспечивают обнаружение и прием последовательности кодов старших разрядов. На входы четвертого дешифратора 30 пос-

тупает ( -1) разрядов с выхода

преобразователя 21, сигнал приема кода неравномерной шкалы с выхода второго дешифратора 28 через первый блок 29 задержки на тактовый интервал, служебная посылка.с третьего выхода преобразователя 21 последовательного кода в параллельный (третий вход). Четвертый дешифратор 30 рабо- тает в соответствии с табл. 6 состоя-

НИИ..

При обнаружении начала последовательности кодов старших разрядов триггер 31 переводится в единичное состояние. Сигнал управления с выхода триггера 31 поступает на вход второго дешифратора 28, обеспечивая появление на его выходе сигнала приема кода старших разрядов (С). Прием последовательности кодов старших разрядов прекращается.После возвращения триггера 31 в нулевое положение по сигналу, поступающему с выхода чет- вертого дешифраора 30 на его вход через третий блок 32 задержки на так- товьй интервал.В этом такте второй дешифратор 28 готов обеспечить, ггрием

кода младших разрядов или неравно мерной шкалы.

Появление логической 1 на выходе четвертого дешифратора 3.0 возможно только при начале последова- тель рости кодов старших разрядов. Эта логическая 1 появляется при обнаружении нулевой посылки после приема кода неравномерной шкалы с перегрузкой,сопровождаемого единичной служебной посылкой.

Формула изобретения

Устройство цифровой передачи и приема телевизионного сигнала, содер жащее на передающей стороне преобразователь параллельного кода в последовательный, первыу синхрогенератор и последовательно соединенные аналого- цифровой преобразователь, вход котот рого объединен с входом первого син- хрогенератора,первый регистр, второй регистр, анализатор кода,цифровой компрессор, первый дешифратор .и первый коммутатор, второй,третий, чет- вертьй, пятый, шестой и седьмой входы которого.соединены соответственно с первым выходом первого регистра соединенного с вторым входом анализатора кода, с вторым выходом первого регистра, соединенного с вторым входом цифрового компрессора, с вторым выходом анализатора кода, соединенного с третьим входом цифрового компрессора, с вторым выходом цифрового компрессора, с вторым выходом первого дешифратора и с третьим выходом первого дешифратора, второй вход которого соединен с третьим выходом анализатора кода, четвертый выход которого соединен с четвертым входом цифрового компрессора, а на приемной стороне второй синхрогенератор и последовательно соединенные .преобразователь последовательного кода в параллельный, третий регистр,второй коммутатор,четвертый регистр и цифро- аналоговьй преобразователь, последовательно соединенные второй дешифратор, первый и второй входы которого соединены соответственно с первым и - вторым выходами преобразователя последовательного кода в параллельный, и первьм блок задержки, выход которого соединен с вторым входом второго коммутатора,цифрового экс- пан дера, пер вьй, второй и третий входы которого соединены соответственно

с первым выходом третьего регистра, с первым и третьим выходами преобразователя последовательного кода в параллельный, и блок установки кода, первый, второй и третий входы которо- го соединены соответстйенно с первым выходом четвертого регистра и с вторым выходом второго дешифратора,соединенного с вторым входом третьего регистра,третий, четвертый и пятый входы которого соединены соответственно с третьим выходом второго дешифратора, с выходом блока установки кода и с третьим выходом преобразователя последовательного кода в параллельный, а второй выход которого соединен с третьим входом второго коммутатора,при этом второй выход четвертого регистра соединен с вторым входом цифроаналогового преобразователя, 20 входы пятого регистра соединены совыход первого синхрогенератора соединен с управляющими входами аналого- цифрового преобразователя,первого и второго регистров и преобразователя параллельного кода в последователь- ньш,а выход второго синхрогенератора, вход которого соединен с четвертым выходом преобразователя последовательного кода в параллельный,соединен с управляющими входами третьего и четвертого регистров, отличающееся тем, что,с целью по вьш1ения точности передачи телевизионного сигнала, введены на передающей стороне последовательно соединенные пятый регистр ,первьй вход которого соединен с первым выходом первого дешифратор а, шестой регистр,третий дешифратор, элемент ИЛИ, регистр сдвига, элемент И и сумматор по модулю

два, выход которого соединен с первым входом преобразователя параллельного кода в последовательный,последовательно соединенные седьмой регистр, первый вход которого соединен с вы- 45 ходом первого коммутатора, и третий коммутатор, выход которого соединен с вторым входом преобразователя па

раллельного кода в последовательный, а второй и третий входы соединены соответственно с выходом второго регистра и с выходом элемента И,второй и третий входы которого соединены соответственно с вторым и третьим выходами регистра сдвига, а на приемной стороне - последовательно соединенные четвертый дешифратор,первый, второй и третий входы которого соединены соответственно с вторым и первым выходами преобразователя последовательного кода в параллельный и с выходом первого блока задержки,третий 5 блок задержки и триггер, второй вход которого соединен с выходом четвертого дешифратора, а выход соединен с. третьим входом второго дешифратора, при этом второй, третий и четвертый

5

0

5

0

5

ответственно с третьим и вторым выходами первого дешифратора и с первым выходом цифрового компрессора, второй, третий и четвертый выходы пятого регистра соединены соответственно с вторым, третьим и четвертыми входами пятого регистра, объединенными соответственно с вторым, третьим и четвертым входами третьего дешифратор а, пятый, шестой, седьмой, восьмой, девятый, десятьй, одиннадцатый и двенадцатый входы которого соединены соответственно с первьм выходом пятого регистра,с вторым, третьим и четвертым выходами шестого регистра,с выходом цифрового компрессора, с вторым, первым и третьим выходами первого дешифратора, второй и третий выходы третьего дешифратора соединены соответственно с вторьи и третьим входами элемента ИЛИ, второй вход седьмого регистра соединен с четвертым выходом первого дешифратора, а второй выход соединен с вторым входом сумматора по модулю два, а выход пер- вогд синхрогенератора соединен с управляющими входами пятого, шестого и седьмого регистров и регистра сдвига.

Таблица 1

001

010

011

100

101

110

111

111

1010 1010 1011 1101

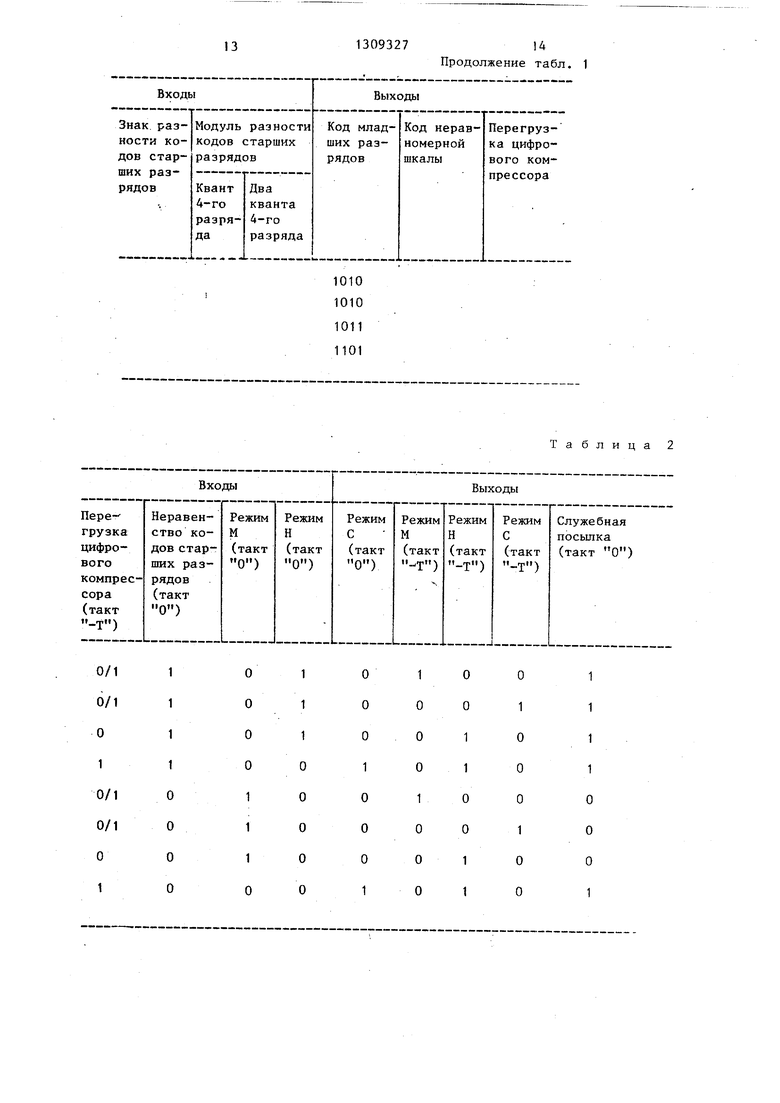

Таблица 2

Таблица 3

Таблица 4

Таблица 6

фиг. /

Фиг. 2

Перегрузка((иуение)

Редактор Л. Гратилло

Составитель Э. Борисов

Техред М.Ходанич Корректор А. Тяско

Заказ 1805/56Тираж 639 .Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифровой передачи и приема телевизионного сигнала | 1981 |

|

SU1001501A1 |

| Система цифровой передачи и приема сигналов цветного телевидения | 1978 |

|

SU764150A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1418903A1 |

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1385327A1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1001092A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1984 |

|

SU1343440A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

Изобретение м.б. использовано в системах передачи телевизионного сигнала методом импульсно-кодовой модуляции . Цель изобретения - повышение точности передачи телевизионного сигнала. На ил. приведены структурные схемы передающей и приемной сторон устр-ва, а также пример формирования неравномерной шкалы квантования цифрового компрессора для кода, записанного в 1-м регистре. Этот код будет передан в режиме Н. Цифровой компрессор работает в соответствии с кодовой табл. Для отрицат. знака разности кодов старших разрядов табл. аналогична, но предполагается осуществление в компрессоре предварительной инверсии кода младших разрядов. Цифровой эксандер может работать в соответствии с др. приведенной кодовой табл. 1-й, 2-й, 3-й, 4-й дешифраторы работают в соответствии с приведенной табл. состояний. 6 табл. 3 ил. (Л с

| Устройство цифровой передачи и приема телевизионного сигнала | 1981 |

|

SU1001501A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-09—Подача