тов и, четвертый вход - с выходом четвертого блока оперативной памяти, соединенного информационным и управляющим входами с одноименными входами первого, второго и третьего блоков оперативной памяти, вторые входы первых элементов И соединены соответственно с выходами вторых формирователей импульсов, отличающеес я тем, что, с целью повьйаения достоверности контроля, в него введены блок измерения времени, формирователь контрольного интервала времени, блок сравнения, инвертор, второй элемент И и пятый блок оперативной памяти, причем входы блока измерения времени и формирователя контрольного интервала времени соединены между собой и с выходом второго элемента И, первый вход которого соединен через инвертор с выходом блока групповой оценки, второй вход второго элемента И соединен с выходом пятого блока оперативной памяти, соединенного информационным и управляющим входами с одноименными входами первого, второго, третьего и четвертого блоков оперативной памяти, выходы формирователя контрольного интервала времени и блока измерения времени соединены с первым и вторым входами блока сравнения соответственно, первый выход которого соединен с первым входом блока печати и дервым входом первого переключателя,второй вход которого соединен с вторым входом блока сравнения.

2.Устройство по п. 1, отличающееся тем, что блок сравнения содержит элемент сравнения, первый и второй триггеры, элемент И,

.элемент ИЛИ, причем первый вход элемента сравнения соединен с первым входом элемента И и первым входом блока, второй вход - с вторым входом блока, а выход - с входом первого триггера, первый выход которого соег динен с вторьм входом элемента И, второй выход - с первым входом элемента ИЛИ,второй вход которого соединен с выходом второго триггера

и первым выходом блока, вход второго триггера соединен с выходом элемента И, второй выход блока- соединен с выходом элемента ИЛИ.

3.Устройство по п. 1, о т л ичающееся тем, что блок измерения времени содержит генератор импульсов, элемент И и счетчик, причем выход генератора импульсов соеди нен с первым входом элемента И-, второй вход которого соединен с входом блока, а выход - с входом счетчика, выход которого соединен с выходом бло.ка.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрического монтажа | 1980 |

|

SU938212A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ | 1990 |

|

RU2062502C1 |

| Устройство контроля параметров | 1982 |

|

SU1119030A1 |

| Устройство для контроля соединений в электрическом монтаже | 1990 |

|

SU1758606A1 |

| Устройство для контроля параметров | 1984 |

|

SU1275472A1 |

| Система управления технологическим процессом дискретного производства | 1984 |

|

SU1251110A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Устройство для контроля и регулирования параметров | 1984 |

|

SU1249491A1 |

| Устройство для контроля параметров | 1985 |

|

SU1267437A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКОГО MOHTAIKA, содержащее блок печати, блок ввода программной информации, выход которого соединен с входом блока предварительной обработки информации, блок распределения информации, вход которого соединен с выходом блока предварительной обработки информации, задающий и опрашивающий коммутаторы, управляющие входы которых соединены соответственно через первьй и второй блоки управления с выходами первого и второго блоков оперативной памяти, причем вь1ходы задающего коммутатора и информационные входы опрашивающего коммутатора соединены с клеммами для подключения входов и выходов объекта контроля соответственно, блоки анализа, первые входы которых соединены с выходами опрашивающего коммутатора, при этом информационные входы первого и второго блоков оперативной памяти соединены с выходом блока распределения. информащш, а их управляющие входы с выходом блока предварительной обработки информации, первый и второй формирователи опорного сигнала, третий и четвертьш блоки оперативной памяти, первый и вторые переключатели, первый и вторые формирователи импульсов-, первые элементы И, элемент ИЛИ, блок групповой оценки, причем выход первого формирователя опорного сигнала соединен с вторыми входами блоков анализа, выход второго формирователя опорного сигнала соединен с информационным входом задающего коммутатора и третьими входами блоков анализа, четвертые входы которых. соединены с выходом третьего блока оперативной памяти,, выходы блоков анализа соединены с первыми входа(Л ми соответствующих элементов И, с соответствующими первыми входами вторых переклюдателей и соответствующими входами блрка групповой оценки, первый вход блока печати соединен с первым входом первого переключателя, соединенного входом-выходом через ч первый формирователь импульсов с первым входом элемента ИЛИ, соединенного вторыми входами через соответствующие вторые форйирователи импульсов с входами-выходами соответ&9 ствующих вторых переключателей, первый из которых соединен вторым входом с выходом первого переключателя, последний выходом соединен с входом блока ввода программной информации, все вторые переключатели, кроме первого из них, вторыми входами - с выходами предшествующих переключателей, выход элемента ИЛИ соединен с вторым взгодом блока печати, третьи входад которого соединены с выходами соответствующих первых элемеи

1

Изобретение относится к контрольно-измерительной технике и может быть использовано для проверки монтажа сложных радиоэлектронных устройств электрических жгутов и печатных плат в процессе производства и эксплуатаЦИН.

Целью изобретения является повыше кие достоверности результатов контроля электрического монтажа за счет уменьшения влияния случайной составляющей на формирование результата контроля.

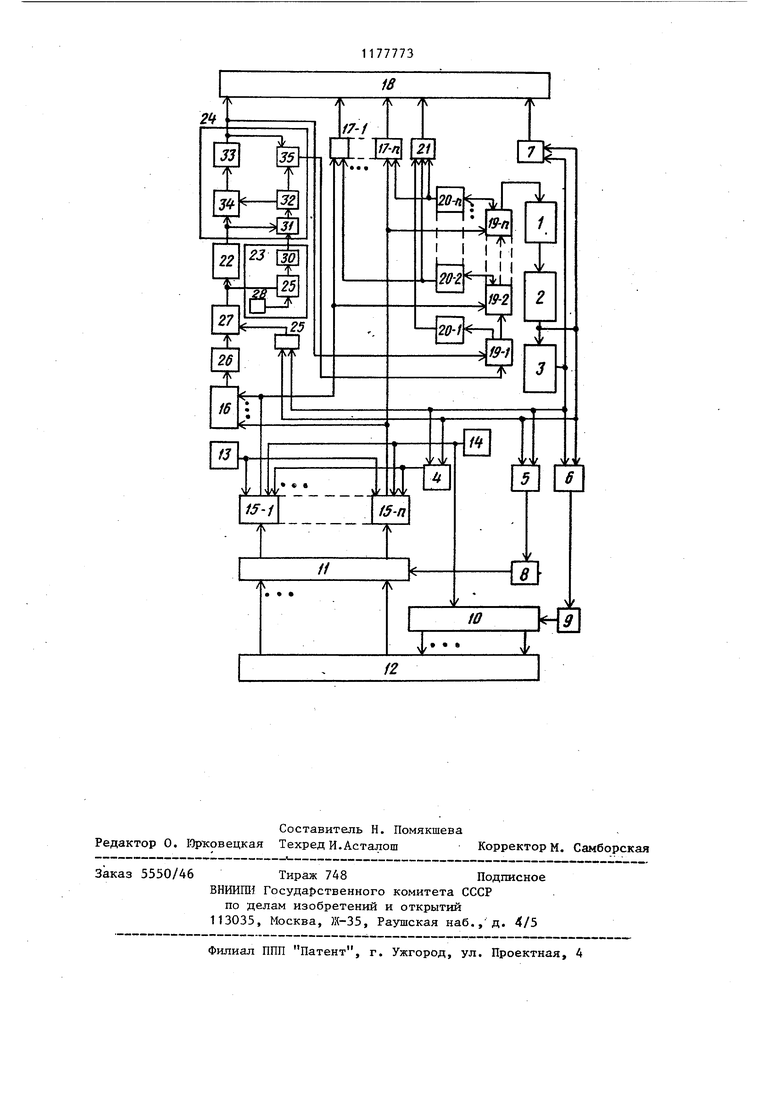

Ра чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит блок 1 ввода программной информации, например

фотосчитывающее устройство,- блок 2 предварительной обработки информации, например дешифратор, блок 3 распределения информации, выполненный, например, на группах двухвходовых элементов И, третий 4, вуорой 5, первый 6 и четвертый 7 блоки оперативной памяти, выполненные, например на КС-триггерах или регистрах, первый 8 и второй 9 блоки управления, например формирователи тока (типа ИМС 146АА2А, 169АА2А), задающий 10 и опрашивающий 11 коммутаторы, контролируемый объект 12, первый 13 и второй 14 формирователи опорных сигнаJIOB, блоки 15 анализа, выполненные, например, на пороговых и коммутирую31

щих элементах, блок 16 групповой оценки, например элемент ИЛИ, первые элементы И 17.1 - 17.п, блок 18 печати, переключатели 19.1 - 19.П, содержащие включенные на .выходе двухвходовые элементы ИЛИ и включенные на входе управляемые переключающие на два направления сигнал запуска элементы, выполненные, например, на электромагнитных реле или логических микросхемах, формирователи 20,1 20.п импульсов, элемент ИЛИ 21,формирователь 22 контрольного интервала времени, блок 23 измерения времени, блок 24 сравнения, пятый блок 25 оперативной памяти, выполненный, например, на RS-триггерах или регистре, инвертор 26 и второй элемент И 27.

Первые входы переключающих элементов из состава переключателей 19.1 - 19.П соединены с первыми входами входящих в переключатели 19.1 19.ri элементов ИЛИ непосредственно, а вторые выходы этих переключающих элементов соединены с вторыми входами указанных элементов ИЛИ через соответствующие формирователи 20.1 20.п импульсов.

В состав блока 23 измерения времени входят генератор 28 импульсов, элемент И 29 и счетчик 30,

Блок 24 сравнения содержит узел 31 сравнения, триггеры 32 и 33, элемент И 34 и элемент ИЛИ 35.

В качестве формирователя 22 контрольного интервала времени может использоваться любой формирователь, например на счетчиках или с использованием КС-элементов.

Узел 31 сравнения может быть, выполнен на логических элементах И, первые входы которых соединены с входами cooтвeтcтвyюE иx разрядов счетчика 30, а второй вход - с выходом формирователя 22 контрольного интервала времени.

777734

информационные входы опрашивающего коммутатора 14 соединены с клеммами для подключения входов и выходов контролируемого объекта 12 соответственно, первые входы блоков 15 анализа соединены с выходами опрашивающего коммутатора 11, информационные входы первого 6 и второго 5 блоков оперативной памяти соединены с выходом блока 3 распределения информации, а их управляющие входы - с выходом блока 2 предварительной обработки информации, выход первого формирователя 13 опорного сигнала соеt5 динен с вторыми входами блоков 15 . анализа, выход второго формирователя

14опорного сигнала соединен с информационным входом задающего коммутатора 10 и третьими входами блоков

20 15 анализа, четвертые входы которых соединены с выходом третьего блока 4 оперативной памяти, выходы блоков

15анализа соединены с первыми входами соответствующих элементов И 17,

25 соответствующими первыми входами вторых переключателей 19.2 - 19.п и соответствующими входами блока 16 групповой оценки, первый вход блока 18 печати соединен с первым входом

30 первого переключателя 19.1, соеди-. ненного входом-выходом через первый формирователь 20.1 импульсов с первым входом элемента ИЛИ 21, соединенного вторыми входами через соответствующие

, вторые формирователи 20.2 - 20.п импульсов с входами-выходами вторых переключателей 19.2 - 19.п, первый из которых соединен вторым входом с выходом первого переключателя 19.1,

0 а последний выходом соединен с входом блока 1 ввода программной информации, все вторые переключатели 19.2 - 19.п, кроме первого из них, вторыми входами соединены с выходами

5 предшествующих переключателей, выход элемента ИЛИ 21 соединен с вторым входом блока 18 печати, третьи входы которого соединены с выходами соответствующих первых элементов И 17,

0 четвертый вход - с выходом четвертого блока 7 оперативной памяти, соединенного информационным и управляющим входами с одноименными входами первого 6, второго 5 и третьего 4 блоков

5 оперативной памяти, вторые входы первых элементов И J 7 соединены соответственно с выходами вторых формирователей 20.2 - 20.П импульсов, входы

блока 23 измерения времени и формирователя 22 контрольного интервала времени соединенгл между собой и с выходом второго элемента И 27, первьш вход которого соединен через инвертор 26 с выходом.блока 16 групповой оценки, второй вход второго элемента И 27- соединен с в 1 ходом пятого блока 25 оперативной памяти, соединенного информационным и управляющим входами с одноименными входами первого 6, второго 5, третьего 4 и четвертого 7 блоков оперативной памяти, выходы формирователя 22 контрольного интервала времени и блока 23 измерения времени соединены с первьм и вторым входами блока 24 сравнения соответственно, первый выход блока 24 сравнения соединен с первым входом блока 18 печати и первым входом первого переключателя 19.1, второй вход которого соединен с вторым выходом блока 24 сравнения, первьй вход элемента 31 сравнения соединен с первым входом третьего элемента И 34 и первым входом блока 24 сравнения, второй вход - с вторым входом блока 24 сравнения, а выход - с входом первого триггера 32, первый выход которого соединен с вторым входом третьего элемента И 34, второй выход - с первым входом второго элемента ШШ 35, второй вход которого соединен с выходом второго триггера 33 и первым выходом блока 24 сравнения, вход второго триггера 33 соединен с выходом третьего элемента И ,34,второй выход блока 24 сравнения соединен с выходом второго элемента ИЛИ 35, выход генера гора 28 импульсов соединен с первым входом четвертого элемента И 29, второй вход которого соединен с входом блока 23 измерения времени, а выход -с входом счетчика ЗО вэходл которого соединен с выходом блока 23 измерения времени.

Устройство работает следующим образом,

Контроль электрического монтажа производят путем последовательной проверки всех цепей объекта на наличие требуемых связей. При этом всякий раз с проверкой очередной цепи на наличие производят контроль на отсутствие у нее непредусмотренных связей с всеми остальными цепями контролируемого объекта 12, В начале контроля каж/.);ой

группы цепей все триггеры и сч,етчики устройства приводят в исходное состояние подачей сигнала Сброс, считываемого с перфоленты блоком 1.

В исходном состоянии в выходных и буферных регистрах блоков 4, 5, 6, 7 и 25 оперативной памяти программная информация отсутствует. В соответствии . с этим на задающий коммутатор 10 управляющие сигналы с блока 9 управления не поступают о Разомкнутые в исходном состоянии контакты задающего KOMMi/татора 10 отключают формирователь 14 от контролируемого объекта 12. Также не подаются управляющие сигналы с блока 8 на опрашивающий коммутатор 11. Выходы блоков 15 анализа отключены от цепей контролируемого объекта 12,

При контроле блок 1 ввода программной информации осуществляет считывание с программоносителя, например с перфоленты, программы контроля группы цепей. Программу с блока 1 обрабатывают в блоке 2, где выявляют служебные команды, определяющие режим работы устройства. Далее программа контроля в соответствии с установленные- в блоке 2 режимом работы и выявленными в блоке 3 адресами распределяется этим блоком по буферным регистрам блоков 4, 5, 6, 7 и 25.

По командам с блока 2, поступающим на управляющие входы блоков 4, 5, 6, 7 и 25, программная информация переписывается из буферных регистров в выходные регистры, освобождая буферные регистры для приема информации по Контролю следующей группы цепей. Кроме того, блоком 2 выявляется команда Сброс,

Прием информации в буферные регистры осуществляют за время, когда идет контроль очередной группы цепей в соответствии,с программой, находящейся в выходных регистрах.блоков 4, 5, 6, 7 и 25.

Программа, поступающая в выходные регистры блока 6, определяет адрес цепи, н.аличие которой надлежит проверить. В соответствии с этой программой блок 9 управления выдает в коммутатор 10 управляющие сигналы для подключения выхода формирователя 1 1 к выбранной цепи объекта 12.

. Программа, поступающая в выходные регистры блока 4, определяет peжи работы каждого из группы блоков ана лиза 15. Программа, поступающая в выходны регистры блока 5, обеспечивает подключение к входам блоков 15 анализа группы цепей объекта 12, контроль которого производят на данном такте программы контроля. В режиму контроля наличия цепи работают те блоки 15 анализа, входы которых в соответствии с программой подключены через коммутатор 11 к цепи, на которую через коммутатор 10поступает сигнал от формировател 14.Остальные блоки 15 анализа, будучи подключенными через коммутатор 11к другим цепям контролируемой гр пы, не имеющим связи с указанной цепью, работают в режиме контроля отсутствия цепи. Блок 15 анализа, работающий в ре жиме контроля наличия цепи, сравнивает сигнал с формирователя 14, пос тупающий на его первый вход, с тем же сигналом, поступающим с формирователя 14 на второй вход через конт ролируемую цепь объекта 12. Если результат анализа показывает, что указанные сигналы с формирователя 14 отличаются на величину, превышаю щую допустимую, то блок 15 вырабатьшает оценку Негоден. Те блоки 15,которые работают в режиме контроля отсутствия связи, сравнивают сигналы, наводимые в контролируемых цепях (электрически не связанных с цепью, на которую подан сигнал с формирователя 14), с опорным сигналом, поступающим с формирователя 13 В случае, когда сигнал, наводимьй в контролируемой цепи через сопротивление утечки из цепи, связанной с формирователем 14, превышает сигнал с формирователя 13, соответствующий блок анализа формирует оценку Негоден. Выявленные в блоках 15 анализа отклонения от программного задания (в виде оценок Негоден) поступают в блок 16 групповой оценки, который формирует оценку контролируемой группы цепей. Группа цепей оценивается блоком 16 как негодная, если на выходе хотя бы одного из блоков 15 анализа сформирована оценка Негоден. Инвертированный инвертором 26 сигнал с выхода блока 16 (сигнал оце ки Годен) через элемент И 27, открытый на период выполнения такта программы контроля, поступает на вход формирователя 22 контрольного интервала времени. Запускаясь по переднему фронту этого сигнала,формирователь 22 вырабатывает контрольный интервал времени, который поступает на первый вход блока 24 сравнения. Сигнал Годен с выхода элемента И 27, поступает также на вход блока 23 измерения, где осуществляется измерение суммарного времени его существования в течение такта программы контроля. Число разрядов счетчика 30 выбирается из условия,что его заполнение импульсами с выхода генератора 28 через элемент И 29 при непрерывности сигнала Годен должно осуществляться за время, не превышающее контрольного интервала, формируемого формирователем 22. Соотношение между контрольным интервалом времени и указанным временем заполнения счетчика 30 определяет уровень обеспечиваемой предлагаемым устройством достоверности контроля. Если сигнал с выхода счетчика 30, свидетельствующий о его заполнении, поступает на вход элемента И узла 31 сравнения до окончания существования на его втором входе контрольного интервала с выхода формирователя 22, то на выходе элемейта И узла 31 срав нения образуется сигнал, свидетельствующий, что контроль группы цепей на данном такте контроля осуществлен с требуемой достоверностью. Результат контроля Годен признан окончательным. Сигнал об этом с выхода элемента И узла 31 сравнения поступает на установочный вход триггера 32, с прямого выхода которого через элемент ИЛИ 35 поступает на первый вход переключа геля 19.1. С инверсного выхода триггера 32 сигнал поступает на первый вход элемента И 34. В противном случае, т.е. когда суммарное время существования- сигнала Годен превышает контрольный интервал времени с формирователя 22, сигнал, соответствующий во времени заднему фронту интервала времени с формирователя 22, поступает на второй вход элемента И 34 и далее (так как на его первом входе запрещающий сигнал с триггера 32 отсутствует) с выхода элемента И 34 на установоч ный вход триггера 33 в качестве оценки Негоден. С выхода триггера 33 сигнал Негоден поступает через элемент . ИЛИ 35 на вход первого переключателя 19.1 и напервый вход блока печати. Переключатель 19.1 запускает фор мирователь 20.1. Импульсный сигнал с формирователя 20.1 через логический элемент ИЛИ 21 поступает на вто рой вход блока 18 печати и разрешает регистрацию результата групповой оценки, поступившего с блока 24 на первый вход блока 18 печати. По заднему фронту сигнала с формирователя 20.1 разрешается прохождение сигналов Годен или Негоден с блока 24 через переключатель 19.1 на вход переключателя 19.2. Работа переключателей 19.2 - 19.П зависит от наличия на втором их входе сигнала Негоден с выхода соответствующего блока 15 (группы блоков). Когда такого сигнала нет, переключатель, например, 19.2 транспортирует на выход сигнал, действующий на его входе, без задержки на время определяемое соответствующим формир вателем 20.2, и не выдает сигнала 1на формирователь 20.2. Когда сигнал 7310 Негоден имеется на втором входе переключателя .19.2, последний выдает его на запуск соответствующего формирователя 20.2 без задержки, а на вход последующего переключателя 19.3с задержкой на время срабатывания формирователя 20.2. Переключатель 19.П выдает сигнал на вход блока 1 ввода программной информации. По этому сигналу блок 1 обеспечивает переход к контролю очередной группы цепей. При этом обеспечивается перезапись информации в блоках 4, 5, 6, 7 и 25 с буферных регистров в- выходные регистры, а затем в буферные регистры вводится программная информация контроля следующей группы цепей. Блок 7 при этом обеспечивает хранение информации, необходимой для переадресации .номеров блоков 15, давших результат Негоден, в конструктивные адреса объекта 12 и в номера его цепей. После окончания контроля всех цепей объекта 12, не связанных непосредственно с очередной цепью, контролируемой на наличие связей, переходят к контролю следующей цепи на наличие требуемых связей и также проверяют отсутствие ложных связей с остальными цепями объекта 12,

| Устройство для контроля монтажных схем | 1975 |

|

SU559244A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля электрического монтажа | 1980 |

|

SU938212A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-09-07—Публикация

1983-05-06—Подача